Изобретение относится к электротехнике и может быть использовано в Качестве вторичного источника электропитания .

Целью изобретения является повышение быстродействия при активно-реактивном характере нагрузки.

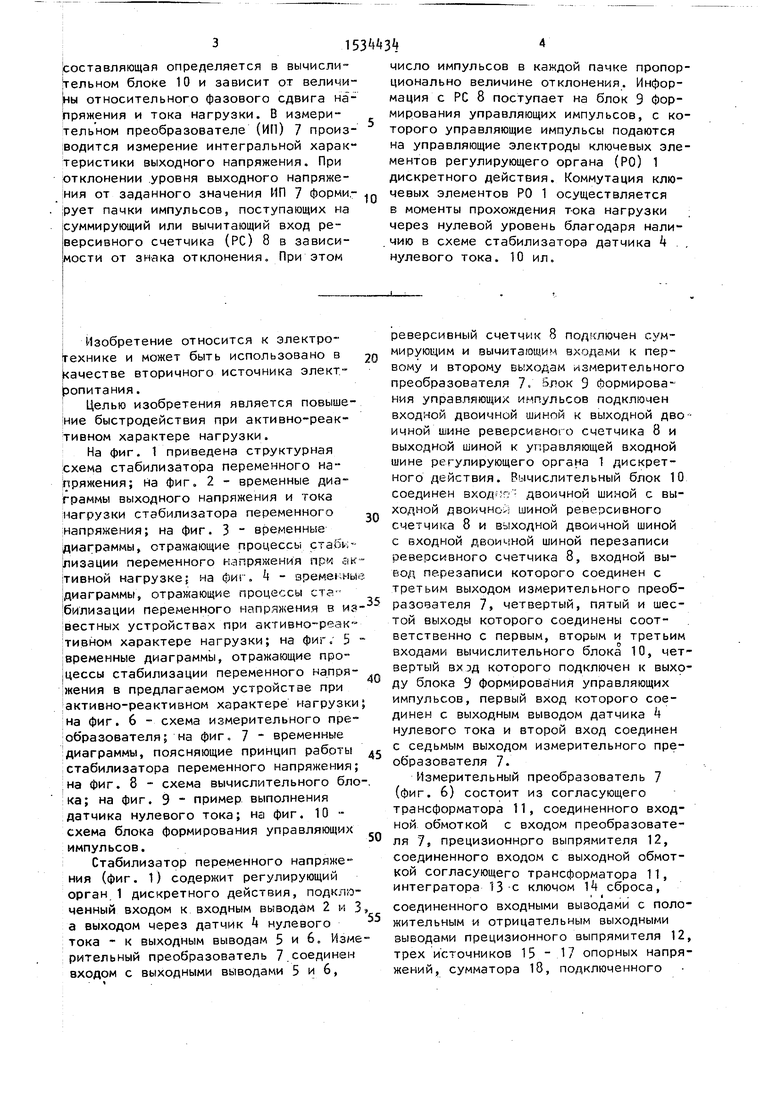

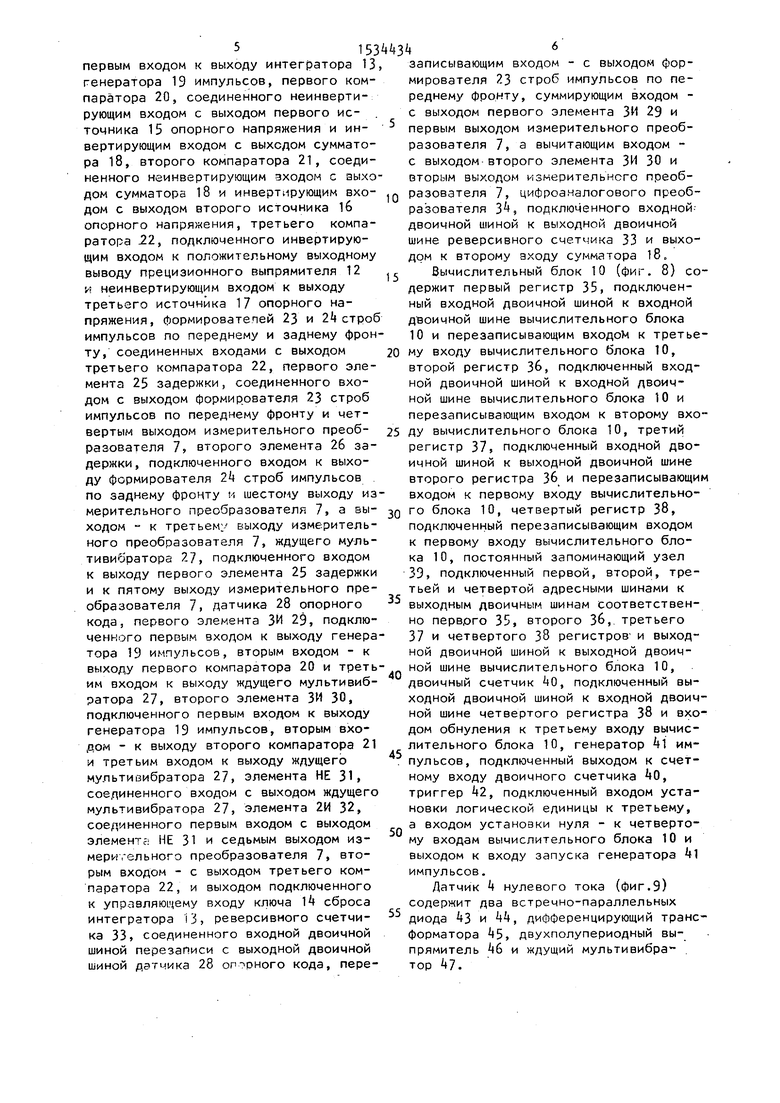

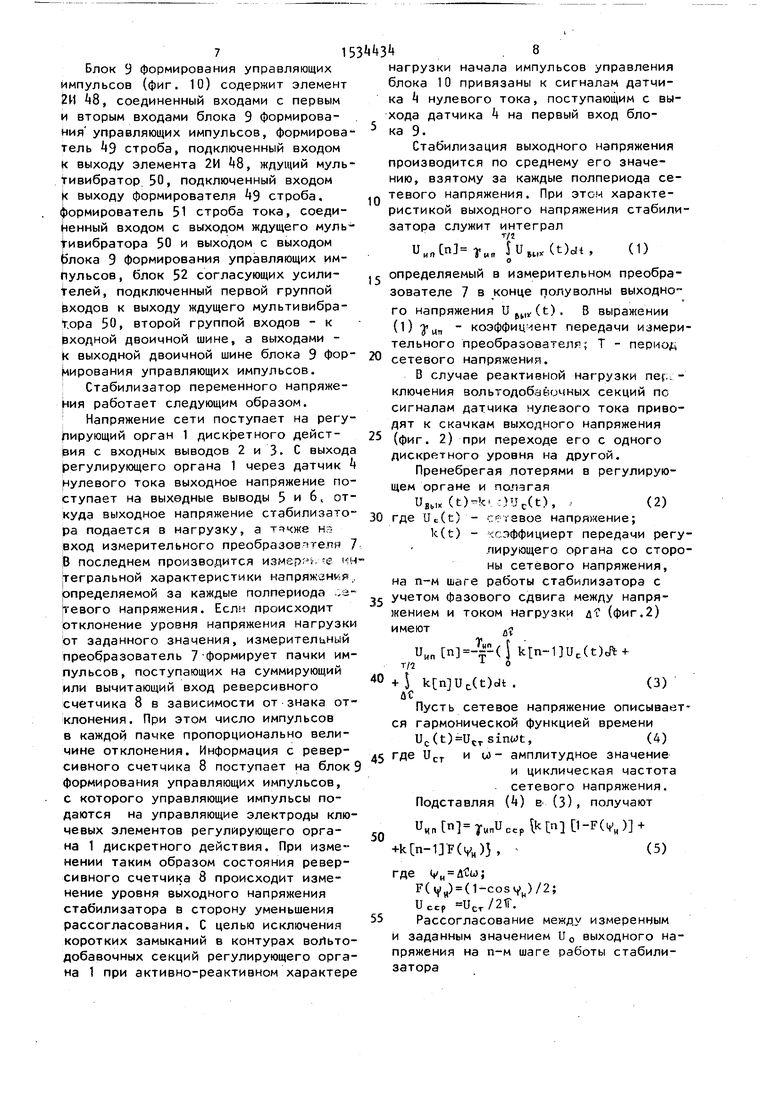

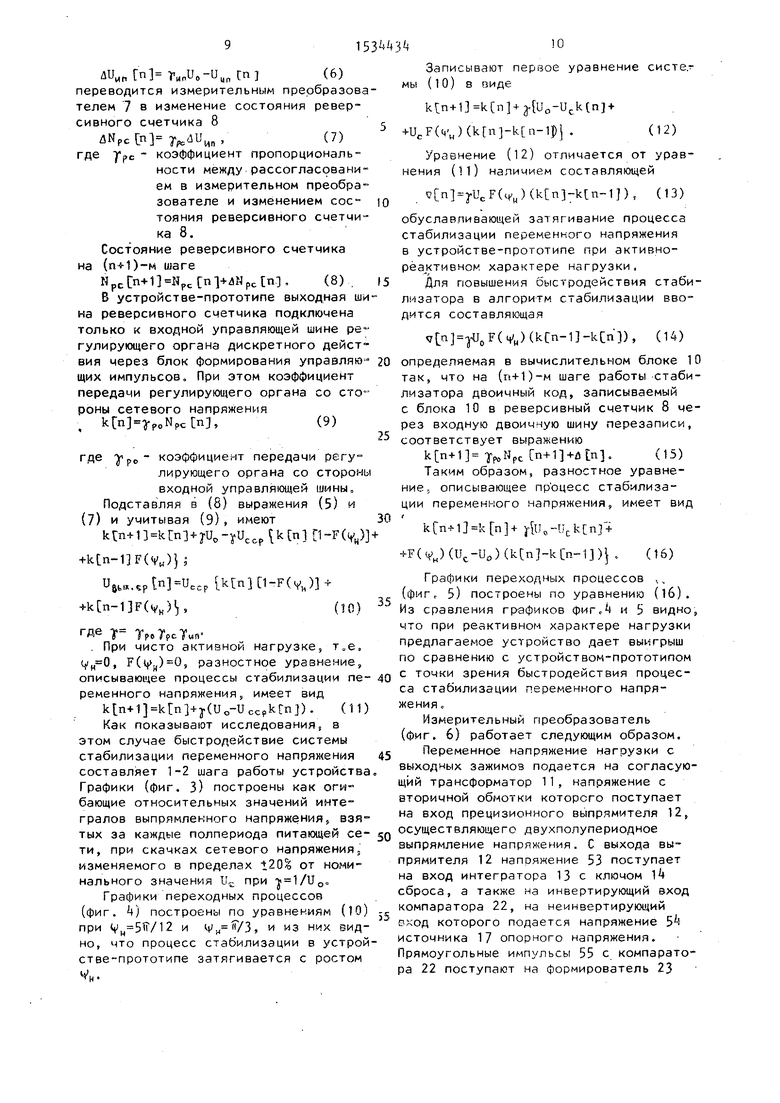

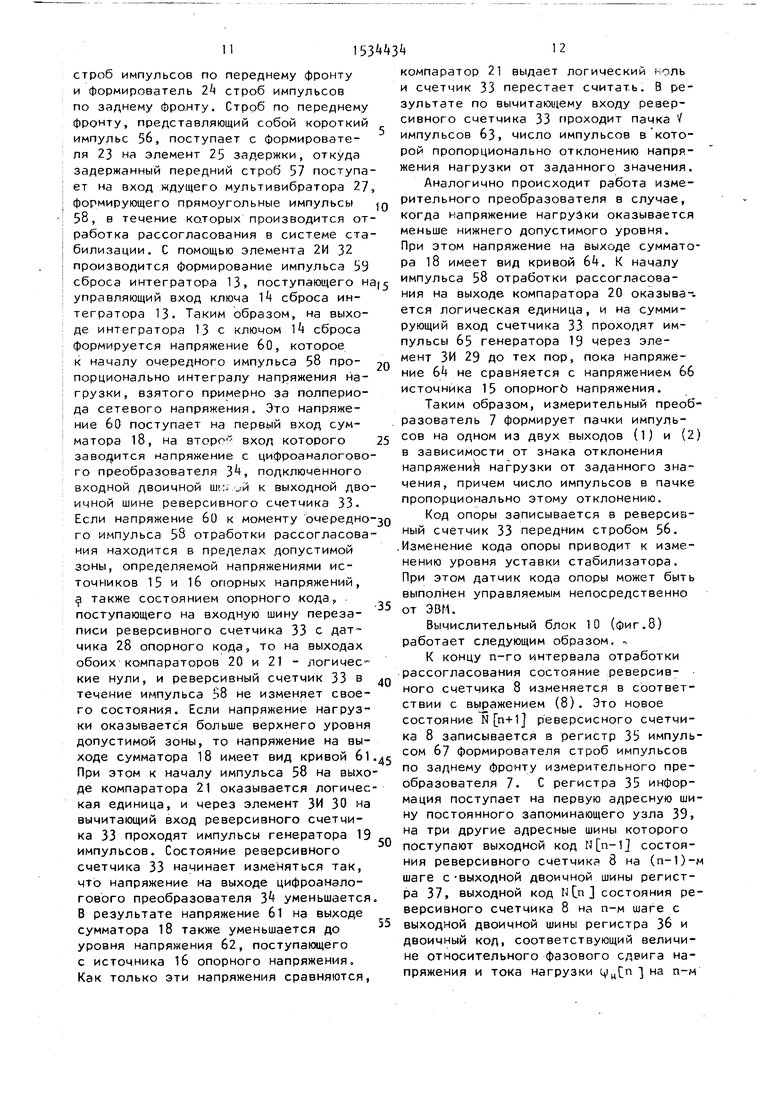

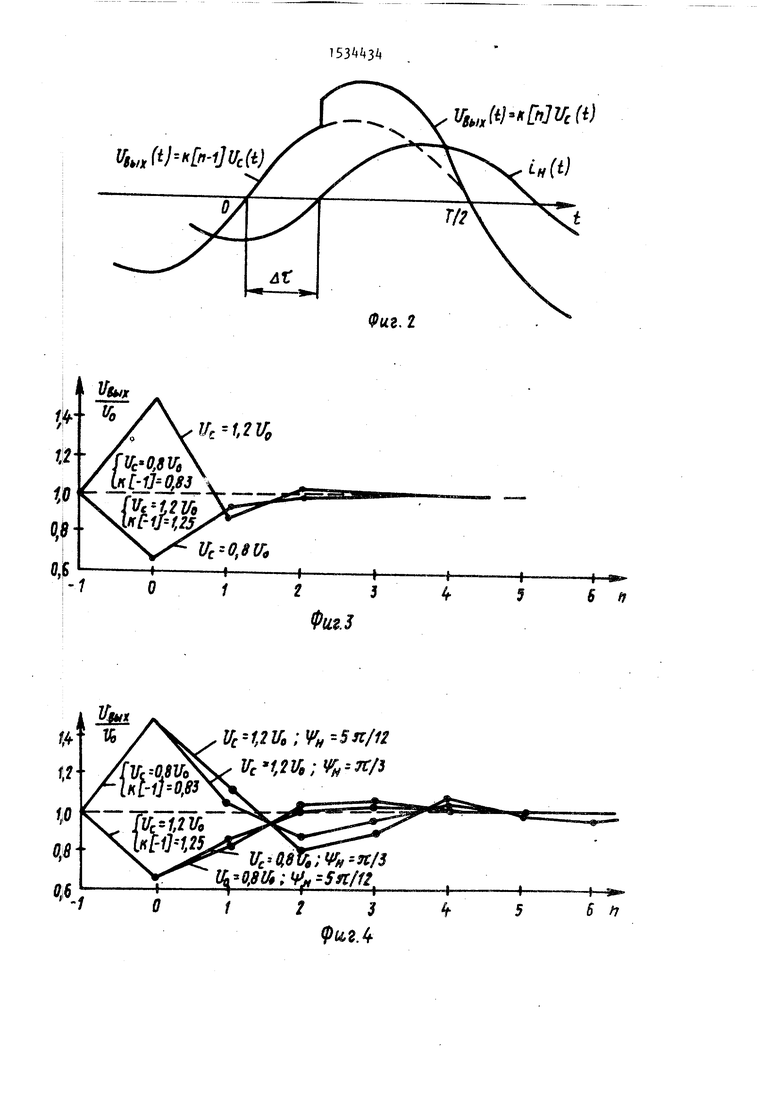

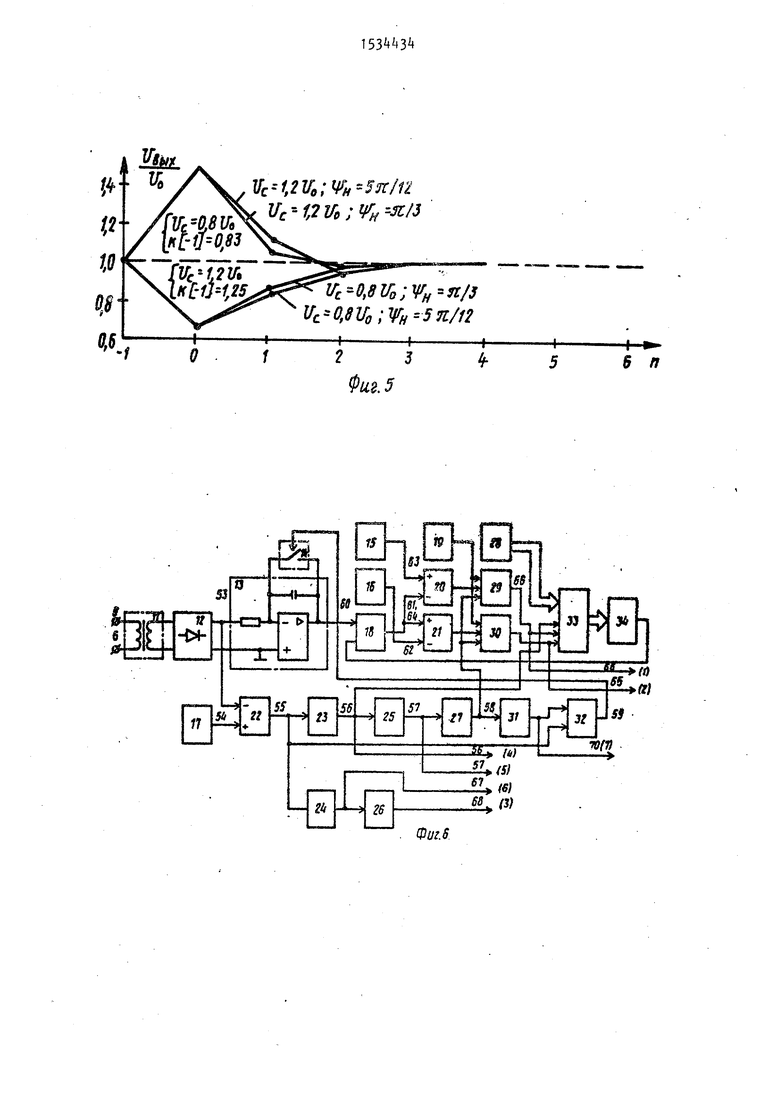

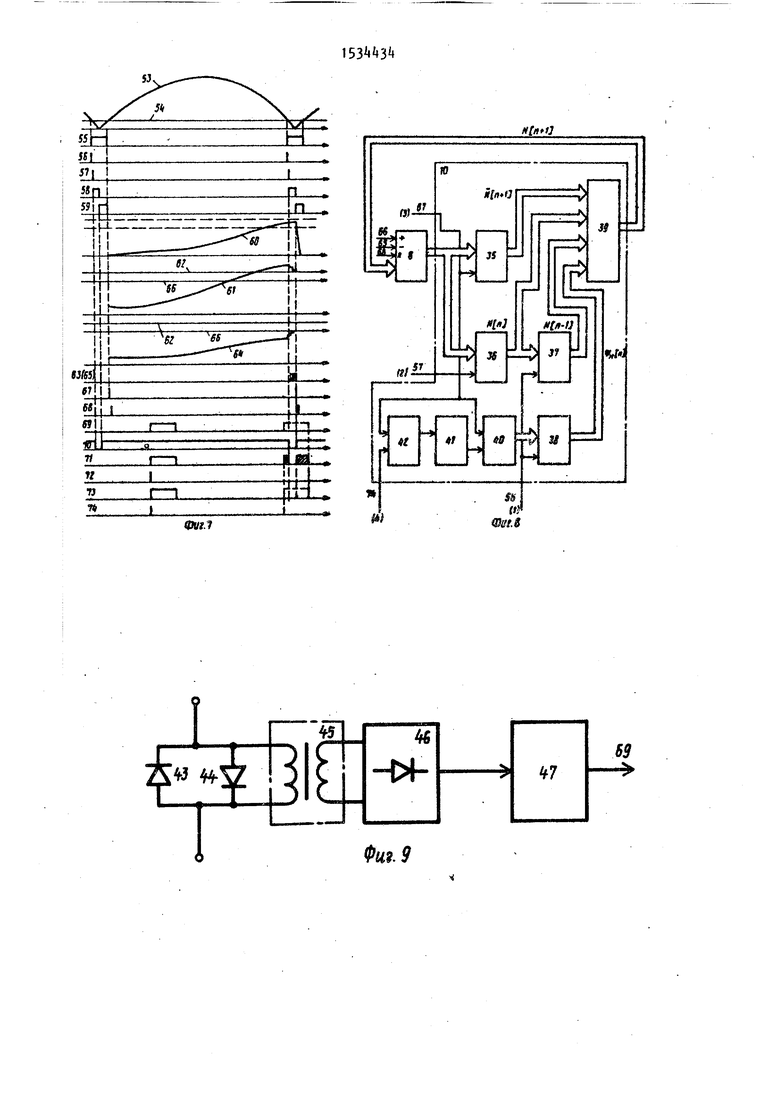

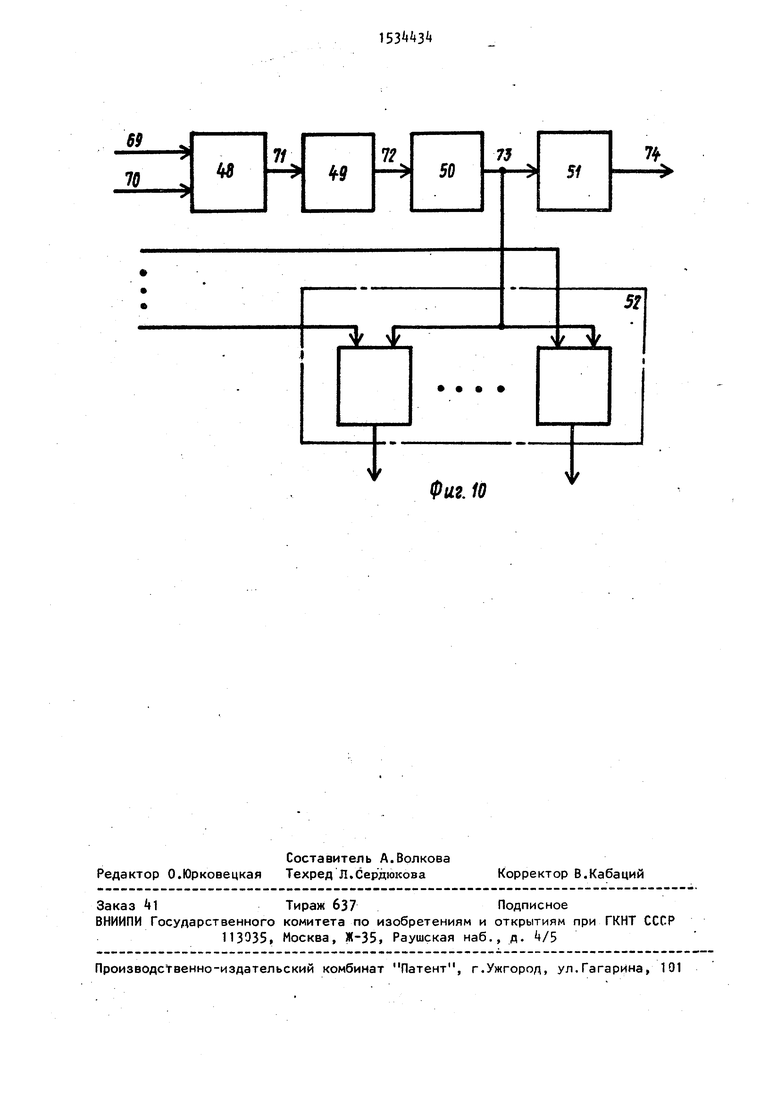

На фиг. 1 приведена структурная схема стабилизатора переменного напряжения; на фиг. 2 - временные диаграммы выходного напряжения и тока нагрузки стабилизатора переменного напряжения; на фиг. 3 - временные диаграммы, отражающие процессы CTal Jv,- лизации переменного напряжения при активной нагрузке; на фиг. - временны диаграммы, отражающие процессы ста-- билизации переменного напряжения в известных устройствах при активно-реактивном характере нагрузки; на фиг; 5 временные диаграммы, отражающие процессы стабилизации переменного напряжения в предлагаемом устройстве при активно-реактивном характере нагрузки на фиг. 6 - схема измерительного преобразователя; на фиг о 7 временные диаграммы, поясняющие принцип работы стабилизатора переменного напряжения; на фиг. 8 - схема вычислительного бло ка; на фиг. 9 - пример выполнения датчика нулевого тока; на фиг. 10 - схема блока формирования управляющих импульсов.

Стабилизатор переменного напряжения (фиг. 1) содержит регулирующий орган 1 дискретного действия, подключенный входом к входным выводам 2 и 3 а выходом через датчик b нулевого тока - к выходным выводам 5 и 6. Измерительный преобразователь 7.соединен входом с выходными выводами 5 и 6,

0

Q

0

0

реверсивный счетчик 8 подключен суммирующим и вычитающим входами к первому и второму выходам измерительного преобразователя 7. ьлок 9 йормирова- ния управляющих импульсов подключен входной двоичной шиной к выходной дво - ичной шине реверсивно о счетчика 8 и выходной шиной к управляющей входной шине регулирующего органа 1 дискретного действия. Вычислительный блок 10 соединен вход-: 7: двоичной шиной с выходной двоично.-: шиной реверсивного счетчика 8 и выходной двоичной шиной с входной двоичной шиной перезаписи реверсивного счетчика 8, входной вывод перезаписи которого соединен с третьим выходом измерительного преобразователя 7, четвертый, пятый и шестой выходы которого соединены соответственно с первым, вторым и третьим входами вычислительного блока 10, четвертый вхэд которого подключен к выхр- ду блока 9 формирования управляющих импульсов, первый вход которого соединен с выходным выводом датчика k нулевого тока и второй вход соединен с седьмым выходом измерительного преобразователя 7.

Измерительный преобразователь 7 (фиг. 6) состоит из согласующего трансформатора 11, соединенного входной обмоткой с входом преобразователя 7, прецизионнрго выпрямителя 12, соединенного входом с выходной обмоткой согласующего трансформатора 11,

интегратора 13-с ключом 14 сброса,

t

соединенного входными выводами с положительным и отрицательным выходными выводами прецизионного выпрямителя 12, трех источников 15 - 17 опорных напряжений, сумматора 18, подключенного

первым входом к выходу интегратора 13 генератора 19 импульсов, первого компаратора 20, соединенного неинвертирующим входом с выходом первого источника 15 опорного напряжения и инвертирующим входом с выходом сумматора 18, второго компаратора 21, соединенного неинвертирующим зходом с выходом сумматора 18 и инвертирующим входом с выходом второго источника 16 опорного напряжения, третьего компаратора 22, подключенного инвертирующим входом к положительному выходному выводу прецизионного выпрямителя 12 у неинвертирующим входом к выходу третьего источника 17 опорного напряжения, Формирователей 23 и 2k строб импульсов по переднему и заднему фронту, соединенных входами с выходом третьего компаратора 22, первого элемента 25 задержки, соединенного входом с выходом формирователя 23 строб импульсов по переднему фронту и четвертым выходом измерительного преобразователя 7, второго элемента 26 задержки , подключенного входом к выходу формирователя 2k строб импульсов по заднему фронту и шестому выходу измерительного преобразователя 7, а вы- Q го блока 10, четвертый регистр 38,

ходом - к третьем/ выходу измерительного преобразователя 7, ждущего муль- тивибоатора 27, подключенного входом к выходу первого элемента 25 задержки и к пятому выходу измерительного преобразователя 7, датчика 28 опорного кода, первого элемента ЗИ 29, подключенного первым входом к выходу генератора 19 импульсов, вторым входом - к выходу первого компаратора 20 и третьим входом к выходу ждущего мультивибратора 27, второго элемента ЗИ 30, подключенного первым входом к выходу генератора 19 импульсов, вторым входом - к выходу второго компаратора 21 л третьим входом к выходу ждущего мупьтивибратора 27, элемента НЕ 31, соединенного входом с выходом ждущего мультивибратора 27, элемента 2И 32, соединенного первым входом с выходом элемент НЕ 31 и седьмым выходом измерительного преобразователя 7, вторым входом - с выходом третьего компаратора 22, и выходом подключенного к управляющему входу ключа 14 сброса

35

40

45

50

подключенный перезаписывающим входом к первому входу вычислительного блока 10, постоянный запоминающий узел 39, подключенный первой, второй, третьей и четвертой адресными шинами к выходным двоичным шинам соответственно перврго 35, второго 36, третьего 37 и четвертого 38 регистров и выходной двоичной шиной к выходной двоичной шине вычислительного блока 10, двоичный счетчик 40, подключенный выходной двоичной шиной к входной двоичной шине четвертого регистра 38 и входом обнуления к третьему входу вычислительного блока 10, генератор 41 импульсов, подключенный выходом к счетному входу двоичного счетчика 40, триггер 42, подключенный входом установки логической единицы к третьему, а входом установки нуля - к четвертому входам вычислительного блока 10 и выходом к входу запуска генератора 41 импульсов.

Датчик 4 нулевого тока (фиг.9) содержит два встречно-параллельных

интегратора ij, реверсивного счетчи- 55 диода 43 и 44, дифференцирующий транска 33, соединенного входной двоичной шиной перезаписи с выходной двоичной шиной дэтиика 28 опорного кода, пере1534434

0

записывающим входом - с выходом формирователя 23 строб импульсов по переднему фоонту, суммирующим входом - с выходом первого элемента ЗИ 29 и первым выходом измерительного преобразователя 7, а вычитающим входом - с выходом второго элемента ЗИ 30 и вторым выходом измерительного преобразователя 7, цифроаналогового преобразователя 34, подключенного входной двоичной шиной к выходной двоичной шине реверсивного счетчика 33 и выходом к второму аходу сумматора 18.

Вычислительный блок 10 (фиг. 8) содержит первый регистр 35, подключенный входной двоичной шиной к входной двоичной шине вычислительного блока 10 и перезаписывающим входом к третье0 му входу вычислительного блока 10, второй регистр 36, подключенный входной двоичной шиной к входной двоичной шине вычислительного блока 10 и перезаписывающим входом к второму вхо5 ДУ вычислительного блока 10, третий регистр 37, подключенный входной двоичной шиной к выходной двоичной шине второго регистра 36 и перезаписывающим входом к первому входу вычислительно5

5

0

5

0

подключенный перезаписывающим входом к первому входу вычислительного блока 10, постоянный запоминающий узел 39, подключенный первой, второй, третьей и четвертой адресными шинами к выходным двоичным шинам соответственно перврго 35, второго 36, третьего 37 и четвертого 38 регистров и выходной двоичной шиной к выходной двоичной шине вычислительного блока 10, двоичный счетчик 40, подключенный выходной двоичной шиной к входной двоичной шине четвертого регистра 38 и входом обнуления к третьему входу вычислительного блока 10, генератор 41 импульсов, подключенный выходом к счетному входу двоичного счетчика 40, триггер 42, подключенный входом установки логической единицы к третьему, а входом установки нуля - к четвертому входам вычислительного блока 10 и выходом к входу запуска генератора 41 импульсов.

Датчик 4 нулевого тока (фиг.9) содержит два встречно-параллельных

5 диода 43 и 44, дифференцирующий трансформатора 45, двухполупериодный выпрямитель 46 и ждущий мультивибратор 47.

Блок 9 формирования управляющих импульсов (фиг. 10) содержит элемент 2И А8, соединенный входами с первым и вторым входами блока 9 формирования управляющих импульсов, формирователь 9 строба, подключенный входом К выходу элемента 2И 8, ждущий мультивибратор 50, подключенный входом К выходу формирователя 9 строба, формирователь 51 строба тока, соеди- (ченный входом с выходом ждущего муль- УИвибратора 50 и выходом с выходом блока 9 формирования управляющих импульсов, блок 52 согласующих усилителей, подключенный первой группой Ьходов к выходу ждущего мультивибра- topa 50, второй группой входов - к входной двоичной шине, а выходами - к выходной двоичной шине блока 9 фор- Мирования управляющих импульсов.

Стабилизатор переменного напряжения работает следующим образом.

Напряжение сети поступает на регулирующий орган 1 дискретного действия с входных выводов 2 и 3. С выхода регулирующего органа 1 через датчик Нулевого тока выходное напряжение поступает на выходные выводы 5 и 6, от10

нагрузки начала импульсов управления блока 10 привязаны к сигналам датчика k нулевого тока, поступающим с выхода датчика k на первый вход бло- 5 ка 9.

Стабилизация выходного напряжения производится по среднему его значению, взятому за каждые полпериода сетевого напряжения. При этом характеристикой выходного напряжения стабилизатора служит интеграл

Juwix(t)cl, (1)

. г определяемый в измерительном преобразователе 7 в конце полуволны выходного напряжения U6(t). В выражении ( wn коэффициент передачи измерительного преобразователя; Т - период сетевого напряжения.

В случае реактивной нагрузки nef.. - ключения вольтодобавочкых секций пс сигналам датчика нулевого тока приводят к скачкам выходного напряжения

25 (фиг. 2) при переходе его с одного дискретного уровня на другой.

Пренебрегая потерями в регулирующем органе и полагая

20

U8bllt (t)-k (t,(2)

куда выходное напряжение стабилизато- Зо где ue(t) - ,гзвое напряжение;

k(t) - .сэффициерт передачи регулирующего органа со стороны сетевого напряжения, на n-м шаге работы стабилизатора с

жением и током нагрузки дТ (фиг.2) имеют д

(t)«ft +

Т/2L О

40

(3)

ра подается в нагрузку, а т-тчже н вход измерительного преобразое- rerw 7 В последнем производится измерь е интегральной характеристики напряжанкя.

рпределяемой за каждые полпериода .л- учетом фазового сдвига между напря- тевого напряжения. Есл51 происходит JJ

отклонение уровня напряжения нагрузки от заданного значения, измерительный преобразователь 7 формирует пачки импульсов, поступающих на суммирующий или вычитающий вход реверсивного счетчика 8 в зависимости от знака отклонения. При этом число импульсов в каждой пачке пропорционально величине отклонения. Информация с реверсивного счетчика 8 поступает на блок 9 формирования управляющих импульсов, с которого управляющие импульсы подаются на управляющие электроды ключевых элементов регулирующего органа 1 дискретного действия. При изменении таким образом состояния реверсивного счетчика 8 происходит изменение уровня выходного напряжения стабилизатора Ё сторону уменьшения рассогласования. С целью исключения

+ (t)dt .

Пусть сетевое напряжение описывается гармонической функцией времени Uc(t)UCTsinwt,(4)

45 гДе и

и

ю- амплитудное значение и циклическая частота сетевого напряжения. Подставляя (k) в (3), получают

50

U«n n TwnUccpfc n 1-F(vH) + (vM)}, (5)

55

где VH A Cw;

Р(уи) (1-созун)/2;

U сер UCT/2f.

Рассогласование между измеренным и заданным значением U0 выходного напряжения на n-м шаге работы стабилизатора

коротких замыканий в контурах вольто- добавочных секций регулирующего органа 1 при активно-реактивном характере

нагрузки начала импульсов управления блока 10 привязаны к сигналам датчика k нулевого тока, поступающим с выхода датчика k на первый вход бло- ка 9.

Стабилизация выходного напряжения производится по среднему его значению, взятому за каждые полпериода сетевого напряжения. При этом характеристикой выходного напряжения стабилизатора служит интеграл

Juwix(t)cl, (1)

г определяемый в измерительном преобразователе 7 в конце полуволны выходного напряжения U6(t). В выражении ( wn коэффициент передачи измерительного преобразователя; Т - период сетевого напряжения.

В случае реактивной нагрузки nef.. - ключения вольтодобавочкых секций пс сигналам датчика нулевого тока приводят к скачкам выходного напряжения

5 (фиг. 2) при переходе его с одного дискретного уровня на другой.

Пренебрегая потерями в регулирующем органе и полагая

жением и током нагрузки дТ (фиг.2) имеют д

(t)«ft +

Т/2L О

учетом фазового сдвига между напря-

(3)

+ (t)dt .

Пусть сетевое напряжение описывается гармонической функцией времени Uc(t)UCTsinwt,(4)

гДе и

и

ю- амплитудное значение и циклическая частота сетевого напряжения. Подставляя (k) в (3), получают

50

U«n n TwnUccpfc n 1-F(vH) + (vM)}, (5)

где VH A Cw;

Р(уи) (1-созун)/2;

U сер UCT/2f.

Рассогласование между измеренным и заданным значением U0 выходного напряжения на n-м шаге работы стабилизатора

лиипГп1 1,пи0-ицпгп (6)

переводится измерительным преобразователем 7 в изменение состояния реверсивного счетчика 8

,(7)

где fpc коэффициент пропорциональности между рассогласованием в измерительном преобразователе и изменением сое- тояния реверсивного счетчика 8.

Состояние реверсивного счетчика на (п-Н)-м шаге

NpCOH NpC(;nl+dNpctn;), (8) В устройстве-прототипе выходная шина реверсивного сметчика подключена только к входной управляющей шине ре гулирующего органа дискретного действия через блок формирования управляющих импульсов. При этом коэффициент передачи регулирующего органа со стороны сетевого напряжения

k nJ ypoNpc nJ,(9)

где 1рр0- коэффициент передачи регулирующего органа со стороны входной управляющей шины, Подставляя в (8) выражения (5) и (7) и учитывая (9), имеют

ktn-H kUn 4- U0-yUccp k nKl-F(vH)J

(vM)} J

U

JbtK.Sp

(vh) +

(vH),

(10)

Графики переходных процессов ,, (фиг, 5) построены по уравнению (16).

35

Из сравления графиков фиг, и 5 видно, что при реактивном характере нагрузки предлагаемое устройство дает выигрыш по сравнению с устройством-прототипом

описывающее процессы стабилизации пе- 40 с точки зрения быстродействия процесса стабилизации переменного напряжения с

Измерительный преобразователь

где тг ТроТРсТмпПри чисто активной нагрузке, т„е, , Р(уи)0, разностное уравнение,

(11)

ременного напряжения, имеет вид ktn+1 k n +j.(uo-Ucc krn). Как показывают исследования, в этом случае быстродействие системы стабилизации переменного напряжения составляет 1-2 шага работы устройства, Графики (фиг. 3) построены как огибающие относительных значений интегралов выпрямленного напряжения, взя(фиг. 6) работает следующим образом. 45 Переменное напряжение нагрузки с

выходных зажимов подается на согласующий трансформатор 11, напряжение с вторичной обмотки которого поступает на вход прецизионного выпрямителя 12,

тых за каждые полпериода питающей се- 50 осуществляющего двухполупериодное

выпрямление напряжения. С выхода выти, при скачках сетевого напряжения5 изменяемого в пределах 120% от номинального значения U, при 1/иоо Графики переходных процессов (фиг. Ь) построены по уравнениям (10) - при VH 5fi712 и 73, и из нмх видно, что процесс стабилизации в устройстве-прототипе затягивается с ростом

V

прямителя 12 напряжение 53 поступает на вход интегратора 13 с ключом Н сброса, а также на инвертирующий вход компаратора 22, на неинвертирующий пход которого подается напряжение 5 источника 17 опорного напряжения. Прямоугольные импульсы 55 с компаратора 22 поступают на формирователь 23

ю1530

Записывают первое уравнение системы (10) s чиде

ktn+1 k(n +3 №0-Uck(n +

+UcF(«,-H)() .(12)

Уравнение (12) отличается от уравнения (11) наличием составляющей

.UcF()U n -ktn-1)s (13)

обуславливающей затягивание процесса стабилизации переменного напряжения в устройстве-прототипе пои активно- реа ктивном характере нагрузки.

Для повышения быстродействия стабилизатора в алгоритм стабилизации вводится составляющая

v n -j4J0F(4 H)(kCn-1 -kCn), (14)

определяемая в вычислительном блоке 10 так, что на (п+1)-м шаге работы стабилизатора двоичный код, записываемый с блока 10 в реверсивный счетчик 8 через входную двоичную шину перезаписи, соответствует выражению

k n+1 -Ti NpcCn+1 +fltn. (15) Таким образом, разностное уравнение описывающее процесс стабилизации переменного напряжения, имеет вид t

„-(-kCn

+F()(Ut-U0)(k nJ-kCn-1J)}. (16)

Графики переходных процессов ,, (фиг, 5) построены по уравнению (16).

20

25

35

Из сравления графиков фиг, и 5 видно, что при реактивном характере нагрузки предлагаемое устройство дает выигрыш по сравнению с устройством-прототипом

(фиг. 6) работает следующим образом. 45 Переменное напряжение нагрузки с

прямителя 12 напряжение 53 поступает на вход интегратора 13 с ключом Н сброса, а также на инвертирующий вход компаратора 22, на неинвертирующий пход которого подается напряжение 5 источника 17 опорного напряжения. Прямоугольные импульсы 55 с компаратора 22 поступают на формирователь 23

1

компаратор 21 выдает логический ль и счетчик 33 перестает считать. В результате по вычитающему входу реверсивного счетчика 33 проходит пачка / импульсов 63, число импульсов в которой пропорционально отклонению напряжения нагрузки от заданного значения. Аналогично происходит работа измерительного преобразователя в случае, когда напряжение нагрузки оказывается меньше нижнего допустимого уровня. При этом напряжение на выходе сумматора 18 имеет вид кривой 64. К началу

строб импульсов по переднему фронту и формирователь 2k строб импульсов по заднему фронту. Строб по переднему фронту, представляющий собой короткий импульс 56, поступает с формирователя 23 на элемент 25 задержки, откуда задержанный передний строб 57 поступает на вход идущего мультивибратора 27,

формирующего ПрЯМОуГОЛЬНЫе ИМПУЛЬСЫ jg

58, в течение которых производится отработка рассогласования в системе стабилизации. С помощью элемента 2И 32 производится формирование импульса 59

сброса интегратора 13, поступающего импУльса 58 отработки рассогласова- управляющий вход ключа 14 сброса ин- ния на выходе компаратора 20 оказывается логическая единица, и на суммирующий вход счетчика 33 проходят импульсы 65 генератора 19 через элемент ЗИ 29 до тех пор, пока напряжение 64 не сравняется с напряжением 66 источника 15 опорного напряжения.

Таким образом, измерительный преобразователь 7 формирует пачки импульсов на одном из двух выходов (1) и (2) в зависимости от знака отклонения напряжений нагрузки от заданного значения, причем число импульсов в пачке пропорционально этому отклонению.

Код опоры записывается в реверсиьгчи

го импульса 58 отработки рассогласования находится в пределах допустимой зоны, определяемой напряжениями источников 15 и 16 опорных напряжений, а также состоянием опорного кода, поступающего на входную шину перезаписи реверсивного счетчика 33 с датчика 28 опорного кода, то на выходах обоих компараторов 20 и 21 - логические нули, и реверсивный счетчик 33 в течение импульса Ь8 не изменяет своего состояния. Если напряжение нагрузки оказывается больше верхнего уровня допустимой зоны, то напряжение на выходе сумматора 18 имеет вид кривой б1.45 сом б7 Формирователя строб импульсов При этом к началу импульса 58 на выхо- по заднему фронту измерительного преде компаратора 21 оказывается логическая единица, и через элемент ЗИ 30 на

тегратора 13- Таким образом, на выходе интегратора 13 с ключом 14 сброса формируется напряжение 60, которое к началу очередного импульса 58 пропорционально интегралу напряжения нагрузки, взятого примерно за полпериода сетевого напряжения. Это напряжение 60 поступает на первый вход сумматора 18, на вторг вход которого заводится напряжение с цифроаналогово- го преобразователя 34, подключенного входной двоичной й к выходной двоичной шине реверсивного счетчика 33. Если напряжение 60 к моменту очередно зо

20

25

35

40

ный счетчик 33 передним стробом 56. Изменение кода опоры приводит к изменению уровня уставки стабилизатора. При этом датчик кода опоры может быть выполнен управляемым непосредственно от ЭВМ.

Вычислительный блок 10 (фиг.8) работает следующим образом, -,

К концу n-го интервала отработки рассогласования состояние реверсивного счетчика 8 изменяется в соответствии с выражением (8). Это новое состояние реверсисного счетчика 8 записывается в регистр 35 импульобразователя 7. С регистра 35 информация поступает на первую адресную шину постоянного запоминающего узла 39, на три другие адресные шины которого

вычитающии вход реверсивного счетчика 33 проходят импульсы генератора 19 импульсов. Состояние реверсивного счетчика 33 начинает изменяться так, что напряжение на выходе цифроанэпо- гового преобразователя 34 уменьшается. В результате напряжение 61 на выходе сумматора 18 также уменьшается до уровня напряжения 62, поступающего с источника 16 опорного напряжения. Как только эти напряжения сравняются,

3412

компаратор 21 выдает логический ль и счетчик 33 перестает считать. В результате по вычитающему входу реверсивного счетчика 33 проходит пачка / импульсов 63, число импульсов в которой пропорционально отклонению напряжения нагрузки от заданного значения. Аналогично происходит работа измерительного преобразователя в случае, когда напряжение нагрузки оказывается меньше нижнего допустимого уровня. При этом напряжение на выходе сумматора 18 имеет вид кривой 64. К началу

g

Код опоры записывается в реверсиь

сом б7 Формирователя строб импульсов по заднему фронту измерительного пре

ный счетчик 33 передним стробом 56. Изменение кода опоры приводит к изменению уровня уставки стабилизатора. При этом датчик кода опоры может быть выполнен управляемым непосредственно от ЭВМ.

Вычислительный блок 10 (фиг.8) работает следующим образом, -,

К концу n-го интервала отработки рассогласования состояние реверсивного счетчика 8 изменяется в соответствии с выражением (8). Это новое состояние реверсисного счетчика 8 записывается в регистр 35 импульсом б7 Формирователя строб импульсов по заднему фронту измерительного преобразователя 7. С регистра 35 информация поступает на первую адресную шину постоянного запоминающего узла 39, на три другие адресные шины которого

поступают выходной код состояния реверсивного счетчика 8 на (п-1)-м шаге с -выходной двоичной шины регистра 37, выходной код состояния реверсивного счетчика 8 на n-м шаге с

выходной двоичной шины регистра 36 и двоичный код, соответствующий величине относительного фазового сдвига напряжения и тока нагрузки НСП 3 на

13153

выходной двоичной шины регист

шаге с ра 38.

Постоянный запоминающий узел 39 запрограммирован для вычисления кода

N n+l Nfr-H -(NCn-l -N hJ) Т го (17)

в соответствии с алгоритмом (16) изменения коэффициента передачи регулирующего органа 1.

Код записывается из постоянного запоминающего узла 39 в реверсивный счетчик 8 задержанным задним стробом 68, поступающим с измерительного преобразователя 7.

Состояние реверсивного счетчика 8 переписывается в регистр 37 из регистра 36 передним стробом 56, а состояние реверсивного счетчика 8 записывается в регистр 36 задержанным передним стробом 57.

Формирование двоичного кода, соответствующего относительному фазовому сдвигу напряжения и тока нагрузки, осуществляется с помощью двоичного счетчика 40, генератора 41 импульсов и триггера 42. Обнуление счетчика 40 производится задним стробом 67} который поступает также на вход установки единицы триггера 42. При этом триггер 42 устанавливается в единичное состояние, производя запуск генератора 41 импульсов. Импульсы генератора 41 поступают на счетный вход двоичного счетчика 40, изменяя его состояние. По приходу строба тока с блока 9 формирования управляющих импульсов на вход установки нуля триггера 42 по следний переводится в нулевое состояние, производя срыв генерации импуль- сов генератора 41. Таким образом, на выходе двоичного счетчика 40 формируется двоичный код, соответствующий величине относительного фазового сдвига напряжения и тока нагрузки, который записывается в регистр 38 передним стробом 56.

Датчик 4 нулевого тока (фиг.9) построен на основе двух диодов 43 и 44, включенных встречно-параллельно в цепь нагрузки. Прямоугольные импульсы с этих диодов поступают на дифференцирующий трансформатор 45, с которого короткие импульсы проходят через двухполупериодный выпрямитель 46 и поступают на вход ждущего мультивибратора 47. Последний формирует импульсы 69, начала которых совпадают

U

5

0

0

с моментами перехода тока нагрузки через нулевое знамение.

Блок 9 формирования управляющих импульсов (фиг. 10) работает следующим образом.

На входы элемента 2И 48 поступают импульсы 69 датчика 4 нулевого тока и импульсы 70 измерительного преобразователя 7. В результате на выходе элемента 2И 48 формируются импульсы 71, поступающие на формирователь 49 строба. С выхода последнего импульсы

72поступают на вход ждущего мультивибратора 50, с выхода которого управляющие импульсы 73 тока идут через согласующие усилители блока 52 на управление ключами регулирующего органа 1 дискретного действия. При этом на один из входов согласующих усилителей поступает информация с реверсивного счетчика 8. Импульсы 70 используются в данном блоке для исключения возможного попадания начала импульса

73тока в интервал отработки рассогласования системой стабилизации. По переднему фронту импульса 73 тока формирователем 51 Формируется строб 74 тока, который поступает в вычислительный блок 10 для определения относительного фазового сдвига напряжения

и тока нагрузки. Все формирователи стробов в предлагаемом стабилизаторе могут быть реализованы на основе дифференцирующих цепочек и компараторов.

I

Регулирующий орган дискретного

действия выполняется на основе транс- форматорно-ключевой исполнительной структуры с коммутацией ключевых элементов в моменты прохождения тока нагрузки через нулевой уровень. При этом учет относительного фазового сдвига напряжения и тока нагрузки введением в алгоритм стабилизации составляющей (14), определяемой в вычислительном блоке, позволяет повы5

0

5

сить быстродействие системы стабилизации переменного напряжения. Выполнение измерительного преобразователя на основе предлагаемой структуры позволяет повысить точность стабилизации переменного напряжения в условиях искажения формы кривой сетевого напряжения, а также дает возможность изменять уро- вень установки стабилизатора путем изменения кода опоры, что позволяет управлять устройством непосредственно от ЭВМ.

Формула изобретения

Стабилизатор переменного напряжения, содержащий регулирующий орган дискретного действия, подключенный входом к входным выводам, а выходом через датчик нулевого тока - к выходным выводам, измерительный преобразователь, входом соединенный с выходны- ми выводами, первый реверсивный счетчик, блок формирования управляющих импульсов, подключенный входной двоичной шиной к выходной двоичной шине первого реверсивного счетчика, первым входом - к выходу датчика нулевого тока, а выходной шиной - к управляющей входной шине регулирующего органа дискретного действия, о т л и-ч а ю- щ и и с я тем, что, с целью повышени быстродействия при активно-реактивном характере нагрузки, в него введен вычислительный блок, соединенный входно двоичной шиной с выходной двоичной шиной первого реверсивного счетчика, а выходной двоичной шиной - с входной двоичной шиной перезаписи первого реверсивного счетчика, суммирующий, вычитающий и перезаписывающий входы которого подключены соответственно к первому, второму и третьему выходам измерительного преобразователя, четвертый, пятый и шестой выходы которого соединены соответственно с первым,

вторым и третьим входами вычислитель

ного блока, четвертым входом подключенного к выходу блока формирования управляющих импульсов, второй вход которого соединен с седьмым выходом измерительного преобразователя, при- чем вычислительный блок снабжен четырьмя регистрами, постоянным запоминающим узлом, двоичным счетчиком, первым генератором импульсов и триггером при этом входные двоичные шины первог и второго регистров соединены с входной двоичной шиной вычислительного блока ,а их перезаписывающие входы подключены соответственно к третьему и второму входам вычислительного блока,третий регистр подключен входной двоичной шиной к выходной двоичной шине второго регистра, а перезаписывающим входом - к первому входу вычислительного блока, к которому подключен такме перезаписывающий вход четвертого регистра, постоянный запоминающий узел соединен первой, второй, третьей и четвертом адресными шинами с выходныз 5 0

5

о

ми двоичными шинами соответственно первого, второго, третьего и четвертого регистров, а выходной двоичной шиной - с выходной двоичной шиной вычислительного блока, причем постоянный запоминающий узел запрограммиро- ван-для вычисления кода

Nln+i N n+i +Z Ntn-i «V

, где Ntn+1, NCn,

Ntn-1 - коды, формируемые

соответственно первым, вторым и третьим регистрами; VH Сп К°Д Формируемый четвертым регистром;

F(v4) (1-cosvH)/2; Т Ifpo Tpc Тип

j-po - коэффициент передачи регулирующего органа со СТОРОНЫ входной управляющей шины;

ТРС коэФФиЦиент пропорциональности между рассогласованием в измерительном преобразователе и изменением состояния первого реверсивного счетчика; v - коэффициент передачи измерительного преобразователя; U0 - заданное значение выходного напряжения;

п - шаг работы стабилизатора,

двоичный счетчик подключен выходной двоичной шиной к входной двоичной шине четвертого регистра, входом обнуления - к третьему входу вычислительного блока, а счетным входом - к выходу первого генератора импульсов, вход запуска которого соединен с выходом триггера, вход установки логической единицы которого подключен к третьему, а вход установки нуля - к четвертому входам вычислительного блока, при этом измерительный преобразователь состоит из последовательно соединенных согласующего трансформатора, входной обмоткой подключенного к входу измерительного преобразователя, прецизионного выпрямителя и интегратора с ключом

17153

сброса, сумматора, подключенного первым входом к выходу интегратора с ключом сброса, трех источников опорного напряжения, второго генератора импульсов, первого компаратора, соединенного неинвертирующим входом с выходом первого источника опорного напряжения, а инвертирующим входом - с выходом сумматора, второго компаратора, сое- диненного неинвертирующим входом с выходом сумматора, а инвертирующим входом - с выходом второго источника опорного напряжения, третьего компаратора, подключенного инвертирующим входом к выходу прецизионного выпрямителя, а неинвертирующим входом - к выходу третьего источника опорного напряжения, формирователей строб импульсов по переднему и заднему фронту, соединенных входами с выходом третьего компаратора, первого элемента задержки, соединенного входом с выходом формирователя строб импульсов по переднему фронту и четвертым выходом измерительного преобразователя, второго элемента задержки, подключенного входом к выходу формирователя строб импульсов по заднему фронту и шестому выходу измерительного преобразователя, а выходом - к третьему выходу измерительного преобразователя, первого ждущего мультивибратора, подключенного входом к выходу первого элемента задержки и к пятому выходу измерительного Преобразователя, датчика опорного кода, первого элемента ЗИ, подключенного первым входом к выходу второго генератора импульсов, вторым входом - к выходу первого компаратора, a третьим входом - к выходу первого ждущего мультивибратора, второго элемента ЗИ, подключенного первым входом к выходу второго генератора импульсов, вторым входом - к выходу второго ком

0 5 0 Q

О

паратора, а третьим входом - к выходу первого ждущего мультивибратора, элемента НЕ, соединенного входом с выходом первого ждущего мультивибратора, первого элемента 2И, соединенного первым входом с выходом элемента НЕ и седьмым выходом измерительного преобразователя, вторым входом - с выходом третьего компаратора, а выходом - с управляющим входом ключа сброса интегратора, второго реверсивного счетчика, соединенного входной двоичной шиной перезаписи с выходной двоичной шиной датчика опорного кода, перезаписывающим входом - с выходом формирователя строб импульсов по переднему фронту, суммирующим входом - с выходом первого элемента ЗИ и первым выходом измерительного преобразователя, а вычитающим входом - с выходом второго элемента ЗИ и вторым выходом измерительного преобразователя, цифро- аналогового преобразователя, подклю - ченного входной двоичной шиной к выходной двоичной шине второго реверсивного счетчика, а выходом - к второму входу сумматора, крюме того, блок формирования управляющих импульсов выполнен в виде последовательно соединенных второго элемента 2И, формирователя строба, второго ждущего мультивибратора и формирователя строба тока, а также блока согласующих усилителей, первая группа входов которого соединена с выходом второго ждущего мультивибратора, вторая группа входов - с входной двоичной шиной, а выходы - с выходной шиной блока формирования управляющих импульсов, при этом первый и второй входы второго элемента 2И и выход формирователя строба тока соединены соответственно с первым и вторым входами и выходом блока формирования управляющих импульсов.

r -3- r f-

+и

(91

92

а5

г№пЯ

«

пл

«t

-а.

л

/t. sr

сс

ЙГ

г

«

&

А

tf

г

s ifjbli. nfl n

UJflJ i-r fi

Si

92

as

ss

95

/i

Si

X

И

Ж

Ј

V

-r H

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического контроля параметров интегральных схем | 1988 |

|

SU1649474A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| КАЛИБРОВОЧНОЕ УСТРОЙСТВО ДЛЯ УЛЬТРАЗВУКОВОГО РАСХОДОМЕРА | 1995 |

|

RU2082951C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2005 |

|

RU2279093C1 |

| Устройство для регулирования компенсатора реактивной мощности | 1986 |

|

SU1372466A1 |

| Адаптивный измерительный преобразователь | 1975 |

|

SU551507A1 |

| Устройство для определения моментов экстремумов гармонических сигналов | 1981 |

|

SU1004899A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942091A1 |

| Трехфазный стабилизатор переменного напряжения | 1987 |

|

SU1436105A1 |

| Устройство для измерения давления | 1988 |

|

SU1569610A1 |

Изобретение относится к электротехнике и может быть использовано в качестве вторичного источника питания. Целью изобретения является повышение быстродействия при активно-реактивном характере нагрузки. Цель достигается путем введения в алгоритм стабилизации составляющей, компенсирующей затягивание процесса стабилизации. Эта составляющая определяется в вычислительном блоке 10 и зависит от величины относительного фазового сдвига напряжения и тока нагрузки. В измерительном преобразователе 7 (ИП) производится измерение интегральной характеристики выходного напряжения. При отклонении уровня выходного напряжения от заданного значения ИП 7 формирует пачки импульсов, поступающих на суммирующий или вычитающий вход реверсивного счетчика (РС) 8 в зависимости от знака отклонения. При этом число импульсов в каждой пачке пропорционально величине отклонения. Информация с РС 8 поступает на блок 9 формирования управляющих импульсов, с которого управляющие импульсы подаются на управляющие электроды ключевых элементов регулирующего органа (РО) 1 дискретного действия. Коммутация ключевых элементов РО 1 осуществляется в моменты прохождения тока нагрузки через нулевой уровень, благодаря наличию в схеме стабилизатора датчика 4 нулевого тока. 10 ил.

5

I

+-h

+11/и нА.

с/вчЫ лаЪъ л

нА.

лаЪъ л

Ј/х--мл:олМ--: п ы/хЈ %:9лгЪ Ъ

Wi№i

«э «О

Ф

Т

5

Фиг. 10

| Стабилизатор переменного напряжения | 1984 |

|

SU1180858A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР IP , кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ( СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | |||

Авторы

Даты

1990-01-07—Публикация

1988-02-05—Подача