нен с первым выходом логического блока, а выход - с первым входом девятого ключа, второй вход которого соединен с выходом седьмого ключа, а выход - с выходом первого ключевого элемента, при этом второй выход логического блока соединен с первым входом десятого ключа, второй вход которого соединен с информационным входом второго ключевого элемента и с первым входом одиннадцатого ключа.

второй вход которого соединен с выходом второго элемента ИЛИ, а выход с первым входом двенадцатого ключа, второй вход которого соединен с выходом десятого ключа, а выход - с ; выходом второго ключевого элемента, а управляющие входы девятого и двенадцатого ключей соединены с соответствукнцими управляющими выходами задатчика длительности цикла измерения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1267272A1 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1285392A1 |

| Устройство для измерения сдвига фаз инфранизкочастотных сигналов | 1976 |

|

SU600474A1 |

| Цифровой интегрирующий вольтметр | 1981 |

|

SU974287A1 |

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| Стробоскопический преобразователь | 1990 |

|

SU1721522A1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

| Измерительное устройство к балансировочному станку | 1985 |

|

SU1320670A1 |

| Измерительное устройство станка для балансировки коленчатых валов | 1986 |

|

SU1366893A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СКОРОСТИ ГАЗОВОЗДУШНОГО ПОТОКА | 2008 |

|

RU2390028C1 |

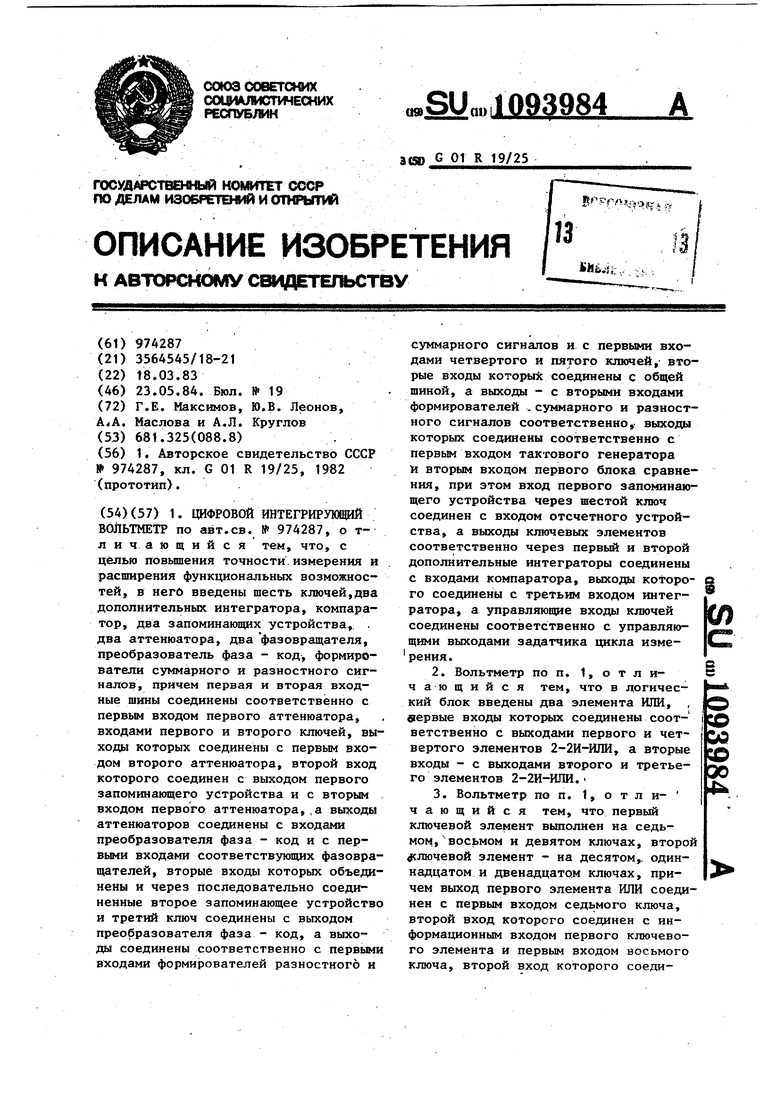

1. ЦИФРОВОЙ ИНТЕГРИРУКЩШ ВОЛЬТМЕТР по авт.св. № 974287, о тли чающийся тем, что, с целью повышения точности.измерения и расширения функциональных возможностей, в него введены шесть ключей,два дополнительных интегратора, компаратор, два запоминающих устройства, два аттенюатора, два фазовращателя, преобразователь фаза - код, формирователи суммарного и разностного сигналов, причем первая и вторая входные шины соединены соответственно с первьм входом первого аттенюатора, входами первого и второго ключей, выходы которых соединены с первым входом второго аттенюатора, второй вход которого соединен с выходом первого запоминающего устройства и с вторым входом первого аттенюатора,,а выходы аттенюаторов соединены с входами преобразователя фаза - код и с первыми входами соответствующих фазовращателей, вторые входы которых объединены и через последовательно соединенные второе запоминающее устройство и третий ключ соединены с выходом преобразователя фаза - код, а выходы соединены соответственно с первыми входами форми зователей разностного и суммарного сигналов и с первьо и входами четвертого и пятого ключей, вторые входы которых соединены с общей шиной, а выходы - с вторыми входами формирователей . суммарного и разностного сигналов соответственно,- выходы которых соединены соответственно с первьм входом тактового генератора И вторым входом первого блока сравнения, при этом вход первого запоминающего устройства через шестой ключ соединен с входом отсчетногр устройства, а выходы ключевых элементов соответственно через первый и второй дополнительные интеграторы соединены с входами компаратора, выходы которого соединены с третьим входом интегратора, а управляющие входы ключей соединены соответственно с управляющими выходами задатчика цикла измерения . 2.Вольтметр по п. 1, о т л ичающийся тем, что в логический блок введены два элемента ИЛИ, первые входы которых соединены соот:о ветственно с выходами первого и четDO вертого элементов 2-2И-ИЛИ, а вторые входы - с выходами второго и третьеэо го элементов 2-2И-ИЛИ. 4 3.Вольтметр по п. 1, о т л ичающийся тем, что первый ключевой элемент выполнен на седьмом, восьмом и девятом ключах, второй ключевой элемент - на десятом,, одиннадцатом и двенадцатом ключах, причем выход первого элемента ИЛИ соединен с первым входом седьмого ключа, второй вход которого соединен с информационным входом первого ключевого элемента и первым входом восьмого ключа, второй вход которого соеди

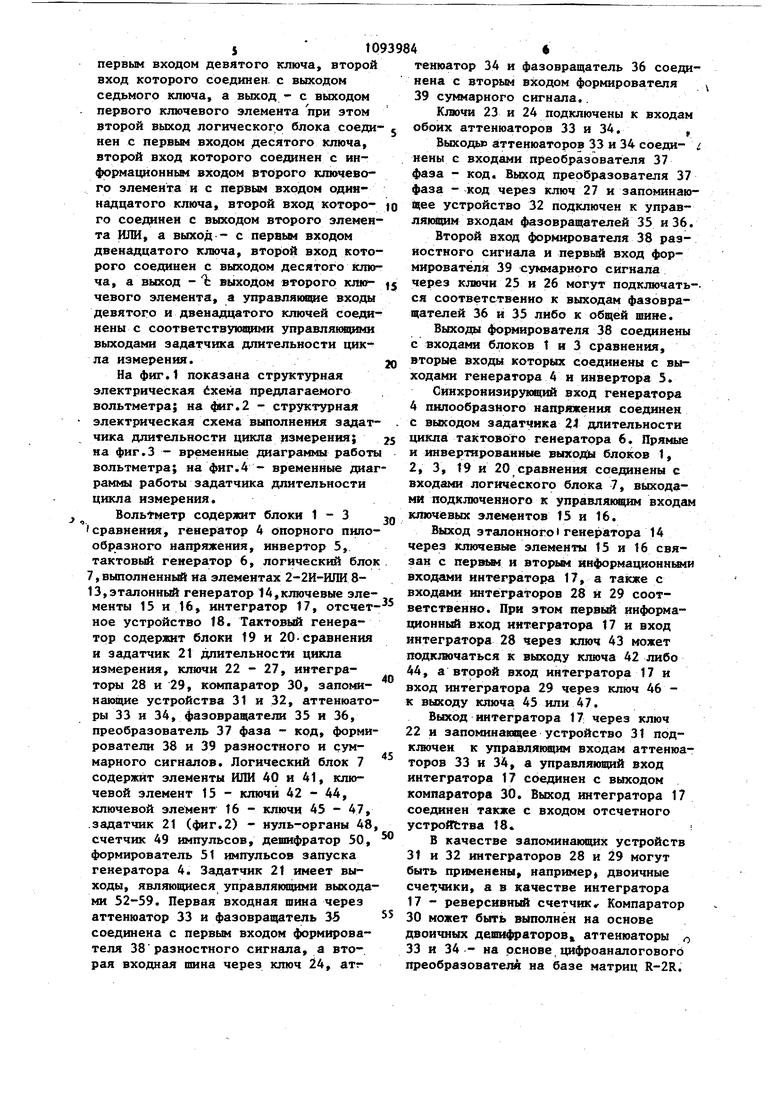

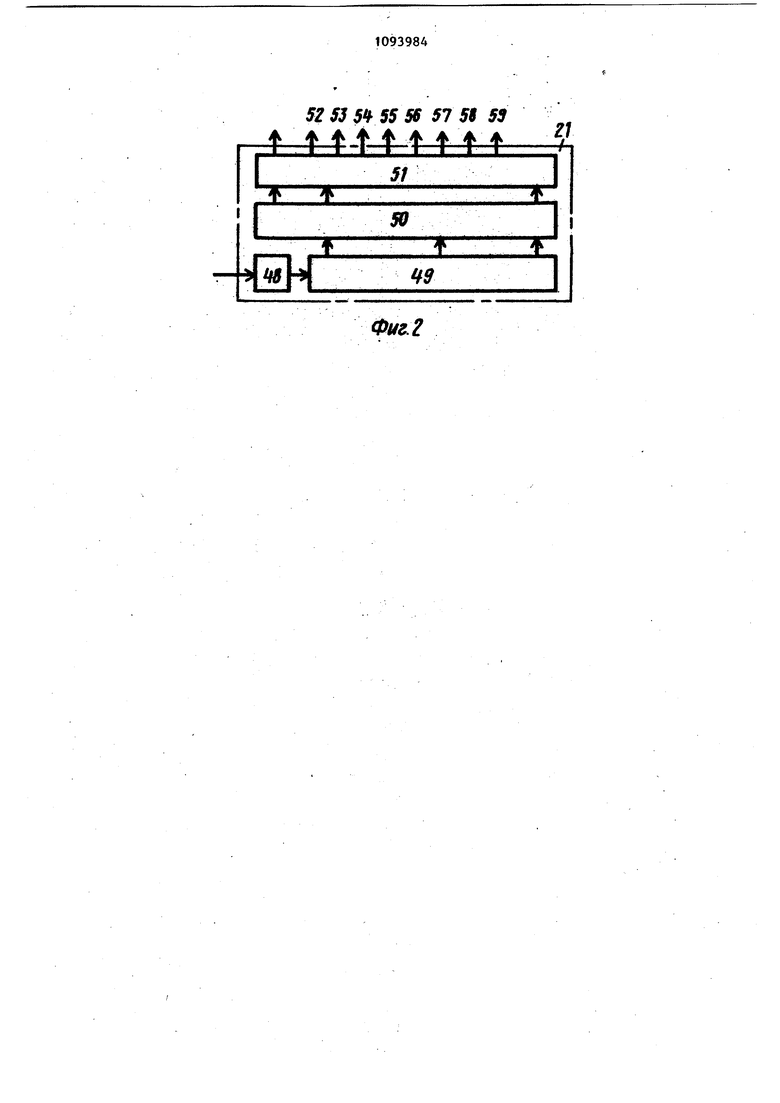

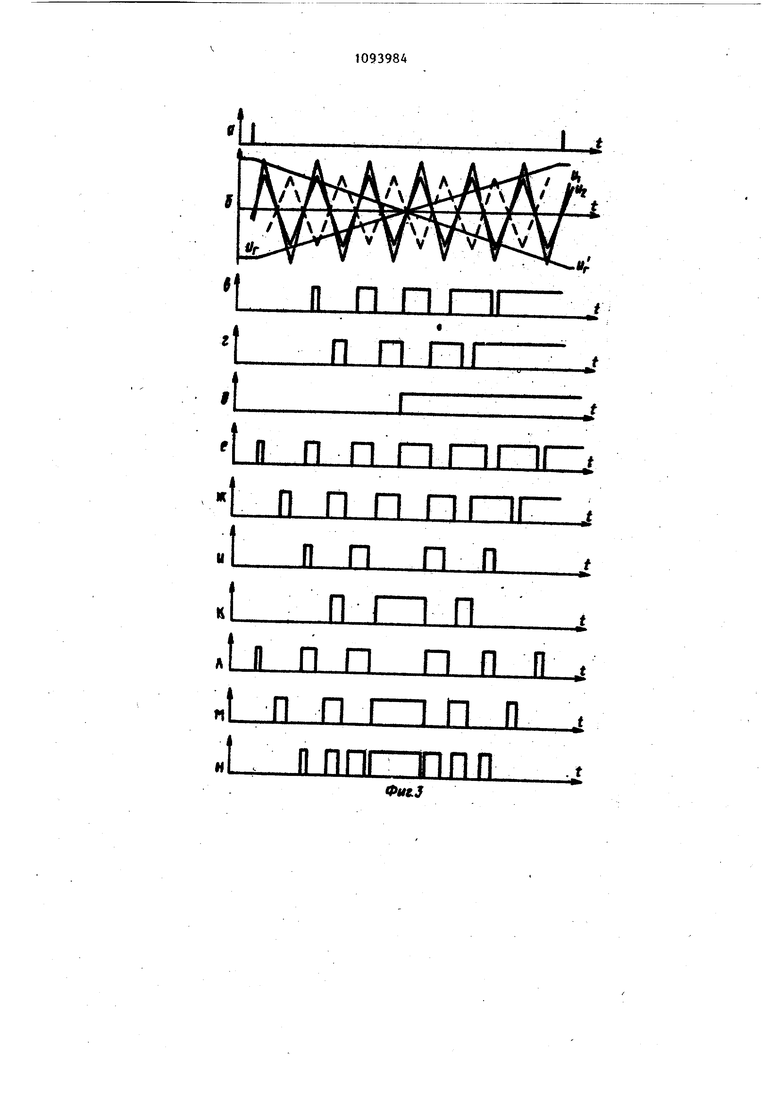

Изобретение относится к электроизмерительной технике и предназначено для измерения среднего значения переменных напряжений производной формы. По основному автТсв. IP 974287 известен цифровой интегрирукидий воль метр, содержащий тактовьй генератор, выполненный на датчике длительности цикла измерения, вход которого сое.динен с первьм входом тактового генератора, подключенного к шине опорного напряжения, а выход - с первым выходом тактового генератора, подключенным к входу генератора опорного пилообразного напряжения, выход которого соединен с первым входом первого блока сравнения, второй вход . которого соединен с шиной входного сигнала, а прямой и инверсный выходы которого соединены соответственно с первьо4 и вторьв4 входами логического блокад выполненного на элементе 2-2И-ИЛИ, первые, вторые, третьи и инверсные входы которого соединены Iсоответственно с перВ1Л И вторыми, третьими и инверсными входами логического блока, первый выход которого соединен с управляющим входом ключевого элемента, информационный вход которого соединен с выходом эталонного генератора, а выход - с первым входом интегратора,. выход которого соединен с отсчетиьш устройством, инвер тор, второй и третий блоки сравнения второй ключевой элемент, а тактовый генератор содержит четвертые и пятые блоки сравнения, логический блок содержит вторс, третий, четвертый. пятый и шестой элементы 2-2И-ШТИ, первый и второй входы второго элемента 2-2И-ШШ соединены соответственно с пятым и шестьм входами логического блока, первый и второй входы третьего элемента 2-2И-ИПИ - соответственно с седьмым и восьмым входами логического блока, а первьй и второй входы четвертого элемента 2-2И-ИЛИ соответственно с девятыми десятым входами логического блока, третьи входы второго, третьего и четвертого элементов 2-2И-ИЛИ соединены с третьим входом логического бхюка, а их четвертые входы - с четвертым входом логического блока, причем выходы первого элемента 2-2И-ИЛИ соединены с первыми вxoдa Ql пятого и шестого элемента 2-2И-ИЛИ, при этом выход второго элемента 2-2И-ИЛИ соединен с вторыми входами пятого и шестого элементов 2-2И-ИЛИ, выход третьего элемента 2-2И-ИЛИ - с третьим входом пятого и четвертым входом шестого элементов 2-2И-ИЛИ, выход четвертого элемента 2-2И-ИШ - с четверть входом пятого элемента 2-2И-ШШ подключенного к первому выходу логического блока, и третьим входом шестого элемента 2И-ШШ, выход которого соединен с вторым выход рм логического блока, подключенного к управляющему входу второго ключевого элемента информационньй вход которого соединен с выходом эталонного генератора, а выход - с ВТО1ШМ входом интегратора, при этом первый вход второго блока сравнения соединен непосредственно с выходом генератора опорного пилообразного напряжения и входом инвертора, а второй вход - с выходом инвертора и первым входом третьего блока сравнения, а прямой и инверсный выходы второго блока сравнения соединены соответственно с третьим и четвертым входами логического блока, пятый и шестой выходы которого соединены соответственно с прямым и инверсным выходами третьего блока сравнения, второй вход которого соединен с шиной входного напряжения, причем вторые прямой и инверсный выходы тактового генератора соединены 1с седьмьсм и восьмьм входами логического блока, третий прямой и инверсны выходы тактового генератора соеданены с девятым и десятым входами логического блока, кроме того, первые входы четвертого и пятого блоков сравнения соединены с входом тактового генератора, второй вход инверсного блока сравнения - с вторы входом тактового генератора, подключенного к выходу генератора пилообразного опорного напряжения, а второ вход пятого блока сравнения - к третьему входу тактового генератора, подключенного к выходу инвертора, прямой и инверсный выходы четвертого блока сравнения соединены соответственно с вторыми прямым и инверсным выходами тактового генератора, а пря мой и инверсный выходы пятого блока сравнения - с третьими прямым и инверсньм выходами тактового генератора СП. Недостатком известного вольтметра является то, что возможность его применения в информационно-измерительных системах ограничивается возрастанием погрешности измерения при отклонении фазового сдвига между измеряемым и опорным напряжением от значений О или 7. Кроме того, зачастую возникает не обходимость в измерении дифференциальной составляющей (разности) двух входных напряжений, что не обеспечивает известное устройство-. Цель изобретения - повышение точности измерения и расширение функщю напьных возможностей. Цель достигается тем, что в цифро вой интегрирующий вольтметр введены шесть ключей, два дополнительных ин-чггратора, компаратор, два запоминаю щих устройства,, два аттенюатора, два фазовращателя, преобразователь фаза код, формирователи суммарного и разностного сигналов, причем первая и вторая входные шины соединены соответственно с первьм входом первого аттенюатора, входами первого и второго ключей, выходы которых соединены с первым входом второго аттенюатора, второй вход которого соединен с выходом первого запоминающего устройства и с вторым входом первого аттенюатора, а вькоды аттенюаторов соединены с входами преобразователя фаза код и с первыми входами соответствующих фазовращателей, вторые входы которых объединены и через последовательно соединенные второе запоминающее устройство и третий ключ соединены с выходом преобразователя фаза код, а выходы соединены соответственно с первыми входами формирователей разностного и суммарного сигналЬв и с первыми входами четвертого и пятого ключей,, вторые входы которых соединены с общей шиной, а выходы с вторыми входами формирователей сум-, марного и разностного сигналов соответственно, выходы которых соединены соответственно с первым входом тактового генератора и вторым входом первого блока сравнения, при этом вход первого запоминающего устройства через шестой ключ соединен с входом отсчетного устройства, а выходы ключевых элементов соответственно через первый и второй дополнительные интеграторы соединены с входами компаратора, которого соединены с третьим входом интегратора, а управляющие входы ключей соединены соответственно к управляющими выходами задатчшса цикла измерения. В логический блок введены два элемента ИЛИ, первые входы которых соединены соответственно с выходами первого и четвертого элементов 2- 2И-ИЛИ, а вторые входы - с выходами второго и третьего элементов 2-2И-ИЛИ. Кроме того, первый ключевой элемент выполнен на седьмом, восьмом и девятом ключах, а второй ключевой элемент на десятом, одиннадцатом и двенадцатом ключах, причем выход первого элемента ИЛИ соединен с первым входом седьмого ключа, второй вход которого соединен с информационным входом первого ключевого элемента и первым входом восьмого ключа, второй вход которого соединен с первым выходом логического блока, а выход - с . первым входом девятого ключа, второй вход которого соединен, с выходом седьмого ключа, а выход с выходом первого ключевого элемента при этом второй выход логического блока соеди ней с первю4 входом десятого ключа, второй вход которого соединен с информационным входом второго ключевого элемента и с первым входом одия надцатого ключа, второй вход кото| ого соединен с выходом второго элемен та ИЛИ, а выход - с первым входом двенадцатого клоча, второй вход кото рого соедщнен с выходом десятого клю ча, а выход -Ъ выходом второго клнгчевого элемента, а управляющие входы девятого и двенадцатого ключей соедщ нены с соответствукящми управлякя ими выходами задатчика длительности цикла измерения. На фиг.1 показана структурная электрическая бхема предлагаемого вольтметра; на - стрзгктурная электрическая схема выполнения задат чика длительности цикла измерения; на фиг.З - временные диаграммы работы вольтметра; на фиг.4 - временные диаг раммы работы задатчика длительности цикла измерения. содержит блоки 1-3 сравнениЕЯ, генератор 4 опорного пилообразного напряжения, инвертор 5, тактовый генератор 6, логический блок 7, выполненный на элементах 2-2И-ИШ 813,эталонный генератор 14,ключевые элементы 15 и 16, интегратор 17, отсчет ное устройство 18. Тактовый генератор содержит блоки 19 и 20-сравнения и задатчик 21 длительности цикла измерения, ключи 22 - 27, интеграторы 28 и 29, компаратор 30, запоминакнцие устройства 31 и 32, аттенюато ры 33 и 34, фазовращатели 35 и 36, преобразователь 37 фаза - код форми роватехш 38 и 39 разностного и суммарного сигналов. Логический блок 7 содержит элементы ИЛИ 40 и 41, ключевой элемент 15 - ключи 42 - 44, ключевой элемент 16 - ключи 45 - 47, .задатчик 21 (фиг.2) - нуль-органы 48 счетчик 49 импульсов, дешифратор 50, формирователь 51 импульсов запуска генератора 4. Задатчик 21 имеет выходы, являющиеся управляющими выхода ми 52-59. Первая входная шина через аттенюатор 33 и фазовращатель 35 соединена с первым входом формирователя 38разностного сигнала, а вторая входная шина через ключ 24, атг тенюатор 34 и фазовращатель 36 соединена с вторым входом формирователя 39 суммарного сигнала.. Ключи 23 и 24 подключены к входам обоих аттенюаторов 33 и 34. , Выходыз а:ттенюаторов 33 и 34 соединены с входами преобразователя 37 фаза - код. Вьрсод преобразователя 37 фаза - код через ключ 27 и запоминаюй(ее устройство 32 подключен к управлякицим входам фазовращателей 35 и 36. Второй вход формирователя 38 разностного сигнала и первый вход формирователя 39 суммарного сигнала через ключи 25 и 26 могут подключать-ся соответственно к выходам фазовращателей 36 и 35 либо к общей шине. Выходы формирователя 38 соединены с входами блоков 1 и 3 сравнения, вторые входы которых соединены с выходами генератора 4 и инвертора 5. Синхронизирующий вход генератора 4 пилообразного напряжения соединен с выходом задатчика 24 длительности цикла тактового генератора 6. Прямые и инвертированные выхо блоков 1, 2, 3, 19 и 20 сравнения соединены с вxoдa ш логического блока 7, выходами подключенного к управляющим входам Kim4ieBUx элементов 15 и 16. Выход эталонного) генератора 14 через клхучевые элементы 15 и 16 связан с перШ| м и вторьт информационными входами интегратора 17, а также с входами интеграторов 28 и 29 соответственно. При этом первый информационный вход интегратора 17 и вход интегратора 28 через ключ 43 может подключаться к выходу ключа 42 либо 44, а второй вход интегратора 17 и вход интегратора 29 через ключ 46 к выходу ключа 45 или 47. Выход интегратора 17 через ключ 22 и запоминающее устройство 31 подключен к управляшщм входам аттенюаторов 33 и 34, а управляющий вход интегратора 17 соединен с выходом компаратора 30. Выход интегратора 17 соединен также с входом отсчетного устройЬтва 18. В качестве запоминакяцих устройств 31 и 32 интеграторов 28 и 29 могут быть применены, например двоичные сче1;чики, а в качестве интегратора 17 - реверсивнь счетчик.- Компаратор 30 может быть выполнен на основе двоичных дешифраторовt аттенюаторы о 33 и 34 - на р.снове цифроаналоговогЬ преобразователя на базе матриц R-2R.

В качестве преобразователя фаза код 37 могут быть применены измерители интервалов времени между переходами через нуль входных сигналов, применяемых в цифровых фазометрах

Фазовраща;тели 35 и 36 могут быть выполнены, например, по мостовым схемам, в качестве одного из плеч которых используется преобразо1ватель код - сопротивление.

Вольтметр может работать в следую1ЩХ режимах: режиме автоматической коррекции неидентичности амплитуднофазовых характеристик каналов; режим автоматической компенсации фазового сдвига между входными сигналами.; режиме измерения дифференциальной составляющей входных напряжений.

Управление указанными режимами осуществляется с помощью ключей 22, 23, 24, 25, 26, 43 и 46. При этом возможность работы в каждом из перечисленных режимов осзпдествляется соответствующей комбинацией напряжений, подаваемых на управляющие входы ключей от задатчика 21 и обеспечивающих необходимое их состояние по заданной программе.

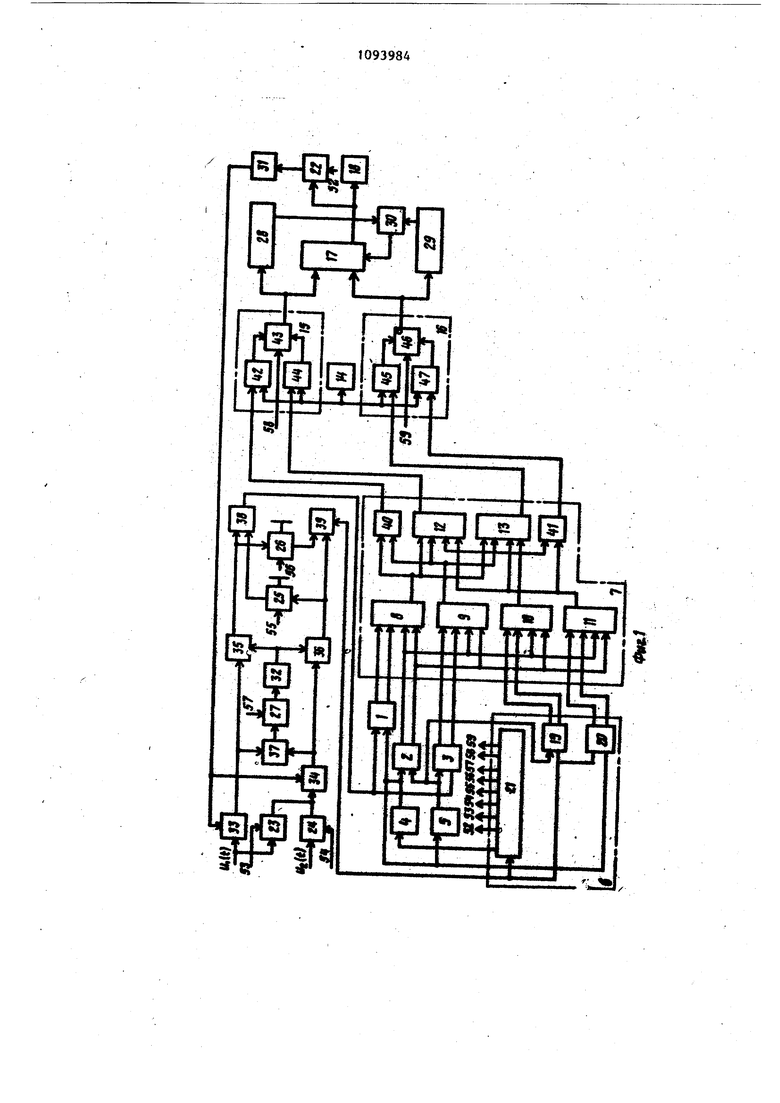

На фиг.З наличие положительного напряжения на вйходах 52 - 59 соответствует открытому состоянию ключей 22 - 27 и образованию связи между входом ключа,42 и входом интеграторо 17 и 28 через ключ 43, и выходом ключа 47 с входами интеграторов 17 и 29 через ключ 46.

При отсутствии напряжения на выходах 52 - 59 задатчика 21 ключи 22 - 27 закрыты, разрьгааются связи между выходом ключа 42 и входами интеграторов 17 и 28, а также выходом ключа 47 с входом интеграторов 17 и 29,.. при том образуются связи между выходом ключа 44 с входами интегра- торов 17 и 28 через ключ 42- и выходом ключа 45 с входами интеграторов 17 и 29 через ключ 46. Йервый из указанных режимов является вспомогательным, осуществляющим автоматическую коррекцию неидентичности коэффициентов передачи трактов вход аттенюатора 33 - выход ключевого элемента 15 и вход аттенюатора 34 - выход ключевого элемента 16, а также автоматическую коррекцию неидентичности фазовых характеристик входных трактов устройства. Зо втором режиме осуществляется, автоматическая компенсация фазового

сдвига между входными сигналами. Данный режим также является вспомогательньм, обеспечивающим повьщ1ение точности измерения- среднего значения

дифференциальной составляющей входных напряжений. Однако в этом режиме устройство с учетом несущественных изменений может быть использовано как двухканальный вольтметр, позволяющий измерять средние значения входных напряжений, их да{фференциальную составлякщую, а также фазовый сдвиг между входными напряжениями. Указанные измерения могут осуществ- ,

ляться поочередно либо при необходимости и при соответствующем выполнении отсчетного устройства - одновременно.

Третий режим с учетом коррекций

амплитудно-фазовых характеристик, осуществленных в.трех предыдущих режимах, обеспечивает повыщенную точность и помехоустойчивость измерения дифференциальной составляющей входных

сигналов.

Первые гармоники сигналов, дифференциальная составляющая которых подлежит измерению, имеет вид:

и (t) V sintot(1)

30

Uj (t) V2 sinCujt + V)(2)

r/jte V и V - амплитудные значения сигналов U (t) и

35 Uj (t) соответственно; Ч - относительный фазовый сдвиг между сигналами;

- круговая частота. В режиме коррекции амплитудно-фа40зовой неидентичности каналов источник сигнала U (t) поступает на вход аттенюатора 33 и через ключ 23 - на вход аттенюатора 34. Режим коррекции амплитудно-фазовых характеристик каналов осуществляется в два этапа. Перед выполнением первого этапа второй вход формирователя 38 и первый выход формирователя 39 через ключи 25 и 26 подключены к общей шине, первьй- вход интегратора 17 и вход интегратора 28 через ключ 43 соединен с выходом ключа 42, а второй вход интегратора 17 и вход интегратора 29 через ключ 46 подключен к выходу ключа 47. Ключи 22, 27 и 24 разомкнуЕсли считать, что в исходном состоянии фазовращатели 35 и 36 не внесят фазового сдвига в сигналы, проходящие через них, коэффициенты передачи фазовращателей 35 и 36 и формирователей 38 и 39 равны единице, а цифровые коды на выходе запоминающих устройств 31 и 32 равны нулю, то сигналы на входах преобразователя 37 фаза - код и на выходах формирова телей 38 и 39 имеют вид: K V sintut (3) (t) (t) ) .sin() AV - фазовая нечцентичность вхо ных трактов; К К+К N-коэффициент передачи аттенюатора 33; K.K..-IOJ - коэффициент передачи аттенюатора 34; коэффициент передачи аттенюатора при N 0; коэффициент пропорциональности; - цифровой код на выходе запоминающего устройства 31 после коррекции амплитудно-фазовых характеристик каналов; N и N - цифровые коды, вводимые в запоминающее устройство 31 после первого.и второго этапов коррекции соответст венно. Коэффициенты передачи К и К2, за висящие от KQ и Ку, первоначально вы бираются исходя из динамического диапазона входных сигналрв и обеспечения линейного режима каскадов устройства. Цикл измерения задается тактовым генератором 6, выполненным на задатчике 21 длительности цикла, на выходе которого образуются импульсы запуска (фиг.За) генератора 4 опорного пилообразного напряжения.. Прямое опорное пилообразное напряжение V подается на входы блоков 1, 2 и 20 сравнения, а инвертированное v} (фиг.Зб). - на входы блоков 2,3 19 сравнения. Напряжение (3) подается на сигнал ные входы блоков 1 и 3 сравнения, а напряжение (4) - через первый вход тактового генератора бс на вторые вхо ды блоков 19 и 20 и синхронизирующий вход задатчика 21.. Для данного режима работы напряжению (3) соответ10 (4) 4 36), а напряствует сигнал V v-jnyci 1.П1 ncui v жению (4) - сигнал V2; в данном случае фазовый сдвиг роли не играет и равен нулю (фиг.Зб). На прямых и инверсньк выходах блдков 1, 3,о19 и 20 сравнения образуются прямоугольные импульсы, когда напряжения U(t), ) больше или меньше значения пилообразного напряжения. На фиг.Зв, г показаны напряжения на прямых выходах блоков 1 и 3, а на фиг. Зе, ж - на прямых выходах блоков Т9 и 20 соответственно. Блок 2 из прямого и инвертирован- . ногр пилообразного напряжений формирует прямоугольные импульсы (фиг.Зд). Сигналы с выходов блоков 1, 2, 3, 19 и 20 поступают на входы элементов 8, 9, 1C и 11, в результате чего вы- . ходное напряжение элемента 8 имеет вид, показанный на фиг.Зи, элемента 9 - на фиг.Зк, элемента 10 - на фиг. 2л, элемента 11 - на фиг. 3м. Напряжения, показанные на фиг.Зи,к через элемент ИЛИ 40 воздействуют на управляющий вход ключа 42, а сигналы, показанные на фиг. 3л, м, через элемент ИЛИ 41 - на управляющий вход ключа 47. При этом выход эталонного генератора 14 через ключи 42 и 43 подключается к первому входу интегратора 17 и к входу интегратора 28, а через ключи 47 и 46 к второму входу интегратора 17 и к входу интеграторе 29. В результате интеграторы 28 и 29 зафиксируют, соответственно, числа: ,; ,, а на выходе интегратора 17 получим цифровой отсчет N. V(K - К) (7) причем знак числа N- определяется выход(((1м сигналом Компаратора 30 в зависимости от того какое из чисел (N или N-) больше. 1ерез замкнутый ключ 22 код вводится в запоминающее устройство 31, воздействуя на аттенюаторы 33 и 34, так, что N. tuN 2АК KV, (8) где N - цифровой отсчет на выходе интегратора 1, обусловленный погрешностью коррекции неидентичности коэффициентов передачи трактов ЛК. Пределом точности коррекции в данном случае является приращение напряжения выходе формирователей 38 и 39, приходящееся на шаг. квантования. I Если считать, что приращение коэф фициентов передачи 4К аттенюаторов 33 и 34, определяемое, например, количеством разрядов матрицы R-2R, может быть выбрано достаточно малым, а частота тактовых импульсов эталонного генератора 14 выбрана исходя из быстродействия элементной базы, на которой выполнен вольтметр,то точность коррекции определяется, главйым образом, уровнем сигналов, на вы ходе формирователей 38 и 39. Возможность повьшения коэффициентов передачи формирователей 38 и 39 с целью увеличения уровня выходного сигнала, ограничена динамическим диапазоном входных сигналов и необходимостью работы формирователей в линейном режиме. Преобразователь 37 фаза - код зафиксирует на выходе цифровой отсчет, пропорциональный фазовому сдвигу д, вносимому фазовой неидентичностью каналов:N ц, - ± , где К. - коэффициент пропорциональности. Введением кода в запоминающее устройство 32 через ключ 27 завершается этап предварительной коррекции амплитудной и фазовой неидентичности каналов. Перед выполнением второго этапа точной к(9рракции амплитуднрй неидентичности каналов - второй вход преобразователя 38 через ключ 25, подключается к выходу фазовращателя 36, а первьй вход преобразователя 39 через ключ 26 - к выходу фазовращателя 35. Первьй вход интегратора 17 и вход интегратора 28 через ключ 43 подключается к выходу ключа 44, а второй вход интегратора 17 и вход ин тегратора 29 через ключ 46 - к выходу ключа 45, ключи 22 и 27 разомкнуты, а,ключи 23 и 24 сохраняют предыдущее -положение. Если пренебречь погрешностью коррекции неидентичности фазовых характеристик 1 аналов, то после подачи сигналов (3) и (4) на входы аттенюаторов 34 и 35 на выходах формировател,ей 38 и 39 образуются суммарный и разностный сигналы: U(t) 12ЛКК - lut; U.(t) 2 KoV,, siniot. где ДК - погрешность предварительной коррекции амплитудной неидентичности каналов; коэффициент передачи формирователя 38 разностного сигнала в случае использования интегральных операционных усилителей может быть достаточно большим Сигналы (10) и (11) поступают на входы блоков 1, 3 и 20. Далее цикл измерения аналогичен вьше описанному При этом сигнал U на фиг. 36 соответствует напряжению U.(t), сигнал изображенный на Фиг.Зб сплошной линией - напряжению V(t) при V(t) 0, а сигнал V показанный штриховой линией - напряжению V(t) при V (t) 0. В результате при V(t) О импульсы, показанные на фиг. Зв,г образуются на выходах блоков t и 3 сравнения соответственно, а при V-(t) 0 напряжение, показанное на фиг. Зв, образуется на выходе блока 3, а на фиг. Зг - на выходе блока 1. Блок 2 из прямого и инвертированного пилообразного напряжения формирует прямоугольные импульсы (фиг. Зд). На выходах блоков 19 и 20 тактового генератора 6 образуются прямоугольные импульсы, показанные на фиг. Зе,ж; а на выходах элементов 10 и 11 - импульсы, показанные на фиг. 3л,м соответственно. При V(t) О напряжение на выходе элемента 8 соответствует представленному на фиг.Зи, а на выходе элемента 9 - на фиг. Зк. При V(t) О (показан на фаг. Зб штриховой линией) напряжение в соответствии с фиг. Зи образуется на выходе элемента 9, а в соответствии с фиг. Зи - на выходе элемента 8. При V(t)0 импульсы (фиг. Зи) совпадут по времени с импульсами (фиг. 3л)., а импульсы (фиг,3к) - с импульсами (фиг. 3м) на входе элемента 12,- а на его выходе образуется напряжение фиг. Зн.. На выходе элемента 13 будет при этом постоянно присутствовать нулевой уровень. При V«(t)0 отмеченное выше временное совпадение импульсов происхо дит на входах элемента 13 и сигнал (фиг. Зи) - появится на его выходе, а на выходе элемента 12 будет постоян но присутствовать.нулевое напряяюние.. Таким образом, при V-.(t)0 через ключи 44 и A3 ключевого элемента 15 происходит подключение эталонного гене ратора 14 fc первому входу интег ратора 17, к входу интегратора 28, при V(t)0 ключи 45 и 46 клю чевого элемента 16 - к второму вход интегратора 17 и входу интегратора 29. На викоде интегратора 17 будет зафиксирован отсчет: ±2КуДК к.У Причем знак Определяется, как и раньше, выходным сигналом компаратора 30. Введением кода (12) в запоминающее устройство 31 через ключ 22 завершается этап точной коррекции амплитудной неидентичности каналов. . . В данном случае погрешность коррекции, контролируемая по коду на выходе интег ратора 17, может быть записана в виде: 2 к K..V, где л к В результате второго этапа корре ции точность коррекции возрастает в К раз. Перед выполнением второго режима автоматической компенсации фазового сдвига между входными сигналами источник сигнала U(t) подключается к входу аттенюатора 33, а источник U-(t) через ключ 24 - к входу аттен атора 34, который одновременно отключается ключом 23 от источника U(t). Перед подачей сигналов U(t) и U2(t) запоминающее устройст во 32 устанавливается в нулевое сос тояние, а запоминакоцее устройство 31 хранит коды коррекции предыдущего режима.. После подачи сигналов (1) и (2) на входы устройства преобразователь 1 4 37 фаза - код зафиксирует на выходе цифровой отсчет, пропорциональный фазовому сдвигу; Введением кода (14) в запоминающее устройство 32 обеспечивается компенсация фазового сдвига Ч между сигналами, что повышает чувствительность измерения дифференциальной составляющей входных сигналов. Если одновременно с указанной компенсацией f необходимо измерить каждый из указанных сигналов, предварительное значение их дифференциальной составля1Ш;ёй, то перед выполнением данного этапа формирсшатели 38 и 39 с помощью ключей 25 и 26 переводятся в режим одновходовых усилителей, а вход отсчетного устройства 18 подключается к выходу интеграторов 28, 29 или 17. После проведения коррекций в предыдущих режимах воль-тетр готов к точному измерению дифференциальной составлякщей входных сигналов. Для этого фо1Я4ИрЬватели 38 и 39 с помощью ключей 25 и 26 переводятся в режим формирования разностного и суммарного сигналов, запоминающие устройства 31 и 32 хранят коды коррекции амплитудной нецдентичности каналов и фазового рассогласования между сигналами. Клю- чи 43 и 46 переводятся в положения второго этапа точной коррекции амплитудной некдентичности каналов. После окончания цикла измерения, аналогичного описанному при втором этапе коррекции, иНтегрирэгаощее устройство 17 за({ {ксирует на своем выходе цифровой отсчет, пропорциональный среднему значению дифференциальной составляющей входных сигналов, несущий инф9рмацию и о ее знаке. Задатчик 21 (4мг.2) работает следующим образом. Переменное напряжение с выхода формирователя 39 поступает на вход нуль-органа 48, на выходе которого образуется импульсы, соответствующие моментам перехода напряжения через нулевой уровень. Указанные импульсы суммируются в счетчике 49. Разрядные шины 49 подключены к входам дешифратора 50 в соответствии с заданной программой управления ключами вольтметра. При этом моменты появления импульсов на выходах формирователя 51 rf длительности импульсов определяются моментами перепадов напряжений на соответствутфпс выходах дешифратора 50, формирующих передний и задний онты управляю1цих импульсов. . Фор1«|рователь 51 может быть выпоАяен, например, на О-триггерахЗбАТМ. Результат измерения является преобразованием усредненного за цикл измерения мгновенных значений ди ференциальной составлякяцей входаых напряжений.; Предлагаемое устройство обеспечивает повышенную точность измерения да(фференщ|альной составляющей входных сигналов при изменении относительного фазового сдвига между ними. .Яри зтом в качестве опорного сигнала, обеспечивающего повьовенную. помехоустойчивость измерения, используется суммарный сигнал, который обеспечивает селективное измерение синфазных и противофазньЬс составляющих разностного сигнала и подавление составляюпщх с фазовым сдвигом, отличаюоашся от значений О или относительно опорного сигнала. Технико-зкономический зффект изобретения заключается в том, что вольтметр имеет чувствительность измерения диффе ренциальной составляющей на порядок выше, чем у {базового образца, и составляет 0,25 мВ при уровне сигналов. мВ и отношении сигнал-вп j в то время как в базовом образце не предусмотрены меры помехоустойчивости. Время измерения в предлагаемом вольтметре около 5 мс, что в 40 раз меньше, чем у базового образца.

/

5f 5J5 555ff 5751 55

Фиг 2

t fl П П

f

.

П П

Inn П

1 П П П ni II t

n П П П

f

П П

к

t о П П П П П

J П л I-1 П П J П ППГПППП

I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-05-23—Публикация

1983-03-18—Подача