1

(21)4354451/24-24

(22)04.01.88

(46) 23.09.89. Бкш. I 35

(71)Томский политехнический институт им. С.М.Кирова

(72)А.И.Лещенко, В.Ю.Борисенко и В.В.Пашин

(53)681.335 (088.8)

(56)Жилинскас Р.-П.П. Измерители отношения и их применения в радиоизмерительной технике. - М.: Советское радио, 1975, с. 113-115, рис. 4.18.

Авторское свидетельство СССР № 1179381, кл. G 06 G 7/16, 1984.

(54)УСТРОЙСТВО ДЕЛЕНИЯ ВЫСОКОЧАСТОТНЫХ СИГНАЛОВ

(57)Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является расширение диапазона частот преобразуемых сигналов. Устройство деления высокочастотных сигналов содержит входы сигнала-делимого I и сигнала-делителя 2, первый и второй пиковые детекторы 3 и 4, первый и второй дополнительные сумматоры 5 и 6, коммутатор 7, блок синхронизации 8, сумматор 9, полосовой фильтр 10 и фазоизмерительный блок 11. Устройство управляется сигнгшами с блока синхронизации 8 циклически таким образом, что часть цикла пропускается - сигнал с входа 1, другая равная часть цикла пропускается - сигнал с входа 2, третья часть цикла - пауза. Сформированный ступенчато-импульсный сигнал пропускают через полосовой фильтр 10, настроенный на частоту первой гармоники ступенчато-импульсного сигнала, фаза которой относительно опорного сигнала с блока синхронизации 8 пропорциональна отношению входных сигналов. 2 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ деления двух сигналов и устройство для его осуществления (его варианты) | 1982 |

|

SU1104536A1 |

| Устройство деления двух аналоговых сигналов | 1986 |

|

SU1348821A2 |

| Устройство для деления аналоговых сигналов | 1987 |

|

SU1529250A1 |

| Устройство для деления сигналов | 1984 |

|

SU1179381A1 |

| Устройство для контроля фазочастотных характеристик каналов связи | 1985 |

|

SU1394440A1 |

| Время-импульсное делительное устройство | 1977 |

|

SU721830A1 |

| Устройство для измерения параметров резонансных контуров | 1982 |

|

SU1071972A1 |

| Программный генератор | 1983 |

|

SU1190484A1 |

| Программный генератор | 1980 |

|

SU917319A1 |

| Устройство для поверки фазометров | 1972 |

|

SU439766A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является расширение диапозона частот преобразуемых сигналов. Устройство деления высокочастотных сигналов содержит входы сигнала- делимого 1 и сигнала-делителя 2, первый и второй пиковые детекторы 3 и 4, первый и второй дополнительные сумматоры 5 и 6, коммутатор 7, блок синхронизации 8, сумматор 9, полосовой фильтр 10 и фазоизмерительный блок 11. Устройство управляется сигналами с блока синхронизации 8 циклически таким образом, что часть цикла пропускается сигнал с входа 1, другую равную часть цикла пропускается сигнал с входа 2, третья часть цикла - пауза. Сформированный ступенчато-импульсный сигнал пропускают через полосовой фильтр 10, настроенный на частоту первой гармоники ступенчато-импульсного сигнала, фаза которо относительно опорного сигнала с блока синхронизациии 8 пропорциональна отношению входных сигналов. 2 ил.

СП

о ;о со ji со

Изобретение относится к электри- ческим вычислительным устройствам и может быть исгГользовано в аналоговых вычислительных машинах.

Цель изобретения - расширение диапазона частот преобразуемых сигналов

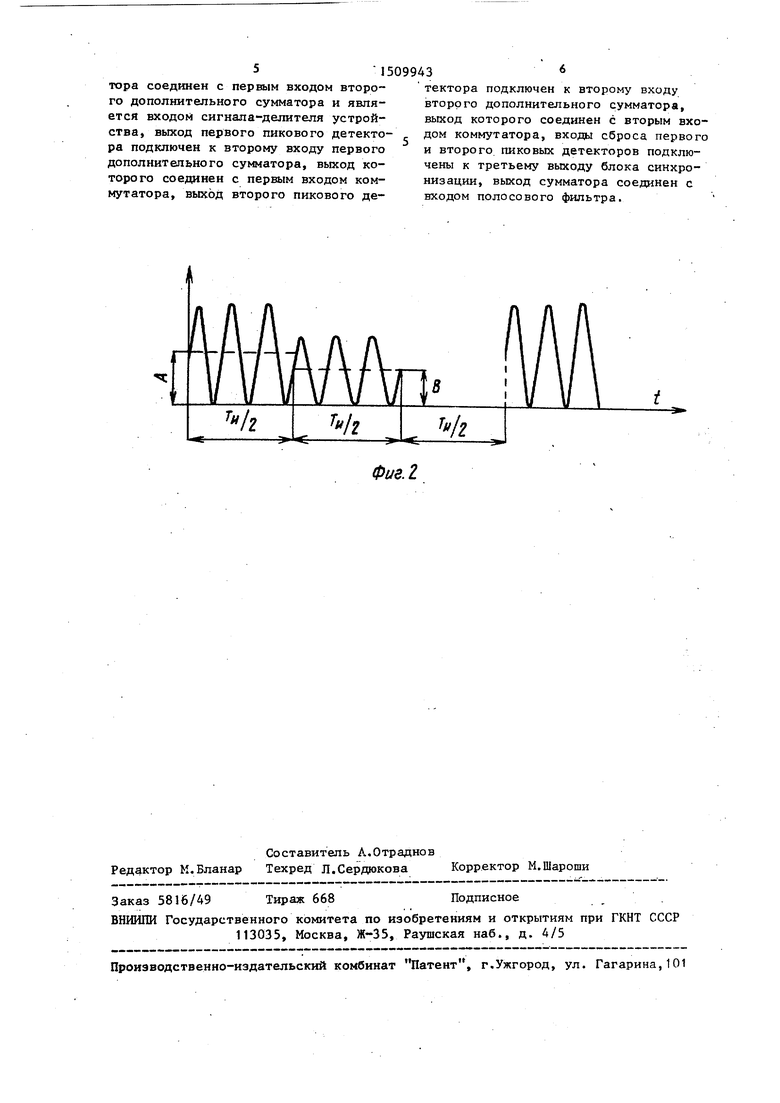

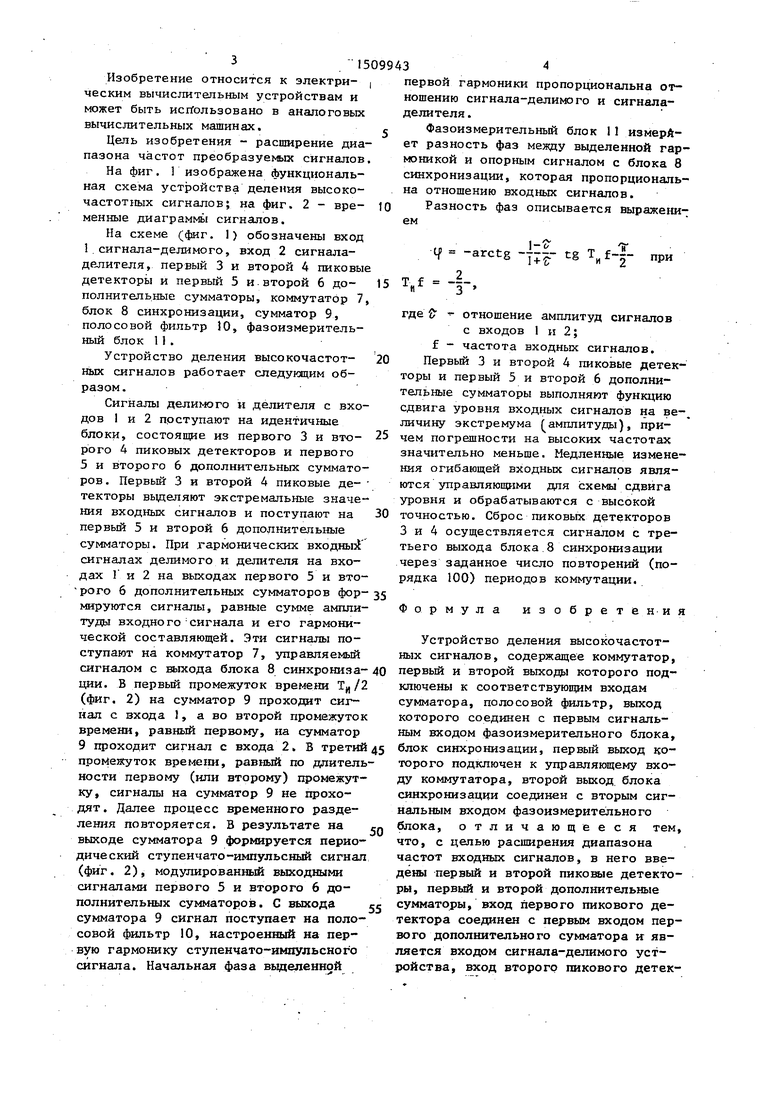

На фиг. 1 изображена функциональная схема устройства деления высокочастотных сигналов; на фиг. 2 - вре- менные диаграммь сигналов.

На схеме (фиг. 1) обозначены вход

Устройство деления высокочастот- сигналов работает следующим образом.

Сигналь: делимого и делителя с входов I и 2 поступают на идентичные блоки, состоящие из первого 3 и вто- рого 4 пиковых детекторов и первого 5 и второго 6 дополнительных сумматоров . Первый 3 и второй 4 пиковые де- текторы выделяют экстремальные значения входных сигналов и поступают на первый 5 и второй 6 дополнителыаю сумматоры. При гармонических входныз сигналах делимого и делителя на входах Г и 2 на выходах первого 5 и вто- -рого 6 дополнительных сумматоров формируются сигналы, равные сумме амплитуды входного сигнала и его гармонической составляющей. Эти сигналы поступают на коммутатор 7, управляемый

сигналом с выхода блока В синхрониза- 40 первый и второй выходы которого подции. В первый промежуток времени (фиг. 2) на сумматор 9 проходит сигнал с входа J, а во второй промежуток времени, равный первому, на сумматор

9 проходит сигнал с входа 2, В третий 45 блок синхронизации, первый выход копромежуток време1ш, равный по длительности первому (или второму) промежутку, сигналы на сумматор 9 не проходят. Далее процесс временного разделения повторяется. В результате на сп выходе сумматора 9 формируется периодический ступенчато-импульсный сигнал (фиг. 2), модулированный выходными сигналами первого 5 и второго 6 дополнительных сумматоро в. С выхода 5 сумматора 9 сигнал поступает на полосовой фильтр 10, настроенный на первую гармонику ступенчато-импульсного сигнала. Начальная фаза вьадеденной

первой гармоники пропорциональна отношению сигнала-делимого и сигнала- делителя .

Фазоизмерительный блок 11 измерА- ет разность фаз между выделенной гармоникой и опорным сигналом с блока 8 синхронизации, которая пропорциональна отношению входных сигналов.

Разность фаз описывается выражением

-г

Т+г

tg Т f-|при

t -arctg

где Ъ отношение амплитуд сигналов

с входов 1 и 2; f - частота входных сигналов. Первый 3 и второй 4 пиковые детекторы и первый 5 и второй 6 дополнительные сумматоры выполняют функцию сдвига уровня входных сигналов на величину экстремума амплитуды), причем погрешности на высоких частотах значительно меньше. Медленные изменения огибающей входных сигналов являются управляющими для схемы сдвига уровня и обрабатываются с высокой точностью. Сброс пиковых детекторов 3 и 4 осуществляется сигналом с третьего выхода блока.8 синхронизации через заданное число повторений (порядка 100) периодов коммутации.

Формула изобретения

Устройство деления высокочастотных сигналов, содержащее коммутатор,

ключены к соответствующим входам сумматора, полосовой фильтр, выход которого соединен с первым сигнальным входом фазоизмерительного блока.

торого подключен к управляющему входу коммутатора, второй выход, блока синхронизации соединен с вторым сигнальным входом фазоизмерительного блока, отличающееся тем, что, с целью расширения диапазона частот входных сигналов, в него введены первый и второй пиковые детекторы, первый и второй дополнительные сумматоры, вход первого пикового детектора соединен с первым входом первого дополнительного сумматора и является входом сигнала-делимого устройства, вход второго пикового детектора соединен с первым входом второго дополнительного сумматора и является входом сигнала-делителя устройства, выход первого пикового детектора подключен к второму входу первого дополнительного сумматора, выход которого соединен с первым входом коммутатора, выход второго пикового детектора подключен к второму входу второго дополнительного сумматора, выход которого соединен с вторым входом коммутатора, входы сброса первого и второго пиковых детекторов подключены к третьему выходу блока синхронизации, выход сумматора соединен с входом полосового фильтра.

Фие.г

Авторы

Даты

1989-09-23—Публикация

1988-01-04—Подача