Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Целью изобретения является повышение точности.

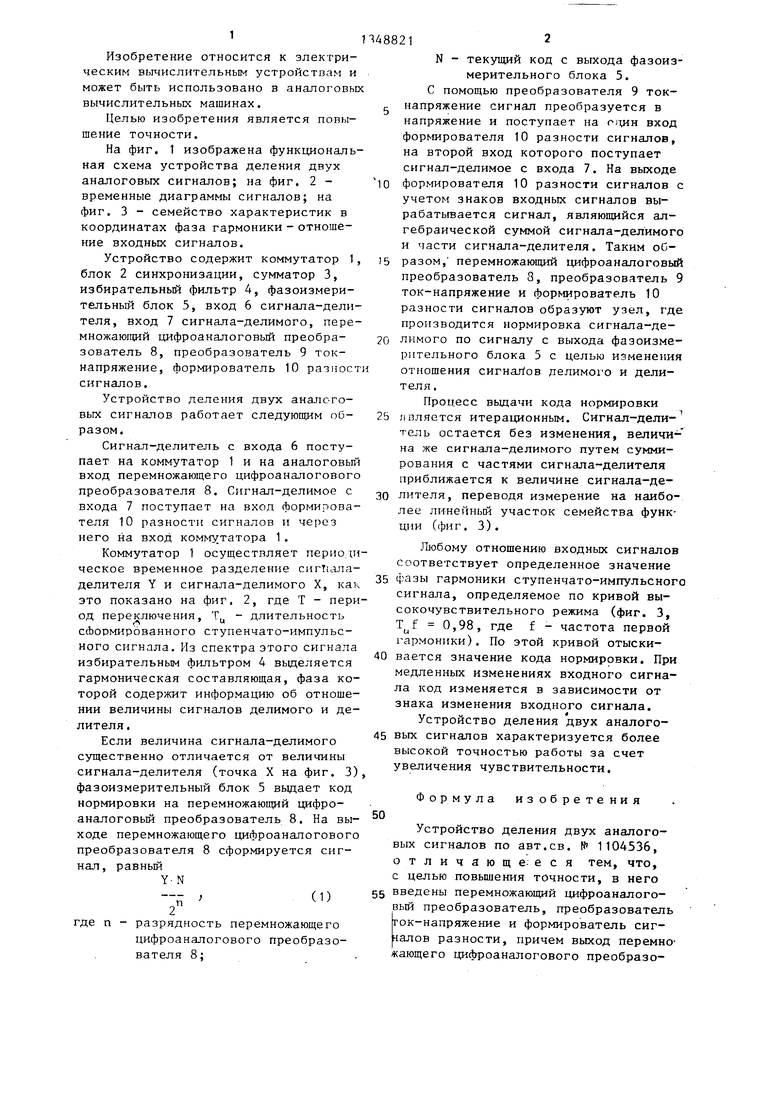

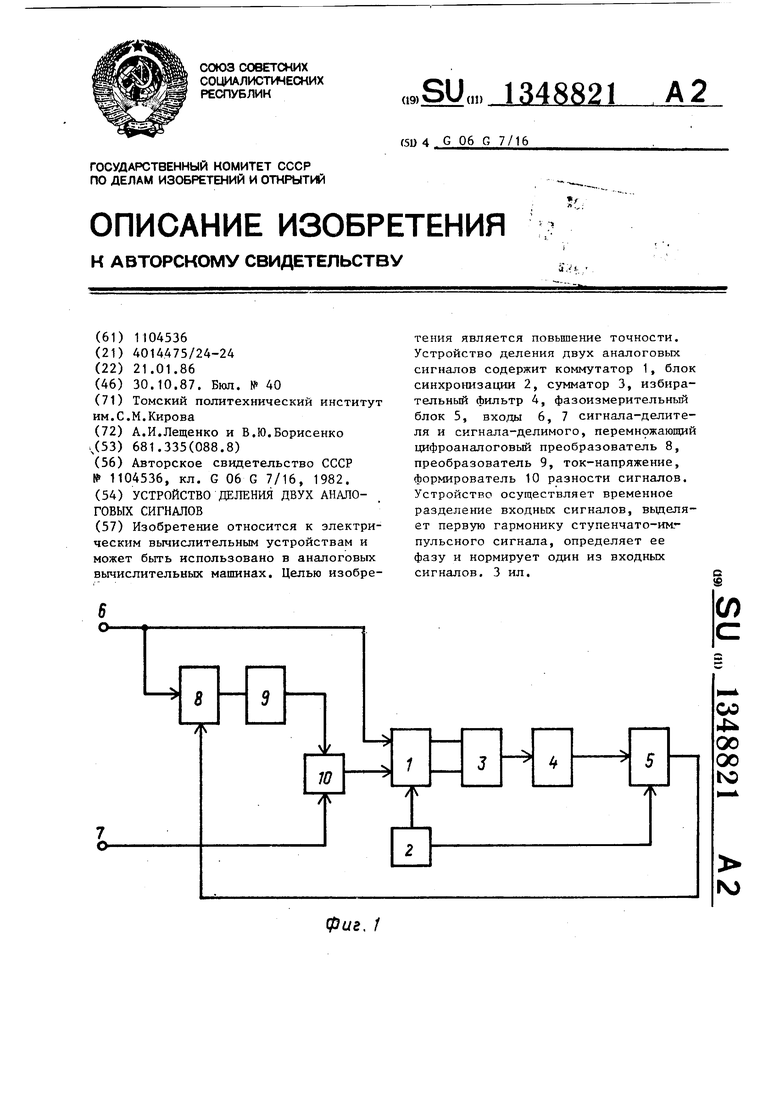

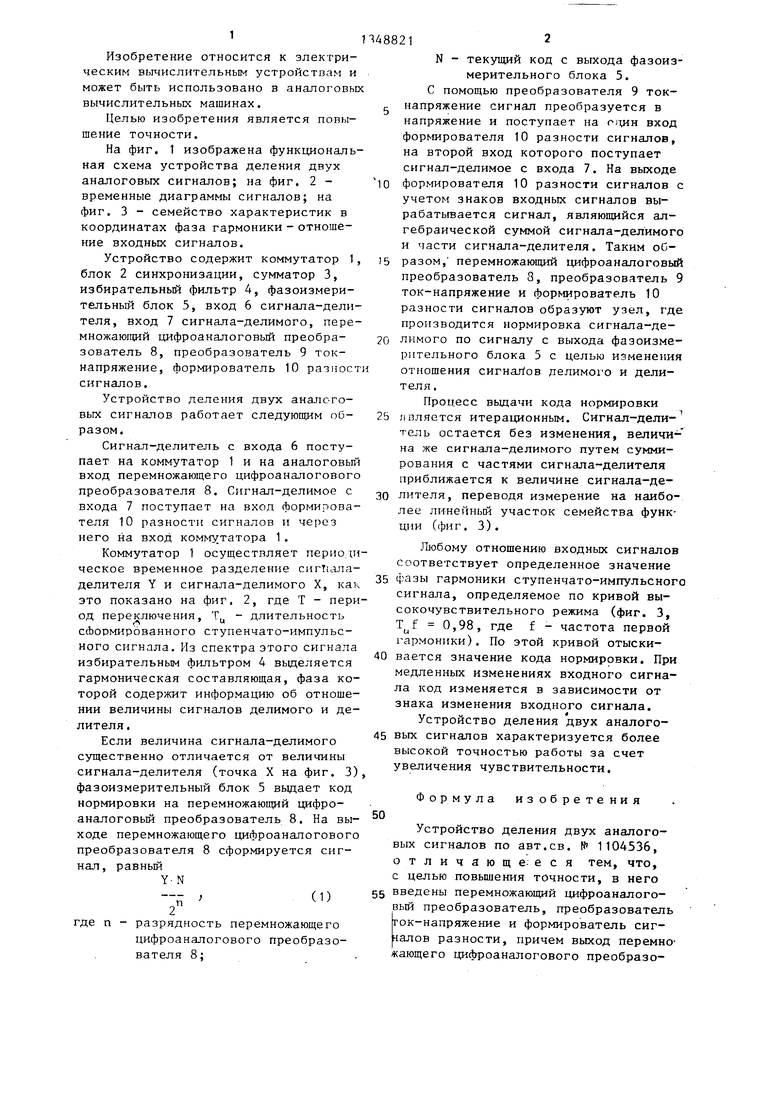

На фиг. 1 изображена функциональная схема устройства деления двух аналоговых сигналов; на фиг. 2 - временные диаграммы сигналов; на фиг. 3 - семейство характеристик в координатах фаза гармоники - отношение входных сигналов.

Устройство содержит коммутатор 1, блок 2 синхронизации, сумматор 3, избирательный фильтр 4, фазоизмери- тельный блок 5, вход 6 сигнала-делителя, вход 7 сигнала-делимого, пере- множаю1ций цифроаналоговый преобразователь 8, преобразователь 9 ток- напряжение, формирователь 10 разност сигналов.

Устройство деления двух аналоговых сигнапов работает следующим образом.

Сигнал-делитель с входа 6 поступает на коммутатор 1 и на аналоговьм вход перемножающего цифроаналогового преобразователя 8. Сигнал-делимое с входа 7 поступает на вход формирователя 10 разности сигналов и через него на вход ком -гу татора 1 .

Коммутатор 1 осуществляет периодическое временное разделение сигТигпа- делителя Y и сигнала-делимого X, как это показано на фиг, 2, где Т - период переключения, Т - длительность сформированного ступенчато-импульсного сигнала. Из спектра этого сигнала избирательным фильтром 4 выделяется гармоническая составляющая, фаза которой содержит информацию об отношении величины сигналов делимого и делителя.

Если величина сигнала-делимого существенно отличается от величины сигнала-делителя (точка X на фиг. 3) фазоизмерительный блок 5 выдает код нормировки на перемножающий цифро- аналоговый преобразователь 8. На выходе перемножающего цифроаналогового преобразователя 8 сформируется сигнал, равный

Y-N

,п

(1)

где п разрядность перемножающего цифроаналогового преобразователя 8;

N - текущий код с выхода фазоизмерительного блока 5. С помощью преобразователя 9 ток- g напряжение сигнал преобразуется в напряжение и поступает на oiyiH вход формирователя 10 разности сигналов, на второй вход которого поступает сигнал-делимое с входа 7. На выходе

0 формирователя 10 разности сигналов с учетом знаков входных сигналов вырабатывается сигнал, являющийся алгебраической суммой сигнала-делимого и части сигнала-делителя. Таким оО5 разом, перемножающий цифроаналоговый преобразователь 8, преобразователь 9 ток-напряжение и формирователь 10 разности сигналов образуют узел, где производится нормировка сигнала-де0 лимого по сигналу с выхода фазоизме- рительного блока 5 с целью изменения отношения сигналов делимог О и делителя ,

Процесс выдачи кода нормировки

5 является итерационным. Сигнал-делитель остается без изменения, величи- на же сигнала-делимого путем суммирования с частями сигнала-делителя приближается к величине сигнала-де0 лителя, переводя измерение на наиболее линейный участок семейства функции (фиг. 3).

Ъобому отношению входных сигналов соответствует определенное значение

5 фазы гармоники ступенчато-импульсного сигнала, определяемое по кривой высокочувствительного режима (фиг. 3, 0,98, где f - частота первой гармоники). По этой кривой отыски0 вается значение кода нормировки. При медленных изменениях входного сигнала код изменяется в зависимости от знака изменения входного сигнала. Устройство деления двух аналого5 вых сигналов характеризуется более высокой точностью работы за счет увеличения чувствительности.

Формула изобретения

Устройство деления двух аналоговых сигналов по авт.св. № 1104536, отличающе.еся тем, что, с целью повышения точности, в него 55 введены перемножающий цифроаналоговый преобразователь, преобразователь ток-напряжение и формирователь сигналов разности, причем выход перемножающего цифроаналогового преобразо3134882

вателя подключен к выходу преобразователя ток-напряжение, выход которого соединен с первым входом формирователя разности сигналов, второй вход которого является входом сигнала- делимого устройства деления, аналоговый вход перемножающего цифроаналого

1

вого преобразователя соединен с первым входом коммутатора, к второму входу которого подключен выход формирователя разности сигналов, цифровой вход перемножающего цифроанало- , Гового преобразователя соединен с выходом фазоизмерительного блока.

Фиг. 2

0,2 0/f 06 Фиъ.З

V

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления аналоговых сигналов | 1987 |

|

SU1529250A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1987 |

|

SU1525614A1 |

| Устройство для деления сигналов | 1984 |

|

SU1179381A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ МЕСТА ПОВРЕЖДЕНИЯ ЭЛЕКТРИЧЕСКОГО КАБЕЛЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2190234C1 |

| Способ деления двух сигналов и устройство для его осуществления (его варианты) | 1982 |

|

SU1104536A1 |

| Устройство деления высокочастотных сигналов | 1988 |

|

SU1509943A1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

| Устройство для управления вибростендом | 1982 |

|

SU1101794A1 |

| Устройство для измерения нелинейных искажений | 1988 |

|

SU1707564A1 |

Изобретение относится к электрическим вьтислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобрефиг. 1 тения является повышение точности. Устройство деления двух аналоговых сигналов содержит коммутатор 1, блок синхронизации 2, сумматор 3, избирательный фильтр 4, фазоизмерительный блок 5, входы 6, 7 сигнала-делителя и сигнала-делимого, перемножающий цифроаналоговый преобразователь 8, преобразователь 9, ток-напряжение, формирователь 10 разности сигналов. Устройство осуществляет временное разделение входных сигналов, выделяет первую гармонику ступенчато-имг пульсного сигнала, определяет ее фазу и нормирует один из входных сигналов. 3 ил. с со 4 00 ОС ю N)

| Способ деления двух сигналов и устройство для его осуществления (его варианты) | 1982 |

|

SU1104536A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-10-30—Публикация

1986-01-21—Подача