XI

40

ел

|нА

а

Физ.1

Изобретение относится к измерительной технике и может найти применение при создании цифровых фазометров повьппенной точности, а также высокоточных преобразователей фаза-код для управляющих цифровых вычислительных систем.

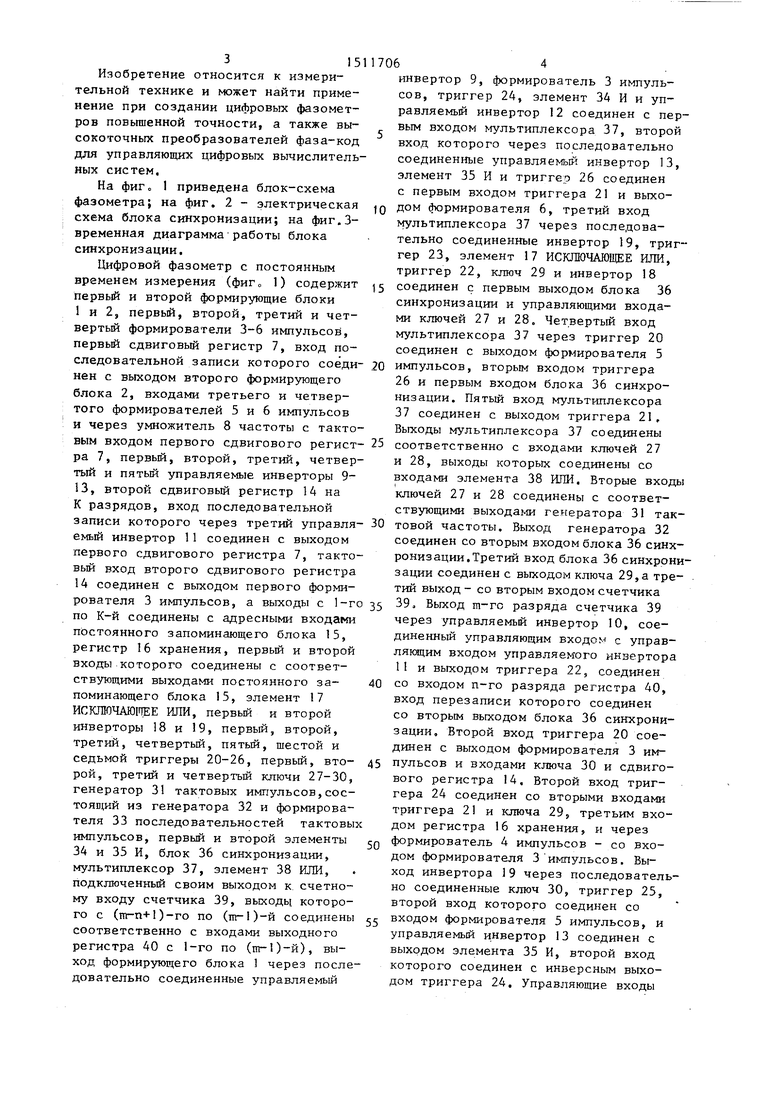

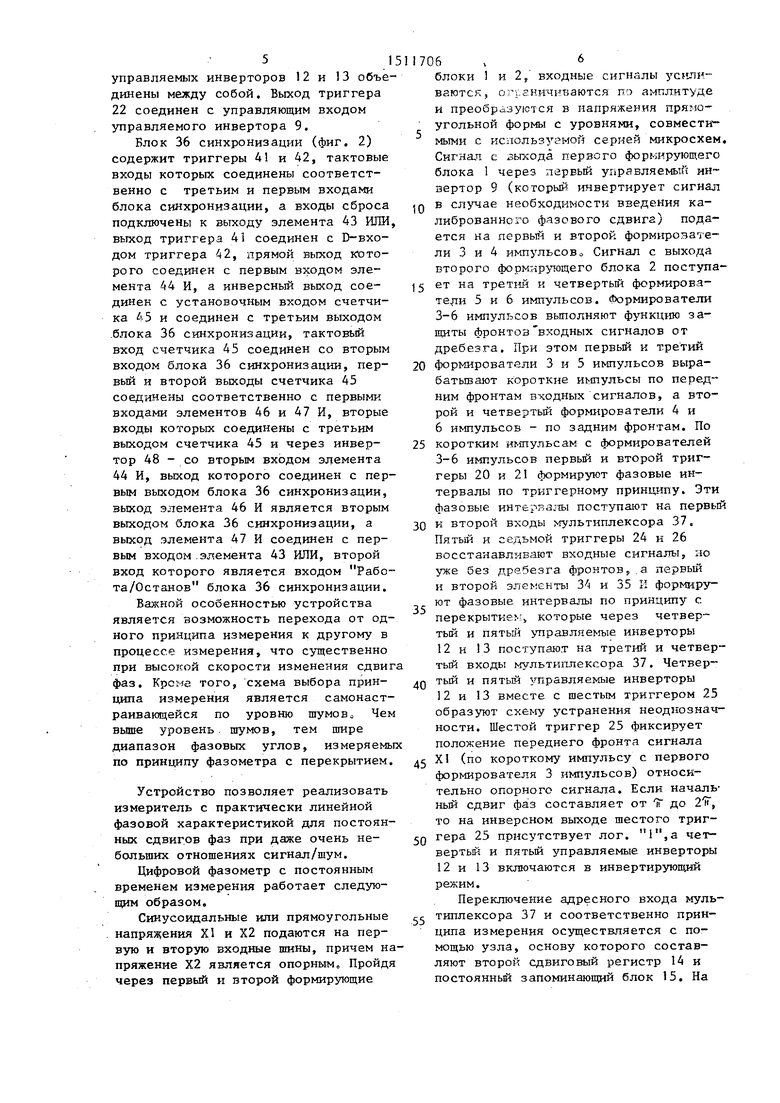

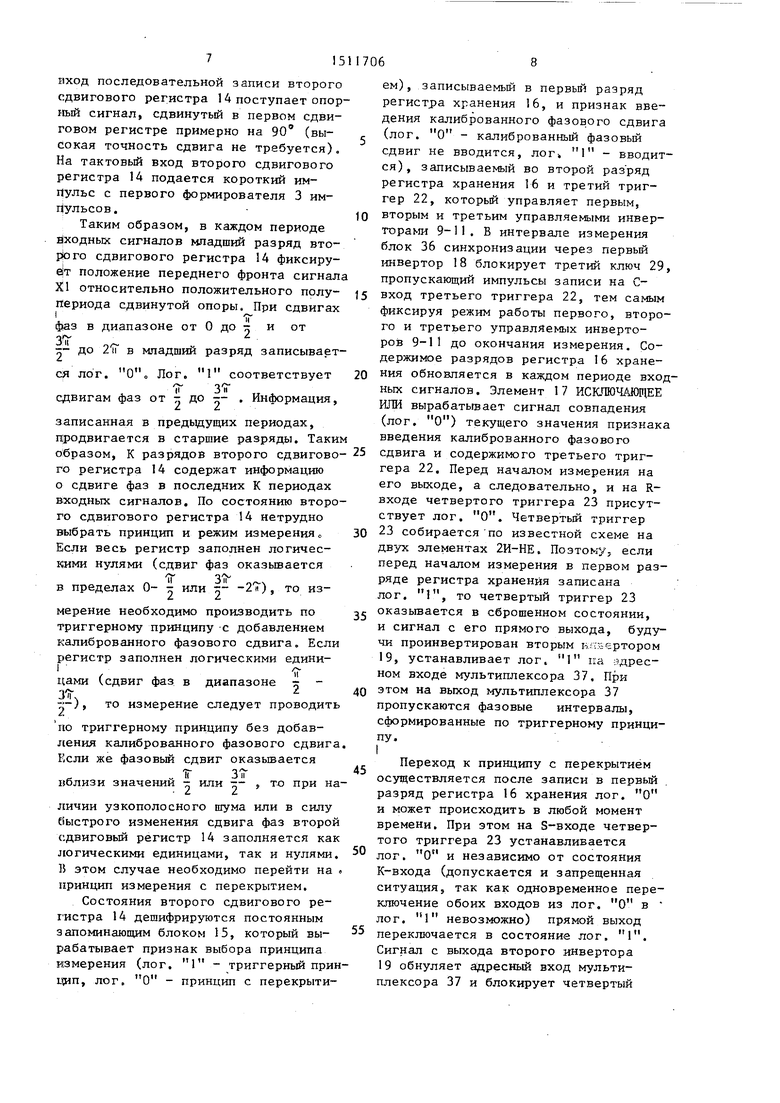

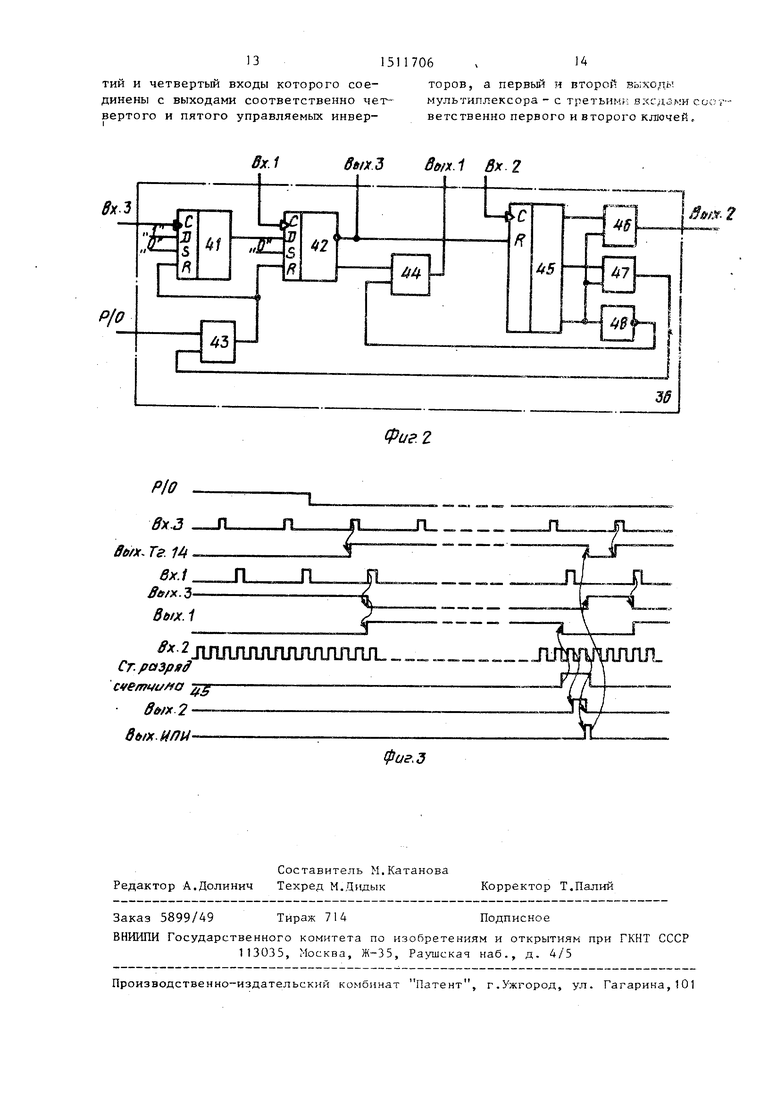

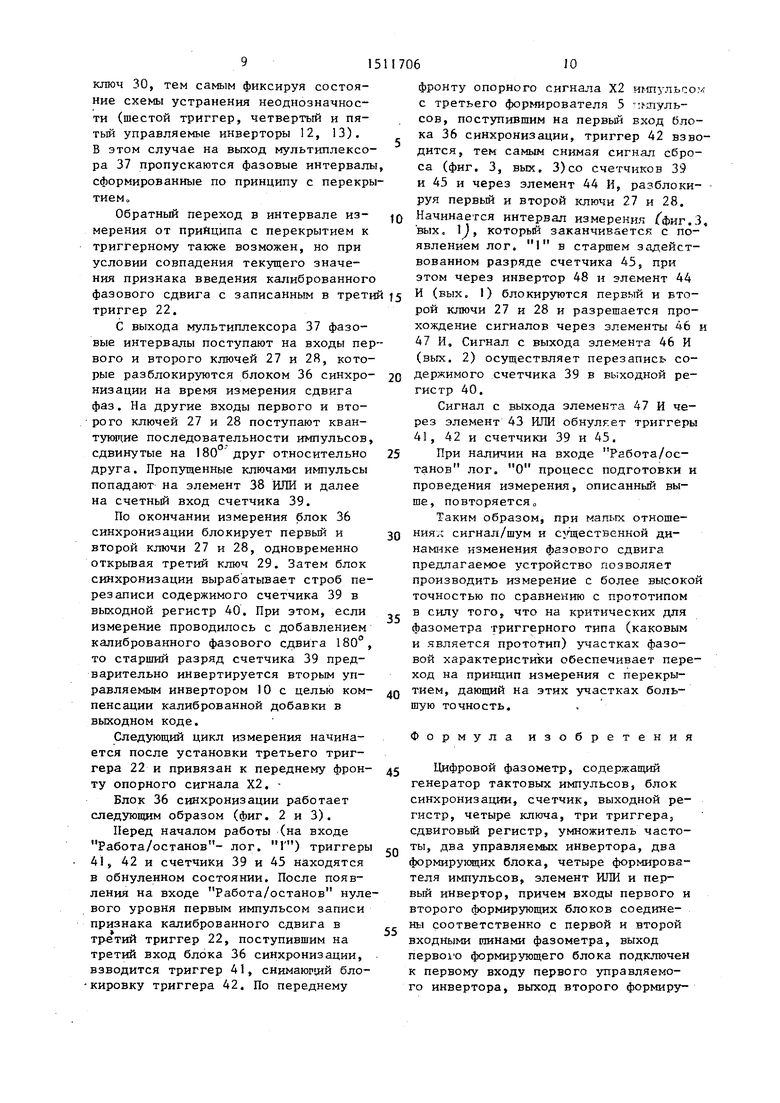

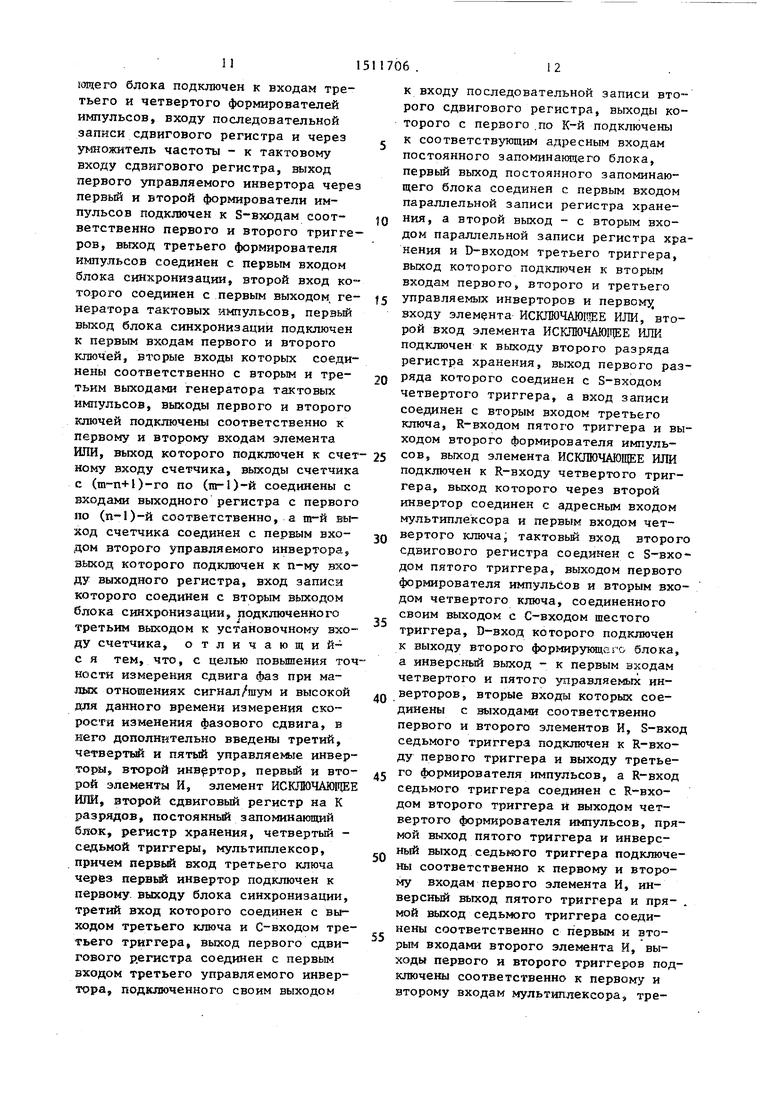

На фиг о 1 приведена блок-схема фазометра; на фиг. 2 - электрическая схема блока синхронизации; на фиг.З- временная диаграмма работы блока синхронизации,

Цифровой фазометр с постоянным временем измерения (фиГо 1) содержит первый и второй формирующие блоки 1 и 2, первый, второй, третий и чет- вертьй формирователи 3-6 импульсов, первьй сдвиговьй регистр 7, вход последовательной записи которого соеди- ней с выходом второго формирующего блока 2, входами третьего и четвертого формирователей 5 и 6 импульсов и через умножитель 8 частоты с тактовым входом первого сдвигового регист- ра 7, первьй, второй, третий, четвертый и пятьй управляемые инверторы 9- 13, второй сдвиговый регистр 14 на К разрядов, вход последовательной записи которого через третий управля- емьй инвертор 11 соединен с выходом первого сдвигового регистра 7, такто вьй вход второго сдвигового регистра 14 соединен с выходом первого формирователя 3 импульсов, а выходы с 1-г по К-й соединены с адресными входами постоянного запоминающего блока 15, регистр 16 хранения, первьй и второй входы которого соединены с соответствующими выходами постоянного за- поминающего блока 15, элемент 7 ИСКПЮЧАЮ1ПЕЕ ИЛИ, первьй и второй инверторы 18 и 19, первый, второй, третий, четвертьй, пятый, шестой и седьмой триггеры 20-26, первьй, вто- рой, третий и четвертъй ключи 27-30, генератор 31 тактовых импульсов,состоящий из генератора 32 и формирователя 33 последовательностей тактовы импульсов, первый и второй элементы 34 и 35 И, блок 36 синхронизации, мультиплексор 37, элемент 38 ИЛИ, подключенньй своим выходом к счетному входу счетчика 39, выходь которого с (пг-п+1)-го по (т-1)-й соединены соответственно с входами выходного регистра 40 с 1-го по (пг-О-й), выход формирующего блока 1 через последовательно соединенные управляемьй

инвертор 9, формирователь 3 импульсов, триггер 24, элемент 34 И и управляемьй инвертор 12 соединен с первым входом мультиплексора 37, второй вход которого через последовательно соединенные управляемый инвертор 13, элемент 35 И и триггер 26 соединен с первым входом триггера 21 и выходом формирователя 6, третий вход мультиплексора 37 через последовательно соединенные инвертор 19, триггер 23, элемент 17 ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер 22, ключ 29 и инвертор 18 соединен с первым выходом блока 36 синхронизации и управляющими входами ключей 27 и 28. Четвертый вход мультиплексора 37 через триггер 20 соединен с выходом формирователя 5 импульсов, вторым входом триггера 26 и первым входом блока 36 синхронизации. Пятый вход мультиплексора 37 соединен с выходом триггера 21, Выходы мультиплексора 37 соединены соответственно с входами ключей 27 и 28, выходы которых соединены со входами элемента 38 ИЛИ, Вторые вход ключей 27 и 28 соединены с соответствующими выходами генератора 31 тактовой частоты. Выход генератора 32 соединен со вторым входом блока 36 синхронизации. Третий вход блока 36 синхронзации соединен с выходом ключа 29,а третий выход - со вторым входом счетчика 39, Выход т-го разряда счетчика 39 через управляемый инвертор 10, сое- диненньй управляющим входом с управляющим входом управляемого инвертора П и выходом триггера 22, соединен со входом п-го разряда регистра 40, вход перезаписи которого соединен со вторым выходом блока 36 синхронизации. Второй вход триггера 20 соединен с выходом формирователя 3 импульсов и входами ключа 30 и сдвигового регистра 14, Второй вход триггера 24 соединен со вторыми входами триггера 2 и ключа 29, третьим входом регистра 16 хранения, и через формирователь 4 импульсов - со входом формирователя 3 импульсов. Выход инвертора 19 через последовательно соединенные ключ 30, триггер 25, второй вход которого соединен со входом формирователя 3 импульсов, и управляемьй инвертор 13 соединен с выходом элемента 35 И, второй вход которого соединен с инверсным выходом триггера 24, Управляющие входы

управляемых инверторов 12 и 13 объединены между собой. Выход триггера 22 соединен с управляющим входом управляемого инвертора 9.

Блок 36 синхронизации (фиг. 2) содержит триггеры 41 и 42, тактовые входы которых соединены соответственно с третьим и первым входами блока синхронизации, а входы сброса подключены к выходу элемента 43 ИЛИ выход триггера 41 соединен с D-BXO- дом триггера 42, прямой выход которого соединен с первым входом элемента 44 И, а инверсный выход соединен с установочным входом счетчика 45 и соединен с третьим выходом -блока 36 синхронизации, тактовьй вход счетчика 45 соединен со вторым входом блока 36 синхронизации, первый и второй выходы счетчика 45 соединены соответственно с первыми входами элементов 46 и 47 И, вторые входы которых соединены с третьим выходом счетчика 45 и через инвертор 48 - со вторым входом элемента 44 И, выход которого соединен с первым выходом блока 36 синхронизации, выход элемента 46 И является вторым выходом блока 36 синхронизации, а выход элемента 47 И соединен с первым входом .элемента 43 ИЛИ, второй вход которого является входом Работа/Останов блока 36 синхронизации.

Важной особенностью устройства является возможность перехода от одного принципа измерения к другому в процессе измерения, что существенно при высокой скорости изменения сдвиг фаз. Крема того, схема выбора принципа измерения является самонастраивающейся по уровню шумов о Чем выше уровень, шумов, тем шире диапазон фазовых углов, измеряемы по принципу фазометра с перекрытием.

Устройство позволяет реализовать измеритель с практически линейной фазовой характеристикой для постоянных сдвигов фаз при даже очень небольших отношениях сигнал/шум.

Цифровой фазометр с постоянным временем измерения работает следующим образом.

Синусоидальные или прямоугольные напряжения XI и Х2 подаются на первую и вторую входные шины, причем напряжение Х2 является опорным. Пройдя через первый и второй формирующие

блоки 1 и 2, входные сигналы усилк- ваютск, ограничиваются по амплитуде и преобразуются в напряжения угольной формы с уровнями, совмести мьгми с используемой серией микросхем. Сигнал с зыхода первого формирующего блока 1 через первый управляемый инвертор 9 (который инвертирует сигнал

Q в случае необходимости введения калиброванного фазового сдвига) подается на первьм и второй формирователи 3 и 4 импульсово Сигнал с выхода второго формирзпощего блока 2 поступа5 ет на третгда и четвертый формирователи 5 и 6 импульсов. Формирователи 3-6 импульсов выполняют функцию защиты фронтов входных сигналов от дребезга. При этом первьй и третий

0 формирователи 3 и 5 импульсов выра- батьшают короткие иьшульсы по передним фронтам входных сигналов, а второй и четвертьш формирователи 4 и 6 импульсов - по задним фронтам. По

5 коротким импульсам с формирователей 3-6 импульсов первьй и второй триггеры 20 и 21 формируют фазовые интервалы по триггерному принципу. Эти фазовые интервалы поступают на первый

0 и второй входы мультиплексора 37, Пятьй и седьмой триггеры 24 и 26 восстанавливают входные сигналы, но уже без дребезга фронтов,.а первый и второй элементы 34 и 35 И формируют фазовые интервалы по принципу с перекрытиеМу которые через четвер- тьй и ПЯТЬЙ управляеьме инверторы 12 и 13 поступают на третий и четвертый входы мультиплексора 37. Четвер-

Q тьй и пятьм управляемые инверторы 12 и 13 вместе с шестым триггером 25 образуют схему устранения неоднозначности. Шестой триггер 25 фиксирует положение переднего фронта сигнала

с XI (по короткому импульсу с первого формирователя 3 импульсов) относительно опорного сигнала. Если началь- ньй сдвиг фаз составляет от Т до 2 ii , то на инверсном выходе шестого тригQ гера 25 присутствует лог. 1,а чет- вертьй и ПЯТЬЙ управляемые инверторы 12 и 13 включаются в инвертирующий режим.

Переключение адресного входа мультиплексора 37 и соответственно принципа измерения осуществляется с помощью узла, основу которого составляют второй сдвиговый регистр 14 и постоянньй запоминающий блок 15. На

5

вход последовательной записи второго сдвигового регистра 14 поступает опор- 1гьй сигнал, сдвинутый в первом сдвиговом регистре примерно на 90° (высокая точность сдвига не требуется). На тактовьй вход второго сдвигового регистра 14 подается короткий им- Пульс с первого формирователя 3 импульсов .

Таким образом, в каждом периоде входных сигналов мпадший разряд вто- рЬго сдвигового регистра 14 фиксирует положение переднего фронта сигнала XI относительно положительного полу- Периода сдвинутой опоры. При сдвигах I„ 7фаз в диапазоне от О до и от

-- до 2 п в мпадший разряд записывается лог. Лог.

соответствует 31Г

сдвигам фаз от - до -- . Информация,

записанная в предыдущих периодах, продвигается в старшие разряды. Таким образом, К разрядов второго сдвигового регистра 14 содержат информацию

0сдвиге фаз в последних К периодах В|Ходных сигналов. По состоянию второго сдвигового регистра 14 нетрудно выбрать принцип и режим измерения Если весь регистр заполнен логическими нулями (сдвиг фаз оказьшается

о/

ч 3ii „л-

в пределах О- т или - -/«;, то измерение необходимо производить по триггерному принципу с добавлением калиброванного фазового сдвига. Если

регистр заполнен логическими едини1 7цами (сдвиг фаз в диапазоне г

-|/Ч,

J 1 ч

-J-), ТО измерение следует проводить

гю триггерному принципу без добавления калиброванного фазового сдвига Если же фазовьй сдвиг оказьшается

«: о II JII

вблизи значений - или -- , то при наличии узкополосного шума или в силу С ыстрого изменения сдвига фаз второй сдвиговый регистр 14 заполняется как логическими единицами, так и нулями. В этом случае необходимо перейти на принцип измерения с перекрытием.

Состояния второго сдвигового регистра 14 дешифрируются постоянным запоминающим блоком 15, который вырабатывает признак выбора принципа измерения (лог. 1 - триггерный прин lyin, лог. О - принцип с перекрытием), записываемый в первьй разряд регистра хранения 16, и признак введения калиброванного фазов.ого сдвига

(лог. О - калиброванный фазовый

сдвиг не вводится, лог 1 - вводится), записываемый во второй раз ряд регистра хранения 16 и третий триггер 22, который управляет первым,

вторым и третьим управляегФ1ми инверторами 9-11. В интервале измерения блок 36 синхронизации через первый инвертор 18 блокирует третий ключ 29, пропускающий импульсы записи на Свход третьего триггера 22, тем самым фиксируя режим работы первого, второго и третьего управляемых инверто- poiB 9-11 до окончания измерения. Содержимое разрядов регистра 16 хранеиия обновляется в каждом периоде входных сигналов. Элемент 17 ИСКЛЮЧАЮЩЕЕ ИЛИ вырабатывает сигнал совпадения (лог. О) текущего значения признака введения калиброванного фазового

сдвига и содержимого третьего триггера 22. Перед началом измерения на его выходе, а следовательно, и на R- входе четвертого триггера 23 присутствует лог. О. Четвертый триггер

23 собирается по известной схеме на двух элементах 2И-НЕ. Поэтому, если перед началом измерения в первом разряде регистра хранения записана лог, 1, то четвертый триггер 23

оказьшается в сброшенном состоянии, и сигнал с его прямого выхода, будучи проинвертирован вторым к;ТЕертором 19, устанавливает лог, 1 ка эдрес- ном входе мультиплексора 37. При

этом на выход мультиплексора 37 пропускаются фазовые интервалы, сформированные по триггерному принципу. I

Переход к принципу с перекрытием

осуществляется после записи в первый разряд регистра 16 хранения лог. О и может происходить в любой момент времени. При этом на S-входе четвертого триггера 23 устанавливается лог. О и независимо от состояния К-входа (допускается и запрещенная ситуация, так как одновременное переключение обоих входов из лог. О в лог. 1 невозможно) прямой выход переключается в состояние лог. 1. Сигнал с выхода второго инвертора 19 обнуляет адресный вход мультиплексора 37 и блокирует четвертый

9

ключ 30, тем самым фиксируя состояние схемы устранения неоднозначности (шестой триггер, четвертый и пятый управляемые инверторы 12, 13). В этом случае на выход мультиплексора 37 пропускаются фазовые интервал сформированные по принципу с перекртием

Обратный переход в интервале измерения от принципа с перекрытием к триггерному также возможен, но при условии совпадения текущего значения признака введения калиброванног фазового сдвига с записанным в трет триггер 22.

С выхода мультиплексора 37 фазовые интервалы поступают на входы певого и второго ключей 27 и 28, которые разблокируются блоком 36 синхронизации на время измерения сдвига фаз. На другие входы первого и второго ключей 27 и 28 поступают кван- тукипие последовательности импульсов сдвинутые на 180 друг относительно друга. Пропущенные ключами импульсы попадают на элемент 38 ИЛИ и далее на счетный вход счетчика 39.

По окончании измерения блок 36 синхронизации блокирует первый и второй ключи 27 и 28, одновременно открьгоая третий ключ 29. Затем блок синхронизации вырабатывает строб перезаписи содержимого счетчика 39 в выходной регистр 40. При этом, если измерение проводилось с добавлением калиброванного фазового сдвига 180° то старший разряд счетчика 39 предварительно инвертируется вторым управляемым инвертором 10 с целью компенсации калиброванной добавки в выходном коде.

Следующий цикл измерения начинается после установки третьего триггера 22 и привязан к переднему фронту опорного сигнала Х2. Блок 36 синхронизации работает следующим образом (фиг. 2 и 3).

Перед началом работы (на входе Работа/останов - лог. Г) триггер 41, 42 и счетчики 39 и 45 находятся в обнуленном состоянии. После появления на входе Работа/останов нулвого уровня первым импульсом записи признака калиброванного сдвига в третий триггер 22, поступившим на третий вход блока 36 синхронизации, взводится триггер 41, снимаюр ий бло кировку триггера 42. По переднему

10

0

5

1706

5

0

5

0

JO

фронту опорного сигнала Х2 ш-шульсом с третьего формирователя 5 -- иуль- сов, поступившим на первый вход блока 36 синхронизации, триггер 42 взводится, тем самым снимая сигнал сброса (фиг. 3, вых. 3)со счетчиков 39 и 45 и через элемент 44 И, разблокируя первый и второй ключи 27 и 28.

Начинается интервал измерения ( фиг.З, вых, 1J, который заканчивается с появлением лог. 1 в старшем задействованном разряде счетчика 45, при этом через инвертор 48 и элемент 44 И (вых. 1) блокируются первый и второй ключи 27 и 28 и разрешается прохождение сигналов через элементы 46 и 47 И, Сигнал с выхода элемента 46 И (вых. 2) осуществляет перезапись содержимого счетчика 39 в выходной регистр 40.

Сигнал с выхода элемента 47 И через элемент 43 ИЛИ обнуляет триггеры 41, 42 и счетчики 39 и 45.

При наличии на входе Работа/останов лог. О процесс подготовки и проведения измерения, описанный выше, повторяется о

Таким образом, при мальгх отношениям: сигнал/шум и слгщественной динамике изменения фазового сдвига предлагаемое устройство позволяет производить измерение с более высокой точностью по сравнению с прототипом в силу ТОГО} что на критических для фазометра триггерного типа (каковым и является прототип) участках фазовой характеристики обеспечивает переход на принцип измерения с перекрытием, дающий на этих участках большую точность.

Формула изобретения

Цифровой фазометр, содержащий генератор тактовых импульсов, блок синхронизации, счетчик, выходной регистр, четыре ключа, три триггера; сдвиговьй регистр, умножитель частоты, два управляе1« 1Х инвертора, два формирукщих блока, четыре формирователя импульсов, элемент ИЛИ и первый инвертор, причем входы первого и второго формирующих блоков соединены соответственно с первой и второй входными шинами фазометра, выход первох о формирующего блока подключен к первому входу первого управляемого инвертора, выход второго формиру-

01цего блока подключен к входам третьего и четвертого формирователей импульсов, входу последовательной записи сдвигового регистра и через y sнoжитeль частоты - к тактовому входу сдвигового регистра, выход первого управляемого инвертора через первьй и второй формирователи импульсов подключен к S-входам соответственно первого и второго триггеров, выход третьего формирователя импульсов соединен с первым входом блока синхронизации, второй вход которого соединен с первым выходом, генератора тактовых импульсов, первый выход блока синхронизации подключен к первым входам первого и второго ключей, вторые входы которых соединены соответственно с вторым и третьим выходами генератора тактовых импульсов, выходы первого и второго ключей подключены соответственно к первому и второму входам элемента ИЛИ, выход которого подключен к счетному входу счетчика, выходы счетчика с (in-n+l)-ro по (га-1)-й соединены с входами выходного регистра с первого по (п-1)-й соответственно, а пг-й выход счетчика соединен с первым входом второго управляемого инвертора, выход которого подключен к п-му входу выходного регистра, вход записи которого соединен с вторым выходом блока синхронизации, подключенного третьим выходом к установочному входу счетчика, отличающий- с я тем, что, с целью повьшения точности измерения сдвига фаз при малых отношениях сигнал/шум и высокой для данного времени измерения скорости изменения фазового сдвига, в него дополнительно введены третий, четвертый и пятый управляемые инверторы, второй инвертор, первый и второй элементы И, элемент ИСКЛЮЧАЮ1 ЩЕ ИЛИ, второй сдвиговый регистр на К разрядов, постоянный запоминающий блок, регистр хранения, четвертый - седьмой триггеры, мультиплексор, причем первьй вход третьего ключа через первьй инвертор подключен к первому, выходу блока синхронизации, третий вход которого соединен с выходом третьего ключа и С-входом третьего триггера, выход первого сдвигового регистра соединен с первым входом третьего управляемого инвертора, подключенного своим выходом

0

5

0

5

0

5

0

5

к входу последовательной записи второго сдвигового регистра, выходы которого с первого ,по К-й подключены к соответствующим адресным входам постоянного запоминающего блока, первый выход постоянного запоминающего блока соединен с первым входом параллельной записи регистра хранения, а второй выход - с вторым входом параллельной записи регистра хранения и D-входом третьего триггера, выход которого подключен к вторым входам первого, второго и третьего управляемых инверторов и первому; входу элемента ИСКЛЮЧАЮ1ПЕЕ ИЛИ, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к выходу второго разряда регистра хранения, выход первого разряда которого соединен с S-входом четвертого триггера, а вход записи соединен с вторым входом третьего ключа, R-входом пятого триггера и выходом второго формирователя импульсов, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к R-входу четвертого триггера, вьпсод которого через второй инвертор соединен с адресным входом мультиплексора и первым входом четвертого ключа, тактовьй вход второго сдвигового регистра соединен с S-входом пятого триггера, выходом первого формирователя импульсов и вторым входом четвертого ключа, соединенного своим выходом с С-входом шестого триггера, D-вход которого подключен к выходу второго формирукнцего блока, а инверсный выход - к первым входам четвертого и пятого управляемых инверторов, вторые входы которых соединены с выходами соответственно первого и второго элементов И, S-вход седьмого триггера подключен к R-входу первого триггера и выходу третьего формирователя импульсов, а R-вход седьмого триггера соединен с R-входом второго триггера и выходом четвертого формирователя импульсов, прямой выход пятого триггера и инверсный Ш11ход седьмого триггера подключены соответственно к первому и второму входам первого элемента И, инверсный выход пятого триггера и пря- . мой выход седьмого триггера соединены соответственно с первым и вторым входами второго элемента И, выходы первого и второго триггеров подключены соответственно к первому и второму входам мультиплексора, тре131511706 V1тий и четвертый входы которого сое- торов, а первьй и второй выходь; динены с выходами соответственно чет- мультиплексора - с третьиг- л; вхсдами coov- вертого и пятого управляемых инвер- ветственно первого и второго ключей

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1986 |

|

SU1368807A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

| Цифровой фазометр | 1980 |

|

SU938197A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Цифровой фазометр мгновенных значений | 1985 |

|

SU1320770A1 |

| Устройство для измерения параметров многополюсников | 1986 |

|

SU1478147A1 |

| Фазометр мгновенных значений | 1981 |

|

SU980015A1 |

| Цифровой фазометр | 1983 |

|

SU1128187A1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

Изобретение может быть использовано в фазометрах и преобразователях фаза-код. Цель изобретения - повышение точности измерения при малых отношениях сигнал-шум и высокой для данного времени измерения скорости изменения сдвига фаз входных сигналов. Для достижения цели в фазометр введены сдвиговый регистр 14, постоянный запоминающий блок 15, управляемые инверторы 11-13, инвертор 19, элементы И 34 и 35, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 17, регистр 16 хранения, триггеры 23-26 и мультиплексор 37 с их связями, что позволяет производить переключения в критических точках характеристики фазометра на формирование фазового интервала по триггерному принципу либо с перекрытием. Устройство содержит также генератор 31 тактовых импульсов, блок 36 синхронизации, счетчик 39, выходной регистр 40, ключи 27-30, триггеры 20-22, сдвиговый регистр 7, умножитель 8 частоты, управляемые инверторы 9 и 10, формирующие блоки 1 и 2, формирователи 3-6 импульсов, элемент ИЛИ 38 и инвертор 18. 3 ил.

ffx.1

бтхЪ 8шЛ Вх 2

п

л

Л

ляшшллшттггиь „ ™

Ст. разряд

cvemt/i/ a

5

вмх2- вых.НЛИФиг. г

JL.-„

фиг,3

| Цифровой фазометр | 1980 |

|

SU938197A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой фазометр | 1982 |

|

SU1092430A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-09-30—Публикация

1988-02-29—Подача