Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации, использующих для обмена биполярный код1.

Цель изобретения - расширение области использования преобразователя за счет обеспечения режима работы Обмен по готовности.

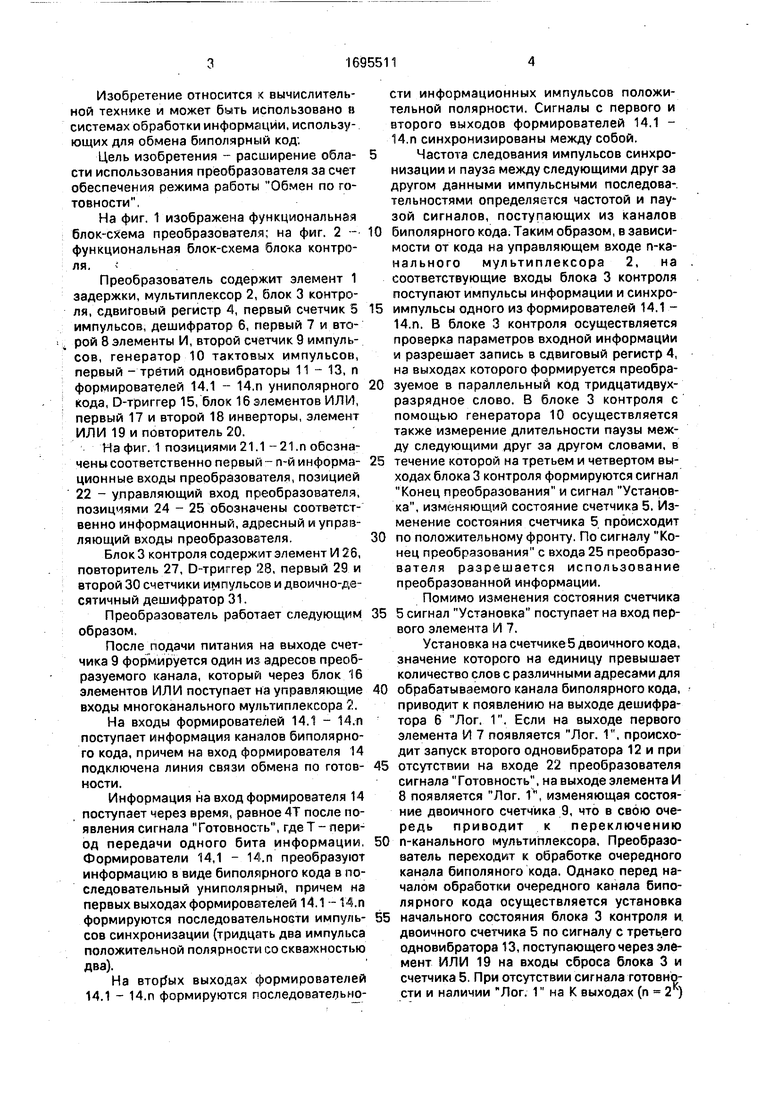

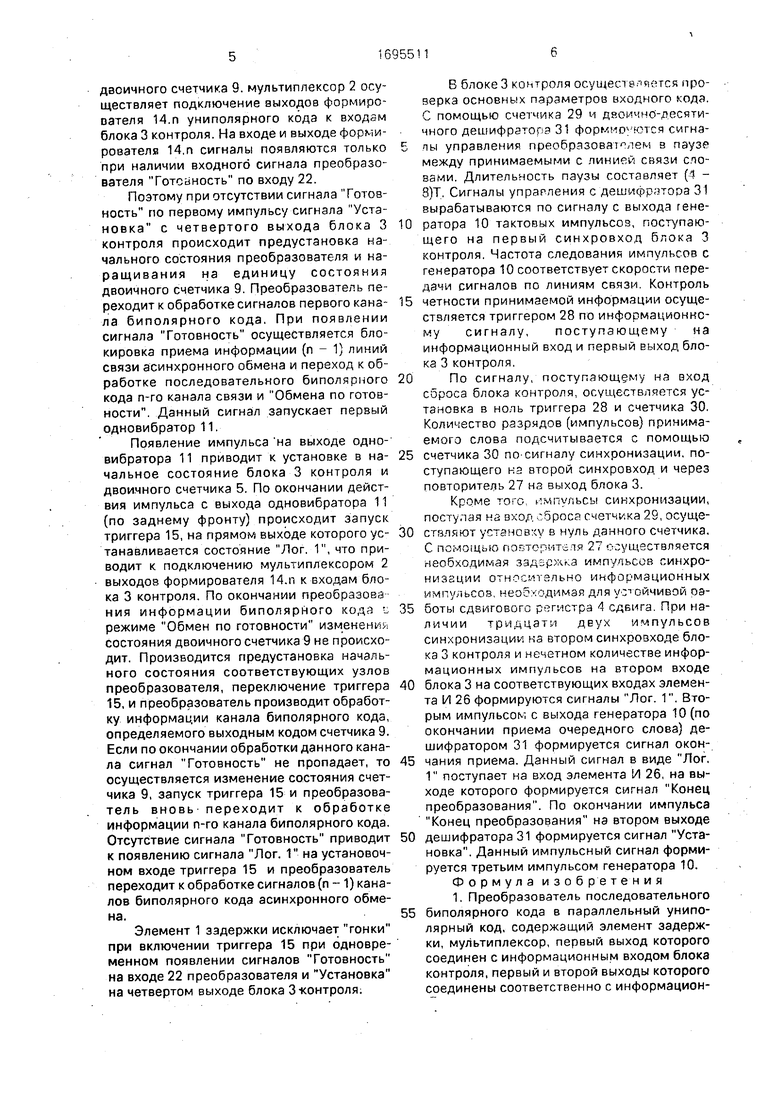

На фиг. 1 изображена функциональная блок-схема преобразователя; на фиг. 2 - функциональная блок-схема блока контроля.

Преобразователь содержит элемент 1 задержки, мультиплексор 2, блок 3 контроля, сдвиговый регистр 4, первый счетчик 5 импульсов, дешифратор 6, первый 7 и второй 8 элементы И, второй счетчик 9 импульсов, генератор 10 тактовых импульсов, первый - третий одновибраторы 11 - 13, п формирователей 14.1 - 14.п униполярного кода, Ь-триггер 15, блок 16 элементов ИЛИ, первый 17 и второй 18 инверторы, элемент ИЛИ 19 и повторитель 20.

На фиг. 1 позициями 21.1 -21.п обозначены соответственно первый -n-й информационные входы преобразователя, позицией 22 - управляющий вход преобразователя, позициями 24 - 25 обозначены соответственно информационный, адресный и управляющий входы преобразователя.

Блок 3 контроля содержит элемент И 26, повторитель 27, D-триггер 28, первый 29 и второй 30 счетчики импульсов и двоично-десятичный дешифратор 31.

Преобразователь работает следующим образом.

После подачи питания на выходе счетчика 9 формируется один из адресов преобразуемого канала, который через блок 16 элементов ИЛИ поступает на управляющие входы многоканального мультиплексора 2. На входы формирователей 14.1 - 14.п поступает информация каналов биполярного кода, причем на вход формирователя 14 подключена линия связи обмена по готовности.

Информация на вход формирователя 14 поступает через время, равное 4Т после появления сигнала Готовность, где Т- период передачи одного бита информации. Формирователи 14,1 - 14.п преобразуют информацию в виде биполярного кода в последовательный униполярный, причем на первых выходах формирователей 14.1 - 14.п формируются последовательности импульсов синхронизации (тридцать два импульса положительной полярности со скважностью два).

На выходах формирователей 14.1 - 14.п формируются последовательности информационных импульсов положительной полярности, Сигналы с первого и второго выходов формирователей 14.1 - 14.п синхронизированы между собой.

Частота следования импульсов синхронизации и пауза между следующими друг за другом данными импульсными последовательностями определяется частотой и паузой сигналов, поступающих из каналов

0 биполярного кода. Таким образом, в зависимости от кода на управляющем входе п-ка- нального мультиплексора 2, на соответствующие входы блока 3 контроля поступают импульсы информации и синхро5 импульсы одного из формирователей 14.1 - 14,п. В блоке 3 контроля осуществляется проверка параметров входной информации и разрешает запись в сдвиговый регистр 4, на выходах которого формируется преобра0 зуемое в параллельный код тридцатидвухразрядное слово. В блоке 3 контроля с помощью генератора 10 осуществляется также измерение длительности паузы между следующими друг за другом словами, в

5 течение которой на третьем и четвертом выходах блока 3 контроля формируются сигнал Конец преобразования и сигнал Установка, изменяющий состояние счетчика 5. Изменение состояния счетчика 5 происходит

0 по положительному фронту. По сигналу Конец преобразования с входа 25 преобразователя разрешается использование преобразованной информации.

Помимо изменения состояния счетчика

5 5 сигнал Установка поступает на вход первого элемента И 7.

Установка на счетчике 5 двоичного кода, значение которого на единицу превышает количество слов с различными адресами для

0 обрабатываемого канала биполярного кода, приводит к появлению на выходе дешифратора 6 Лог. 1. Если на выходе первого элемента И 7 появляется Лог. 1, происходит запуск второго одновибратора 12 и при

5 отсутствии на входе 22 преобразователя сигнала Готовность, на выходе элемента И 8 появляется Лог. 1, изменяющая состояние двоичного счетчика 9, что в свою очередь приводит к переключению

0 n-канального мультиплексора, Преобразователь переходит к обработке очередного канала биполяного кода. Однако перед началом обработки очередного канала биполярного кода осуществляется установка

5 начального состояния блока 3 контроля и двоичного счетчика 5 по сигналу с третьего одновибратора 13, поступающего через элемент ИЛИ 19 на входы сброса блока 3 и счетчика 5. При отсутствии сигнала готовности и наличии Лог. Г на К выходах (п 2 )

двоичного счетчика 9 мультиплексор 2 осуществляет подключение выходов формирователя 14 п униполярного кода к входам блока 3 контроля. На входе и выходе формирователя 14.п сигналы появляются только при наличии входного сигнала преобразователя Готовность по входу 22

Поэтому при отсутствии сигнала Готовность по первому импульсу сигнала Установка с четвертого выхода блока 3 контроля происходит предустановка начального состояния преобразователя и наращивания на единицу состояния двоичного счетчика 9 Преобразователь переходит к обработке сигналов первого канала биполярного кода. Пои появлении сигнала Готовность осуществляется блокировка приема информации (п - 1) линий связи асинхронного обмена и переход к обработке последовательного биполярного кода п-го канала связи и Обмена по готовности. Данный сигнал запускает первый одновибратор 11.

Появление импульса на выходе одно- вибратора 11 приводит к установке в начальное состояние блока 3 контроля и двоичного счетчика 5. По окончании действия импульса с выхода одновибратора 11 (по заднему фронту) происходит запуск триггера 15, на прямом выходе которого устанавливается состояние Лог. 1, что приводит к подключению мультиплексором 2 выходов формирователя 14.п к входам блока 3 контроля. По окончании преобразования информации биполярного кода L режиме Обмен по готовности изменение состояния двоичного счетчика 9 не происходит. Производится предустановка начального состояния соответствующих узлов преобразователя, переключение триггера 15, и преобразователь производит обработку информации канала биполярного кода, определяемого выходным кодом счетчика 9. Если по окончании обработки данного канала сигнал Готовность не пропадает, то осуществляется изменение состояния счетчика 9, запуск триггера 15 и преобразователь вновь переходит к обработке информации n-го канала биполярного кода. Отсутствие сигнала Готовность приводит к появлению сигнала Лог. 1 на установочном входе триггера 15 и преобразователь переходит к обработке сигналов (п -1) каналов биполярного кода асинхронного обмена.

Элемент 1 задержки исключает гонки при включении триггера 15 при одновременном появлении сигналов Готовность на входе 22 преобразователя и Установка на четвертом выходе блока 3-контроля.

В блоке3 контроля осуществляется проверка основных параметров входного кода С помощью счетчика 29 и дроиччо-десяти- чного дешифратора 31 форм о4 «от с я сигнэ- 5 лы управления преобразователем в паузе1 между принимаемыми с пинией связи словами. Длительность паузы составляет ( - 8)Т. Сигналы упрагления с дешифратора 31 вырабатываются по сигналу с выхода гене0 ратора 10 тактовых импульссз, поступающего на первый синхровход блока 3 контроля. Частота следования импульсов с генератора 10 соответствует скорости передачи сигналов по линиям связи Контроль

5 четности принимаемой информации осуществляется триггером 28 по информационному сигналу, поступающему на информационный вход и первый выход блока 3 контроля.

0По сигналу, поступающему на вход

сброса блока контроля, осуществляется установка в ноль триггера 28 и счетчика 30. Количество разрядов (импульсов) принимаемого слова подсчитывается с помощью

5 счетчика 30 по сигналу синхронизации, поступающего на второй синхровход и через повторитель 27 на выход блока 3.

Кроме того ПМПУЛЬСЫ синхронизации, поступая на вход оброс счетчика 29, осуще0 ствляют установку в нуль данного счетчика. С помощью повторит-то 27 осуществляется необходимая зэдзрхгз имп/пьсов синхронизации от носит епьно информационных импульсов, неоочэдимая для устойчивой оэ5 боты сдвигового регистра 4 сдвига При наличии тридцати двух импульсов синхронизации на втором синхровходе блока 3 контроля и нечетном количестве информационных импульсов на втором входе

0 блока 3 на соответствующих входах элемента И 26 формируются сигналы Лог. 1. Вторым импульсом с выхода генератора 10 (по окончании приема очередного слова) дешифратором 31 формируется сигнал окон5 чания приема. Данный сигнал в виде Лог. 1 поступает на вход элемента И 26, на выходе которого формируется сигнал Конец преобразования, По окончании импульса Конец преобразования на втором выходе

0 дешифратора 31 формируется сигнал Установка. Данный импульсный сигнал формируется третьим импульсом генератора 10. Формула изобретения 1. Преобразователь последовательного

5 биполярного кода в параллельный униполярный код, содержащий элемент задержки, мультиплексор, первый выход которого соединен с информационным входом блока контроля, первый и второй выходы которого соединены соответственно с информационным и тактовым входами сдвигового регистра, первый и второй выходы которого являются соответственно информационным и адресным выходами преобразователя, первый счетчик импульсов, выходы которого со- единены с соответствующими первыми входами дешифратора, выход которого соединен с первым входом первого элемента И, второй элемент И, выход которого соединен с входом второго счетчика импульсов, третий выход блока контроля является управляющим выходом преобразователя, отличающийся тем, что, с целью расширения области использования преобразоватепя за счет обеспечения режима работы Обмен по готовности, в преобразователь введены генератор тактовых импульсов, одновибра- торы, п формирователей униполярного кода (п 1, N - разрядность входного кода), D-триггер, блок элементов ИЛИ, инверторы, элемент ИЛИ и повторитель, выход которого соединен через первый одновиб- ратор с первым входом элемента ИЛИ и через последовательно соединенные первый инвертор и элемент задержки с установочным входом D-триггера, инверсный выход которого соединен с первым входом второго элемента И и с D-входом D-триггера, выход первого элемента И соединен с входом второго одновибрато а, прямой выход которого соединен с вторым входом второго элемента И, инверсный выход второго одновибратора соединен через третий од- новибратор с вторым входом элемента ИЛИ, выход которого непосредственно соединен с входами сброса блока контроля и первого счетчика импульсов и через второй инвертор с синхровходом D-триггера, прямой выход которого соединен с вторым входом дешифратора и первым входом блока элементов ИЛИ, выходы которого соединены с соответствующими входами управления мультиплексора и с третьими входами дешифратора, выход генератора тактовых импульсов соединен с первым синхровходом блока контроля, четвертый выход которого соединен с вторым входом первого элемента И и с синхровходом первого счетчика импульсов, выходы второго счетчика импульсов соединены с соответствующими

вторыми входами блока элементов ИЛИ, первые выходы формирователей униполярного кода соединены с соответствующими первыми информационными входами мультиплексора, вторые выходы - ссоответствующими вторыми информационными входами мультиплексора, второй выход которого соединен с вторым синхровходом блока контроля, входы формирователей униполярного кода являются соответственно одноименными информационными входами преобразователя, вход повторителя является управляющим входом преобразователя.

2. Преобразователь по п. 1, от л и ч а.ющ и и с я тем, что блек контроля выполнен на элементе И, повторителе, D-триггере, счетчиках импульсов и двоично-десятичном дешифраторе, первый выход которого сое- . динен с первым входом элемента И, выходы

разрядов первого счетчика импульсов соединены с соответствующими входами двоично-десятичного дешифратора, прямой выход D-триггера соединен с вторым входом элемента И, выход старшего разряда

второго счетчика импульсов - с третьим входом элемента И, инверсный выход D-триггера - с D-входом D-триггера, синхровход первого счетчика импульсов является первым синхровходом блока, синхровход Dтриггера - информационным входом и первым выходом блока, установочный вход D-триггера объединен с входом сброса второго счетчика импульсов и является входом сброса блока, синхровход второго счетчика

импульсов объединен с входом повторителя и входом сброса первого счетчика импуль1- сов и является вторым синхровходом блока, выходы повторителя, элемента И и второй выход двоично-десятичного дешифратора

являются соответственно вторым, третьим и четвертым выходами блока.

/

ОО

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ РЕЗЕРВИРОВАНИЯ РАДИОСТАНЦИЙ | 1990 |

|

RU2018939C1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Устройство для ввода учебной информации | 1990 |

|

SU1732369A1 |

| Устройство для контроля коммутации информационных каналов | 1982 |

|

SU1120333A1 |

| Устройство для отображения информации | 1984 |

|

SU1354182A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах обработки информации, использующих для обмена биполярный код. Изобрел ГлГ ние позволяет производить преобразова-, ние биполярного кода не только при асинхронном приеме, но и в Обмен по готовности, что расширяет область применения преобразователя. Преобразователь содержит элемент 1 задержки, мультиплексор 2, блок 3 контроля, сдвиговый регистр 4, счетчики 5 и 9 импульсов , дешифратор 6 , элементы И 7 и 8 .генератор 10 тактовых импульсов , одновибрато- ры 11 -13 , п формирователей 14.1 -14 п униполяторного кода , D-триггер 15 , блок 16 элемент ИЛ И,инверторы 17 и 18, элемент ИЛИ 19 и повторитель 20.Бяок 3 контроля выполнен на элементе И, . повторителе , D- триггере , счетчиках импульсов и двоично- десятичном дешифраторе . 1 з.п. ф-лы , 2 ил. сл с о о сл сл

г

J

MNfr-Co

Сд |tfc

1

s

lu;

I

| Устройство для преобразования последовательного кода в параллельный | 1986 |

|

SU1361725A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР Мг 1366029, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-11-30—Публикация

1989-04-18—Подача