вой и второй групп, с тактовыми входами первого и второго триггеров и с первым входом элемента ИЛИ первого и второго логического анализа, второй выход распределителя тактовых импульсов соединен с вторыми входами элементов ИЛИ первой группы, вторыми входами элементов И третьей группы и первым входом,первого элемента И первого и второго блоков логического анализа, третий выход распределителя тактовых импульсов и выход узла группировки разрядов щодкЛйчень: соответственно к первому и второму управляющим входам дешифраторов нуля первого и второго блоков логического анализа, вход запуска устройства подключен к входам обнуления первого и второго триггеров первого и второго

6426

блоков логического анализа, при этом в каждом, блоке логического анализа выход переполнения сумматора подключен к информационным входам первого и третьего триггеров, выход первого триггера подключен к входу переноса сумматора и к входу элемента НЕ,выход которого соединен с первым входом второго элемента И, выход которого является выходом данного блока логического анализа, а второй вход соединен с выходом второго триггера,информационный вход которого соединен с выходом дешифратора нуля, выход .. третьего триггера подгшючен к второму входу первого элемента И, выход которого соединен с вторым входом элемента ИШ, выход которого подключен к управляющему входу регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| Устройство для поиска чисел в заданномдиАпАзОНЕ | 1979 |

|

SU822179A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Автоматический мост переменного тока | 1984 |

|

SU1213423A1 |

| Устройство для логарифмирования | 1978 |

|

SU711560A1 |

| Устройство для цифровой индикации | 1972 |

|

SU445053A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Устройство для поиска чисел в заданном диапазоне | 1985 |

|

SU1260945A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сортировки информации | 1985 |

|

SU1278834A1 |

УСТРОЙСТВО ДПЯ ПОИСКА ЧИСЕЛ В ЗАДАННОМ ДИАПАЗОНЕ, содержащее регистр входных чисоп, регистр цеитра .диапазона, генератор тактовых импуль.сов,узел группировки, узел вьщеления такта старшей декады, блок логического анализа и элемент ИЛИ, причем вход регистра входных чисел подключен к информационному входу устройства, вход регистра центра диапазона подключен к задающему входу устройства, выход блока логического анализа под1слючен к первому входу элемента ИЛИ, вход генератора тактовых импульсов подключен к входу запуска устройства, а выход - к входам узла группировки . разрядов и узла выделения такта старшей декады, о тличающееся тем, что, с целью повышения быстродействия устройство содержит распределитель тактовых импульсов, второй блок логического анализа, триггер и две группы элементов НЕ, при этом блок логического анализа содержит группы элементов И, группы элементов ШШ, дешифратор нуля, сумматор, регистр, три триггера, два элемента И, элемент ИЛИ и элемент НЕ, при этом выход генератора тактовых импульсов подключенк входу распределителя тактовых импульсов, выход узла выделения такта старшей декады подключен к тактовому входу триггера, выход которого является выходом устройства, а информационный вход подключен к выходу элемента , второй вход которого подключен к выходу второго блока логического анализа, выход генератора тактовых импульсов подключен к входам управления сдвигом регистра входных чисел и регистра центра диапазона, выходы младших декад которых подключены к входам элементов НЕ соответственно первой и второй групп, первые входы элементов И первых групп первого и второго блоков логического анализа, подключены к выходам младших декад регистра входных чисел и регистра центра диапазона соответственно,первые входы элементов 2 И вторых групп первого и второго блоков логического анализа подключены к выходам элементов НЕ второй и пер вой групп соответственно, в каждом блоке логического анализа выходы элементов И первой и второй групп нодкпючены к первым .входам элементов ИЛИ первой и второй групп соотйетственно, выходы которых подключены к входам первой и второй групп сумматора,выходы разрядов которого подключены к информа1шонным входам регистра, выходы разрядов которого подключены к информационным входам дешифратора нуля и первым входам элементов И третьей группы, выхода которых соединены с вторыми входами элементов ИЛИ второй группы, первый выход .распределителя тактовых импульсов соедит ней с вторыми входами элементов И пер-

Изобретение относится к вычисли-г: тельной технике и может быть использовано в устройствах обработки цифровой радиолокационной информации.

Известно устройство для поиска чисел в заданном диапазоне, содержащее регистры чисел, блоки сравнения,триггеры, регистр значений границ диапазона С I -5 .

Недостатки- ; указанного устройства состоят в его сложности и низком быстродействии.

Наиболее близко к предлагаемому устройство для поиска чисел в заданном диапазоне, содержащее регистры, генератор тактовых сигналов, формирователи тактовых сигналов, элементы И, ИЛИ, НЕ, триггеры, дешифратор, сумматор и сдвигающий регистр 2 .

Однако и данное устройство имеет недостаточное быстродействие.

Цель изобретения - повышение быстродействия, устройства,

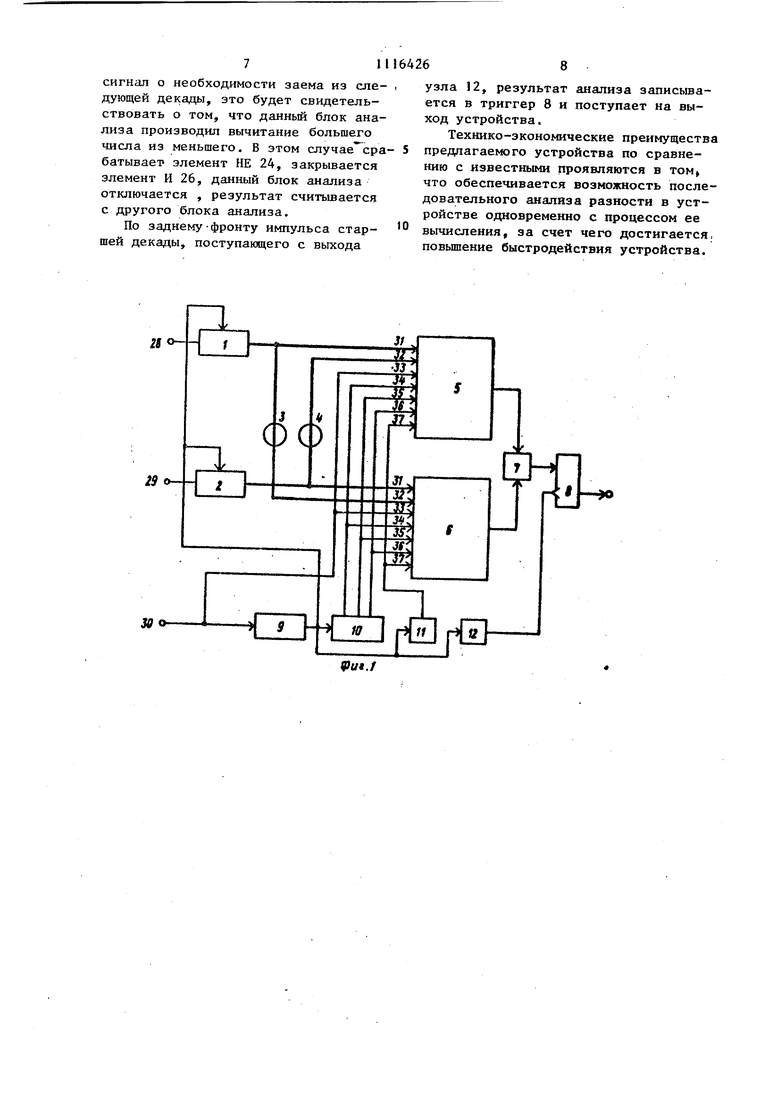

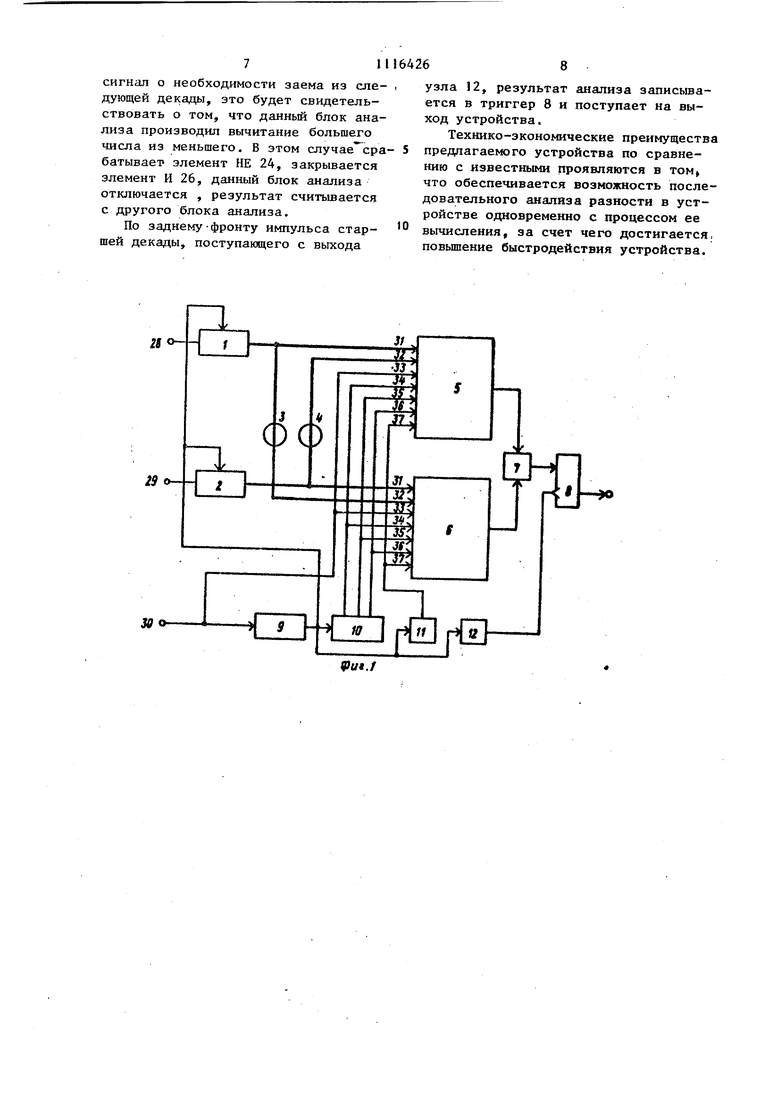

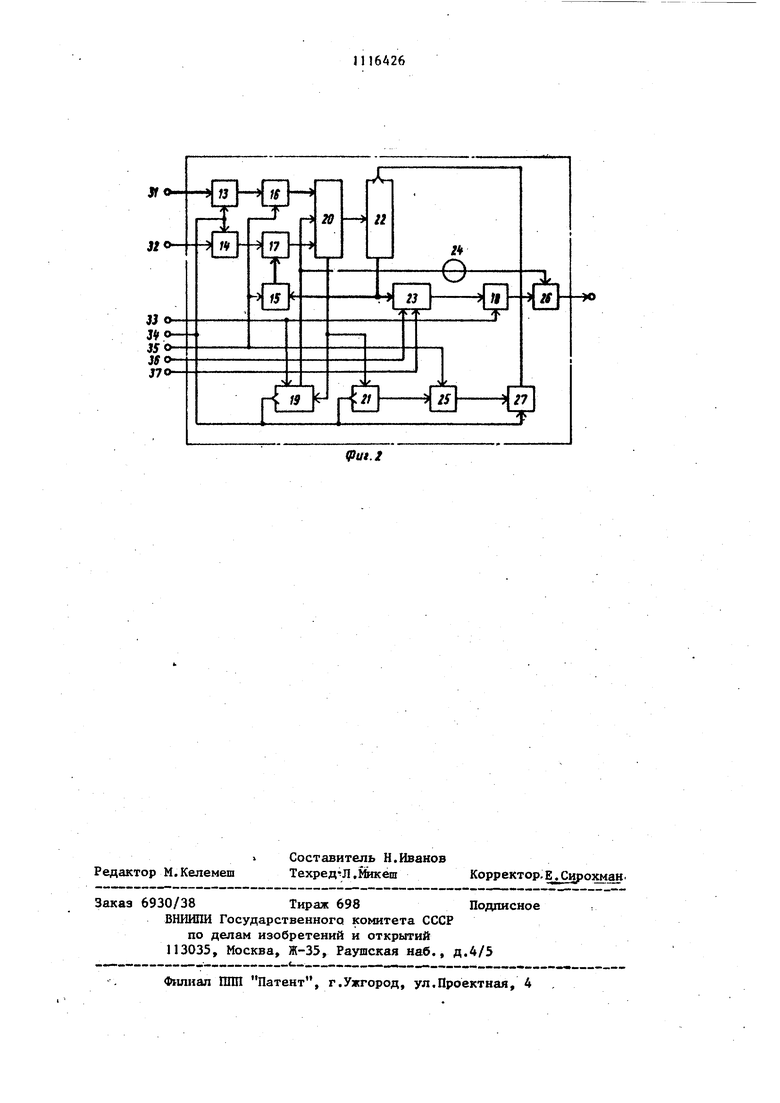

Поставленная цель достигается тем, что в устройство для поиска чисел в заданном диапазоне, содержащее регистр входных чисел, регистр центра диапазона, генератор тактовых импульсов, узел группировки, узел выделения такта старшей декады, блок логического анализа и элемент ИЛИ, причем вход регистра входиьпс чисел подключен к информационному входу устройства, вход .регистра центра диапазона подключен к задающему входу устройства, выход .блока логического анализа подключен к первому входу элемента ШШ, вход генератора тактовых импульсов подключен к входу запуска устройства, а выход - к входам узла группировки разрядов и узла выделе ния такта старшей декады, введены распределитель тактовых- импульсов, второй блок логического анализа,триггер и две группы элементов НЕ, при этом каждый блок логического анализа содержит, группы элементов И, группы элементов Ш1И, дешифратор нуля, сумматор, регистр, три триггера, два элемента И, элемент Ш1И и элемент НЕ, при этом выход генератора тактовых импульсов подключен;к входу распределителя тактовых импульсов, выход узла вьщеления такта старшей декады подключен к тактовому входу триггера, выход которого является выходом устройства, а информационный вход подключен к выходу элемента ИЛИ,второй вход которого подключен к выходу второго блока логического анализа, выход генератора тактовых импульсов подключен к входам управления сдвигом регистра входных чисел и регистра центра диапазона, выходы младших декад которых подключены к входам элементов НЕ соответственно первой и второй групп, первые входы элементов И первых,групп первого и второго бло ков логического анализа подключены к выходам младших декад регистра вхо ных чисел и регистра центра диапазона соотвественно, первые входы эле.ментов И вторых групп первого и второго блоков логического анализа подключены к выходам элементов НЕ вто.рой и первой групп соответственно,в каждом блоке логического анализа выходы элементов И первой и второй - групп подключены к первым входам элементов ИЛИ первой и второй групп соот ветственно, выходы которых подключены к входам первой и второй групп сумматора, выходы разрядов которого под ключены к информационным входам регистра, выходы разрядов которого под ключены к информационным входам дешифратора нуля и первым входам элементов И третьей группы, выходы кото рых соединены с вторыми входами элементов ИЛИ второй группы, первый выход рапределителя тактовых импульсов соединен с вторыми входами элементоэ И первой и второй групп, с тактовыми входами первого и второго триггеров и с первым входом элемента ИЛИ перво го и второго блоков логического анализа, второй выход распределителя тактовых импульсов соединен с вторыми входами элементов ШШ первой груп пы, вторыми входами элементов И трет ей группы и первым входом первого элемента И первого и второго блоков логического анализа, третий выход распределителя тактовых импульсов и выход узла группировки разрядов подключены соответственно к первому и второму управляющим входам дешифраторов нуля первого и второго блоков логического анализа,вход запуска устройства подключен к входам обнуления первого и второго триггеров первого и второго блоков логического анализа, при этом в каждом блоке логического анализа выход переполнения сумматора подключен к информационным входам первого и третьего тригге ров, выход первого триггера подключен к вхбду переноса сумматора и к входу элемента НЕ, выход которого соединен с первым входом второго элемента И, выход которого является выходом данного блока логического анализа, а второй вход соединен с выходом второго триггера, информационный вход которого соединен с выходом дешифратора нуля, выход третьего триггера Подключен к второму входу первого элемента И выход которого соединен с вторым входом элемента ШШ, выход которого подключен к управляющему входу регистра. На фиг. I представлена блок-схема предлагаемого устройства для поиска чисел в заданной диапазоне; на фиг.2t. блок-схема блошка логического анализа. Устройство содержит регистр 1 входных чисел, регистр 2 центра диапазона, группы элементов НЕ 3 и 4, блоки 5 и 6 логического анализа, элемент ИЛИ 7, триггер 8, генератор 9 тактовых импульсов, распределитель 10 тактовых импульсов, узел И группировки и узел12 выделения такта старшей декады. Блоки 5 и 6 логического анализа содержат группы элементов И 13, 14 и 15, группы элементов ИЛИ 16 и 17, триггеры 18 и 19, сумматор 20,триггер 21, регистр 22, дешифратор 23 нуля, элемент НЕ 24, элементы И 25 26, элемент ШШ 27.Устройство имеет информационный вход 28, заданиций вход 29, вход 30 запуска. Елок 5 (6) имеет входы 3137. Устройство работает следующим образом. В регистр 2 вводится двоично-десяг тичное число А - центр диапазона в регистр 1 вводятся поочередно двоич5-десятичные числа X, подлежащие анализу. По окончании ввода в регистр 1 каждого очередного числа на вход Запуск устройства подается пусковой импульс; Этот импульс устанавливает в исходное состояние триггеры 19 и 18 блоков 5 (6) логического анализа и запускает генератор 9 тактовых импульсов, формирующий серию тактовых импульсов. сло тактовых импульсов соответствует количеству, де °° входных двоично-десятичных числах. Начиная с младших декад,чиса с регистров 1 и 2 начинают поступать на входы 31 и 32 блоков 5 и 6 огического анализа. Принадлежность чисел зад,анно1.- диапазону определяется путем подекадного вычисления.разности между входными числами X и числом А (центром диа пазона) с одновременным анализом получаемой разности. Если разность по абсолютной величине не превьппает половины заданного диапазона поиска, то анализируемое число считывается принадлежащим диапазону. Поскольку заранее неизвестно какое из чисел А или X больше, в устройстве имеются два параллельно работающих блока 5 и 6-логического анализа. В блоке 5 производит.ся вычитание Х-А, в блоке 6 вычисляется А-Х,одновременно производится анализ каждой из этих разностей. При вычитании пос ледних старших декад чисел А и X ста .новится известно какое из этих двух чисел больше, одновременно заканчивается анализ обоих значений разности. Результат анализа снимается с выхода того из блоков 5 или 6, в котором производилось вычитание меньше го числа из большего. . Через элемент ИЛИ 7 по импульсу уз ла 12 выделения такта старшей декады результат анализа записывается в три гер 8, где хранится до окончания ана лиза следующего числа X. Выход тригrfepa 8 является выходом устройства. Каждый из блоков 5 и 6 логического анализа производит подекадное вычитание поступающих на входдз 31 и 32 двоично-де.сятичных чисел с одновременным анализом получаемой разности. Для упрощения понимания блок-схем фиг. 1 и фиг. 2 связи, по которым происходит передача декад параллельным четырехразрядным кодом, обозначены толстыми стрелками.

По каждой декаде работа блоков 5,6 производится в три такта. По такту Т(| , поступающему с распределителя 10

тактовых импульсов на входы 34 блоков вательно, величина диапазона поиска

5 и 6, открьшаются группы элементов определяются количеством такИ 13 и 14, чер.ез.которые на параллель-, старших декад, группируемых узный четырехразрядный сумматор 20 поступает очередная декада вычитаемых

чисел. По заднему фронту такта Т. , 50в момент времени Т проверяется напрошедшему через элемент ИЛИ 27, про- декаде. Любая изводится запись некорректированной единица в старших разрядах кода

декады разности в четырехразрядныйразности вызовет срабатывание тригге регистр 22. Одновременно устанавлива-Р произойдет пропадание на выхоются в состояние,соответствующее cnrk5SДе блока анализа сигнала принадлежносналу на выходе переноса сумматора 20, .

триггер 19 переноса в следукяцую дека- Если в MOMeat вычитания последней

ду и триггер 21 |фррекции.,старшей декады разности возникает

в старших декадах кода разности.

Количество проверяемых на отсутствие единиц старших декад и, следолом 11 группировки. По каждому из. сгруппированных тактов старших декад lio такту Т, ,поступающему с распределителя10 тактовых импульсов на входы 35 блоков 5 и 6,.осуществляется коррекция полученной декады разности. Для этого на один из входов сумматора 20 через группу элементов И 15 к группу элементов ИЛИ 17 подключается некорректированная декада разности с выхода регистра 22, а на другой вход сумматора 20 через группу элементов ИЛИ 16 подается импульс такта Т , обеспечивая тем самым существование на данном входе сумматора 20 параллельного корректирующего кода 1010 (десять).Если в это время триггер 21 коррекции дает команду на коррекцию,т.е. коррекция необходима, то элемент И 25 открыт, и по з.аднему фронту импульса TQ , прошедшему по цепи элемент И 25, элемент.ИЛИ 27, в регистр 22 запишется коректированное значение данной декады разности. По такту Т , поступающему с распределителя 10 на вход 36 блоков 5 и 6, производится анализ полученной декады разности. Анализ разности чисел А и X основан на том факте, что о величине разности можно судить по наличию единиц в старших декадах разности. Например, если числа содержат четыре декады, а в двух старших декадах разности нет ни одной единицы, то разность не может превышать числа 99 (код 0000 0000 1001 1001), которое в данном случае и будет соетавлять половину диапазона поиска чисел при любом заданном числе А .-..центре диапазона, превышающем число 99. Таким образом, задача определения принадлежности числа диапазону сводится к проверке наличия всех нулей сигнал о необходимости заема из следующей декады, это будет свидетельствовать о том, что данный блок анализа производил вычитание большего числа из меньшего. В этом случае ера батывает элемент НЕ 24, закрывается элемент И 26, данный блок анализа отключается , результат считьшается с другого блока анализа. По заднемуфронту импульса старшей декады, поступающего с выхода узла 12, результат анализа записывается в триггер 8 и поступает на выход устройства. Технико-экономические преимущества предпагаемого устройства по сравнению с известными проявляются в том что обеспечивается возможность последовательного анализа разности в устройстве одновременно с процессом ее вычисления, за счет чего достигается, повьшенне быстродействия устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для поиска чисел в заданномдиАпАзОНЕ | 1979 |

|

SU822179A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-09-30—Публикация

1982-04-26—Подача