1 (61)

(21)14357381/2 t-2

(22)05.01.88

(А6) 15.10.89. Бюл. IP 38

(71)Тернопольский финансово-экономический институт

(72)А.А.Саменко, В.В.Кочан, В.И.Матвиив и Б.А.Маслыяк (53) 681.325 (088.8)

(56)Авторское свидетельство СССР fP Й1197А, кл. Н 03 М 1/52, 1985.

(Sk) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ДВУХТАКТНОГО ИНТЕГРИРОВАНИЯ

(57)Изобретение относится к измерительной и вычислительной технике, в частности к преобразованиям в цифровой код напряжения постоянного тока низкого уровня. Целью изобретения является повышение точности аналого-цифрового преобразования.,Это достигается тем, что в преобразователь введен делитель частоты, вход которого объединен с вторым входом формирователя временных интервалов, а выход подключен к дополнительному входу первого ключа, который выполнен на основе двух элементов И-НЕ. Преобразователь содержит пять ключей, усилитель, резисторы, интегратор на операционном усилителе и первом накопительном эле-, менте, компаратор, источник образцового напряжения, делитель частоты, второй накопительный элемент, генератор тактовых импульсов, формирователь импульсов, элемент И,, счетчик, формирователь временных интервалов, инвертор и элемент ИЛИ. 1 з.п. ф-лы, 2 ил.

с S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1988 |

|

SU1547064A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1697265A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1674373A2 |

| Помехоустойчивый преобразователь напряжения в интервал времени | 1985 |

|

SU1283972A1 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| Интегрирующий аналого-цифровой преобразователь | 1986 |

|

SU1314458A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

Изобретение относится к измерительной и вычислительной технике, в частности к преобразованиям в цифровой код напряжения постоянного тока низкого уровня. Целью изобретения является повышение точности аналого-цифрового преобразования. Это достигается тем, что в преобразователь введен делитель частоты, вход которого объединен с вторым входом формирователя временных интервалов, а выход подключен к дополнительному входу первого ключа, который выполнен на основе двух элементов И-НЕ. Преобразователь содержит пять ключей, усилитель, резисторы, интегратор на операционном усилителе и первом накопительном элементе, компаратор, источник образцового напряжения, делитель частоты, второй накопительный элемент, генератор тактовых импульсов, формирователь импульсов, элемент И, счетчик, формирователь временных интервалов, инвертор и элемент ИЛИ. 1 з.п. ф-лы, 2 ил.

Изобретение относится к электроизмерительной и вычислительной технике, в частности, для преобразования в цифровой код напряжения постоянного тока низкого уровня.

Целью изобретения является повышение точности.

На фиг.1 показана функциональная схема преобразователя; на фиг.2 - схема первого ключа.

Аналого-цифровой преобразователь (АЦП) содержит ключи 1 и 2, входной усилитель 3, резистор k, интегратор на операционном усилителе 5 и первом накопительном элементе, выполненном на конденсаторе 6, ключи 7 и 8, компаратор 9, источник 10 образцового

напряжения с резистором 11, цепь коррекции дрейфа нуля, состоящая из второго накопительного элемента, выпол-; ненного на конденсаторе 12, и ключа 13, а также генератор l тактовых импульсов (ГТИ), формирователь 15 импульсов, элемент И 1б и счетчик 17, формирователь 18 временных интервалов (ФВИ), инвертор 19, элемент ИЛИ 20, делитель 21 частоты.

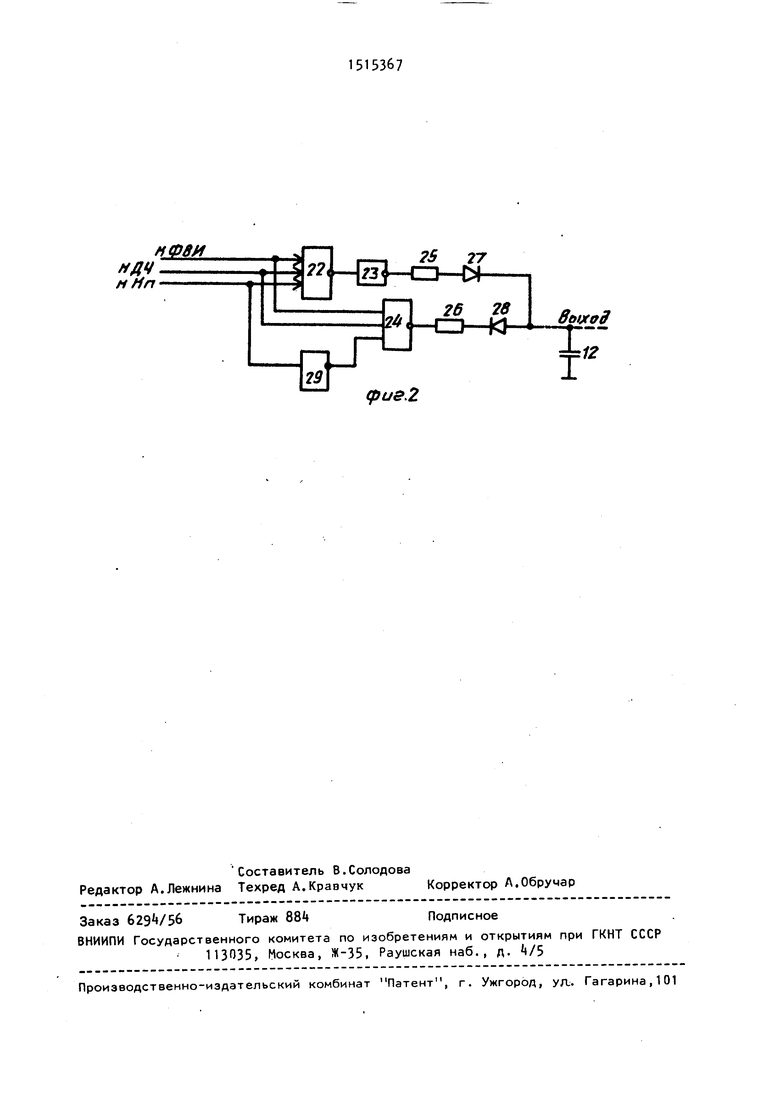

Ключ 13 (фиг.2) выполнен на первом элементе И-НЕ 22, первом инверторе 23, втором элементе И-НЕ 2, первом 25 и . втором 26 резисторах, первом 27 и втором 28 диодах и втором инверторе 29.

Аналого-цифровой преобразователь работает следующим обра,зом.

СП

ел

со

Од

sj

1Ч

В исходном состоянии ключ 1 закрыт, а остальные ключи 2, 7, 8 и 13 открыты. За счет действия источника 10 образцового напряжения и резисторов с и 11 на входе операционного усилителя Б интегратора образуется отрицательное смещение (с учетом дрейфа усилителя 3), которое благодаря действию обратной связи через ключ 13 запоминается ю на конденсаторе 12.

Обратная связь через ключ 13 и запоминающий конденсатор 12 действует следующим образом.

Сигнал ФВИ 18 разрешает работу клю-15 ча 13 (фиг.2). Сигнал на выходе компаратора 9 управляет прохождением импульсов делителя частоты на выход ключа 13 через первый 27 или второй 28 диоды. В первом случае происходит за- 20 ряд запоминающего конденсатора 12 порцией заряда, а во втором - его разряд. Частота выходных импульсов делителя частоты выбирается в три-пять раз меньшей граничной частоты работы ком- 25 паратора 9 для того, чтобы прсле заряда-разряда конденсатора 12 компаратор успел занять устойчивое состояние, т.е. успел сработать. Порция зарядг (пропорциональная амплитуде и дяи1ель-30 ности импульсов делителя частоты) выбирается равной примерно второй-третьей части единицы младшего разряда (кванта) аналого-цифрового преобразователя. В этом случае погрешность лого-цифрового преобразования, возникшая из-за несоответствия напряжения конденсатора 12 напряжению дрейфа АЦП, не превышает половины кванта.

С приходом импульса запуска ФВИ 1840 производит сброс счетчика 17 и изменяет состояние своих выходов так, что ключ 1 открывается, а ключи 2, 8 и 13 закрываются. Преобразуемое напряжение, усиленное усилителем 3. поступает че-дз рез резистор k и ключ 7 на вход интегратора. Скорость изменения напряжения на выходе интегратора зависит от величины и полярности преобразуемого напряжения. Отрицательное смещениеCQ на входе усилителя 5 интегратора должно выбираться более отрицательным, чем максимальное усиленное усилителем 3 отрицательное преобразуемое напряжен ние. В этом.случае при преобразовании55 максимального отрицательного напряжения скорость напряжения на выходе усилителя 5 интегратора будет минимальной, а при преобразовании максимального положительного напряжения - максимальной. Нулевому преобразуемому напряжению соответствует скорбеть изменения выходного напряжения, строго определяемая выходным напряжением источника 1 О и соотношением сопротивлений резисторов и 11. Длительность первого такта (выбирается из условий обеспечения максимального подавления помех) определяется длительностью импульса на первом выходе ФВИ 18. I

Во время второго такта ключи 1 и 7 закрываются, а ключи 2 и 8 открываются. Ключ 13 остается закрытым. При этом на вход усилителя 5 интегратора через резистор 11 подается отрицательное (относительно напряжения смещения и дрейфа на конденсаторе 12) напряжение источника 10. Направление изменения напряжения на выходе интегратора изменяется на обратное, причем скорость изменения напряжения остается постоянной и определяется, кроме значения напряжения источника 10, соотношением сопротивлений резисторов 4 и 11 и значением сопротивления резистора 11. После достижения выходным напряжением усилителя 5 интегратора ис- ходного уровня срабатывает компаратор 9 и второй такт заканчивается. По сигналу компаратора 9 ФВИ 18 изменяет состояние и тем самым переводит схему в исходное состояние - ключ 1 закрыт, остальные открыты, на конденсаторе 12 происходит запоминание дрейфа.

i

формирование отсчета в счетчике 17

происходит следующим образом-.

j

Нулевому преобразуемому напряжению на входе соответствует строго заданная напряжением смещения скорость изменения напряжения на выходе усилителя 5 интегратора как в первом, так и во втором такте, т.е. момент срабатывания компаратора 9 в этом случае заранее известен. Именно в этот момент изменяется на противоположный сигнал на втором выходе ФВИ 18. Формирователь 15 импульсов реализует по отношению к импульсам компаратора 9 и второму сигналу ФВИ 1В функцию ИСКЛЮЧАЮЩЕЕ ИЛ1;, Когда эти импульсы не совпадают, он разрешает прохождение счетных импульсов генератора 1 через элемент И 1б на счетный вход счетчика 17. При уменьшении значения отрицательного

515

преобразуемого напряжения момент срабатывания компаратора 9 приближается к моменту изменения состояния выхода ФВИ 18, что вызывает уменьшение коли- честна импульсов, поступающих на счетчик 17. При равенстве преобразуемого напряжения нулю моменты срабатывания совпадают и на счетчик 17 импульсы не поступают. При преобразовании положи- тельного напряжения момент срабатывания компаратора 9 запаздывает по отношению к моменту изменения состояния выхода ФВИ 18, что вызывает заполнени счетчика 17 соответствующим количест- вом импульсов. Анализируя последовательность срабатывания компаратора и изменения сигнала ФВИ 18, можно определить полярность преобразуемого напряжения цифровым методом. Коррекция дрейфа напряжения смещения на входе усилителя 3 (а одновременно и усилителя 5 интегратора и компаратора 9) осуществляется за счет запоминания состояния схемы в исходном состоянии

и подключения источника 10 одним полюсом к выходу усилителя 3.

ключ

-

Делитель 21 частоты, а также 13 могут быть выполнены на микросхе мах серии К5б1 , например К561ИЕ10, К561ТМ2/ К561ЛА7, К561ЛН1 или других.

15367

с Ю - 15

25

30

6

Формула изобретения

1,Аналого-цифровой преобразователь двухтактного интегрирования по авт. св.№Й1197, отличающийс я тем,что,с целью повышения точности преобразования, в него введен делитель частоты, вход которого объе- с вторым входом формирователя временных интервалов, а выход подключен к дополнительному входу первого ключа.

и первый резистор соединен с анодом первого диода, катод которого подключен к аноду второго диода и является выходом ключа, катод второго диода через второй резистор соединен с выходом второго элемента И-НЕ, первый вход которого через .инвертор объединен с первым входом первого элемента И-НЕ и является информационным входом ключа, вторые и третьи входы первого и второго элементов И-НЕ соответственно объединены и являются соответственно дополнительным и управляющим входами ключа.

(ригЛ

НФВИ

мДЧ

мНп

25 27

в(ижо9

fpus2

Авторы

Даты

1989-10-15—Публикация

1988-01-05—Подача