Изобретение относится к информационно-измерительной технике и может быть использовано для преобразования в цифровой код и индикации в цифровой форме или вдова в ЭВМ напряжения постоянного тока низкого уровня.

Целью изобретения является повышение точности преобразователя.

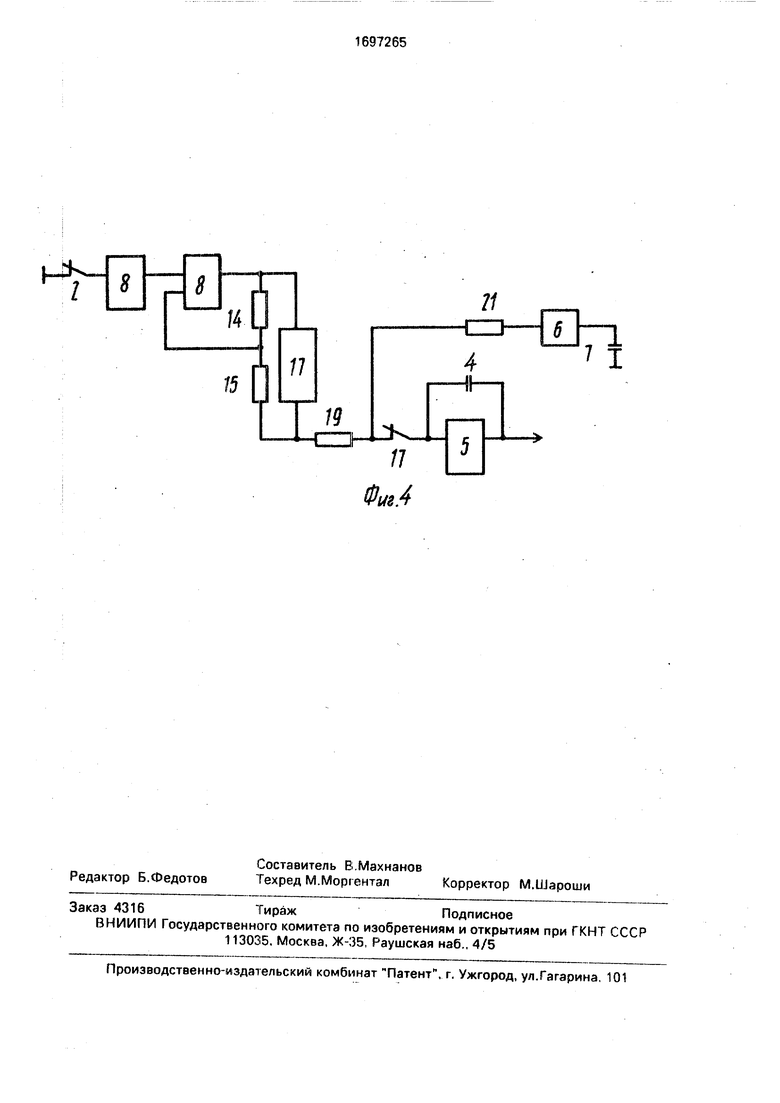

Структурная схема устройства изображена на фиг. 1; эквивалентные схемы для различных тактов работы изображены на фиг. 2-4.

Аналого-цифровой преобразователь содержит ключи 1 и 2, инвертор 3, интегратор на конденсаторе 4 и операционном усилителе 5, повторитель б напряжения, накопительный элемент на конденсаторе 7. входной усилитель 8, компаратор 9, ключ 10, формирователь 11 временных интервалов, операционный усилитель 12, генератор 13 счетных импульсов, токоогрэничивающие элементы 14. 15, выполненные на резисторах, формирователь 16 импульсов, источник образцового напряжения (ИОН) 17, токоограничива- ющие элементы 18, 19 элемент И 20, гокоограничиаающие элементы 21, 22, ключ 23, счетчик 24. кпюч 25, элемент ИЛИ 26.

Цикл состоит из трех обязательных тактов - установки в исходное состояние (обнуление схемы), интегрирование входного оигчзлз, интегрирование сигнала источника опорного напряжения.

В исходном состоянии АЦП происходят обнуление интегратора и запоминание дрейф усилителей 5, 8, 12 на конденсаторе 7. На фяг 2 приведена эквивалентная схема АЦП длг ).-о такта. Под действием управляю л . i janOb формирователя 11 вход усилител/ ° г.одктючается к общей точке схемы - 1 разомкнут (закрыт), ключи 2, 10, 23, 25 замкнуты (огкрмты) Напряжение на Вс. ходе усилителя 8

Ua К Одев,

ЮГГ

С

где идр8 напряжение дрейфа входного усилителя 8, приведенное к входу;

К - коэффициент усиления входного усилителя..

Учитывая действие ИОН 17 и делителя, образованного резисторами 14 и 15, напряжение на выходе операционного усилителя 12

U17 R14

+ UAp12+K UfipB

Rl4 + R15

где U17 - напряжение ИОН 17,

Исходя из того, что напряжение из выходе усилителя 12 равно входному плюс

11 п R1Л

-к-т-g- (постоянное смещение),

усилитель 12 для удобства называется смещенным повторителем. При этом напряжение на отрицательном выводе ИОН 17

+ идрГК .идр8

Напряжения Ui2° и через резисторы 18 и 19 и соответствующие ключи 25 и 23 поступают на вход интегратора. Инверсный вход интегратора находится под потенциалом иДр5, поскольку его прямой вход заземлен.

Ток Не0, проходящий через резистор 18 в исходном состоянии,

itii/ii i Ul7. Rl4 , 11,

иДР12 + К UW8 + -|ТГЛ; + UflpS

IY81R

Ток 119°, проходящий через резистор 19 в исходном состоянии,

itii/i i 17 Rl4 ,11

UflP12 + К UflpB +БТ4-4ГК15 + УДР5

R19

Суммарный ток Ij, поступающий на инверсный вход интегратора,

Ј 118° + 119° - (Uflp5 + Uflp12 + К«иДрв)х

-ГГ- + Rl8

1

R19

+

U,7

R14

Rl4 R18

Так как Ri4, Ris, Ri8 w Rts выбраны точными и соответственно попарно равными,

. (иДр5-ЩдрТ2+К-идр8

Как видно, суммарный ток на входе интегратора определяется напряжениями смещения применяемых операционных усилителей. Он компенсируется цепью отрицательной обратной связи из компаратора 9, пятого ключа 10, конденсатора 7, повторите ля напряжения 6 и равных резисторов 21 к 22. Напряжение на конденсаторе 7 зависит от номиналов резисторов 21 и 22.

10

15

20

25

30

35

40

45

50

Ток, проходящий через них, численно равен i° и противоположен по направлению. Таким образом, в исходном состоянии запоминается эквивалент напряжения дрейфа усилителей 5, 8, 12 на конденсаторе 7.

В начале первого такта преобразования формирователь 11 сбрасывает счетчик 24 и изменяет состояние своих выходов на противоположное. При этом ключ 1 открывается, а ключи 2, 23, 10 закрываются. На фиг. 3 приведена эквивалентная схема АЦП в первом такте. Напряжение на входе смещенного повторителя

.U« K(UX + идр8)

Соответственно на его выходе имеется напряжение

I Ji-7

U12 К Ux + идр5 + К идрв-ьтр + иДР12

Это напряжение создает ток через резистор Ris

,/ К Ux + идр5 + К U17/2 + UAP12

Следует отметить, что через резистор R22 проходит ток, компенсирующий напряжения дрейфа усилителей, величину которого определяет напряжение на конденсаторе дрейфа 7. Поэтому ток заряда конденсатора 4 интегратора определяем по формуле

., ., ., K UX+U17 U-|18-l22--R -

где I22 - компенсирующий напряжение дрейфа усилителей 5, 6, 21 ток через резистор 22, численно равный Ц/2и противоположный по направлению.

Как видно из формулы, ток заряда конденсатора 4 интегратора 5 в первом такте не зависит от дрейфа усилителей. Длительность первого такта обычно выбирают из условий обеспечения наибольшей помехе- защищенности.

После окончания первого такта ключи 1 и 25 закрываются, а ключи 2 и 23 открываются, ключ 10 остается закрытым. Эквивалентная схема второго такта приведена на фиг. 4. При этом вход АЦП подключается к общей точке и на вход интегратора через резистор 19 проходит ток разряда конденсатора 4 интегратора, обусловленный напряжением ИОН 17:

А ЦдР12 + идрб - U17/2

I jyf.

Rl9

Вместе с тем через резистор 21 во втором такте протекает ток компенсации дрейфа усилителей. Его величина равна 1 и противоположна по знаку. Поэтому результирующий ток разряда конденсатора интегратора:

I 2 if г Цдр5 +ЦДР12 + К Одре - U17/2 1с ИЗ 421 -Rig

Учитывая, что Ris Rl9 и R21 R22. получим

Ul7

1С 2 Rig

Следует отметить, что в первом такте отсутствует ток, компенсирующий дрейф усилителей через резистор R21, а во втором чеоез резистор R22. Это обусловлено работой ключей 25 и 23. После достижения выходным напряжением усилителя интегратора 5 исходного уровня, срабатывает компаратор 7, и второй такт заканчивается.

Баланс зарядов на конденсаторе 4:

lilEbUjL

С 4С 4

где ты - длительность первого такта; Гх - длительность второго такта. Отсюда г, + 1|.та

U17

Как видно из приведенной формулы, из цикла аналого-цифрозого преобразования исключены практически все погрешности, обусловленные неидеальными операционными усилителями.

По сигналу компаратора 9 формирователь 11 изменяет состояние своих выходов и переводит схему в исходное состояние.

Формирование отсчета в счетчике 24 происходит следующим образом.

Нулевому преобразуемому напряжению на входе соответствуют строго заданные ИОН 17 и соотношением резисторов 18 и 19 скорости изменения напряжения на выходе интегратора как в первом, так и во втором такте, т.е. момент срабатывания компаратора 9 в этом случае заранее известен. Именно в этот момент изменяется на противоположное состояние выхода 2 блока 11. Формирователь 16 импульсов реализует по отношению к сигналам компаратора 9 и выходу 2 формирователя 11 функцию ИСКЛЮЧАЮЩЕЕ ИЛИ (т.е. пропускает че- рез схему И 20 импульсы ГСИ 13, если эти сигналы на входе формирователя 16 импульсов не совпадают).

При отрицательном преобразуемом напряжении компаратор 9 срабатывает рань- ше поступления импулъса с выхода 2 формирователя 11. Чем меньше отрицательное напряжение, тем меньше импульсов проходит на счетчии 24. так как скорость изменения напряжения на выходе интегра- тора приближается к скорости при нулевом преобразуемом напряжении.

При равенстве преобразуемого напряжения нулю моменты срабатывания компаратора 9 и выхода 2 формирователя 11 совпадают, и импульсы на счетчик 24 не

®

5

0

5

0

5 0 5

0 5

поступают. При положительном преобразуемом напряжении момент срабатывания компаратора 9 запаздывает по отношению к изменению состояния выхода 2 формирователя 11, что вызывает заполнение счетчика 24 соответствующим числом импульсов.

Анализируя последовательность срабатывания компаратора 9 и выхода 2 формирователя 11 можно определить полярность преобразующего напряжения без использования аналоювых элементов.

Таким образом, вводимые блоки и связи позволяют по сравнению с прототипом повысить точность аналого-цифрового преобразования за повышения устойчивости схемы, т.е. СНИУ ения влияния шумов и устранения скпонностн к самовозбуждению. Кроме того, они дают возможность использовать при построении интегратора более простые и дешевыо усилители с малым коэффициентом подавления синфазной составляющей сигнала.

Формула изобретения

Аналого-цифровой преобразователь, содержащий первый и второй ключи, информационные которых являются соответственно входной шиной и шиной нулевого потенцпа/ia, а выходы подключены к входу входного усилителя, -1СТОЧНИК образцового напряжения, первый и второй выходы которого через соответствующие последовательно соединенные первый токоограничиваю ций элемент, выполненный на резистоое, и третий ключ, и второй токсограничивакнциГ элемент, выполненный на резисторе, и четвертый ключ подключены к первому входу интегратора, выход которого через компаратор соединен с первым входом формирователя импульсов и первым входом формирователя временных интервалов непосредственно и через пятый ключ - с первым выводом накопительное элемента, выполненного на конденсаторе, второй вывод которого является шиной нулевого потенциала, з управляющий вход первого ключа объединен с первым входом элемента ИЛИ и соединен с первым выходом формирователя временных интервалов и через инвертор подключен к управляющим входам второго и четвертого ключей, второй выход формирователя временных интервалов подключен к второму входу формирователя импульсов, зы,- д ко , орого соединен с первым входом элемента И, выход которого соединен с первым входом счетчика, а второй вход - с выходом генератора счетных импульсов и объединен с вторым входом формирователя временных интервалов, третий и четвертый выходы которого соединены соответственно с управляющим входом пятого ключа и вторым входом счетчика, второй вход элемента ИЛИ соединен с третьим выходом формирователя временных интервалов, выход - с управляющим входом третьего ключа, отличающийся тем, что. с целью повышения точности, в него введены операционный усилитель, третий, четвертый, пятый и шестой токоог раничиваю- щие элементы, выполненные на резисторах, и повторитель напряжения, через который первый вывод накопительного элемента соединен с первыми выводами третьего и четвертого резисторов, вторые выводы которых

0

соединены соответственно с точками соединений первого резистора и третьего ключа и второго резистора и четвертого ключа, а между выходами источника образцовых напряжений включены последовательно соединенные пятый и шестой резисторы точка соединейия которых подключена к инвертирующему входу операционного усилителя, неинвертирующий вход которого соединен с выходом входного усилителя, а выход подключен к первому выходу источника опорного напряжения, второй вход интегратора является шиной нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь двухтактного интегрирования | 1988 |

|

SU1515367A2 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547064A2 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Преобразователь сопротивления постоянному току в интервал времени | 1984 |

|

SU1237993A1 |

| Преобразователь напряжения в частоту | 1988 |

|

SU1522407A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1674373A2 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ СОВМЕЩЕННОГО ИНТЕГРИРОВАНИЯ | 1992 |

|

RU2036559C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

Изобретение относится к информацией но-измерительной технике, в частности к преобразованию в цифровой код напряжения постоянного токч низко о уровня. Цель изобретения - поеышечие точности аналого-цифрового преобразования напряжения постоянного тока за счет облегчения режима работы интегратора - достигается тем, то з устройство дополнительно введены повторитель напряжения и второйопераци- оинчй усилитель делитель напряжения, два .нитель х piзястера, подключенных соответственно к третьему и четвертому ключам. УСТРОЙСТВО содержит первый и второй кл1сч1л, входной усилитель, источник опорного напряжения, интегратор, выполнен -шй на операционном усилителе с обратной емкостной связью, компаратор, элементы ццскрзтной техники Л ил. (Л

Vx

Фиъ.1

Лл/

/07.3

Фиг.З

| Приборы и системы управления, 1973 №2, с | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-12-07—Публикация

1989-09-26—Подача