Изобретение относится к электроизмерительной технике и может быть использовано в цифровых вольтметрах для линейного преобразования сопро- тивления в интервал времени.

Цель изобретения - повьшение точности преобразования.

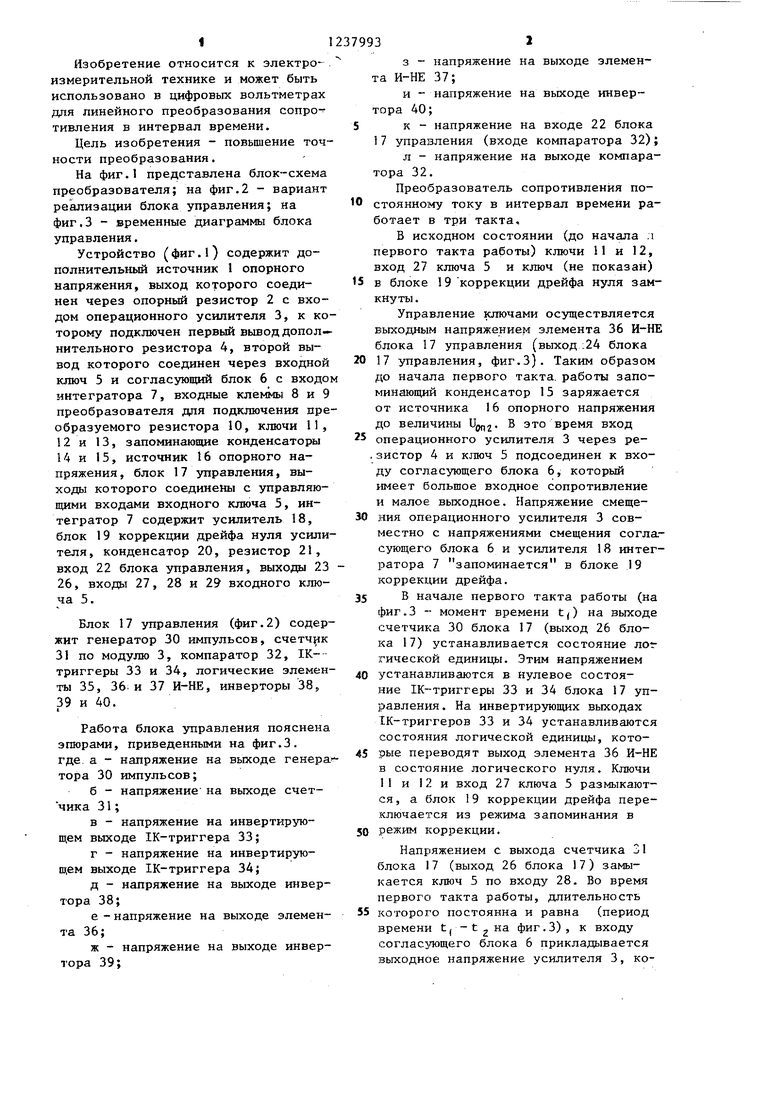

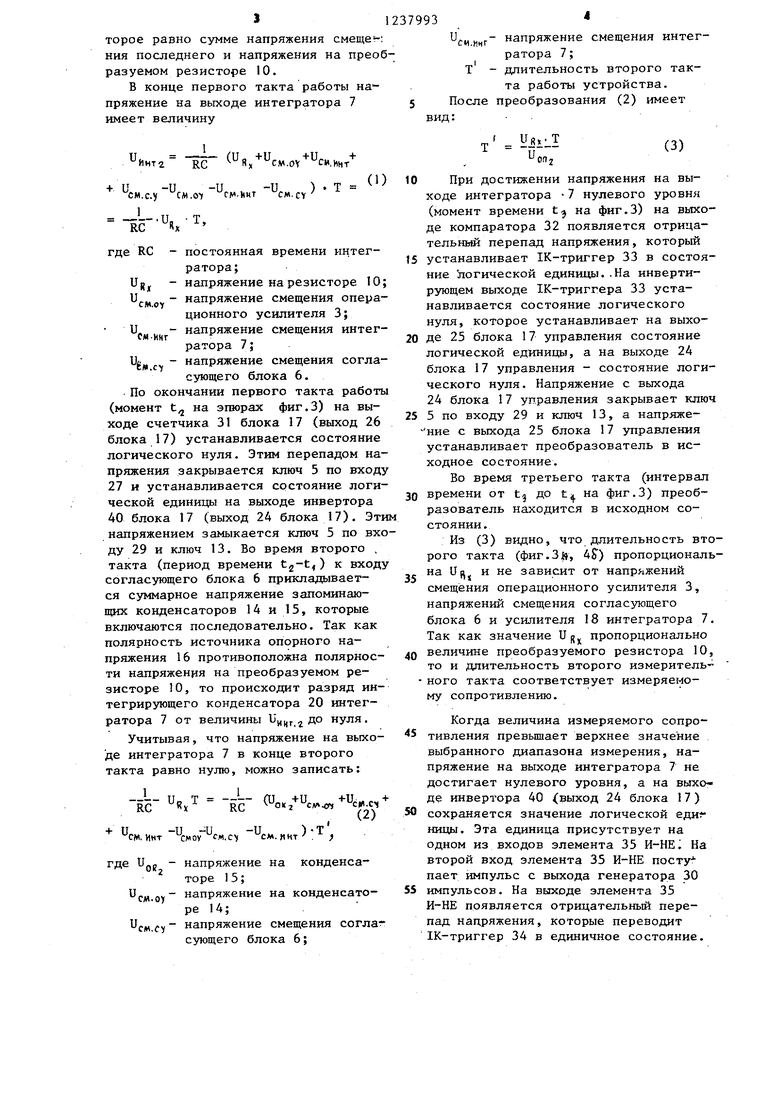

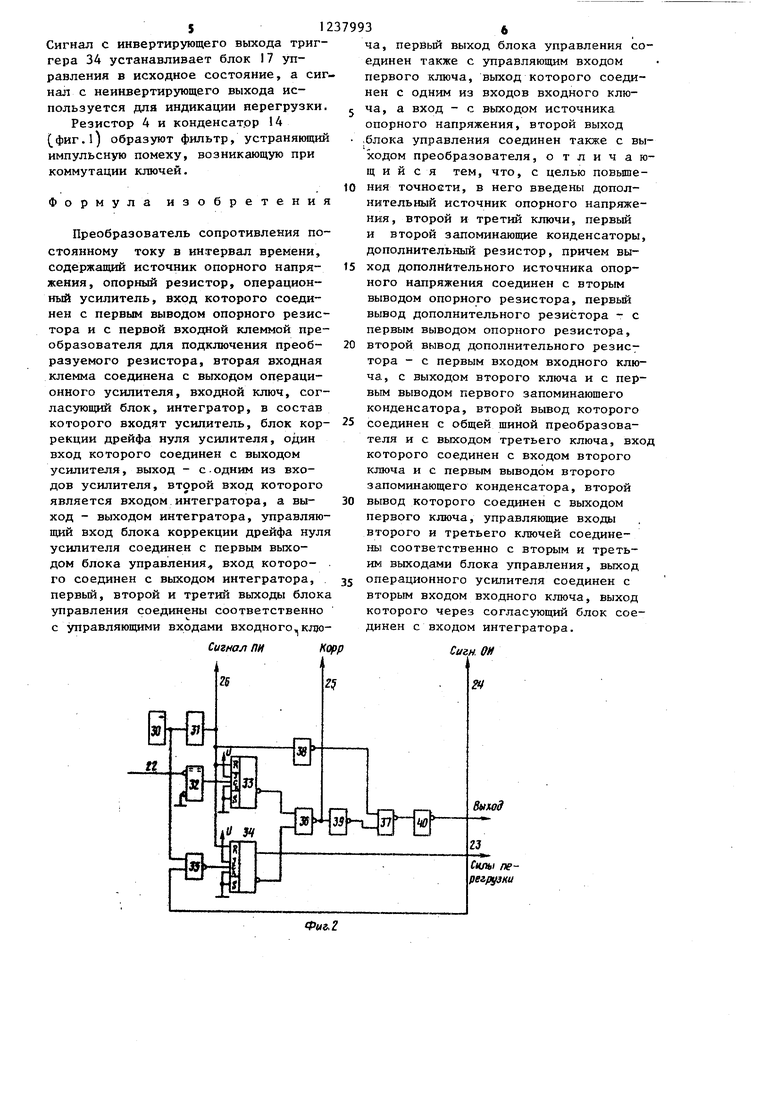

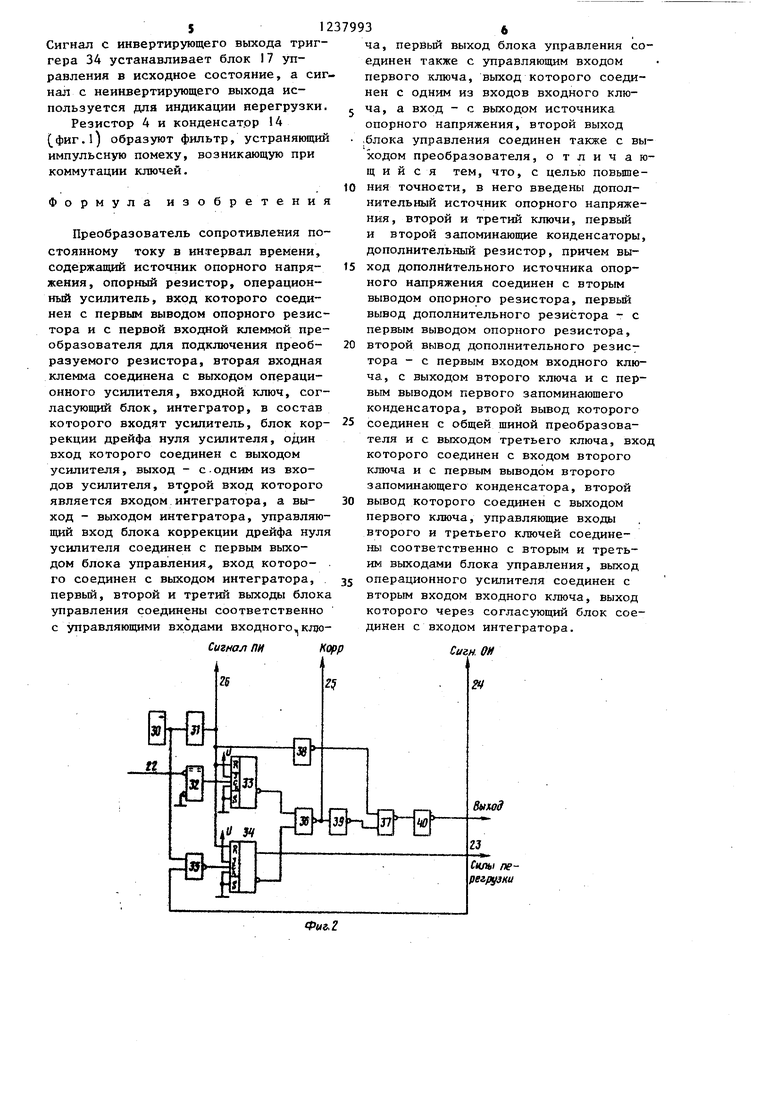

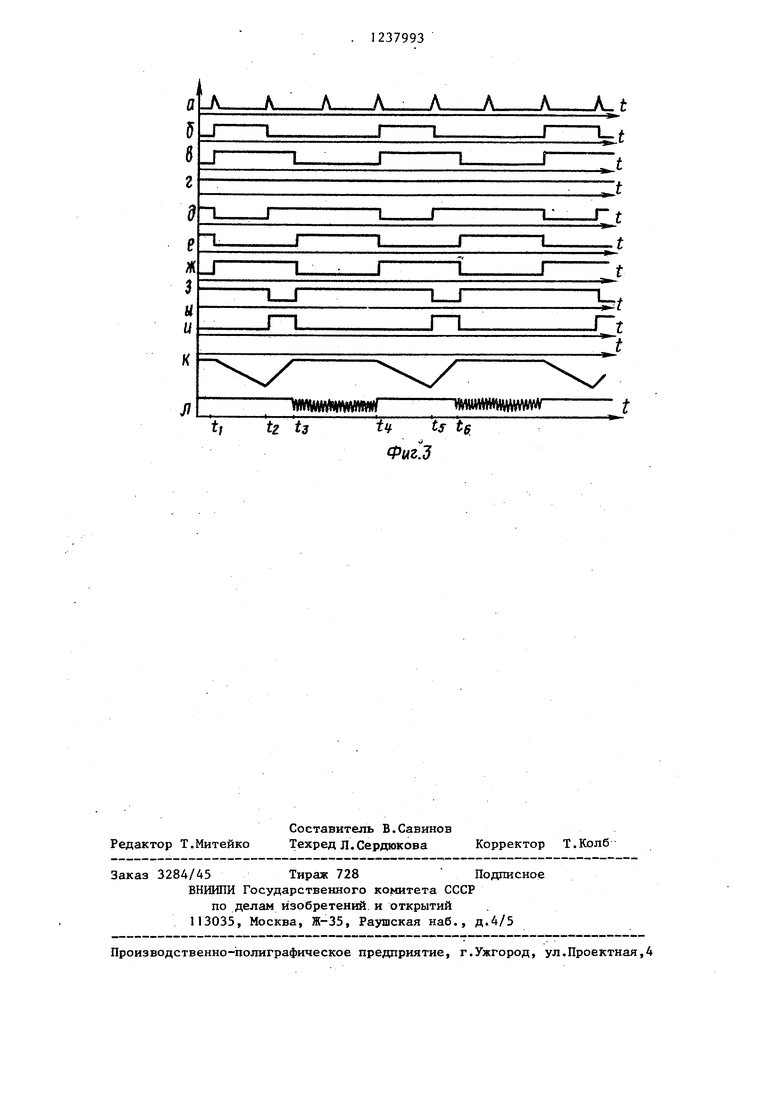

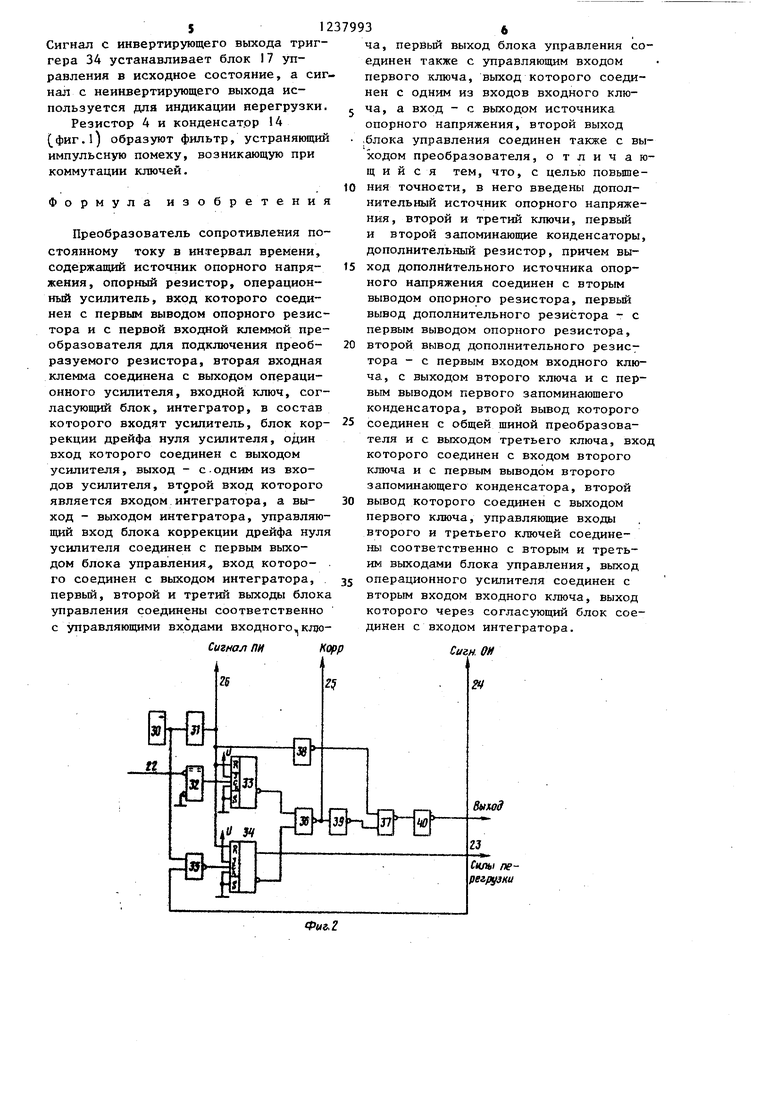

На фиг.1 представлена блок-схема преобразователя; на фиг.2 - вариант реализации блока управления; на фиг.З - временные диаграммы блока управления.

Устройство (фиг.1) содержит дополнительный источник 1 опорного напряжения, выход которого соединен через опорный резистор 2 с входом операционного усилителя 3, к которому подключен первый вывод дополнительного резистора 4, второй вывод которого соединен через входной ключ 5 и согласующий блок 6 с входо интегратора 7, входные клекмы 8 и 9 преобразователя дпя подключения преобразуемого резистора 10, ключи П, 12 и 13, запоминающие конденсаторы 14 и 15, источник 16 опорного напряжения , блок 17 управления, выходы которого соединены с управляющими входами входного ключа 5, интегратор 7 содержит усилитель 18, блок 19 коррекции дрейфа нуля усилителя, конденсатор 20, резистор 21, вход 22 блока управления, выходы 23 26, входы 27, 28 и 29 входного ключа 5.

Блок 17 управления (фиг.2) содержит генератор 30 импульсов, счетчик 31 по модулю 3, компаратор 32, IK- триггеры 33 и 34, логические элементы 35, 36: и 37 И-НЕ, инверторы 38, 39 и 40.

Работа блока управления пояснена эпюрами, приведенными на фиг.З. где. а - напряжение на выходе reHepa тора 30 импульсов;

б - напряжение на выходе счет- чика 31;

в - напряжение на инвертирующем выходе 1К-триггера 33;

г - напряжение на инвертирующем выходе 1К-триггера 34;

д - напряжение на выходе инвертора 38;

е - напряжение на выходе элемента 36;

ж - напряжение на выходе инвертора 39;

s

0

5

0

5

0

5

0

5

3 - напряжение на выходе элемента 37;

и - напряжение на выходе инвертора 40;

к - напряжение на входе 22 блока 17 управления (входе компаратора 32);

л - напряжение на выходе компаратора 32.

Преобразователь сопротивления постоянному току в интервал времени работает в три такта,

В исходном состоянии (до начала л первого такта работы) ключи 11 и 12, вход 27 ключа 5 и ключ (не показан) в блоке 19 коррекции дрейфа нуля замкнуты .

Управление ключами осуществляется выходным напряжением элемента 36 И-НЕ блока 17 управления (выход ;24 блока 17 управления, фиг.З). Таким образом до начала первого такта, работы запоминающий конденсатор 15 заряжается от источника 16 опорного напряжения до величины В это время вход операционного усилителя 3 через резистор 4 и ключ 5 подсоединен к входу согласующего блока 6, который имеет большое входное сопротивление и малое выходное. Напряжение смещения операционного усилителя 3 совместно с напряжениями смещения согласующего блока 6 и усилителя 18 интегратора 7 запоминается в блоке 19 коррекции дрейфа.

В начале первого такта работы (на фиг.З - момент времени t() на выходе счетчика 30 блока 17 (выход 26 блока 17) устанавливается состояние лог гической единицы. Этим напряжением устанавливаются в нулевое состояние 1К-триггеры 33 и 34 блока 17 управления . На инвертирующих выходах ГК-триггеров 33 и 34 устанавливаются состояния логической единицы, которые переводят выход элемента 36 И-НЕ в состояние логического нуля. Кгаочи I1 и 12 и вход 27 ключа 5 размыкаются , а ешок 19 коррекции дрейфа переключается из режима запоминания в режим коррекции.

Напряж€шием с выхода счетчика 31 блока 17 (выход 26 блока 17) замыкается ключ 5 по входу 28. Во время первого такта работы, длительность которого постоянна и равна (период времени t, фиг.З), к входу соглас пощего блока 6 прикладывается выходное напряжение усилителя 3, которое равно сумме напряжения смещет-: ния последнего и напряжения на преобразуемом резисторе 10.

В конце первого такта работы напряжение на выходе интегратора 7 имеет величину

CM.OY

+U

С/И.О- Г/И.ЦНТ см. CY

СИ. ИНТ

) т

1 RC

, TI .т

и

Rjt cM.of

и

СМ-ИКГ

где RC - постоянная времени интегратора;

UB, - напряжение на резисторе 10; напряжение смещения операционного усилителя 3; напряжение смещения интегратора 7; Ugj с напряжение смещения согласующего блока 6.

По окончании первого такта работы (момент t на эпюрах фиг.З) на выходе счетчика 31 блока 17 (выход 26 блока 17) устанавливается состояние логического нуля. Этим перепадом напряжения закрывается ключ 5 по входу 27 и устанавливается состояние логической единицы на выходе инвертора 40 блока 17 (выход 24 блока 17). Эти напряжением замыкается ключ 5 по входу 29 и ключ 13. Во время второго , такта (период времени tj-t) к входу согласующего блока 6 прикладывается суммарное напряжение запоминающих конденсаторов 14 и 15, которые включаются последовательно. Так как полярность источника опорного напряжения 16 противоположна полярности напряжения на преобразуемом резисторе 10, то происходит разряд интегрирующего конденсатора 20 интегратора 7 от величины Uj, ДО нуля.

Учитывая, что напряжение на выходе интегратора 7 в конце второго такта равно нулю, можно записать:

«.

-I- (U RC

o..Uc..c, (2)

см, Инт С)«оу см.су см. икт

)-т

где UQU - напряжение на конденсаторе 1 5;

напряжение на конденсаторе 14;

напряжение смещения согласующего блока 6;

си инг напряжение смещения интегратора 7;

Т - длительность второго такта работы устройства. После преобразования (2) имеет вид: Т

,.T

ио.г

(3)

10 При достижении напряжения на выходе интегратора 7 нулевого уровня (момент времени t на фиг.З) на выходе компаратора 32 появляется отрицательный перепад напряжения, который

15 устанавливает 1К-триггер 33 в состояние логической единицы. .На инвертирующем выходе 1К-триггера 33 устанавливается состояние логического нуля, которое устанавливает на выхо20 де 25 блока 17 управления состояние логической единицы, а на выходе 24 блока 17 управления - состояние логического нуля. Напряжение с выхода 24 блока 17 управления закрывает ключ

25 5 по входу 29 и ключ 13, а напряже- ние с выхода 25 блока 17 управления устанавливает преобразователь в исходное состояние.

Во время третьего такта (интервал

30 времени от tj до tj, на фиг.З) преобразователь находится в исходном состоянии.

Из (3) видно, что длительность второго такта (фиг.Зй, 4S) пропорциональна Uj и не зависит от напряжений смещения операционного усилителя 3, напряжений смещения согласзгющего блока 6 и усилителя I8 интегратора 7. Так как значение пропорционально

40 величине преобразуемого резистора 10,

то и длительность второго измеритель-- ного такта соответствует измеряемому сопротивлению.

35

Когда величина измеряемого сопротивления превышает верхнее значение выбранного диапазона измерения, напряжение на выходе интегратора 7 не достигает нулевого уровня, а на Bfcjxo- де инвертора 40 (выход 24 блока 7) сохраняется значение логической еди ницы. Эта единица присутствует на одном из входов элемента 35 И-НЕ На второй вход элемента 35 И-НЕ посту пает импульс с выхода генератора 30 импульсов. На выходе элемента 35 И-НЕ появляется отрицательный перепад напряжения, которые переводит 1К-триггер 34 в единичное состояние.

Сигнал с инвертирующего выхода триггера 34 устанавливает блок 17 управления в исходное состояние, а сигнал с неиквертирующего выхода используется дла индикации перегрузки.

Резистор 4 и конденсатор 14 (фиг.1) образуют фильтр, устраняющий импульсную помеху, возникающую при коммутации ключей.

Формула изобретения

Преобразователь сопротивления постоянному току в интервал времени, содержащий источник опорного напряжения, опорный резистор, операционный усилитель, вход которого соединен с первым выводом опорного резистора и с первой входной клеммой преобразователя для подключения преобразуемого резистора, вторая входная клемма соединена с выходом операционного усилителя, входной ключ, согласующий блок, интегратор, в состав которого входят усилитель, блок коррекции дрейфа нуля усилителя, один вход которого соединен с выходом усилителя, выход - с.одним из входов усилителя, второй вход которого является входом интегратора, а выход - выходом интегратора, управляющий вход блока коррекции дрейфа нуля усилителя соединен с первым выходом блока управления вход которого соединен с выходом интегратора, первый, второй и третий выходы блока управления соединены соответственно с управляющими входами входного клюСигнал ЛИ Корр

12379936

ча, первый выход блока управления соединен также с управляющим входом первого ключа, выход которого соединен с одним из входов входного клюс ча, а вход - с выходом источника

опорного напряжения, второй выход .блока управления соединен также с выходом преобразователя, отличающий с я тем, что, с целью повьше10 имя точности, в него введены дополнительный источник опорного напряжения, второй и третий ключи, первый и второй запоминающие конденсаторы, дополнительный резистор, причем вы15 ход дополнительного источника опорного напряжения соединен с вторым выводом опорного резистора, первый вывод дополнительного резистора - с первым выводом опорного резистора,

20 второй вывод дополнительного резистора - с первым входом входного ключа, с выходом второго ключа и с первым выводом первого запоминающего конденсатора, второй вывод которого

25 соединен с общей шиной преобразователя и с выходом третьего ключа, вход которого соединен с входом второго ключа и с первым выводом второго запоминающего конденсатора, второй

30 вывод которого соединен с выходом первого ключа, управляющие входы второго и третьего ключей соединены соответственно с вторым и третьим выходами блока управления, выход

35 операционного усилителя соединен с вторым входом входного ключа, выход которого через согласующий блок соединен с входом интегратора.

Bttxoff

Сипь перегрузки

tz ts

Редактор Т.Митейко

Составитель В.Савинов

Техред Л.Сердюкова Корректор Т.Колб

Заказ 3284/45 Тираж 728 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

tif. tf tg Фиг.д

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжения в интервал времени | 1988 |

|

SU1649662A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1401602A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1411974A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Интегрирующий преобразователь постоянного напряжения в код | 1988 |

|

SU1672565A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1444950A1 |

| Источник калиброванных напряжений | 1985 |

|

SU1283726A1 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

Изобретение относится к электроизмерительной технике и может быть использовано в цифровых вольт ; метрах. Цель изобретения - повышение точности преобразования. Устройство содержит источники 1 и 16 опорного напряжения, опорный резистор 2, операционный усилитель 3, резистрры 4 и 21, согласующий блок 6, интегратор 7, входные клеммы 8 и 9 преобразователя, преобразуемый резистор 10,ключи И, 12 и 13, запоминающие конденсаторы 14, 15, блок 17 управления с входом 22 и выходами 23-26, усилитель 18, блок 19 коррекции, конденсатор 20, входной ключ 5 с входами 27-29. Достижению поставленной цели способствует введение в устройство источника 1 опорного напряжения, ключей 12 и 13, запоминающих конденсаторов и резистора 4. В описании представлены временные диаграммы поясняющие работу устройства и вариант реализации блока управления. 3 ил. i (Л ГС со « со со со Вым9 Перегрузка

| Устройство для вычисления дробнорациональной функции | 1975 |

|

SU532097A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель сопротивления | 1973 |

|

SU464867A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-05—Подача