3-

ci.jui гпеино, выход 27 логического Г С. ерБировапного устройства, выходы ОС - ,7 д(- Шифратора 10, выход QO дегаиф- 1Я :-ору 10 тс используется, выходы

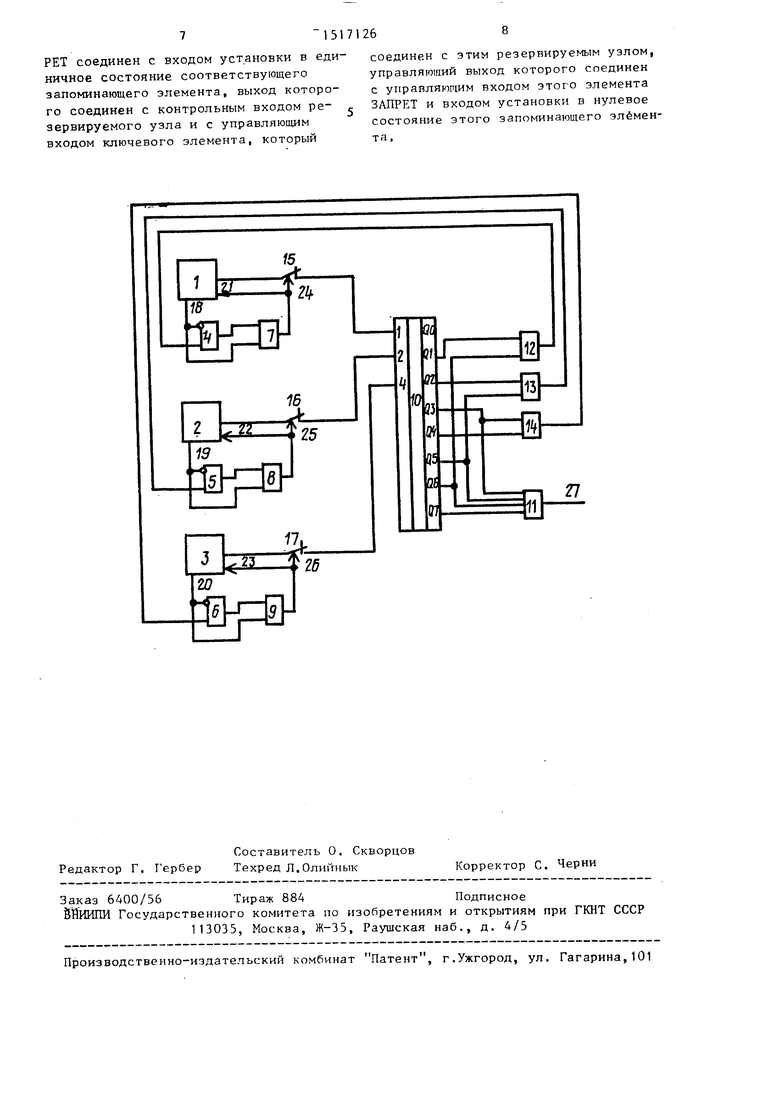

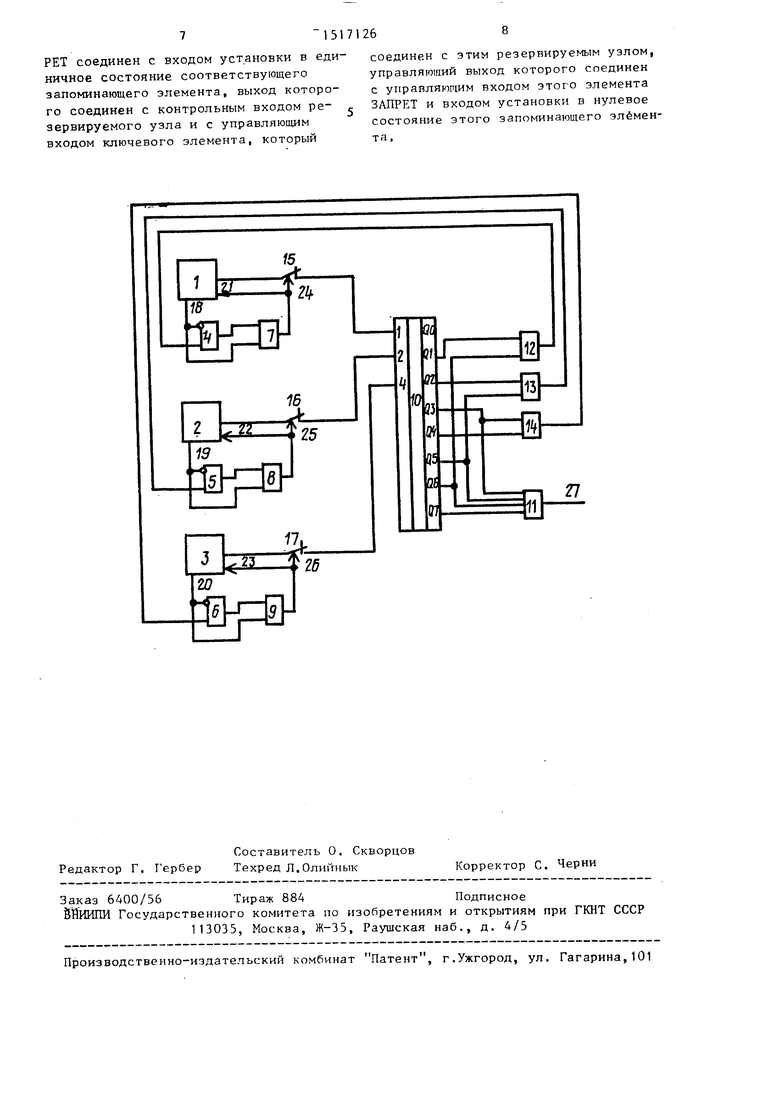

.Л-2 ;тодк,г1 гачены к первым входам, а Hixmri подключены к вторым входам элементов ИЛ1 12-14 соответствен- iHi, выхолм 0,3, Q5-07 подключены к иход;1 - - лемента ИЛИ 1 1 , Выходы элемен топ Iljill 12-14 под1Ш1очекы к инЛормаци- oj KFi -i входам элементов i SAIlPET 4-6 i-ooTiu-iTCTBenuo, выходы которых под- ключенм к входам установки в единичное состояние соответствующих запоми- и; элементов 7-9, выходы которых ni-iusJiioqeHbi к управляющим входам 24- 2- ,,;,:o4eiих элементов 15-17 и к контре JJ .III.IM лхоцам 21-23 резервируемых y;:j:.. B I-: соответственно, управляю- ; ti iii-ixc д.м 18-20 резервируемых узлов подключены к управляющим (инверс- /ij и;; здпм соответствую1Г1ИХ им эле- : ; гов ЗАПРЕТ 4-6 и к входам уста- втл н пулевое состояние запоминага- i-i--i . rTet- oHTOB 7-9 Соответственно, а Т 1.; .дъ ключевых элементов 15-17 под- ;v,ii-:cnb соответственно к первому - rpciio -iy дешифратора 10, пы- ; л - емелта иЛИ 11 является выходом -/ :, ;м-ическо: о ре: ервированного уст- иа.

Ло, ;itrijcKoe резервированное устройств. р аОотао т следующим образом.

и;ч:ра}зном состоянии резервиру- 1-3 тслючевые элементы 15

1/ ч.: .1клуп), если кпформация имеет р Г.д .--.о: г чаского О, то она с выходов P :J(. j-inniiycMMX узлов 1-3 через замкну- т:;г -:л очавые элементы 15-17 поступа- сч :}. соотве 1 ству1ощие входы деигифра- : :-. 10, с р лхчдов Q1-Q7 дешифратора- j ti входы элементов ИЛИ 11-14

5

0

5

0

5

0

264

ментов ИЛИ 12, на информадионные входы злементов ЗАБРЕТ 4-6 соответственно поступает сигнал в виде логического О, что свидетельствует об исправной работе резервируемых узлов 1-3.

При наличии ошибка тина Ложный О, например резервируемого узла 1, на первый вход дешифратора 10 через ключевой элемент 15 поступает ложная информация в виде логического О, а на второй и третий входы дешифратора 10 через ключевые элементы 16 и 17с резервируемых узлов 2 и 3 соответственно поступает правильная информация в виде логической 1, при этом с выхода Q6 дешифратора 10 через элемент ИЛИ 11 на выход 27 устройства поступает правильная инЛорма- ция и виде логической 1, кроме того , эта информация с выхода 06 поступает на второй вход элемента ИЛИ 12, на выходе которого формируется сигнал Ошибка, так как при этом на управляющий вход элемента ЗАЛРЕТ 4 с управляющего выхода 18 резервируемого узла 1 выдается сигнал Логический О, то сигнал Ошибка через элемент -ЗАЛРЕТ 4 поступает на вход установки в единичное состояние запоминающего элемента 7, где запоминается и выдается на управляющий вход 24 ключевого элемента 15 и на контрольный вход 21 резервируемого узла.1, ключевой элемент 15 размыкается, тем самым разрывается цепь прохождения лолсной информации с неисправного резервируемого узла 1 ,

При наличии ошибки типа Ложная 1, например резервируемого узла 1, на первый вход дешифратора 10 через ключевой элемент 15 поступает лож

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1981 |

|

SU1058097A1 |

| Логическое резервированное устройство | 1980 |

|

SU970700A2 |

| Многоканальное восстанавливающее логическое устройство | 1981 |

|

SU978352A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Мажоритарное устройство | 1980 |

|

SU892732A1 |

| Резервированное устройство | 1983 |

|

SU1121676A1 |

| Трехканальное восстанавливающее резервированное логическое устройство | 1982 |

|

SU1018255A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Мажоритарное устройство | 1981 |

|

SU1096767A1 |

| Устройство для управления режимом обмена мажоритарно-резервированной системы | 1982 |

|

SU1086432A2 |

Изобретение относится к радиоэлектронике и может использоваться в устройствах автоматического контроля и для создания резервированных систем. Целью изобретения является повышение достоверности и надежности восстановления информации путем исключения ложного срабатывания ключевых элементов и потери информации об ошибке резервируемых устройств. Это достигается тем, что в логическое резервированное устройство, содержащее резервируемые узлы и подключенные к ним ключевые элементы, введены дешифратор, второй, третий и четвертый элементы ИЛИ, первый, второй и третий элементы ЗАПРЕТ, первый, второй и третий запоминающие элементы, подключенные, таким образом между собой, что при любой ошибке любого резервируемого устройства на выходе элемента ИЛИ соответствующего канала формируется сигнал "ошибка", который запоминается запоминающим элементом и поступает на управляющий вход ключевого элемента и контрольный вход резервируемого устройства своего канала. Ключевой элемент размыкается и остается разомкнутым до тех пор, пока не произойдет восстановление информации в резервируемом устройстве. При этом с управляющего выхода резервируемого устройства на вход установкив состояние "о" запоминающего элемента поступает сигнал "запуск", сигнал "ошибка" с управляющего входа ключевого элемента снимается, ключевой элемент замыкается. 1 ил.

lUa; гуиар.Т ИНфОр .чТЛЦИЯ

; 11

8 виде логичес 0, которая через элемент ИЛИ ст;;;;ает па выход 27 логическо- v:4 i :tpoB itiHoro устройства, ес- ,. трмалич вид логической - :, , м л с вьисодов резервируем1.1Х , -,Л }1 1-. (Срез замкнутые ключевые |. ts пты I)-1 7 посгупает на соответ- . .yi j:ui;c . дешифратора 10, при r.t: с ль ходг; 0.7 дешифратора 10 че- V-4 ;ле:1П 1т ИЛИ 1 1 на выход 27 пос- rvnacT -чЛ .lп,IIЯ. в виде логической , л г ()дов Q1 -Q6 дешифратора 10 иг. с:: 1 летству 01цие входы элемен1-14 г;оступает информация в

v

. Т С К (5 Г О

О

с выхода эле

ная информация в виде логической 1 , а на второй и третий входы дешифратора 10 через ключевые элементы 16 и 17 с резервируемых узлов 2 и 3 поступает правильная информация в виде, логического О, при этом на входы элемента ИЛИ 11 с выходов Q3, Q5-Q7 дешифратора 10 поступает информация в виде логического О, на выход 27 логического резервированного устройства поступает правильная информация в виде логического О, кроме того, по сигналу логическая 1 с выхода Q дешифратора 10, поступающему на первый вход элемента ИЛИ 12, на его выходе форм1 1руется сигнал Ошибка,

5 ,

который через элемент ЗАПРЕТ 4 поступает на вход установки в единичное состояние запоминающего элемента 7, где запо шнается и выдается на упраляющий вход 24 ключевого элемента 15 и контрольный вход 21 резервируемого узла 1, ключевой элемент 15 размыкается .

Таким образом, если один из резер вируемых узлов, например резервируемый узел 1, неисправен, то соответствующий ему ключевой элемент 15 разомкнут. Если при этом с выходов резервируемых уялов 2 и 3 через ключе- вые элементы 16 и 17 на соответствующие входы дешифратора 10 поступает информация в виде логического О, то правильная информация логического О через элемент ИЛИ 11 с соответ- ствующих выходов дешифратора 10 поступает на выход 27 логического резервированного устройства, кроме этого сигнал Ошибка резервируемого узла 1 с выхода элемента -. ЗАПРЕТ , 4 сни- мается, однако, так как этот сигнал запомнился запоминающим элементом 7, то ключевой элемент 15 остается разомкнутым, После устранения неисправности резервируемого узла 1 с его управляющего выхода I8 выдается сигнал Запуск, который поступает на управляющий вход элемента ЗАПРЕТ 4 тем самым запрещается прохождение сигнсгла Ошибка на вход установки в единичное состояние запоминающего элемента 7, сигнал Запуск поступает также на вход установки в нулевое состояние запоминающего эле-- мента 7, который по этому сигналу устанавливается в нулевое состояние, при этом сигнал Ошибка, поступающий на управляющий вход 24 ключевого элемента 15 и контрольный вход 21 резервируемого узла 1, снимается, ключевой элемент 15 замыкается, если при этом информация с выхода резервируемого устройства совпадает с информацией резервируемых узлов 2 и 3, то сигнал Ощибка с выхода элемента ИЛИ 12 снимается. В дальнейшем логическое резервированное устройство работает аналогично,

В случае, если ошибка в резервируемом узле 2, то сигнал Ошибка формируется элементом ИЛИ 13, входы которого подключены к выходам Q,2 и fi5 дещифратора 10, а если ощибка произошла в резервируемом узле 3,

д5 20 25 о лп .г 0

с

5

1266

то сигнал Ошибка формируется элементом ИЛИ 14, входы которого подключены к выходам Q3 и Q4 дешифратора 10, В этих случаях логическое резервированное устройство работает аналогично случаю, если неисправен резервируемый узел 1,

Таким образом, логическое резервированное устройство различает лю-. бую ошибку резервируемых устройств и исключает ложное срабатывание ключевых элементов, что повышает достоверность информации, надежность ее восстановления, а также надежность самого устройства и расширяет его функциональные возможности и область применения.

Формула изобретения

Логическое резервированное устройство, содержащее три резервируемых узла, выходы которых соедине;м с соответствующими ключeвы ш ле- ментами, а также содержащее первый элемент РШИ, выход которого является выходом устройства, отличающееся тем, что, г. повышения достоверности и нппежт ости восстановления информации, Б него рведе- ны дешифратор, первый, второй.и третий входы которого соединены с выходами соответствующих ключевых тломе - тов, второй, третий и четвертьп элементы ИЛИ, первый вход второго элемента ИЛИ соединен с первым вь;ходом дешифратора, второй выход которого соединен с первым входом,третьего элемента РШИ, третий выход дешифратора соединен с первыми входаю-i перво го и четвертого элементов ИЯИ четвертый выход дешифратора соединен с вторым выходом четвертого эле тента ИЛИ, пятый выход дешифратора соединен с вторыми входами первого и третьего элементов ИЛ1 1, шестой выход дешифратора соединен с вторым входом второго и третьим входом первого элементов ИЛИ, четвертый вход первого элемента Ш1И соединен с седьмым выходом дешифратора, в устройство также введены три элемента. ЗАПРЕТ и три запомшгающих элемента, информационные входы первого, второ- го и третьего элементов ЗАПРЕТ соединены с выхо;2а 1 соответственно второго, третьего и четвертого элементов ИПИ, выход каждого из элементов ЗАПч 1517

PET соединен с входом установки в единичное состояние соответствующего запоминающего элемента, выход которого соединен с контрольным входом резервируемого узла и с управляющим входом ключевого элемента, который

соединен с этим резервируемым узлом, управляющий выход которого соединен с управляющим входом этого элемента ЗАПРЕТ и входом установки в нулевое состояние этого запоминающего элемента.

| Фритч В | |||

| Применение микропроцессоров в системах управления, - М.: Мир, 1984, с | |||

| Устройство для телефонирования по проводам токами высокой частоты | 1921 |

|

SU374A1 |

| Логическое резервированное устройство | 1979 |

|

SU839059A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Логическое резервированное устройство | 1980 |

|

SU970700A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-23—Публикация

1988-04-26—Подача