Изобретение относится к вычисли тельной технике и может быть испол зовано при построении высоконадежных управляющих цифровых вычислительных систем. Известно резервированное цифровое вьиислительное устройство (ЦВУ в состав которого входят запоминаю щие устройства.(ЗУ), блоки процессоров, блоки обмена, магистраль, объединяющая информационные выходы этих блоков, а также блок управления конфигураций. В состав блока управления конфигурацией входят узлы контроля, выходами подсоединенные к соответствующим входам модификации регистра конфигураций, выходы которого соединены с входам управления конфигурацией блоков ЦВУ, и узел управления lj.. .В рабочем режиме узлы контроля осуществляют оперативное обнаружение ошибок функционирования,ЦВУ и формирование соответствующих сигна лов в регистр конфигураций и узел управления, вызывая смену конфигураций отказавшего блока и возврат на последнюю контрольную точк программы, т.е. повторное выполнен участка программы. Наиболее близкой к предлагаемой по технической сущности является резервированная вычислительная система, содержащая резервированны блоки ЭВМ, блоки обмена, узлы контроля, а также блоки и узлы управления конфигурацией резерва с темы: счетчики числа сбоев резервированных блоков ЭВМ, счетчик-регистр конфигурации резерва для под счета числа отказавщих резервирова ных блоков ЭВМ, элементы И и ИЛИ. Счетчики числа сбоев служат для различения случайных сбоев и отказов. При случайном сбое реконфигурация резерва не производит ся, она происходит, когда число сбоев превьшает коэффициент пересчета счетчика Н . , Недостатком известной системы является низкая эффективность сред восстановления работоспособности. Это вьгражается в следующем. Рассмотрим период установившегося процесса работы системы длительностью Т. Предположим, что поток сбоев является простейшим с интенсивностью Л а коэффициент пер счета счетчика сбоев на интервале может быть определен в виде При этом потери времени на реконфигурацию из-за появления постоянного отказа в текущей конфигурации « резерва равны Т N /С , где J - средний временной интервал от момента. перезапуска программы с контрольной точки до момента обнаружения ошибки. Время 6 может менять свое значение от минимального, когда отказ проявляется на первых же командах повторяемого участка программы, до значения d, соответствующего средней длительности всего повторяемого участка программы (т.е. фрагмента программы между двумя последовательными контрольными точками).Если в среднем составляет 5-15% длительности d повторяемого участка программы, то потери времени можно оценить как t (О,05+0,15)Nd. Таким образом, известная система имеет ограниченную эффективность восстановления прохолщения программы, после сбоев, так как для того,чтобы снизить число k ложных реконфигураций резерва в ней необходимо значительно увеличивать коэффициент пересчета счетчиков сбоев. Это, в свою очередь, приводит к существенным потерям времени при появлении постоянного отказа в текущей конфигурации резерва, что затрудняет использование системы для управле- ния объектами в реальном масштабе времени. Кроме того, известной системе присуща слабая защищенность от сбоев в оперативной памяти, так как при накоплении сбоев во всех комплектах памяти системы (это возможно .при работе в условиях мощных или высокоинтенсивных помех) она теряет возможность автоматического восстановления работоспособности. Действительно, перезапуск программ с контрольных точек предполагает перезагрузку аппаратурных ресурсов ЦВУ информацией, заранее запомненной в оперативной памяти, при разрушении этой информации система не может автоматически восстанавливаться.Это также .свидетельствует о недостаточной сбоеустойчивости системь:.

. 3

- Цель изобретения - повьшение устойчивости.к сбоям устройства. Поставленная цель достигается

.тем, что в резервированное устройство, содержащее резервируемые вычислительные блоки, блоки памяти и блоки обмена, информационные входы и выходы которых подключены к соответствующим шинам магистрали,и блок управления конфигурацией резерва, содержащий счетчик сбоев резервируемых вычислительных блоков счетчик.сбоев блоков памяти, счетчик сбоев блоков обмена, регистр признаков ошибок, регистр конфигураций резерва и элемент ИЛИ, выход которого соединен с входами установки резервируемых вычисли тельных блоков, блоков памяти и блоков обмена, а входы - соответственно с одноименными контрольными выходами резервируемых вычислительных блоков, блоков памяти и блоков обмена, с входами первого, второго и третьего разрядов регистра признаков ошибок и со счетными входами счетчиков сбоев, выходы которых соединены с соответствующими входами модификации регистра конфигураций резерва, управляющие выходы которого подключены к одноименным входам резервируемых вычислительных блоков, блоков памяти и блоков обмена, а информационные выходы - к соответствующим шинам магистрали, к которой подключены выходы регистра признаков ошибок и дешифратор, введен счетчик числа реконфигурации резерва блоков памяГи, выход которого соединен с входом четвертого разряда регистра признаков.ошибок, а вход установки в ноль - с одноименными входами счетчиков сбоев и с первым выходом дешифратора, второй выход которого соединен с входом сброса регистра признаков ошибок, а входы - с соответствующими шинами двунаправленной магистрали.

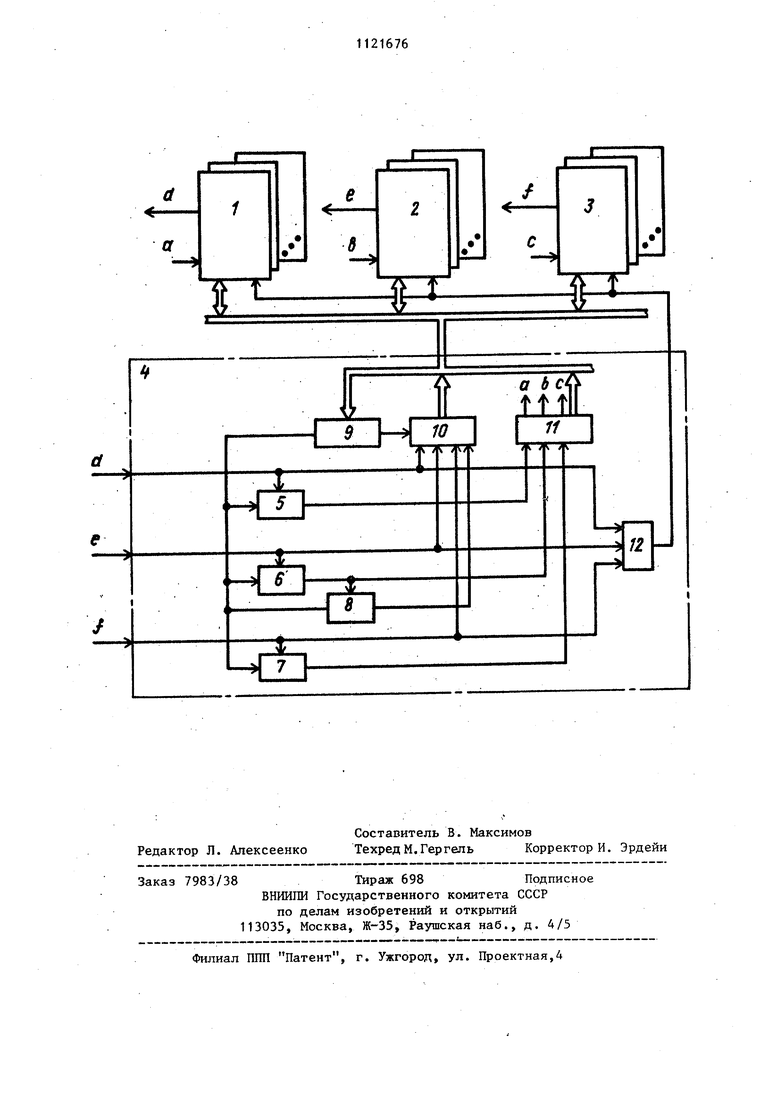

. На чертеже представлена схема предлагаемого резервированного цифрового вычислительного устройства.

Устройство содержит резервируемые вычислительные блоки 1, блоки 2 памяти, блоки 3 обмена и блок 4 управления конфигурацией резерва,в состав которого входят счетчики 5, 6 и 7 числа сбоев вычислительных

216764

блоков, блоков памяти и блоков обмена соответственно, счетчик 8 числа конфигураций памяти, дешифратор 9, регистр 10 признаков ошибок, 5 регистр 11 конфигураций и элемент ИЛИ 12.

Магистральные выходы блоков 1-3, регистров 10 и 11, а также вход дешифратора 9 соединены двунаправ10 ленной магистралью. Выходы контроля блоков 1-3 соответственно соединены со счетными входами счетчиков 5-7, с первым, вторым и третьим входами элемента ИЛИ и с входами соответст15 вующих разрядов регистра 10. Выходы счетчиков 5-7 соединены с соответствующимй входами модификации регистра 11, выход счетчика 6 сбоев блоков памяти, кроме того, соединен

20 со счетным входом счетчика 8, выход которого Соединен с входом четвертого разряда регистра 10, а вход обнуления - с аналогичнымивходами счетчиков 5-7 и первым выходом де5 шифратора 9, второй выход которого соединен с входом обнуления регистра 10. Выходы а, Ъ и с регистра 11 : соединены с входами управления конфигурацией резерва блоков 1-3 Соот0 ветственно, а выход элемента 12 с входом установки этих блоков.

Критерием отказа текущей конфигурации резерва блоков является N-кратное неудачное (т.е. приводящее к ошибке) выполнение повторяемого участка программы. Указанньй критерий реализуется путем счета в счетчиках .сбоев числа возвратов на начало каждого повторяемого участка программы и сброса значения счетчиков при переходе от данного повторяемого участка программы к следующему.

Така.я организация позволяет практически исключить возможность ложной реконфигурации резерва в ЦВУ, существенно повышая оперативность и эффективность восстановления программы после сбоя.

0 Наличие счетчика реконфигураций блоков ;памяти позволяет обнаружить состояние в системе,когда информация не может быть правильно считана из блоков памяти во всех

5 , конфигурациях резерва этих блоков. Это позволяет и в этом случае автоматически проводить восстановление, например, перезагрузив содержимое памяти информацией из внешнего накопителя или проведя программные процедуры коррекции. Указанное свойство также позволяет повысить устойчивость ЦВУ к сбоям. Устройство работает следующим об разом. При включении устройства счетчики 5-8, а также регистры 10 и 11 об нуляются, причем нулевой код в регистре 11 обеспечивает установку исходных конфигураций блоков 1-3 (на шинах О, Ь и с - нулевой код) Число основных и резервных комплектов этих, блоков, типы конфигураций резерва и последовательность их перебора определяются требованиями к надежности, производительности, физическим параметрам ЦВУ и могут быть различными. В ходе работы ЦВУ вьтолняет целевые программы, обеспечивая процесс управления. Правильность функционирования бл ков 1-3 оперативно контролируется входящими в их состав контрольными схемами, в качестве которых могут быть использованы любые контрольные схемы (например, схемы контроля по модулю, схемы сравнения и другие). При обнаружении ошибки вьиислительного блока памяти или блока обмена на контрольных выходах о,е или i соответственно формируется сигнал, поступаю1ций на счетный вход счетчи.ка 5,6 или 7 сбоев, на вход первого второго и третьего разряда регистра 10 и на вход элемента ИЛИ. Это обеспечивает модификацию содержимого соответствующего счетчика сбое установку в единичное состояние соответствующего разряда регистра признаков ошибок, а также формирова ние сигнала ошибки на выходе элемента ИЛИ и на входах установки бло ков 1-3, который переводит их в фик сированное состояние, а также блокирует обмен, реакцию на прерывание запись в память (на время наличия сигнала ошибки) и инициирует вьшол нение программы анализа ошибок пут установки фиксированного адреса пе вой ее команды в вычислительных блоках. При выполнении программы анализа ошибок вычислительный .блок по магистрали считывает содержимое регистр 10 и производит его анализ, по результатам которого вырабатывает необходимую соответствующую типу ошибки программную реакцию, например коррекцию содержимо.го ЗУ, установку состояний абонентов и т.д. и осуществляет сброс регистра 10, а также возврат на контрольную точку программы (на начало повторяемого участка программы).Сброс регистра 10- выполняется при подаче вычислительным блоком по магистрали на вход дешифратора 9 кода К1. Организация контрольных точек в программе является одним из наиболее распространенных методов защиты программ и данных от аппаратурных ошибок и производится обычно следующим образом. Все программы, предназначенные для выполнения, разбиваются на участки, вьшолнение каждого из которых начинается с загрузки аппаратурных средств. Информация для загрузки готовится в каждом таком участке для последующего, причем при Появлении ошибки также производится перезагрузка и возобновление работы с начала участка. Особенность предлагаемого устройства состоит в следующем. На границах повторяемых участков программы, непосредственно перед формированием информации о следующей контрольной точке выполняется операция сброса содержимого счетчиков 5-7, которьй происходит при подаче вычислительным блоком по магистрали на вход дешифратора 9 кода К2. При возникновении ошибки и возврате на предыдущую контрольную точку производится накопление в соответствующем счетчике сбоев их числа (сброс счетчиков в этом случае не происходит), а при успешном переходе к следующему участку счетчики обнуляются. Папример, при возникновении сбоя в блоке 1 (2 или 3) на контрольном выходе d блока 1 (е или i соответственно) вырабатывается сигнал, устанавливающий первьй (второй, третий) разряд регистра 10, добавляющий единицу к содержимому счетчика 5 (6,7), устанавливая блоки 1-3 в фиксированное состояние и переводя ЦВУ на выполнение программы анализа ошибок. Последняя передает управление прер7ванной ошибкой программе, начиная с последней контрольной точки. Если данные события повторяются менее чем N раз (N - коэффициент пересчета, для счетчиков 5-7 он может быть различным), а затем текущий участок программы выполняется правильно, то счетчики 5-7 сбрасываютс и реконфигурации блоков 1-3 не происходит . Если же происходит N-кратное повторение ошибки данного типа при вьптолнении текущего участка программы, то соответствующий блок считается отказавшим и его конфигурация резерва изменяется, так как на выходе счетчика сбоев появляется сигнал переполнения, приводящий к модификации поля разрядов регистра 11, содержащего код конфигурации этого блока (меняется значение на выходе а Ъ или с соответственно При одновременномпоявлении ошибок нескольких типов они обрабатываются параллельно, что обеспечивает быстрое удаление отказавших блоков. Число реконфигураций блока 2 памяти подсчитывается п счетчике 8 Это обеспечивается тем, что вход этого счетчика соединен с выходом переполнения счетчика 6 сбоев блоков памяти. Сброс счетчика 8 происходит на границе повторяемых участков программы вместе со счетчиками 5-7 сбоев. Коэффициент пересчета этого счетчика равен или превышает число конфигураций блоков памяти, поэтому его переполнение наступает в том случае, когда текущий участок программы не удается выполнить изза ошибки памяти ни в одной из конфигураций блока 2. В этом случае сигнал с выхода счетчика 8 устанавливает четвертый разряд регистра 10 так что программа анализа ошибок способна в этой ситуации инициироват перезагрузку блоков ЗУ из ниешних источников, информации или провести иное корректирующее действие. Для анализа эффективности предлагаемого устройства оценим характе ристики его функционирования. Предполагая, что интенсивность потока сбоев равна интенсивность потока восстановлений (обнуле ний счетчиков сбоев) - М, причем 6 Л « М, вероятность накопления числа N в счетчике может быть определена как P(N) -(). При этом М определяется как величина, обратная средней длительности повторяемого участка программы d, а так как и новый сбой, и появление восстановления приводит к обнулению счетчика сбоев, то среднее время пребывания в этом состоянии (состоянии N) Л+М 1+ Для длительного интервала Т стационарной работы ЦВУ время пребывания в состоянии, когда счетчик содержит число N, можно определить в виде T(N) TPCN), а число попаданий в это состояние, т.е. число ложных реконфигураций, можно оценить как T(N) „,с1л 4N- НА Например, для практического случая Т 10000 ч, d 0,1 ч, Л Л 0,1 чи N 3 среднее значение К составляет 0,1 (т.е. возможность ложной реконфигурации практичес.ки исключается), а потери времени t на реконфигурацию всего 0,015 ч. При тех же значениях для прототипа откидаемое число ложных реконфигураций составит более 300. При увеличении коэффициента пересчета до 100 ожидаемое число ложных реконфигураций резерва в прототипе может быть снижено до 10, однако потери времени на реконфигурацию при появлении постоянного дефекта могут вьфасти при этом до 0,5 ч. Таким образом, в предложенном устройстве использован более совершенный критерий отказа, позволяющий снизить потери времени на реконфигурацию резерва и повысить сбоеустойчивость. Этому же служит обеспеченная в ЦВУ возможность обнаружения группового сбоя в блоках памяти и автоматическое восстановление работоспособности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления переключением резервных блоков | 1981 |

|

SU1108623A1 |

| Устройство для управления реконфигурацией резервированного вычислительного комплекса | 1983 |

|

SU1149449A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Резервированное цифровое устройство | 1981 |

|

SU1023685A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Резервированная система | 1982 |

|

SU1089771A1 |

| Двухканальная резервированная вычислительная система | 1989 |

|

SU1734251A1 |

| Адаптивное четырехканальное резервированное устройство | 1990 |

|

SU1742821A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ И РЕЗЕРВИРОВАНИЯ ИНФОРМАЦИОННОЙ СИСТЕМЫ | 2010 |

|

RU2453079C2 |

РЕЗЕРВИРОВАННОЕ УСТРОЙСТВО, содержащее резервируемые вычислитель ные блоки, блоки памяти и блоки обмена, информационные входы и выходы которых подключены к соответствующим шинам .магистрали, и блок управления конфигурацией резерва, содержащий счетчик сбоев резервируемых вычислительных блоков, счетчик сбоев блоков памяти, счетчик сбоев блоков обмена, регистр признаков ошибок, регистр конфигураций резерва и эле|мент ИЛИ, выход которого соединен с входами установки резервируемых вычислительных блоков, блоков, памяти и блоков обмена а входы - соответственно с одноименными контрольными выходами резервируемых вычислительных блоков, блоков памяти и- блоков обмена, с входами первого, второго и третьего разрядов регистра признаков ошибок и со счетными входами счетчиков сбоев, выходы которых соединены с соответствующими входами модификации регистра конфигураций резерва, управляющие выходы которого подключены к одноименным входам резервируемых вычислительных блоков, блоков памяти и блоков обмена, а информационные выходы - к соответствующим шинам магистрали, к которой подключены также выходы регистра признаков ошибок и дешифратор, отличающееся тем, что, с целью повышения устойчивости к сбоям, в устройство введен счетчик числа реконфигураций резерва блоков памяти, выход которого соединен с входом четвертого разряда регистра признаков ошибок, а вход установки в ноль - с одноименными входами счетчиков сбоев и с первым выходом дешифратора, второй выход которого сое- динен с входом сброса регистра признаков ошибок, а входы - с соответствующими шинами магистрали.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Park N.G., Вагг Р.С | |||

| The SERF Fault-Tolerant Computer | |||

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Резирвированная вычислительная система | 1973 |

|

SU478460A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-30—Публикация

1983-01-06—Подача