Изобретение относится к вычислительной технике и можег быть применено при разработке резервированных систем контроля и управления повышенной надежности, а также адаптирных резервированных систем.

Целью изобретения является повышение разрешающей способности и быстродействия.

Сущность изобретения состоит в:

- повышении глубины диагностирования и обеспечении возможности формирования работоспособной конфигурации при наличии отказов во всех каналах резервированной системы, если отказ произошел не по вине одного и того же блока всех трех каналов;

-уменьшении времени нахождения работоспособной конфигурации резераиро- ванной системы, так как в устройстве проверяется работоспособность мажорию о о

™JI

тарной (частично-мажоритарной) конфигурации, и если она работоспособна, то проверка заканчивается, а если нет, то оптимальным образом находится первая работоспособная одноканальная конфигурация, а затем осуществляется попытка перевода его по группам резервируемых боков (слоям) в мажоритарный режим.

Под термином оптимальным образом понимается следующая процедура поиска работоспособной конфигурации:

Поканальная (канал А, канал Б, канал В) проверка работоспособности системы. Здесь и в дальнейшем, принимается следующее -- если результаты проверки любой одноканальной конфигурации положительны, то эта работоспособная конфигурация фиксируется счетчиком и преобразователем 7, дальнейший поиск в данном прерывании, работоспособных конфигураций не производит. При проведении трех пока- нальных проверок получается положительный результат, если в мажоритарной системе нет отказавших блоков во всех трех каналах.

Группа из 6 п проверок (п - количество резервируемых слоев системы) работоспо собности системы. В каждой из этих проверок онредляется работоспособность одного из каналов, с заменой з нем одного из резервируемых слоев на однотипный соседнего канала. При проведении этих проверок получается положительный результат, если в системе хотя бы в одном канале имеется не более одного отказавшего блока, и конечно, если работоспособная конфигурация вообще существует. Таким образом, при проведении этих проверок гарантировано нахождение работоспособной конфигурации резервированной системы, если в ней имеется до пяти отказавших блоков.

Проводятся проверки методом полного перебора одноканальных конфигураций, исключая уже проверенные, неработоспособные. Эта группа проверок дает положительный результат, если в системе имеется хотя бы одна работспособная конфигурация.

В табл.1 приводится последовательность првоеряемых на работоспособность конфигураций для трехслойной резервированной системы.

Устройство позволяет также испольэо вать результаты предыдущих тестирований с целью уменьшения времени нахождения работоспособной конфигурации. Так, например, если 8-я конфигурация в 1-м прерывании дает положительный результат (табл.1), а проверки 1-й - 7-й, проведенные раньше, отрицательны, то очевидно, при

сравнении конфигураций в третьей и восьмой проверках, что в первом сечении отказывает блок Б. Этот факт фиксируется в i-м прерывании и при поиске работоспособной

конфигурации в 1+1-м и последующих прерываниях проверки конфигураций блока Б в первом сечении проводиться не будет (проверки 9, 10, 18, 20, 24 и 28).

Если, например, в +1-м прерывании

0 проверка 16 дает положительный результат, то по результатам сравнения проверки 16с проверками 2, 7, 11 и 12 видно, что отказывают резервированные блоки: в третьем сечении канала А и канала Б, во втором

5 сечении канала Вив первом сечении канала В. Таким образом, с учетом результатов 1-го и i+1-го прерывания при возникновении следующего отказа в Н2-м прерывании проверяется единственно возможная работо0 способная конфигурация: канал А в первом сечении, канал Б во втором, канал В в третьем (проверка 27).

Если отказ происходит только в одном из блоков группы резервируемых блоков, то

5 на этом уровне сохраняется мажоритарная структура.

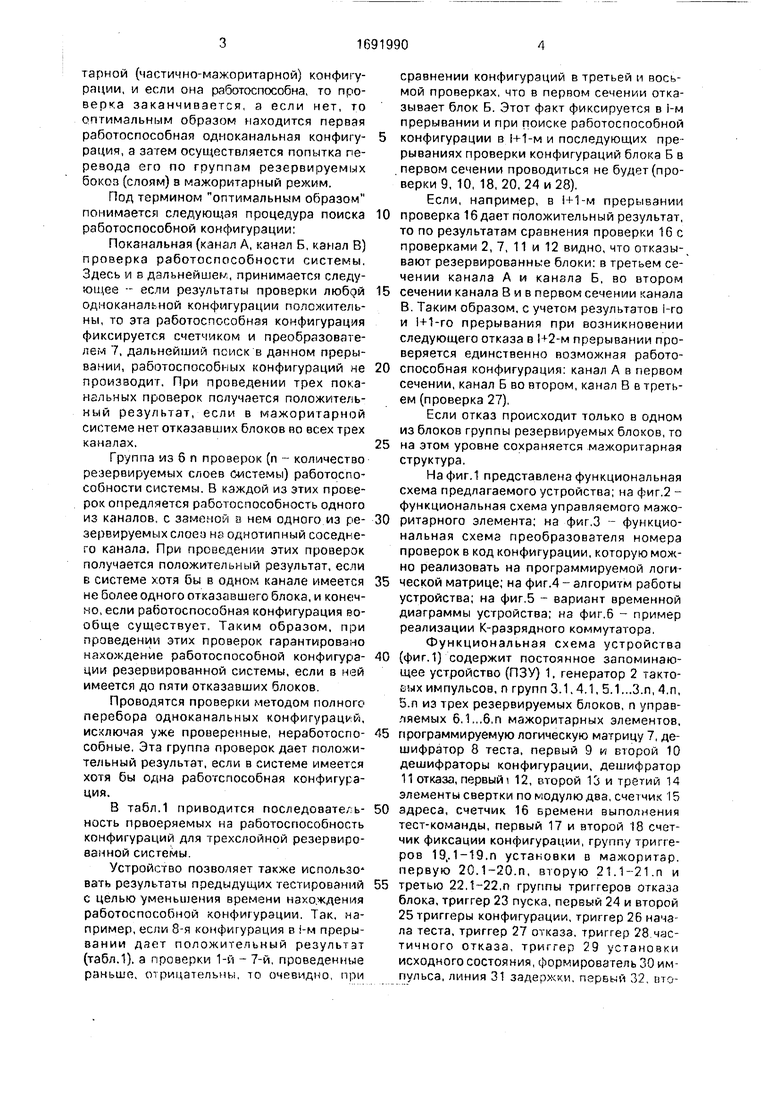

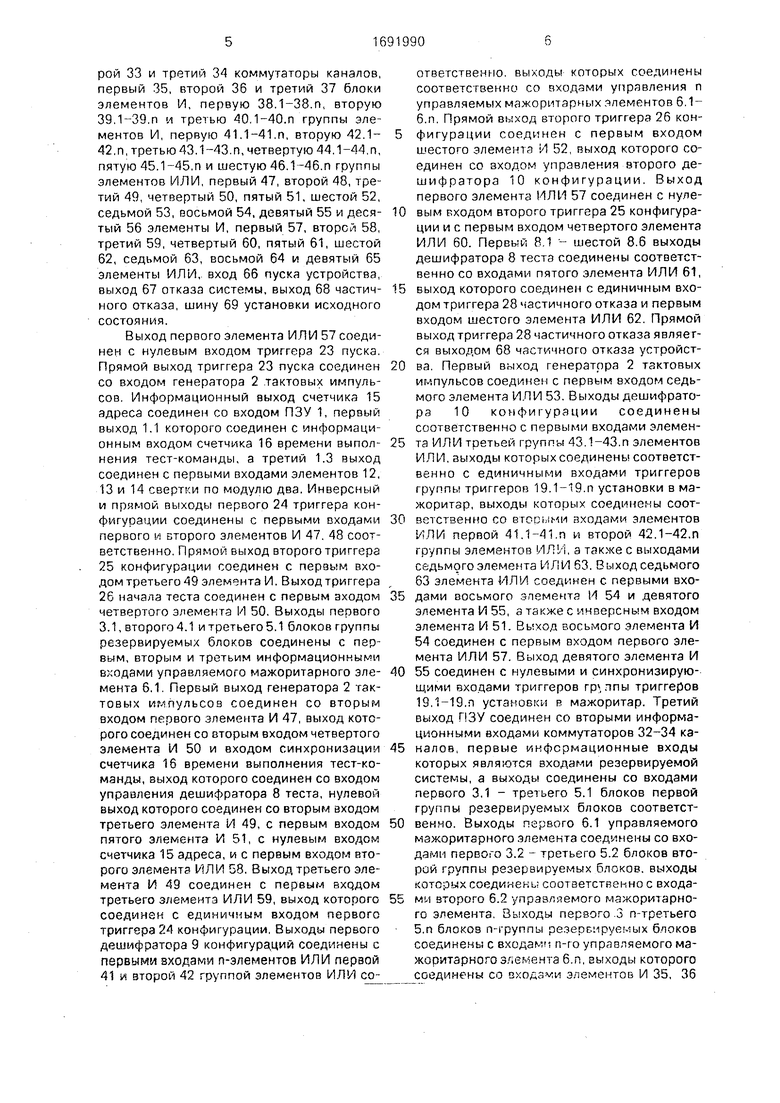

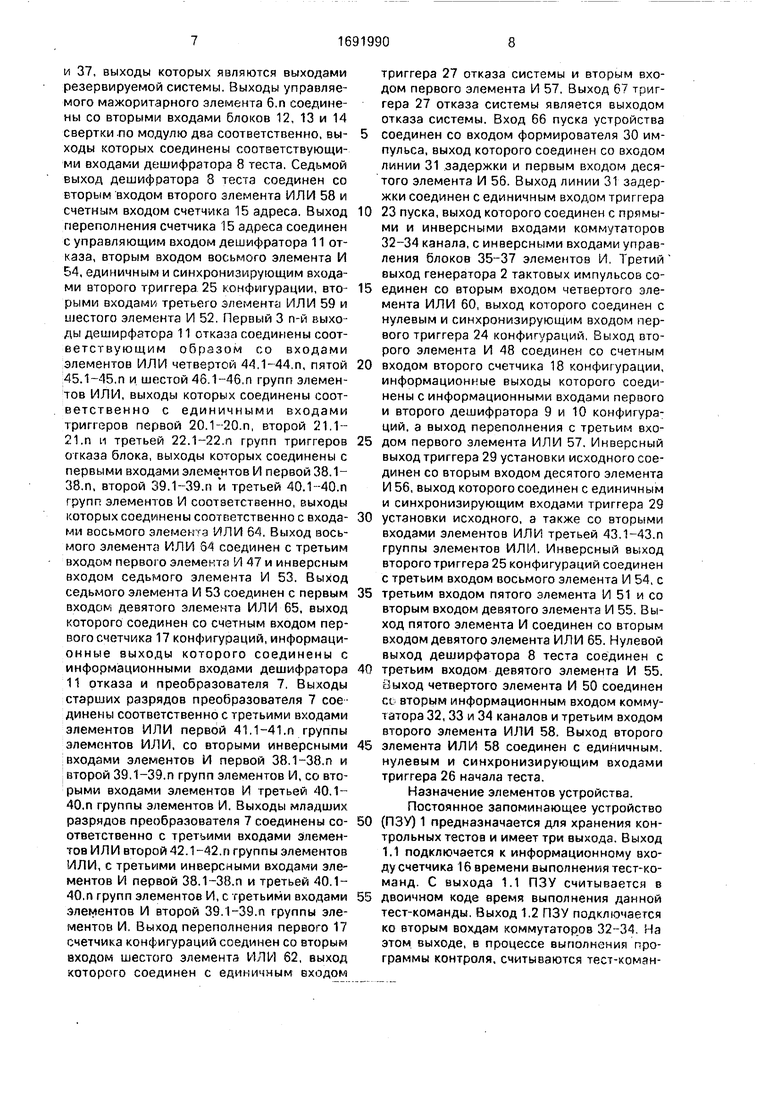

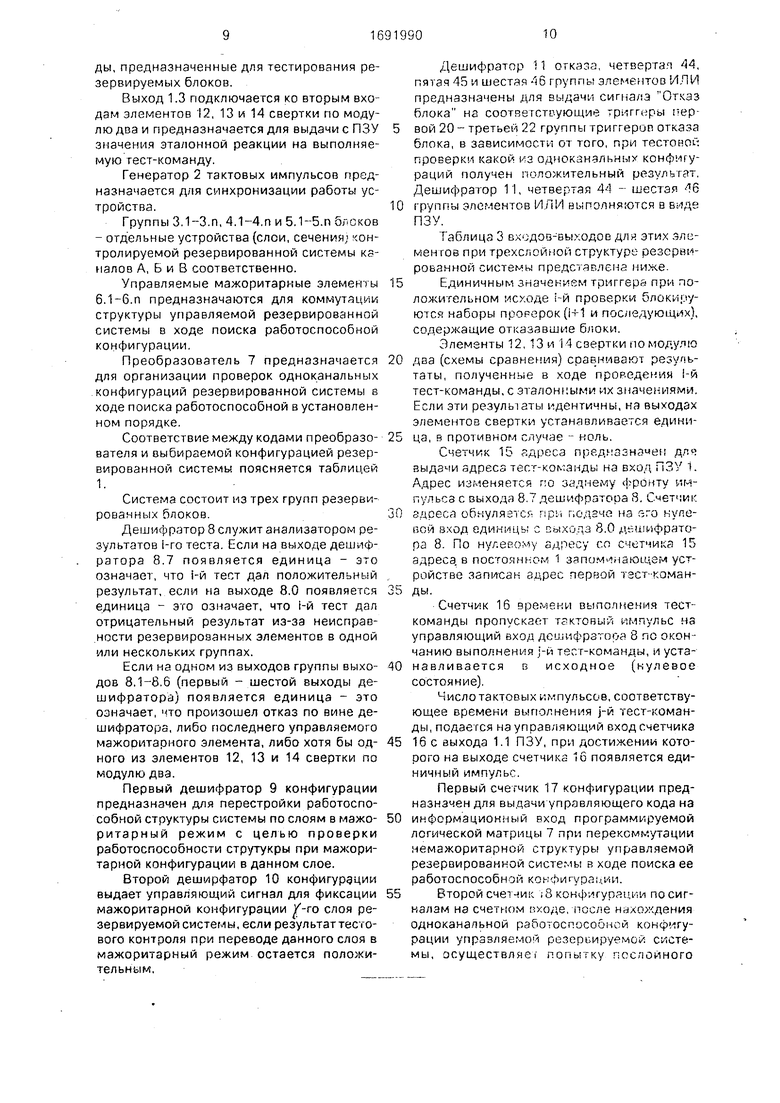

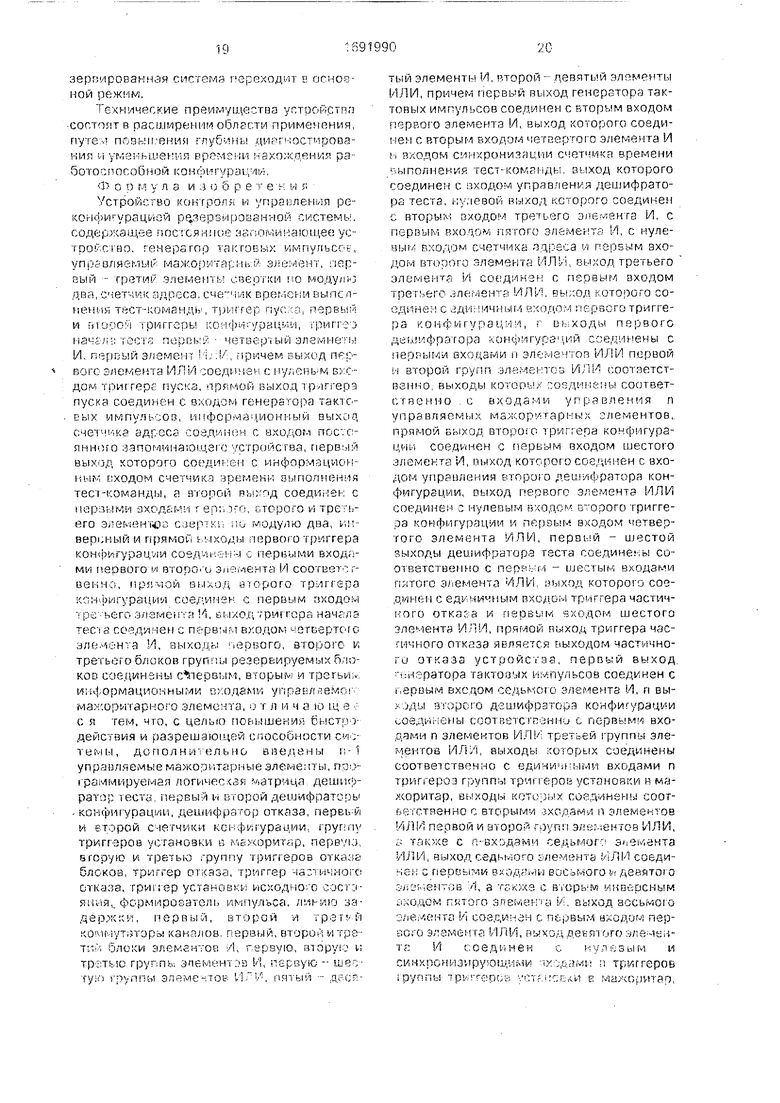

На фиг.1 представлена функциональная схема предлагаемого устройства; на фиг.2 - функциональная схема управляемого мажо0 ритарного элемента; на фиг.З - функциональная схема преобразователя номера проверок в код конфигурации, которую можно реализовать на программируемой логи5 ческой матрице; на фиг.4 - алгоритм работы

устройства; на фиг.5 - вариант временной

диаграммы устройства; на фиг,6 - пример

реализации К-разрядного коммутатора.

Функциональная схема устройства

0 (фиг.1) содержит постоянное запоминающее устройство (ПЗУ) 1, генератор 2 такто- аых импульсов, п групп 3.1,4.1, 5.1...3.П, 4.п, 5.п из трех резервируемых блоков, п управляемых 6.1...6.П мажоритарных элементов,

5 программируемую логическую матрицу 7, дешифратор 8 теста, первый 9 и второй 10 дешифраторы конфигурации, дешифратор 11 отказа, первый 1 12, второй 13 и третий 14 элементы свертки по модулю два, счетчик 15

0 адреса, счетчик 16 времени выполнения тест-команды, первый 17 и второй 18 счетчик фиксации конфигурации, группу триггеров 19..1-19.П установки в мажоритар. первую 20.1-20.п, вторую 21.1-21.п и

5 третью 22.1-22.п группы триггеров отказа блока, триггер 23 пуска, первый 24 и второй 25 триггеры конфигурации, триггер 26 начала теста, триггер 27 отказа, триггер 28 частичного отказа, триггер 29 установки исходного состояния, формирователь 30 импульса, линия 31 задержки, первый 32, второй 33 и третий 34 коммутаторы каналов, первый 35, второй 36 и третий 37 блоки элементов И, первую 38.1-38.п, вторую 39.1-39.п и третью 40.1-40.п группы элементов И, первую 41,1-41.п, вторую 42.1- 42.п, третью 43.1-43. п, четвертую 44.1-44, п, пятую 45.1-45.п и шестую 46.1-46.п группы элементов ИЛИ, первый 47, второй 48, третий 49, четвертый 50, пятый 51, шестой 52, седьмой 53, восьмой 54, девятый 55 и десятый 56 элементы И, первый 57, второй 58, третий 59, четвертый 60, пятый 61, шестой 62, седьмой 63, восьмой 64 и девятый 65 элементы ИЛИ, вход 66 пуска устройства, выход 67 отказа системы, выход 68 частичного отказа, шину 69 установки исходного состояния.

Выход первого элемента ИЛИ 57 соединен с нулевым входом триггера 23 пуска. Прямой выход триггера 23 пуска соединен со входом генератора 2 тактовых импульсов. Информационный выход счетчика 15 адреса соединен со входом ПЗУ 1, первый выход 1.1 которого соединен с информационным входом счетчика 16 времени выполнения тест-команды, а третий 1.3 выход соединен с первыми входами элементов 12, 13 и 14 свертки по модулю два. Инверсный и прямой выходы первого 24 триггера конфигурации соединены с первыми входами первого и второго элементов И 47. 48 соответственно. Прямой выход второго триггера

25конфигурации соединен с первым вхо- домтретьего49 элемента И. Выход триггера

26начала теста соединен с первым входом четвертого элемента И 50. Выходы первого 3.1, второго 4.1 и третьего 5.1 блоков группы резервируемых блоков соединены с первым, вторым и третьим информационными входами управляемого мажоритарного элемента 6.1. Первый выход генератора 2 тактовых импульсов соединен со вторым входом первого элемента И 47, выход которого соединен со вторым входом четвертого элемента И 50 и входом синхронизации счетчика 16 времени выполнения тест-команды, выход которого соединен со входом управления дешифратора 8 теста, нулевой выход которого соединен со вторым входом третьего элемента И 49, с первым входом пятого элемента И 51, с нулевым входом счетчика 15 адреса, и с первым входом второго элемента ИЛИ 58. Выход третьего элемента И 49 соединен с первым вхрдом третьего элемента ИЛИ 59, выход которого соединен с единичным входом первого триггера 24 конфигурации. Выходы первого дешифратора 9 конфигураций соединены с первыми входами л-элементов ИЛИ первой 41 и второй 42 группой элементов ИЛИ соответственно, выходы которых соединены соответственно со входами управления п управляемых мажоритарных элементов 6.1- 6.п. Прямой выход второго триггера 26 кон- 5 фигурации соединен с первым входом шестого элемента И 52, выход которого соединен со входом управления второго дешифратора 10 конфигурации. Выход первого элемента ИЛИ 57 соединен с нупе- 0 вым входом второго триггера 25 конфигурации и с первым входом четвертого элемента ИЛИ 60. Первый 8.1 - шестой 8,6 выходы дешифратора 8 теста соединены соответственно со входами пятого элемента ИЛИ 61,

5 выход которого соединен с единичным входом триггера 28 частичного отказа и первым входом шестого элемента ИЛИ 62. Прямой выход триггера 28 частичного отказа является выходом 68 частичного отказа устройст0 ва. Первый выход генератора 2 тактовых импульсов соединен с первым входом седьмого элемента ИЛИ 53. Выходы дешифратора 10 конфигурации соединены соответственно с первыми входами элемен5 та ИЛИ третьей группы 43.1-43.п элементов ИЛИ, выходы которых соединены соответственно с единичными входами триггеров группы триггеров 19.1-19.п установки в ма- жоритар, выходы которых соединены соот0 ветственно со вторыми входами элементов ИЛИ первой 41.1-41.п и второй 42.1-42,п группы элементов ИЛИ, а также с выходами седьмого элемента ИЛИ 63. Выход седьмого 63 элемента ИЛИ соединен с первыми вхо5 дами восьмого элемента И 54 и девятого элемента И 55, а также с инверсным входом элемента И 51. Выход восьмого элемента И 54 соединен с первым входом первого элемента ИЛИ 57. Выход девятого элемента И

0 55 соединен с нулевыми и синхронизирующими входами триггеров группы триггеров 19.1-19.П установки в мажоритар. Третий выход ПЗУ соединен со вторыми информационными входами коммутаторов 32-34 ка5 налов, первые информационные входы которых являются входами резервируемой системы, а выходы соединены со входами первого 3.1 - третьего 5.1 блоков первой группы резервируемых блоков соответст0 венно. Выходы первого 6.1 управляемого мажоритарного элемента соединены со входами первого 3.2 - третьего 5.2 блоков второй группы резервируемых блоков, выходы которых соединены соответственно с входа5 ми второго 6.2 управляемого мажоритарного элемента. Выходы первого 3 л-третьего 5,п блоков n-группы резервируемых бпоков соединены с входами n-го управляемого мажоритарного элемента 6.п, выходы которого соединены со входами элементов И 35. 36

и 37, выходы которых являются выходами резервируемой системы. Выходы управляемого мажоритарного элемента б.п соединены со вторыми входами блоков 12, 13 и 14 свертки по модулю два соответственно, выходы которых соединены соответствующими входами дешифратора 8 теста. Седьмой выход дешифратора 8 теста соединен со вторым входом второго элемента ИЛИ 58 и счетным входом счетчика 15 адреса. Выход переполнения счетчика 15 адреса соединен с управляющим входом дешифратора 11 отказа, вторым входом восьмого элемента И 54, единичным и синхронизирующим входами второго триггера 25 конфигурации, вторыми входами третьего элемента ИЛИ 59 и шестого элемента И 52. Первый 3 n-й выходы деширфатора 11 отказа соединены соответствующим образом со входами элементов ИЛИ четвертой 44.1-44.П, пятой 45.1-45.П и шестой 46.1-46.п групп элементов ИЛИ, выходы которых соединены соответственно с единичными входами триггеров первой 20.1-20.п, второй 21.1- 21.п и третьей 22.1-22.п групп триггеров отказа блока, выходы которых соединены с первыми входами элементов И первой 38.1- 38.п, второй 39.1-39.п и третьей 40.1-40.ti групп элементов И соответственно, выходы которых соединены соответственно с входами восьмого элемента ИЛИ 64. Выход восьмого элемента ИЛИ 64 соединен с третьим входом первого элемента И 47 и инверсным входом седьмого элемента И 53. Выход седьмого элемента И 53 соединен с первым входом девятого элемента ИЛИ 65, выход которого соединен со счетным входом первого счетчика 17 конфигураций, информационные выходы которого соединены с информационными входами дешифратора 11 отказа и преобразователя 7. Выходы старших разрядов преобразователя 7 соединены соответственно с третьими входами элементов ИЛИ первой 41.1-41.п группы элементов ИЛИ, со вторыми инверсными входами элементов И первой 38.1-38.п и второй 39.1-39.п групп элементов И, со вторыми входами элементов И третьей 40.1- 40.п группы элементов И. Выходы младших разрядов преобразователя 7 соединены соответственно с третьими входами элементов ИЛИ второй 42.1-42.п группы элементов ИЛИ, с третьими инверсными входами элементов И первой 38.1-38.П и третьей 40.1- 40.п групп элементов И, с третьими входами элементов И второй 39.1-39.п группы элементов И. Выход переполнения первого 17 счетчика конфигураций соединен со вторым входом шестого элемента ИЛИ 62. выход которого соединен с единичным входом

триггера 27 отказа системы и вторым входом первого элемента И 57. Выход 6 триггера 27 отказа системы является выходом отказа системы. Вход 66 пуска устройства

соединен со входом формирователя 30 импульса, выход которого соединен со входом линии 31 задержки и первым входом десятого элемента И 56. Выход линии 31 задержки соединен с единичным входом триггера

23 пуска, выход которого соединен с прямыми и инверсными входами коммутаторов 32-34 канала, с инверсными входами управления блоков 35-37 элементов И. Третий выход генератора 2 тактовых импульсов соединен со вторым входом четвертого элемента ИЛИ 60, выход которого соединен с нулевым и синхронизирующим входом первого триггера 24 конфигураций. Выход второго элемента И 48 соединен со счетным

входом второго счетчика 18 конфигурации, информационные выходы которого соединены с информационными входами первого и второго дешифратора 9 и 10 конфигураций, а выход переполнения с третьим входом первого элемента ИЛИ 57. Инверсный выход триггера 29 установки исходного соединен со вторым входом десятого элемента И 56, выход которого соединен с единичным и синхронизирующим входами триггера 29

установки исходного, а также со вторыми входами элементов ИЛИ третьей 43.1-43.п группы элементов ИЛИ. Инверсный выход второго триггера 25 конфигураций соединен с третьим входом восьмого элемента И 54, с

третьим входом пятого элемента И 51 и со вторым входом девятого элемента И 55. Выход пятого элемента И соединен со вторым входом девятого элемента ИЛИ 65. Нулевой выход деширфатора 8 теста соединен с

третьим входом девятого элемента И 55. Выход четвертого элемента И 50 соединен со вторым информационным входом коммутатора 32, 33 и 34 каналов и третьим входом второго элемента ИЛИ 58. Выход второго

элемента ИЛИ 58 соединен с единичным, нулевым и синхронизирующим входами триггера 26 начала теста.

Назначение элементов устройства. Постоянное запоминающее устройство

(ПЗУ) 1 предназначается для хранения контрольных тестов и имеет три выхода. Выход 1.1 подключается к информационному входу счетчика 16 времени выполнения тест-команд. С выхода 1.1 ПЗУ считывается в

5 двоичном коде время выполнения данной тест-команды. Выход 1.2 ПЗУ подключается ко вторым вохдам коммутаторов 32-34. На этом выходе, в процессе выполнения программы контроля, считываются тест-команды, предназначенные для тестирования резервируемых блоков.

Выход 1.3 подключается ко вторым входам элементов 12, 13 и 14 свертки по модулю два и предназначается для выдачи с ПЗУ значения эталонной реакции на выполняемую тест-команду.

Генератор 2 тактовых импульсов предназначается для синхронизации работы устройства.

Группы 3.1-З.п, 4.1-4.П и 5..п блоков - отдельные устройства(слои,сечения;контролируемой резервированной системы каналов А, Б и В соответственно.

Управляемые мажоритарные элементы 6.1-б.п предназначаются для коммутации структуры управляемой резервированной системы в ходе поиска работоспособной конфигурации.

Преобразователь 7 предназначается для организации проверок одноканальных конфигураций резервированной системы в ходе поиска работоспособной в установленном порядке.

Соответствие между кодами преобразователя и выбираемой конфигурацией резервированной системы поясняется таблицей 1.

Система состоит из трех групп резервированных блоков.

Дешифратор 8 служит анализатором результатов 1-го теста. Если на выходе дешифратора 8.7 появляется единица - это означает, что i-й тест дал положительный результат, если на выходе 8.0 появляется единица - это означает, что i-й тест дал отрицательный результат из-за неисправности резервированных элементов в одной или нескольких группах.

Если на одном из выходов группы выходов 8.1-8.6 (первый - шестой выходы дешифратора) появляется единица - это означает, что произошел отказ по вине дешифратора, либо последнего управляемого мажоритарного элемента, либо хотя бы одного из элементов 12, 13 и 14 свертки по модулю два.

Первый дешифратор 9 конфигурации предназначен для перестройки работоспособной структуры системы по слоям в мэжо- ритарный режим с целью проверки работоспособности струтукры при мажоритарной конфигурации в данном слое.

Второй деширфатор 10 конфигурации выдает управляющий сигнал для фиксации мажоритарной конфигурации /-го слоя резервируемой системы, если результат тестового контроля при переводе данного слоя в мажоритарный режим остается положительным.

Дешифратор 11 отказа, четвертая 44, пятая 45 и шестая 46 группы элементов ИЛИ предназначены для выдачи сигнала Отказ блока на соответствующие триггеры пер- 5 вой 20- третьей 22 группы триггеров отказа блока, в зависимости от того, при тестовой проверки какой из ОДНОКЗНЗЛЬНЫУ конфигураций получен положительный результат. Дешифратор 11, четвертая 44 - шестая 46 0 группы элементов ИЛИ выполняются в виде ПЗУ.

Таблица 3 входов-выходов для этих зле- менгов при трехслойной структуре резервированной системы представлена ниже.

5Единичным значением триггера при положительном исходе i-й проверки блокируются наборы проверок (К 1 и последующих), содержащие отказавшие блоки.

Элементы 12,13 и 14 свертки по модулю

0 два (схемы сравнения) сравнивают результаты, полученные в ходе проведения i-й тест-команды, с эталонными их значениями. Если эти результаты идентичны, на выходах элементов свертки устанавливается едини5 ца, в противном случае - ноль.

Счетчик 15 адреса предназначен для выдачи адреса тест-команды на вход ПЗУ 1. Адрес изменяется по заднему фронту импульса с выхода 8.7 дешифратора 8. Счетчик

0 адреса обнуляется при подаче на яго нулевой вход единицы с выхода 8.0 дешифратора 8. По нулевому адресу сп счычика 15 адреса в постоянном 1 запоминающем устройстве записан адрес первой тзст-коман5 ды.

Счетчик 16 времени выполнения тест- команды пропускает тактовый импульс на управляющий вход дешифратора 8 лс окончанию выполнения j-й тест-команды, и устз0 навливзется в исходное (нулевое состояние).

Число тактовых импульсов, соответствующее времени выполнения j-й тест-команды, подается на управляющий входсчетчикз

5 16с выхода 1.1 ПЗУ, при достижении которого на выходе счетчика 16 появляется единичный импульс.

Первый счегчик 17 конфигурации предназначен для выдачи управляющего кода на

0 инфоомзционный вход программируемой логической матрицы 7 при перекоммутзции мемажоритарной структуры управляемой резервированной системы в ходе поиска ее работоспособной конфигурации.

5Второй счетчик i8 конфигурации по сигналам на счетном входе, после нахождения одноканальной работоспособной конфигурации управляемой резервируемся системы, осуществляет попытку послойного

перевода ее в мажоритарную конфигурацию.

Группа триггеров 19.1-19.п установки в мажоритар, третья группа 43.1-43.п элементов ИЛИ предназначены для установки системы в мажоритарную конфигурацию перед первым прерыванием или по управляющим сигналам от дешифратора 10. Первая 20.1- 20,п, вторая 21.1-21.п и третья 22.1-22.п группы триггеров отказа блоков, первая 38.1-38.П, вторая 39.1-39.п и третья 40.1- 40.п группы элементов И, восьмой 64 элемент ИЛИ формируют сигнал запрета тестирования заведомо неработоспособной конфигурации системы, и выдают разрешение на запись следующего тактового импульса в счетчик 17.

Триггер 23 пуска устанавливается в единичное состояние при появлениии положительного импульса на выходе линии задержки 31, и служит для запуска и остановки генератора 2 тактовых импульсов.

Первый триггер 24 конфигурации, элементы И 47 и И 48 определяют порядок записи синхронизирующих импульсов в счетчики 16 времени выполнения тест-команды и 18 конфигурации.

Второй 25 триггер конфигурации устанавливается в единичное состояние после нахождения одноканзльной работоспособной конфигурации резервируемой системы. Он определяет совместно с элементами И 49 и ИЛИ 59, И 51 и ИЛИ 65. И 52 порядок записи информации в первый триггер 24 конфигурации, первый счетчик 17 конфигурации, второй дешифратор 10 конфигурации соответственно.

Триггер 26, элементы И 50 и ИЛИ 58 прденазначены для формирования управляющего сигнала начала теста - инициализации выполнения тестовой программы. Триггер 26 устанавливается в единичное состояние по заднему фронту импульсов с выходов 8.0 и 8.7 дешифратора 8 теста, а затем посредством обратной связи с выхода элемента И 50 устанавливается в нулевое состояние.

Триггер 27 отказа системы, элемент ИЛИ 62 предназначены для формирования сигнала на выход 67 отказа системы.

Триггер 28 частичного отказа и элемент ИЛИ 61 предназначены для формирования сигнала на выход 68 частичного отказа устройства.

Триггер 29 установки исходного состояния и девятый элемент И 55 служат для первоначальной установки системы в мажоритарный режим.

Формирователь 30 импульса позволяет сформировать единичный импульс по команде контроля от внешнего устройства. Линия 31 задержки позволяет осуществить первоначальную перекоммутацию устройства контроля до начала проверок.

Коммутаторы каналов А, Б и В - 32, 33 и 34 служат для выбора направления приема информации на информационные входы

группы из трех резервируемых блоков. Управление коммутаторами осуществляется с прямого выхода триггера 23.

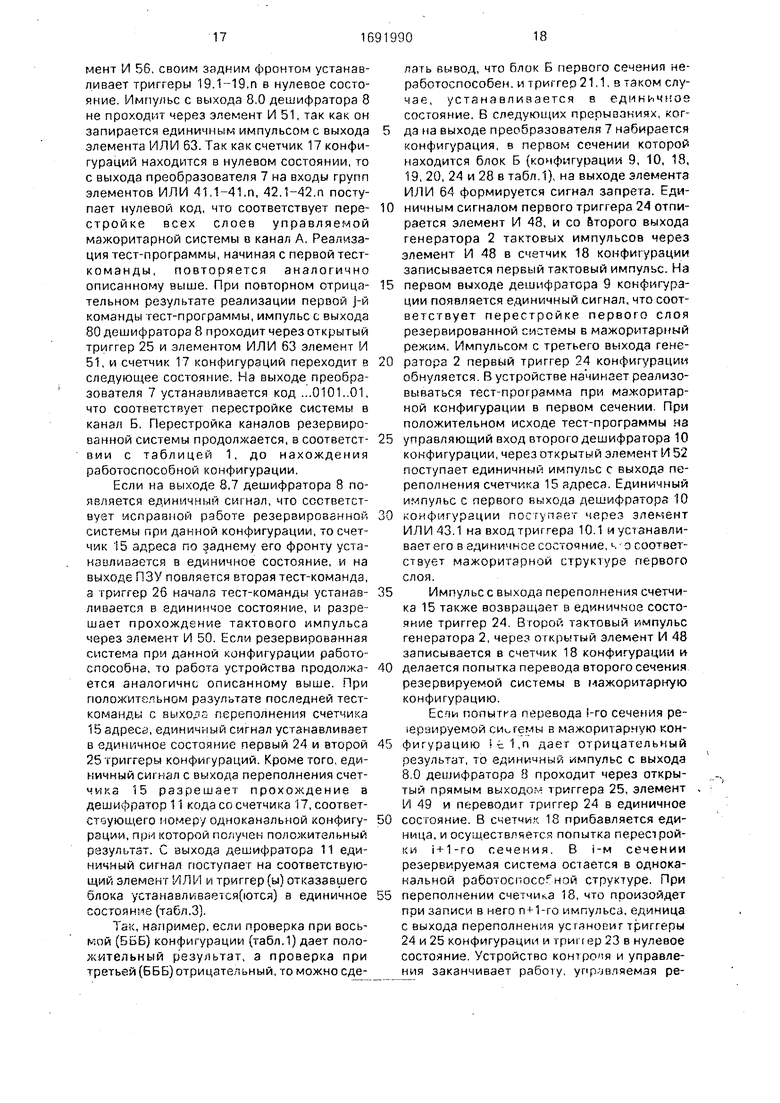

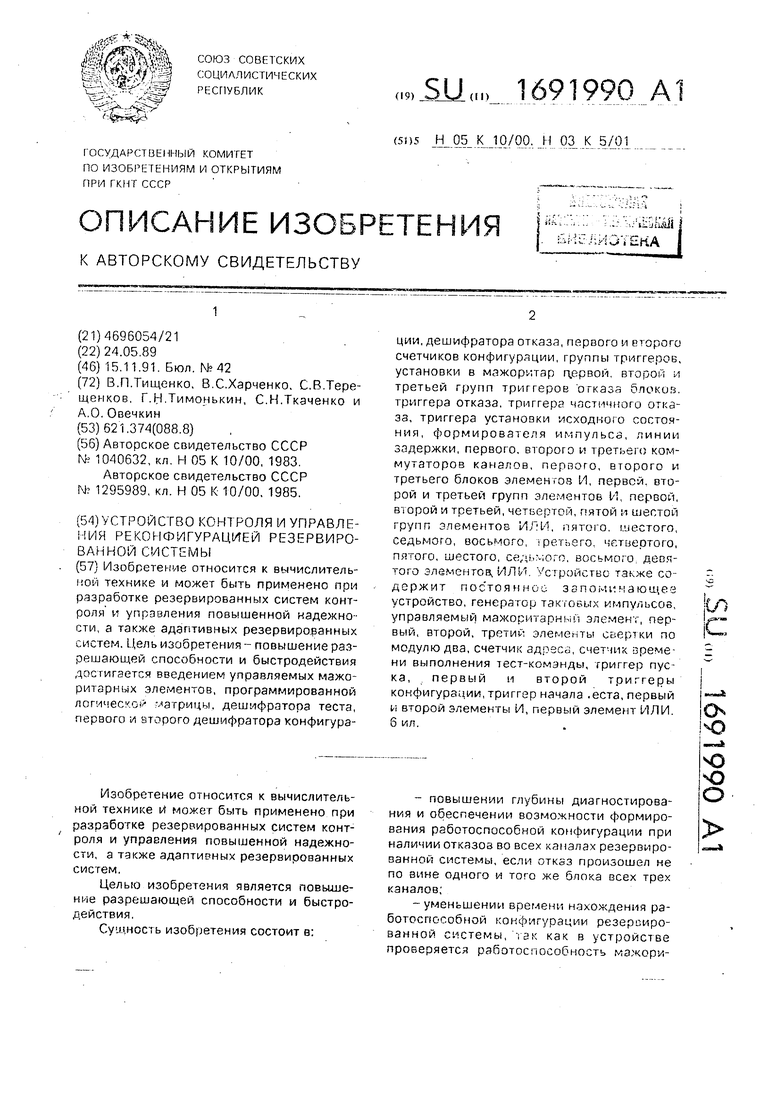

Пример реализации К-рззрядного коммутатора представлен на фиг.6. На вторые

5 входы коммутаторов поступает в параллельном (К-разрядном) коде информация от внешних устройств (например, датчиков информации) в основном режиме работы резервированной системы. С выходов блоков

0 элементов И 35-37 снимается информация в основном режиме работы. В процессе режима Контроль вторые входы коммутаторов 32-34 и выходы блоков элементов И 35-37 блокируются управляющими сигналами.

5 Значения кодов и разрядность входов и выходов системы зависят от конкретных особенностей выполнения системы.

Первая 41.1-41.п и вторая 42.1-42.п группы элементов ИЛИ пропускают управ0 ляющие сигналы от преобразователя 7, первого дешифратора конфигурации 9, или группы 19.1-19.п триггеров установки в мажоритар при перестройке структуры управляемой резервированной системы.

5 Седьмой элемент И 53 пропускает на свой выход татковый импульс с выхода генератора 2 тактовых импульсов, если в подго- товленной к тестовому контролю конфигурации имеется заведомо неисправ0 ный блок.

Восьмой элемнет И 54 позволяет выдавать управляющий сигнал на прекращение тестового контроля, если контроль мажоритарной (частично мажоритарной) структуры

5 дал положительный результат.

Десятый элемент И 56 обнуляет группу триггеров 19.1-19.п в случае отрицательного результата тестового контроля мажоритарной (частично мажоритарной)

0 конфигурации.

Первый элемент ИЛИ 57 выдает на нулевой вход триггера 18 пуска единицу при положительном результате программы тестового контроля, при частичном, или полном

5 отказе устройства.

Через элемент ИЛИ 60 устанавливается в нулевое состояние триггер 24 конфигурации, или по синхроимпульсу третьего с выхода генератора 2 тактовых импульсов, или по окончанию работы устройства.

Третий элемент ИЛИ 64 контролирует наличие мажоритарного (частично мажоритарного) состояния системы.

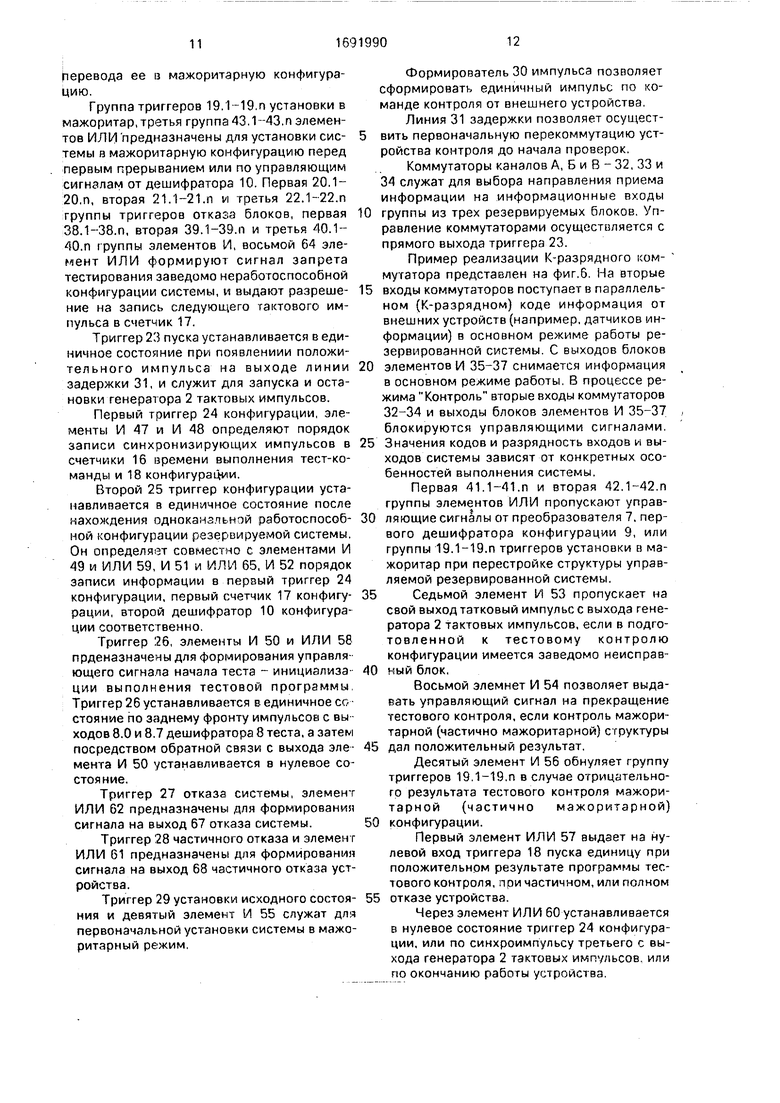

Управляемый мажоритарный блок б (фиг.2} содержит мультиплексоры 70, 71 и 72, мажоритарные элементы 73, 74 и 75.

Если на адресные входы мультиплексоров поступает код на выходы управляемого мажоритарного блока поступает информация с выходов мажоритарных элементов; информация канала А; 10 - канала Б, 11 - канала В.

На фиг.З представлена схема преобразователя 7, реализующая систему уравнений (1) и выполненная на биполярных элементах.

X1X2X3X4X5 + X1X2X3X4X5+

+ XlX2X3X 4X5 + XlX2X3X4X5+

+ X1X2X3X4X5 + X1X2X3X4X5+

X1X2X3X4X5 + X1X2X3X4X5+

+ XlX2X3X4X5 + XiX2X3X4X5+

+ XlX2X3X4X5 + X1X2X3X4X5+

X1X2X3X4X5 + X1X2X3X4X5+

+ X1X2X3X4X5 + X lX2X3X4X5+

+ X1X2X3X4X5 + X1X2X3X4X5+

X 1X2X3X X5 + XlX2X3X4X5+

+ X1X2X3X4X5 + X1X2X3X4X5+

t- X1X2X3X4X5 + X1X2X3X4X5+

Х1Х 2ХзХ4Х5 + XlX2X3X4X5+

-i X1X2X3X4X5 + X1X2X3X4X5f

+ X1X2X3X4X5 + X1X2X3X4X5+

X1X2X3X4X5 + XjX2X3X4X5+

+ XiX2X3XjjX5 + Х1Х2ХзХ4Х5+

+ XiX2X3X4X5 + XiX2XaX4X5+

Системой уравнения (i) описывается преобразователь 7 (фиг.З) для трехслойной структуры резервированной системы, гдеХт Xs - входы ПЛМ (Xi - младший разряд, Х5 - старший) у1туб выходы ПЛМ (yiy2 - входы мажоритарного элемента б, 1; узу4 - элемента 6.2; уаУб - элемента 6.3).

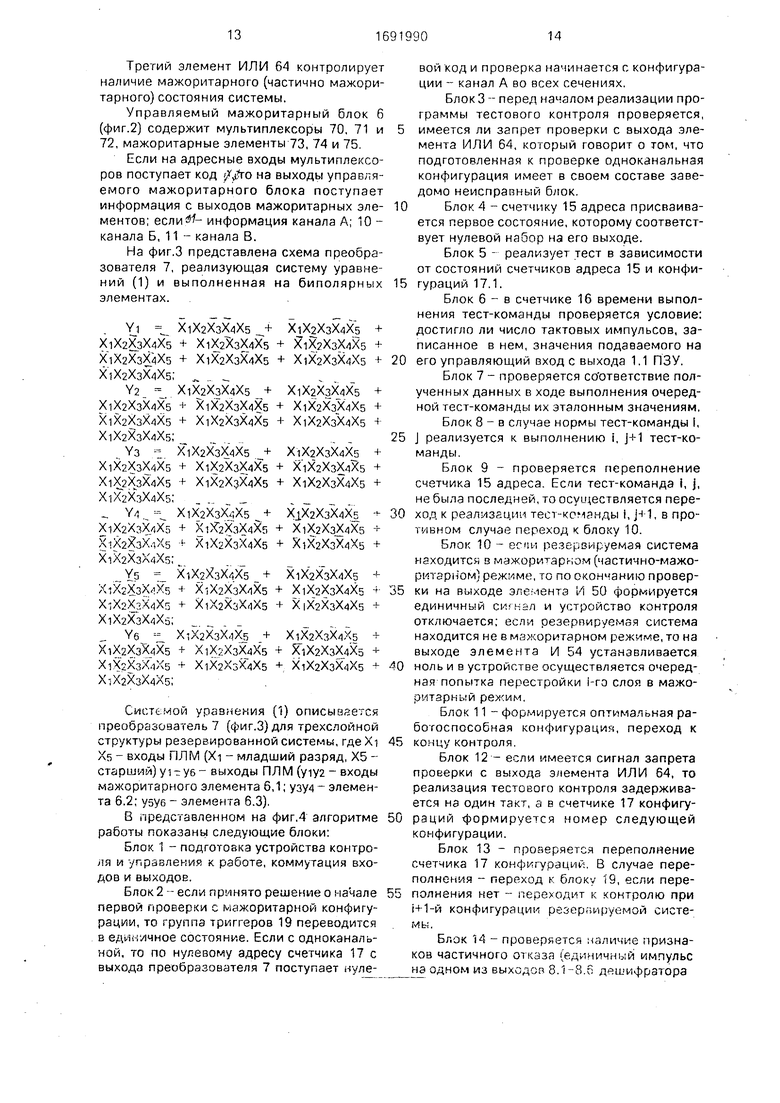

В представленном на фиг.4 алгоритме работы показаны следующие блоки:

Блок 1 - подготовка устройства контроля и управления к работе, коммутация входов и выходов.

Блок 2 -- если принято решение о начале первой проверки с мажоритарной конфигурации, то группа триггеров 19 переводится в единичное состояние. Если с одноканаль- ной, то по нулевому адресу счетчика 17 с выхода преобразователя 7 поступает нулевой код и проверка начинается с конфигурации - канал А во всех сечениях.

Блок 3 - перед началом реализации программы тестового контроля проверяется, 5 имеется ли запрет проверки с выхода элемента ИЛИ 64, который говорит о том, что подготовленная к проверке одноканальная конфигурация имеет в своем составе заведомо неисправный блок.

0 Блок 4 - счетчику 15 адреса присваивается первое состояние, которому соответствует нулевой набор на его выходе.

Блок 5 - реализует тест в зависимости от состояний счетчиков адреса 15 и конфи5 гураций 17.1.

Блок 6 в счетчике 16 времени выполнения тест-команды проверяется условие: достигло ли число тактовых импульсов, записанное в нем, значения подаваемого на

0 его управляющий вход с выхода 1.1 ПЗУ.

Блок 7 - проверяется соответствие полученных данных в ходе выполнения очередной тест-команды их эталонным значениям. Блок 8 - в случае нормы тест-команды I,

5 j реализуется к выполнению i, j+1 тест-команды.

Блок 9 - проверяется переполнение счетчика 15 адреса. Еспи тест-команда i, J, не была последней, то осуществляется пере0 ход к реализации тест-команды I, j-i 1, в противном случае переход к блоку 10.

Блок 10 - резервируемая система находится в мажоритарном (частично-мажоритарном) режиме, то по окончанию провер5 ки на выходе элемента И 50 формируется единичный сигнал и устройство контроля отключается; если резервируемая система находится не в мажоритарном режиме, то на выходе элемента И 54 устанавливается

0 ноль и в устройстве осуществляется очередная попытка перестройки 1-го слоя в мажоритарный режим.

Блок 11 -формируется оптимальная работоспособная конфигурации, переход к

5 концу контроля.

Блок 12 - если имеется сигнал запрета проверки с выхода элемента ИЛИ 64, то реализация тестового контроля задерживается на один такт, а в счетчике 17 конфигу0 раций формируется номер следующей конфигурации.

Блок 13 - проверяется переполнение счетчика 17 конфигураций. В случае переполнения - переход к блоку 19, если пере5 полнения нет - к контролю при i+1-й конфигурации резервируемой системы.

Блок 14 - проверяется наличие признаков частичного отказа (единичный импульс на одном из выходов 8.1-8 6 дешифратора

8), если отказ системы является частичным - переход к блоку 19, если нет - к блоку 15. Блок 15 - если отказ происходит до нахождения работоспособной конфигурации, то продолжается ее поиск, если после, осуществляется попытка перевода очередного слоя в мажоритарный режим.

Блок 16-если отказ не является частичным и работоспособная структура не найдена, то счетчику конфигураций присваивается i+1-я конфигурация.

Блок 17 - осуществляется попытка перевода очередного слоя резервируемой системы в мажоритарный режим.

Блок 18 - проверяется условие: осуществляется ли попытка перевода в мажоритарное состояние всех слоев управляемой резервируемой системы. Если да - переход к блоку 11, если нет - к блоку 3.

Блок 19 - на выход 67 (68) устройства выдается единица, если счетчиком конфигурации перебраны все возможные конфигурации резервированной системы, но работоспособное состояние не найдено, т.е. в одном из слоев резервированной системы происходит отказ всех трех блоков, или если зафиксирован частичный отказ.

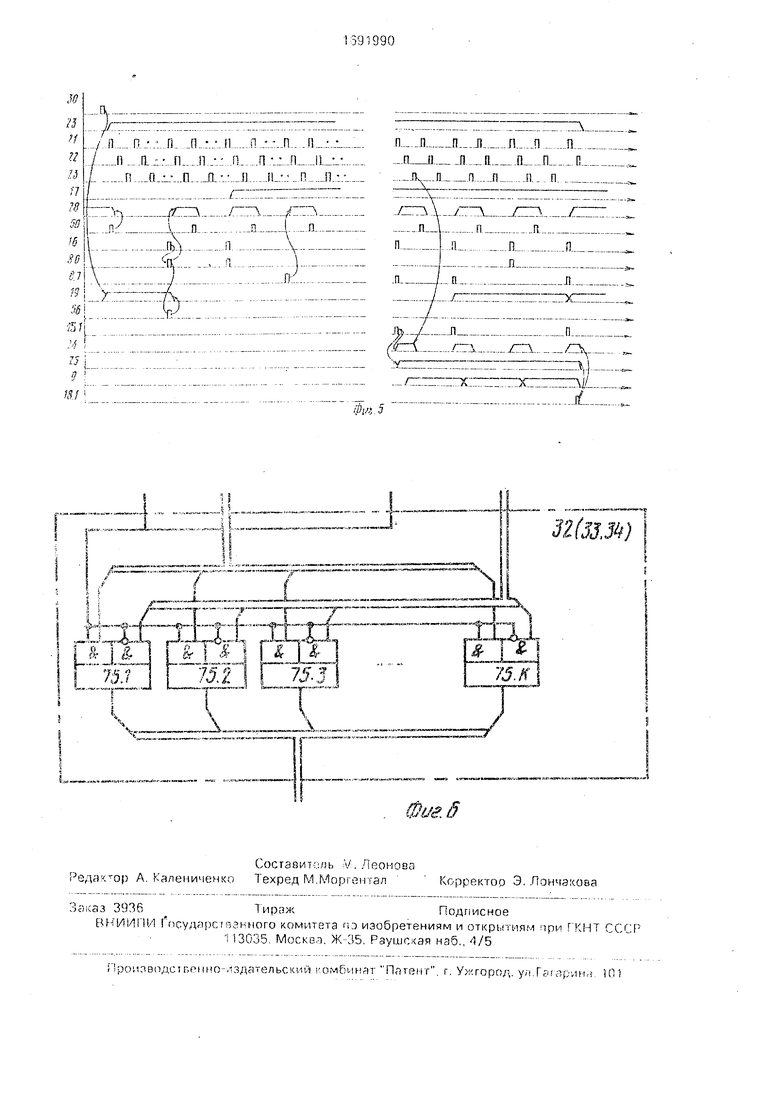

В представленной на фиг.5 временной диаграмме работы устройства введены следующие обозначения: 30, 23, 17, 26, 50, 16, 19, 56, 24, 25, 9 - выходы элементов в соответствии с их номерами сфиг.1, 2.1, 2.2,2.3. 8.0,8.7,15.1,18.1 - номера выходов элементов в соответствии с фиг.1.

Устройство контроля и управления работает следующим образом.

В исходном состоянии, что соответствует нулевому адресу счетчика 15, на выходе постояного запоминающего устройства 1 присутствует код первой тест-команды программы контроля резервированной системы, триггер 26 начала теста в единичном состоянии, все остальные элементы памяти обнулены. Если контроль начинается не с мажоритарной конфигурации системы, а с перебора одноканальных, то триггер 29 устанавливается в исходное единичное состояние по входу S. Цели установки исходного состояния условно не показаны.

При поступлении на вход 66 пуска устройства единицы, формирователь 30 импульса формирует единичный импульс, который проходит через открытый элемент И 56 и устанавливает группу триггеров 19 в единичное состояние, что соответствует мажоритарной структуре системы.

В триггер 29 установки исходного состояния записывается единица и элемент И 56 запирается на все время работы устройства. После перестройки структуры в мажоритарный режим, на выходе задержки 31 появляется единичный импульс, триггер 23 пуска устанавливается в единичное состояние и запускает генератор 2 тактовых импульсов.

Сигнал с прямого выхода триггера 23 пуска подготавливает коммутаторы 32-34 каналов к пропуску информации с выхода постоянного запоминающего устройства 1, и запрещает выдачу информации через блоки 35-37

0 элементов И на выходы резервированной системы. Первый тактовый импульс со второго выхода генератора 2 тактовых импульсов проходит через элемент И 47, открытый единичными значениями на инверсных вы5 ходах триггера 24 и элемента ИЛИ 64, затем через элемент И 50, открытый единичным значением выхода триггера 26. Этот импульс поступает в общую шину второго выхода ПЗУ 1. Так как, коммутаторы 32-34

0 настроены единичным значением триггера 23 на прием информации по первому входу, то на входы резервируемых блоков 3.1, 4.1 и 5.1 поступают значения с этого входа. Тактовый импульс, поступивший в общую шину,

5 определяет начало реализации первой тест- команды. В счетчике 16 времени выполнения тест-команды отсчитывается первый такт выполнения теста. Импульс с выхода элемента И 50 проходит через элемент ИЛИ

0 58 и обнуляется триггер 26 начала теста, нулевым сигналом которого запирается элемент И 50, что исключает повторную подачу первой тест-команды в резервируемое устройство во время ее выполнения. Во время

5 выполнения первой тест-команды в резервируемом устройстве счетчик 16 производит подсчет тактовых импульсов с выхода генератора 2 тактовых импульсов. Когда это число достигнет значения кода подаваемого на

0 управляющий вход счетчика 16 с первого выхода ПЗУ, что соответствует максимальному времени выполнения первой тест-команды, то на его выход пропускается единичный импульс, который опрашивает

5 дешифратор 8 (счетчик 16 при этом обнуляется). Элементы 12-14 сравнивают результаты, полученные в ходе реализации первой тест-команды, с эталонными значениями, записанными на третьем выходе ПЗУ 1. В

0 случае совпадения, на их выходах появляются единицы, при несовпадении - нули.

Если реализация первой тест-команды дает отрицательный результат, то в этом случае на выходе элементов 12, 13 и 14 ло5 являются нули и единичный импульс с выхода счетчика 16 проходит на выход 8.0 дешифратора 8, который устанавливает в нулевое состояние счетчик 15, в единичное состояние триггер 26 и, пройдя через открытый триггером 25 и элементом ИЛИ 63 элемент И 56, своим задним фронтом устанавливает триггеры 19.1-19.п в нулевое состояние, Импульс с выхода 8.0 дешифратора 8 не проходит через элемент И 51, так как он запирается единичным импульсом с выхода элемента ИЛИ 63. Так как счетчик 17 конфигураций находится в нулевом состоянии,то с выхода преобразователя 7 на входы групп элементов ИЛИ 41,1-41.п, 42.1-42.п поступает нулевой код, что соответствует перестройке всех слоев управляемой мажоритарной системы в канал А. Реализация тест-программы, начиная с первой тест- команды, повторяется аналогично описанному выше. При повторном отрицательном результате реализации первой j-й команды тест-программы, импульс с выхода 80 дешифратора 8 проходит через открытый триггер 25 и элементом ИЛИ 63 элемент И 51, и счетчик 17 конфигураций переходит в следующее состояние. На выходе преобразователя 7 устанавливается код ...0101..01, что соответствует перестройке системы в канал Б, Перестройка каналов резервированной системы продолжается, в соответствии с таблицей 1, до нахождения работоспособной конфигурации.

Если на выходе 8.7 дешифратора 8 появляется единичный сигнал, что соответствует исправной работе резервированной системы при данной конфигурации, то счетчик 15 адреса по заднему его фронту устанавливается в единичное состояние, и на выходе ПЗУ повляется вторая тест-команда, а триггер 26 начала тест-команды устанавливается в едининчое состояние, и разрешает прохождение тактового импульса через элемент И 50. Если резервированная система при данной конфигурации работоспособна, то работа устройства продолжается аналогично описанному выше. При положительном результате последней тест- команды с выходе- переполнения счетчика 15 адреса, единичный сигнал устанавливает в единичное состояние первый 24 и второй 25 триггеры конфигураций. Кроме того, единичный сигнал с выхода переполнения счет- чика 15 разрешает прохождение в дешифратор 11 кода со счетчика 17, соответствующего номеру одноканальной конфигурации, при которой получен положительный результат. С выхода дешифратора 11 единичный сигнал поступает на соответствующий элемент ИЛИ и триггер (ы) отказавшего блока устанавливается(ются) в единичное состояние (табл.3).

Так. например, если проверка при восьмой (ББВ) конфигурации (табл.1) дзет положительный результат, а проверка при третьей (БББ) отрицательный, то можно сделать вывод, что блок Б первого сечения неработоспособен, и триггер 21.1,в таком случае, устанавливается в единичное состояние. В следующих прерываниях, ког- 5 да на выходе преобразователя 7 набирается конфигурация, в первом сечении которой находится блок Б (конфигурации 9, 10, 18, 19, 20, 24 и 28 в табл.1), на выходе элемента ИЛИ 64 формируется сигнал запрета. Еди- 0 ничным сигналом первого триггера 24 отпирается элемент И 48, и со второго выхода генератора 2 тактовых импульсов через элемент И 48 в счетчик 18 конфигурации записывается первый тактовый импульс. На

5 первом выходе дешифратора 9 конфигурации появляется единичный сигнал, что соответствует перестройке первого слоя резервированной системы в мажоритарный режим. Импульсом с третьего выхода гене0 ратора 2 первый триггер 24 конфигурации обнуляется. В устройстве начинает реализовываться тест-программа при мажоритарной конфигурации в первом сечении. При положительном исходе тест-программы на

5 управляющий вход второго дешифратора 10 конфигурации, через открытый элемент И 52 поступает единичный импульс с выхода переполнения счетчика 15 адреса. Единичный импульс с первого выхода дешифратора 10

0 конфигурации поступает через элемент ИЛИ 43.1 на вход триггера 10.1 и устанавливает его в единичное состояние, ч- о соответствует мажоритарной структуре первого слоя.

5Импульс с выхода переполнения счетчика 15 также возвращает в единичное состояние триггер 24. Второй тактовый импульс генератора 2, через открытый элемент И 48 записывается в счетчик 18 конфигурации и

0 делается попытка перевода второго сечения резервируемой системы в мажоритарную конфигурацию.

Если попытка перевода 1-го сечения ре- (ервируемой системы в мажоритарную кон5 фигурацию г.1,п дает отрицательный результат, то единичный импульс с выхода 8.0 дешифратора 8 проходит через открытый прямым выходом триггера 25, элемент И 49 и переводит триггер 24 в единичное

0 состояние. В счетчик 18 прибавляется единица, и осуществляется попытка перестройки i + 1-го сечения. В i-м сечении резервируемая система остается в одноканальной работоспособной структуре. При

5 переполнении счетчика 18, что произойдет при записи в него п+1-го импульса, единица с выхода переполнения установит триггеры 24 и 25 конфигурации и триггер 23 в нулевое состояние. Устройство контропя и управления заканчивает работу, управляемая резервированная система переходит в основной режим.

Технические преимущества устройства состоят в расширении области применения, путем повышения глубины диагностирования м уменьшения времени нахождения работоспособной конфигурации.

Формула изобретения Устройство контроля и управления реконфигурацией резервированной системы, содержащее постоянное запоминающее устройство, генератор тактовых импульсов, управляемый мажоритарный элемент, первый - третий элементы свертки по модулю два, счетчик адреса, счетчик времени выполнения тест-команды, триггер пуска, первый и второй триггеры конфигураций, триггер начала тоста, первый. - четвертый элемнеты И, первый элемент И, il/l, причем выход первого элемента ИЛИ соединен с нулевым входом триггера пуска, прямой выход триггера пуска соединен с входом генератора тактовых импульсов, информационный выход счетчика адреса соединен с входом постоянного запоминающего устройства, первый выход которого соединен с информационным входом счетчика времени выполнения тест-команды, а второй выход соединен с первыми сходами пеппого, второго и третьего элементов саерткг: по модулю два, инверсный и прямой выходы первого триггера конфигурации соединены с первыми входами первого и второго элемента И соответственно, прямой выход второго триггера конфигурации соединен с первым входом | ретьего элемента И, выход триггера начала теста соединен с первым входом четвертого элемента 1/1, выходы первого, второго и третьего блоков группы резервируемых блоков соединены с первым, вторым и третьим информационными входами управляемой мажоритарного элемента, отличающей с я тем, чго, с целью повышения быстродействия и разрешающей способности системы, дополнительно введены п-1 управляемые мажоритарные элементы, программируемая логическая матрица, дешифратор теста, первый и второй дешифраторы - конфигурации, дешифратор отказа, первый и второй счетчики конфигурации, группу триггеров установки в мажоритар, первую, вторую и третью группу триггеров отказа блоков, триггер отказа, триггер частичного отказа, триггер установки исходного состояния,, формирователь импульса, линию задержки, первый, второй и грегий коммутаторы каналов, первый, второй и третий блоки элементов I/I, первую, вторую и третью группы элементов И, первую - шестую группы элементов ИЛИ, пятый - десятый элементы И. второй -девятый элементы ИЛИ, причем первый выход генератора тактовых импульсов соединен с вторым входом первого элемента И, выход которого соединен с вторым входом четвертого элемента И h входом синхронизации счетчика времени выполнения тест-команды, выход которого соединен с входом управления дешифратора теста, нулевой выход которого соединен с вторым входом третьего элемента И. с первым входом пятого элемента И, с нулевым входом счетчика адреса и первым входом второго элемента ИЛИ, выход третьего элемента И соединен с первым входом третьего элемента ИЛИ, выход которого соединен с единичным входом первого триггера конфигурации, п выходы первого дешифратора конфигураций соединены с перпыки входами п элементов ИЛИ первой и второй групп элементов ИЛИ соответственно, выходы которых соединены соответственно с входами управления п управляемых мажоритарных элементов, прямой выход второго триггера конфигурации соединен с первым входом шестого элемента И, выход которого соединен с входом управления второго дешифратора конфигурации, выход первого элемента ИЛИ соединен с нулевым входом второго триггера конфигурации v, первым входом четвертого элемента ИЛИ, первый - шестой выходы дешифратора теста соединены соответственно с первым - шестым входами пятого элемента ИЛИ, выход которого соединен с единичным входом триггера частич- наго отказа и первым входом шестого элемента ИЛИ, прямой выход триггера частичного отказа является выходом частичного отказа устройства, первый выход снзратора тактовых импульсов соединен с первым входом седьмого элемента И, п выгоды второго дешифратора конфигурации соединены соответственно с первыми входами п элементов ИЛИ третьей группы элементов ИЛИ, выходы которых соединены соответственно с единичными входами п триггеров группы триггеров установки в мажоритар, выходы которых соединены соответственно с вторыми входами п элементов ИЛИ первой и второй групп элементов ИЛИ, а также с п-входами седьмого элемента ИЛИ, выход седьмого элемента ИЛИ соединен с первыми входями восьмого и девятого элементов И, а токже с вторым инверсным эходсм пятого элемента И, выход восьмого элемента И соединан с первым входом первого элемента ИЛИ, выход девятого элечен- та И соединен с нулевым и синхронизирующими входами я триггеров группы триггеров 7стансеки р. мажоритар,

третий выход постоянного запоминающего устройства соединен со вторыми информационными входами первого, второго и третьего коммутаторов каналов, первые информационные входы которых являются сходами резервируемой системы, а выходы соединены с входами первого, второго и третьего блоков первой группы резервируемых блоков соответственно, первый,второй и третий выходы первого управляемого мажоритарного элемента соединены с входами первого, второго и третьего блоков второй группы резервируемых блоков, выходы которых соединены соответственно с первым, вторым и третьим входами второго управляемого мажоритарного элемента, выходы первого, второго и третьего блоков п-й группы резервируемых блоков соединены с первым, вторым и третьим входом п-го управляемого мажоритарного элемента, первый, второй и третий выходы которого соединены с входами первого, второго и третьего блоков элементов И, выходы которых являются выходами резервируемой системы, первый, второй и третий выходы п-го управляемого мажоритарного элемента соединены с вторыми входами первого, второго и третьего блоков свертки по модулю два соответственно, выходы которых соединены соответственно с информационными входами дешифратора теста, седьмой выход дешифратора тестз соединен с вторым входом второго элемента ИЛИ и счетным входом счетчика адреса, выход переполнения счетчика адреса соединен с управляющим входом дешифратора отказа, вторым входом восьмого элемента И, единичным и синхронизирующим входами второго триггера конфигурации, вторыми входами третьего элемента ИЛИ и шестого элемента И, выходы дешифратора отказа соединены соответ- ственно Ј входами п элементов ИЛИ четвертой, пятой и шестой групп элементов ИЛИ, выходы которых соединены соответственно с единичными входами п триггеров первой, второй и третьей групп триггеров отказа блока, выходы которых соединены с первыми входами п элементов И первой, второй и третьей групп элементов И соответственно, выходы которых соединены соответственно с входами восьмого элемента ИЛИ, выход восьмого элемента ИЛИ соединен с третьим входом первого и вторым инверсным входом седьмого элементов И, выход седьмого элемента И соединен с первым входом девятого элемента ИЛИ, выход которого соединен со счетным входом первого счетчика конфигураций, информацион- кые выходы которого соединены с информационными входами дешифратора

отказа и преобразователя номера проверок в код конфигурации, п выходы старших разрядов преобразователя номера проверок в код конфигурации соединены соответственно с третьими входами п элементов ИЛИ первой группы элементов ИЛИ, с вторыми инверсными входами п элементов И первой и второй групп элементов И. с вторыми входами п элементов И третьей группы элемом- тов И, n-выходы младших разрядов преобразователя номера проверок в код конфигурации соединены соответственно с третьими входами п элементов ИЛИ второй группы элементов ИЛИ, с третьими инеярс ными входами п элементов первой и третьей групп элементов И, с третьими входами и элементов И второй группы элементов И. выход переполнения первого счетчика конфигураций соединен со вторым входом шч стого элемента ИЛИ, выход которого соединен с единичным входом триггера ст- каза и вторым входом первого элемента И, выход триггера отказа является выходом отказа системы, вход пуска устройства соединен с входом формирователя импульса, выход которого соединен с входо л линии задержки и первым входом десятого элемента И, выход линии задержки соединен с единичным входом триггера пускз, выход которого соединен с прямыми и инверсными входами первого, второго и третьего коммутаторов канала, с инверсными зходамм управления первого, второго и третьего блоков элементов И, третий выхо гскерагорз тактовых импульсов соединен со вторым входом четвертого элемента ИЛИ, ВУХОД которого соединен с нулевым и синхрокизкру- ющим входом первого триггера конфигураций, выход второго элемента И соединен со счетным входом второго счетчика конфигурации, информгционные выходыкоторогосоединенысинформационными входами первого и второго дешифратора конфигураций, а выход переполнения с третьим входом первого элемента ИЛИ, инверсный выход триггера установки исходного состояния соединен со вторым БХОДОМ десятого элемента И, выход котооого соединен с единичным и синхронизирующим входами триггера установки исходного состояния, з также со вторыми входами п элементов ИЛИ третьей группы элементов ИЛИ, инверсный выход второго триггера конфигураций соединен с третьим входом восьмого элемента И, третьим входом пятого элемнета И и вторым входом девятого элемента И, выход пятого элемента И соединен с вторым входом девятого элемента ИЛИ, нулевой выход дешифратора теста соединен с третьим входом девятого элемента И, выход четвертого элемента И соединен с информационным входом первого, второго и третьего коммутаторов каналов и третьим входом второго элемента

ИЛИ, выход второго элемента ИЛИ соединен с единичным, нулевым и синхронизирующим входами триггера начала теста.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля и управления реконфигурацией | 1984 |

|

SU1213554A1 |

| Устройство для оперативной реконфигурации резервированной системы | 1990 |

|

SU1727125A1 |

| Резервированное устройство | 1982 |

|

SU1102068A1 |

| Устройство для резервирования и восстановления микропроцессорной системы | 1986 |

|

SU1374235A1 |

| Устройство для обмена информацией | 1986 |

|

SU1322299A1 |

| Адаптивное резервированное устройство | 1989 |

|

SU1755281A1 |

| Четырехканальная резервированная система | 1990 |

|

SU1746383A1 |

| Устройство для управления режимамиОбМЕНА РЕзЕРВиРОВАННОй СиСТЕМы | 1979 |

|

SU849216A1 |

| Адаптивное резервированное устройство | 1983 |

|

SU1174929A1 |

| Мажоритарно-резервированный интерфейс памяти | 1990 |

|

SU1751766A1 |

Изобретение относится к вычислительной технике и может быть применено при разработке резервированных систем контроля и управления повышенной надежности, а также адаптивных резервированных систем. Цель изобретения - повышение разрешающей способности и быстродействия достигается введением управляемых мажоритарных элементов, программированной логической матрицы, дешифратора теста, первого и второго дешифратора конфигурации, дешифратора отказа, первого и второго счетчиков конфигурации, группы триггеров, установки в мажоритар п,ервой, второй и третьей групп триггеров отказа Споков, триггера отказа, триггера частичного отказа, триггера установки исходного состояния, формирователя импульса, линии задержки, первого, второго и третьего коммутаторов каналов, первого, второго и третьего блоков элементов И, первой, второй и третьей групп элементов И. первой, второй и третьей, четвертой, пятой и шестой групп элементов ИЛИ, пятого, шестого, седьмого, восьмого, фетьего, четвертого, пятого, шестого, седьмого, восьмого девятого элементов, ИЛИ. Устройство также содержит постоянное запоминающее устройство, генератор тактовых импульсов, управляемый, мажоритарный элемент, первый, второй, третий элементы свертки по модулю два, счетчик адреса, счет1 ни зреме- ни выполнения тест-команды, триггер пуска, первый и второй триггеры конфигурации, триггер начала . еста, первый и второй элементы И, первый элемент ИЛИ. 8 ил. {/) С 2 о о

о о о

СП

о

С Начало j

71

Комму т. 0х. и бых

Фиксация конфигурации

i С Конец 3

/V системы (частичная №)

J

&/. 4

П П П Q Л П V П Л

П П П П П П Q i.- П Jl Л П ПSI -

Л Лfl J1 J1 П Л

ПИП .

ИП П „ П П

Фчь 5

32(33,%)

Фиг. 6

| Устройство для управления реконфигурацией резервированной системы | 1982 |

|

SU1040632A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Авторское свидетельство СССР № 1295989, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-11-15—Публикация

1989-05-24—Подача