7}-t- j J {«

Изобретение относится к радиотехнике и может быть использовано в широкополосных системах синхронизации и синтезаторах частоты, радиоизмерительных устройствах.

Цель изобретения - повышение быстродействия.

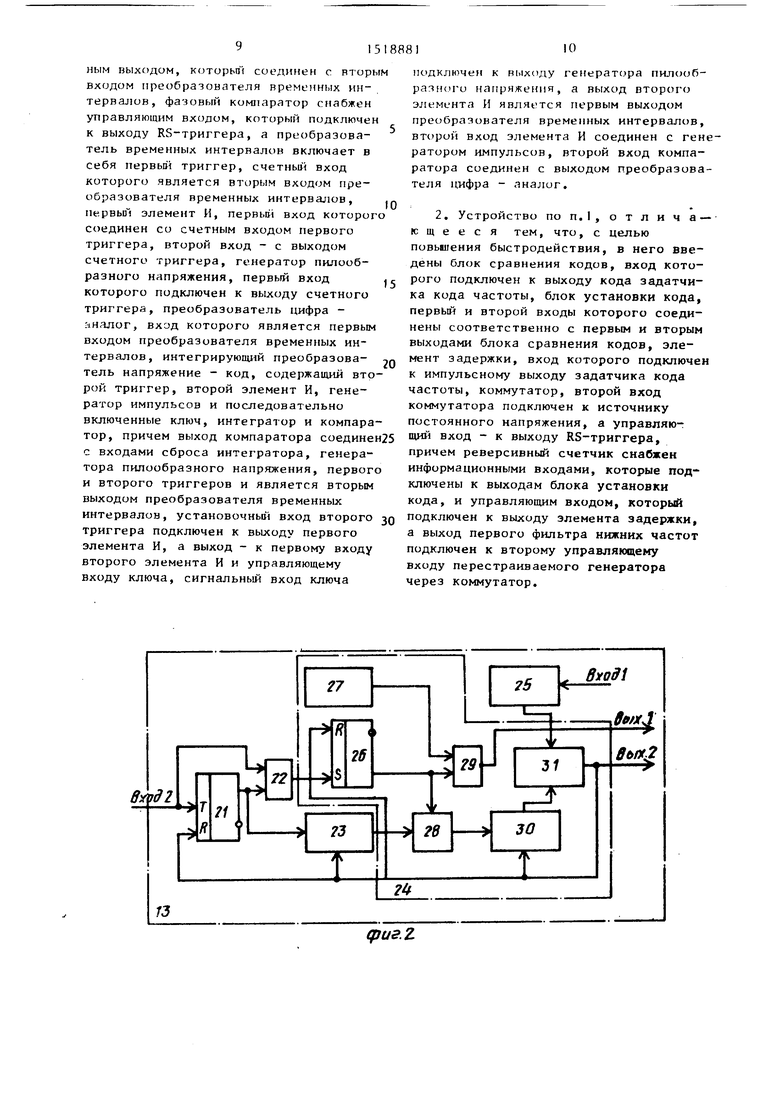

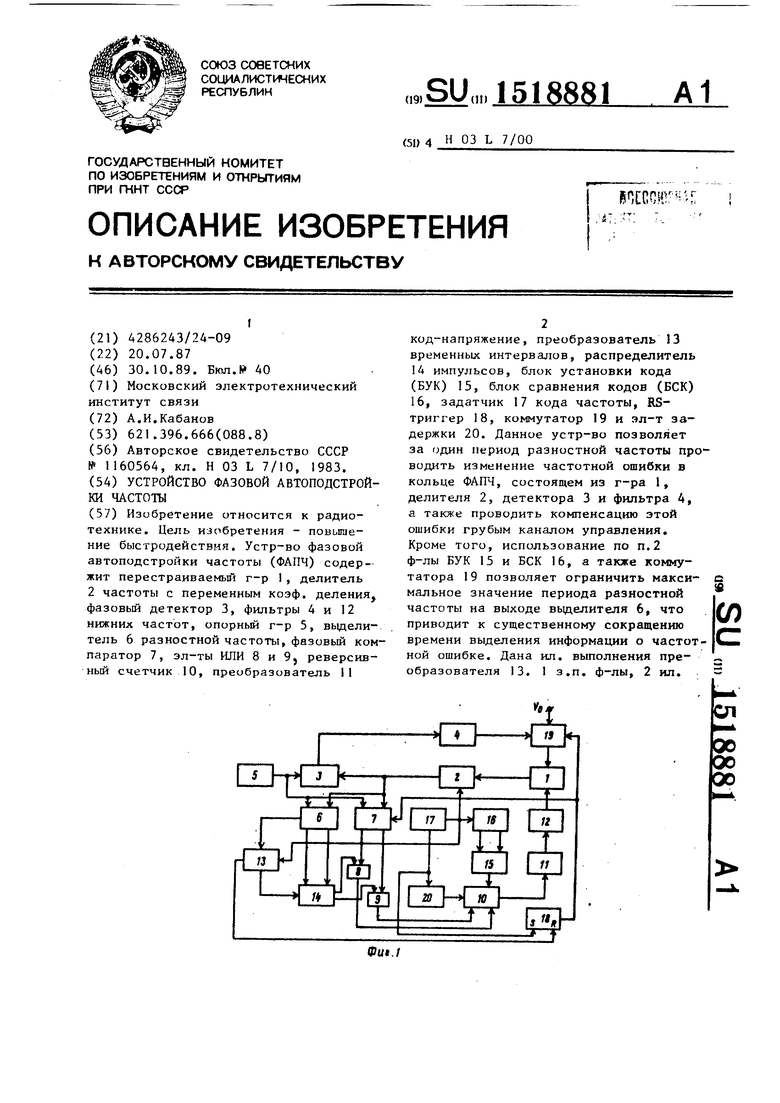

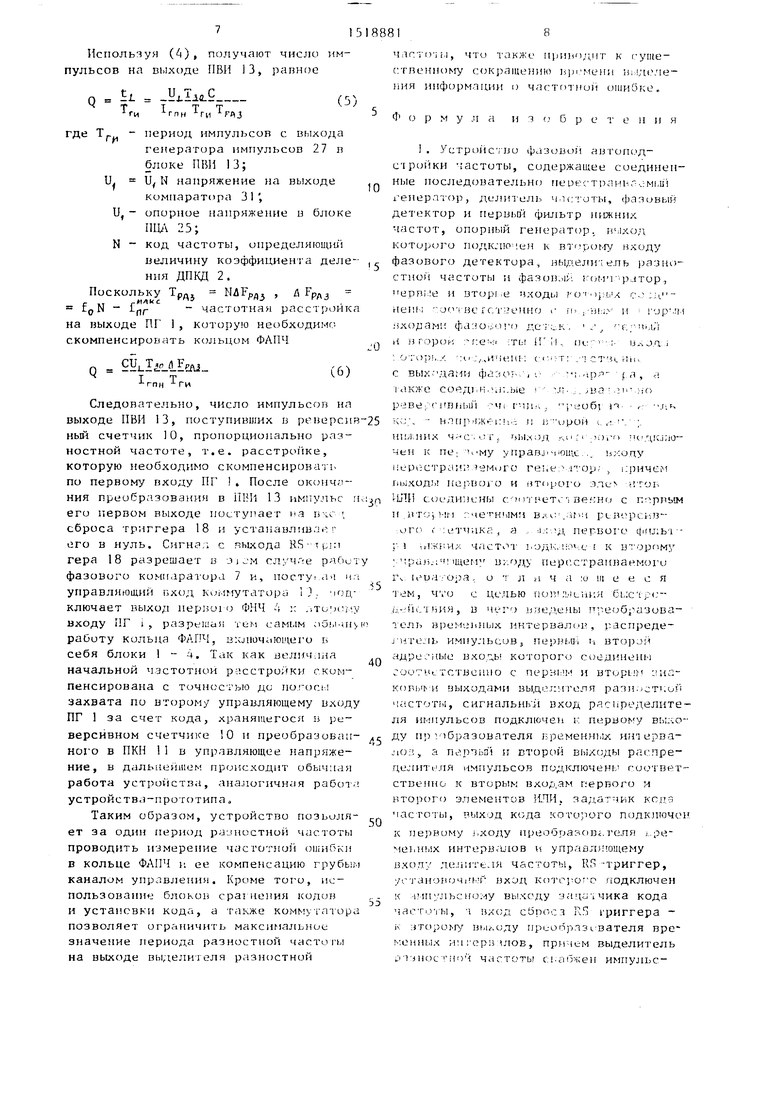

На фиг,1 представлена структурная электрическая схема устройства фазовой автоподстройки частоты (ФАПЧ); на фиг.2 - структурная схема преобразователя временных интервалов устройства ФАПЧ.

Устройство фазовой автоподстройки частоты (фиг.1) содержит перестраиваемый генератор (ПГ) 1, делитель частоты с переменным коэффициентом деления (ДПКД) 2, фазовьп детектор (ФД) 3, первый фильтр нижних частот 4, опорный генератор 5, выделитель разностной частоты (ВРЧ) 6, фазовый компаратор 7, нервьй и второй элементы ИЛИ 8 и 9 соответственно, реверсивный счетчик 10, преобразователь код - напряжение (ПКН) I1, второй ФН 12, преобразователь временных интервлов (ПВИ) 13, распределитель 14 импульсов, блок 15 установки кода, блок 16 сравнения кодов, задатчик 17 кода частоты, RS-триггер 18, комму а тор 19, элемент 20 задержки.

Преобразователь 13 временных интевалов 13 содержит первый триггер 21, первый элемент И 22, генератор пило- образного напряжения (ГПН) 23 со сбросом, интегрирующий преобразователь напряжение - код (ИППК) 24, а также преобразователь цифра-аналог (ПЦА) 25. ИПНК 24 состоит из второго триггера 26, генератора 27 импульсов ключа 28, второго элемента И 29, интегратора 30 со сбросом и компаратора 31 напряжений.

Устройство фазовой автоподстр(

частоты работает следующим образом. (

При изменении рабочей частоты задатчик 17 кода частоты вырабатываг т по импульсному выходу импульс пере- ключения частоты, который поступает на вход RS-триггера 18, устанавливая его в еди1П1чн()е состояние. При э) ом на инверсном выходе RS-триггсра 18 появляется сигнал, соответствующиГ) нулевому потенциалу, который, поступая на управляющий иход фазового компаратора 7, запрещает на время его работу. Зтим же сигналом, поступающим на управляющий вход коммутатор 19, производится отключение выхода ФНЧ 4 от второго управляющего входа ПГ I и подключение к нему источника постоянного напряжения U, который соединен с вторым входом коммутатора 19, Величина Uu выбирается такой, при которой частота ПГ 1 соответствует середине диапазона перестройки по второму входу ПГ 1.

При этом на выходе кода задатчика 17 кода частоты появляется невьсй код частоты, который поступает па управляющий вход ДПКД 2, устанавливая тем самым новый коэффициент деления частоты. Это же значение нового кода частоты поступает в блок 16 сравнения кодов, где производится его сравнение с кодом частоты, хранящимся в запоминающем элементе блока 16 сравнения кодов, и выносится оценка проведенного сравнения. Код, хранящийся в блоке 16 сравнения кодов, соответствует средней частоте диапазона перестройки устройства фазовой автоподстройки частоты. Если код новой частоты меньше или равен коду, хранящемуся в блоке 16 сравнения кодов, то сигнал единичного уровня появляется на перво выходе, если меньше - на втором. Клок 16 сравнения кодов управляет рабтой блока 15 установки кода, на выходах которого, в зависимости от наличия единичного уровня на одном из его входов появляется один из кодов X или Y, храняищхся в запоминающих элементах блока 15 установки кода. При записи кода X в реверсивный счетчик 10 на выходе ПГ 1 устанавливается частота, равная максимальной рабочей частоте устройства фазовой автоподстройки частоты. При записи кода Y устанавливается частота ПГ 1, соответствующая минимальной рабочей частоте устройства.

Пусть для определенности в результате сравнения в блоке сравнения Кодов сигнал единичного уровня появля ется на пертзом входе. Тогда этот сигнал разрешает прохождение кода X н выход блока 15 установки кода и далее на информационные входы реверсивного счетчика 10. Импульс переключения частоты, пройдя через элемент 20 задержки, поступает на управляющий вход реверсивного счетчика 10 и производит запись кода X в ревер сивньо счетчик 10. При этом частота ПГ 1 устанавливается равной максимольной рабочей частоте устройстна. Далее происходит обычная работа Д11КД 2 и ВРЧ 6, в результате которой на импульсном выходе ВРЧ 6 появляются импульсы, период которых соответствует разностной частоте между сигналами, поступаюишми на входы ВРЧ 6.

ВРЧ 6 в процессе работы определя- ет также знак частотного рассогласования, о чем свидетельствует сигнал высокого уровня на одном из знаковых выходов ВРЧ 6. В случае единичный сигнал на первом знаковом выходе БРЧ 6 разрешает прохождение сигнала с выхода ПЕЙ 13 через распределитель 14 импульсов на первый его выход и далее через первый элемент Ш1И 8 на первый счетный вход реверсивного счетчика 10.

При поступлении первого импульса на вход ПВИ 13 с ВРЧ 6 начинает работ блок ПВИ 13. Первьй импульс, поступив Ш1та на вход ПВИ 13, устанавливает на выходе первого триггера 21 единичный уровень сигнала, который разрешает работу ГПН 23. В ГПН 23 происходит преобразование временного интервала, соответствующего разностной частоте, в постоянное напряжение. Поскольку ток через заряжающую емкость С ГПН 23

Т. так зависит от выходного напряжения ГПН 23 - Urnn

т а Т гпн dt ггн

const (1)

и начальное значение вькодного напряжения ГПН 23 при наличии цеПи сброса равно нулю, то получают

Отн 1гпн /С(2)

где Т - длительность импульса на выходе первого триггера 21,

Второй импульс на входе ПВИ 13, соответствующий окончанию периода сигнала с разностной частотой на выходе ВРЧ 6, происходит через первый элемент И 22 на вход установки второго триггера 26, устанавливая его в единицу. Кроме того, он опрокидывает первьй триггер 21 в нуль, останавливая при этом работу ГПН 23, на выходе которого устанавливается напряжение постоянного уровня.

При этом начинает работать ИПНК 24, Ключ 28 замыкается и постоянное напряжение с выхода ГПН 23 поступает на вход интегратора 30, а на выход

5 0

5 0

5

Q

5 0 5

ПВИ 13 начинают поступать импульсы с генератора 27 импульсов через второй элемент И 29. Эти импульсы поступают на счетный вход реверсивного счетчика 10, изменяя его содержимое в сторону уменьшения частотной расстройки между сравниваемыми сигналами в ВРЧ 6,Выходное напряжение интегратора 30 сравнивается по уровню в компараторе 31 напряжений. При равенстве напряжении на его выходе появляется сигнал высокого уровня, который свидетельствует об окончании преобразования в блоке ИПНК 24, На один из входов компаратора 31 поступает напряжение с выхода ПЦА 25, которое, в свою очередь, зависит от кода, поступающего от задатчика 17 кода частоты. При этом необходимо помнить, что в случае использования разных кодов для управления ДПКД 2 и ПВИ 13 необходимо включение специального преобразователя кодов (например преобразователя двоично-десятичного кода в двоичиый) между выходом кода задатчика 17 кода частоты и входом управления ПВИ 13« Сигнал с выхода компаратора 31 устанавливает второй триггер 26 в нуль (при этом ключ 28 размыкается), запрещая прохождение импульсов с генератора 27 импульсов через второй элемент И 29 на выход ПВИ 13; осуществляет сброс в нуль ГПН 23; устанавливает RS- триггер 18 в исходное состояние; осуществляет сброс в нуль интегратора 30, после чего уровень сигнала на выходе компаратора, т.е, на управляющем выходе ПВИ 13, снова становится низким.

Число импульсов на выходе ПВИ 13 за время его работы определяется длительностью импульса на выходе второго триггера 26, которая, в свою очередь, зависит от времени интегрирования в блоке 30, Напряжение на выходе интегратора 30 равно

зо - f и,„ , t, /Т,, , (3)

оп

поскольку при сбросе Uj , гпм const, где Tj, - постоянная времени интегратора 30; t, - время интегрирования. При t t , Uj0 Uy, следовательно, время интегрирования

t . (с учетом 2), (4)

гпн РАЗ

где Трд, - период разностной частоты на выходе ВРЧ 6.

Используя (4), получают число нм- пульсов на выходе ПВИ 13, рапное

Q

де Т

tl .С

Ги

т Т Т

гпн ги FflJ

(5)

- период импульсов с BFlIxoдa генератора импульсов 27 в блоке ПВИ 13; и. и Ы напряжение на выходе

компаратора 3 1 , и, - опорное напряжение в блоке

пи/ 25;

N - код частоты, определяющ1ш целичину коэффициента деления ДПКД 2. Поскольку ЫЛРрд , Д

foN -

пг

- частотная расстройка

на выходе ПГ 1, которую необходимо скомпенсировать кольцом ФАПЧ

Т Т ги

(6)

Следовательно, число импульсов на выходе ПВИ 13, поступивших в реверсив ньй счетчик 10, пропорциопаль}1о разностной частоте, т.е. paccTpoi iKe, которую необходимо скомпенсировать по первому входу ПГ 1 . После ок(Я1ч;.- ния преобразования в П1П1 13 им1;ульс n его первом выходе поступает на вчс -, сброса триггера 18 и устаиавливлг: г его в нуль. Сигна;; с выхода RS-Tpi:i гера 18 разрешает в л i ом случ е рлОот фазового ком1мратора 7 и, посту ..ч на управляющий тзход коммутатора Г}- чгщ- ключает выход nepjioi (j ФНЧ 4 :: .ти п му входу ПГ i, разрешая тем самым обьыи работу кольца ФАП. вхлючаюгцего к

себя блоки 1 - 4. Так как Белмч;1на

начальной частотной расстро;тки скомпенсирована с точностью до ПОГОС:,

захвата по второму управляющему вх(;ду ПГ 1 за счет кода, хранящегося в реверсивном счетчике 0 и преобразовал- ного в ПКН 1 1 в уп15авляющее напряжение, в дальнейшем про1и:ходит обыч:1ая работа ycTpoiicTBa, аналогичная работ/; устройства-прототипа

Таким образом, устройство позволяет за один период разностной частоты проводить измерение частотно (лиибкн в кольце ФЛПЧ ц ее компенсацию грубым каналом управления. Кроме того, использование блоков cpai иония кoд(JB и устансвки кода, а также коммутатора позволяет ограничить максимальное значение периода разностной частогы на выходе выделителя разностно

члгто ;ы, чти также приьодкт к гуще- стленноьгу сокрл|це})ию isin Moin . ie- информации о частотно) ошибке,

Ф о р м у л а и 3 (, б р е т е н н я

1 , Устройстио фаз1,1вой автопс д- c lpoiiKH частоты, содержащее соединенные по следователь НС.) riepKc-Tp;n- iin.,:Mi,ui генератор, делитель мстоты, Ьаяовый детектор и первьо фильтр нижних частот, опорн(1Й генератор., ii )ixo;i которого гкздключен к нтг рсп-г/ входу фазового детектора выде1 И ;ель разно- cTHOi i частоты и фaз(Jв. комт ратор, и BTopi.e входы г О- ор-ь х ,

n

0

г

0

vr

1 i и гормм

. , ( :; п-лЛ 1К:; : и.-, ол J .

;.-1рЯ - (Л, а

} , . jUa . ;iO

ГеОбГ г- .Г;,

ирои 1 ,-v

IГ oor. i n(, j.i,K,i;iO

neiu ofi i BO rcT jeHHo г нходам ; фа:ю(.(1 и н горой :м;е;-. :TL И П, ; 0 ;ч)Т),.х -41 :/. ее с вык. дами фсззс -,-,. также сойд1|И. и;.Ь1е i

p;iBef-(MfBhl Ui . -Ч; I- ili. ,

к;.: нлпрнже ; - ii i;

ini/i-.иих . Ji , Ы1|.

Чей к пе; П му у npaBji-nomc -.. ь;-;оду

11ерг;С 1 ри1ии емого гei,e; i /op; , иричсг

Г1ыход;. Ц1гг. ВО)-о и итпрого зли IJTOI,

1ШИ слн диисны с: 1пт 1етг ве. :но с п трпьЕМ

И,)ГГО-,МП Г:четнММИ Бл1. pLBOpCi- .BОГС1 .- :етчака , а .. : :- Д П(рвого фплы-- г- 1 -.ижи И; -; ьодь:. -о1-:( к иторпму ; ipaji.i : идем в;.одУ Г1ерг.с грацваем(л о г leuaropa. о т л ii чающееся 1 ем, что с целью ( б1,;счр(;-- .ц-ль Угчия, ц Ч , Г ) иледеяы nr.e j6i a3OBa- 1 ель врем;;)1ных интервале, гаспреде- j HTO.ib имнульсоВ; и второй адре: иые входы которого соединены couTiit тствеаио с перны - и вторым : и;:;- кор1) М ыыходани выделителя ра:и.чст1.о li .cTOTni, сигнальнь } вход распределителя импульсов подключен i; первому выходу нр мбразователя 1;ременнь х и/перва- jicjr;, а П1: . и второй выходы распределителя импульсов под слючень сооч вет- cTBeinio к вторым вхор.ам первого и второго элементов ИЛИ. задат жк кпд.а час готы, выход кода которого подключен к первому j.xo;,y преобраг-юв.теля j..pe- -lebHbsx интерв. июв н управляшш,ему вхоау делителя частоты, RS -триггер, yT j aHOBfj4i Mr- вход котсрог-р подключен к -iMiiyjibCHoi -iy Bbixcviy зацоччика кода jacTorhi, -1 нкод сброса КЯ 1 риггера - i ;ггором вы.оду приопрлзивателя вре Г - енных им repii (ЛОВ, причем выделитель

р г нос- . ноч частоты с.абч;ен импульс

ным выходом, которьо( coeflHFieH с вторы входом преобразонсэтеля временных интервалов, фазовый компаратор снабжен управляющим входом, который подключен к выходу RS-триггера, а преобразователь временных интервалов включает в себя первьй триггер, счетньй вход которого является вторым входом преобразователя временных интервалов, первьи элемент И, первьй вход которог соединен со счетным входом первого триггера, второй вход - с выходом счетного триггера, генератор пилообразного напряжения, первый вход которого подключен к выходу счетного триггера, преобразователь цифра - аналог, вход которого является первым входом преобразователя временных интервалов, интегрируюпи1й преобразователь напряжение - код, содержащий второй триггер, второй элемент И, генератор импульсов и последовательно включенные ключ, интегратор и компаратор, причем выход компаратора соединен с входами сброса интегратора, генератора пилообразного напряжения, первого и второго триггеров и является вторым выходом преобразователя временных интервалов, установочньо вход второго триггера подключен к выходу первого элемента И, а выход - к первому входу второго элемента И и управляющему входу ключа, сигнальный вход ключа

0

5

5

0

подключен к выходу генератора пилообразного напряжения, а выход второго элемента И является первым выходом преобразователя временных интервалов, второй вход элемента И соединен с генератором импульсов, второй вход компаратора соединен с выходом преобразователя цифра - аналог.

2. Устройство поп.1,отлича- 1C щ е е с я тем, что, с целью повышения быстродействия, в него введены блок сравнения кодов, вход которого подключен к выходу кода задатчи- ка кода частоты, блок установки кода, первьй и второй входы которого соединены соответственно с первым и вторым выходами блока сравнения кодов, элемент задержки, вход которого подключен к импульсному выходу задатчика кода частоты, коммутатор, второй вход коммутатора подключен к источнику постоянного напряжения, а управляющий вход - к выходу RS-триггера, причем реверсивный счетчик снабжен информационными входами, которые подключены к выходам блока установки кода, и управляющим входом, который подключен к выходу элемента задержки, а выход первого фильтра нижних частот подключен к второму управляющему входу перестраиваемого генератора через коммутатор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1338071A1 |

| Устройство автоматической подстройки частоты | 1989 |

|

SU1698987A1 |

| Устройство фазовой автоподстройки частоты | 1983 |

|

SU1160564A2 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| Устройство для приема частотно-манипулированных сигналов | 1978 |

|

SU768000A1 |

| ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА ВАЛА В НАПРЯЖЕНИЕ | 1987 |

|

RU2056700C1 |

| Устройство фазовой автоподстройки частоты | 1981 |

|

SU1012444A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 2002 |

|

RU2241246C2 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия. Устройство фазовой автоподстройки частоты (ФАПЧ) содержит перестраиваемый генератор 1, делитель 2 частоты с переменным коэф. деления, фазовый детектор 3, фильтры 4 и 12 нижних частот, опорный генератор 5, выделитель 6 разностной частоты, фазовый компаратор 7, элементы ИЛИ 8 и 9, реверсивный счетчик 10, преобразователь 11 код-напряжение, преобразователь 13 временных интервалов, распределитель 14 импульсов, блок установки кода (БУК) 15, блок сравнения кодов (БСК) 16, задатчик 17 кода частоты, RS-триггер 18, коммутатор 19 и элемент задержки 20. Данное устройство позволяет за один период разностной частоты проводить измерение частотной ошибки в кольце ФАПЧ, состоящем из генератора 1, делителя 2, детектора 3 и фильтра 4, а также проводить компенсацию этой ошибки грубым каналом управления. Кроме того, использование по п.2 ф-лы БУК 15 и БСК 16, а также коммутатора 19 позволяет ограничить максимальное значение периода разностной частоты на выходе выделителя 6, что приводит к существенному сокращению времени выделения информации о частотной ошибке. Дана ил. выполнения преобразователя 13. 1 з.п. ф-лы, 2 ил.

(риг.г

| Устройство фазовой автоподстройки частоты | 1983 |

|

SU1160564A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-10-30—Публикация

1987-07-20—Подача