&

Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1985 |

|

SU1336231A1 |

| Синтезатор частот | 1986 |

|

SU1478328A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1984 |

|

SU1252909A1 |

| Устройство фазовой автоподстройки частоты | 1987 |

|

SU1518881A1 |

| Цифровой синтезатор частот с частотной модуляцией | 1987 |

|

SU1515363A2 |

| Цифровой синтезатор частот с частотной модуляцией | 1990 |

|

SU1774465A2 |

| Цифровой синтезатор частот с частотной модуляцией | 1985 |

|

SU1293840A1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение быстродействия синтезатора и стабильности частоты выходных сигналов. Цифровой синтезатор частоты с частотной модуляцией содержит источник 1 модулирующего сигнала, коммутатор 2, первый управляемый аттенюатор 3, блок напряжения смещения 4, интегратор 5, фазовый модулятор (ФМ) 6, фазовый детектор (ФД) 7, первый ключ 8, первый интегрирующий фильтр 9, фильтр нижних частот

VI

V4

О ON 00

(ФНЧ) 10, перестраиваемый генератор 11, делитель частоты с переменным коэффициентом деления (ДПКД) 12, формирователь управляющих сигналов (ФУС) 13, блок установки частоты (БУЧ) 14, второй ключ 15, второй интегрирующий фильтр 16, второй управляемый аттенюатор 17, первый компаратор 18, второй компаратор 19, элемент ИЛИ 20, импульсный дифференциатор (ИД) 21, первый реверсивный счетчик 22, первый

Изобретение относится к радиотехнике и может быть использовано в качестве возбудителя передатчика с широкополосной частотной модуляцией.

Целью изобретения является повышение быстродействия синтезатора и стабильности частоты выходных сигналов.

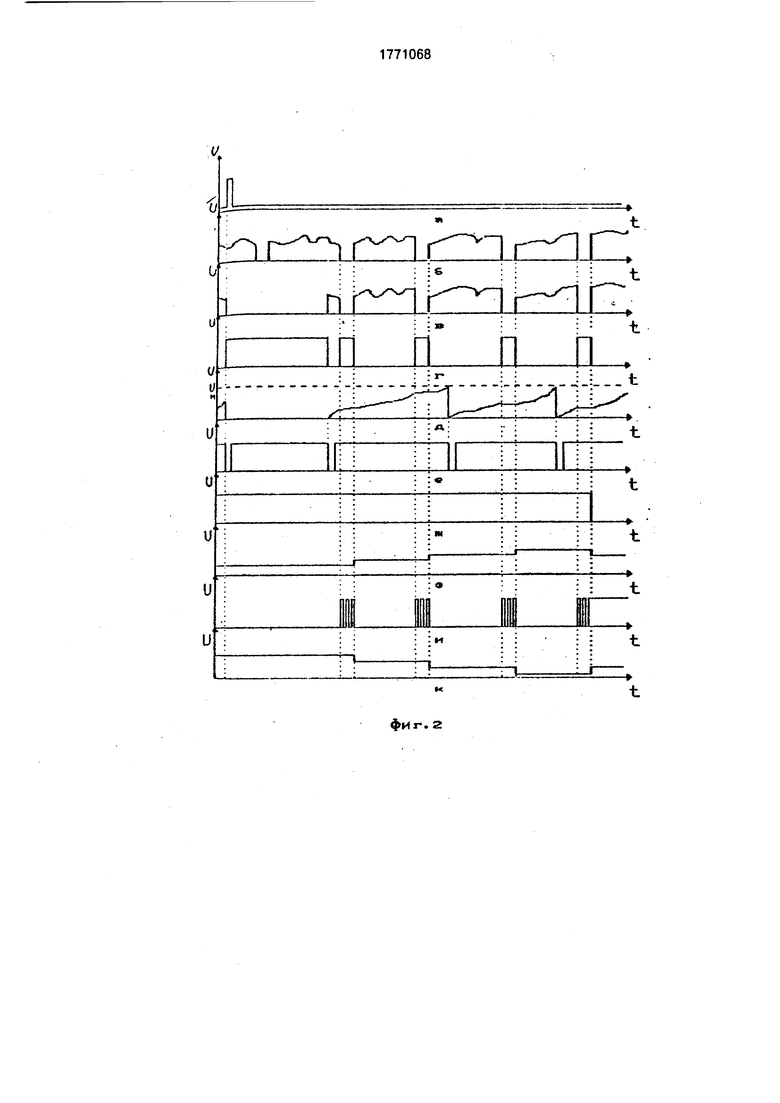

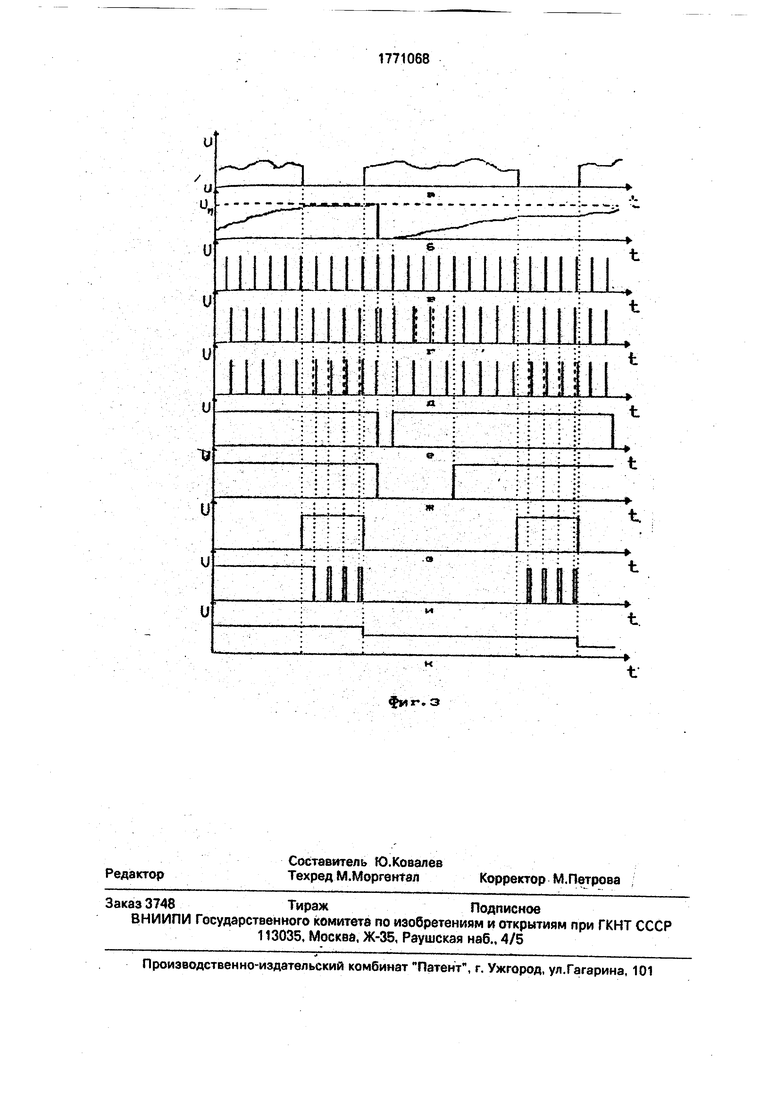

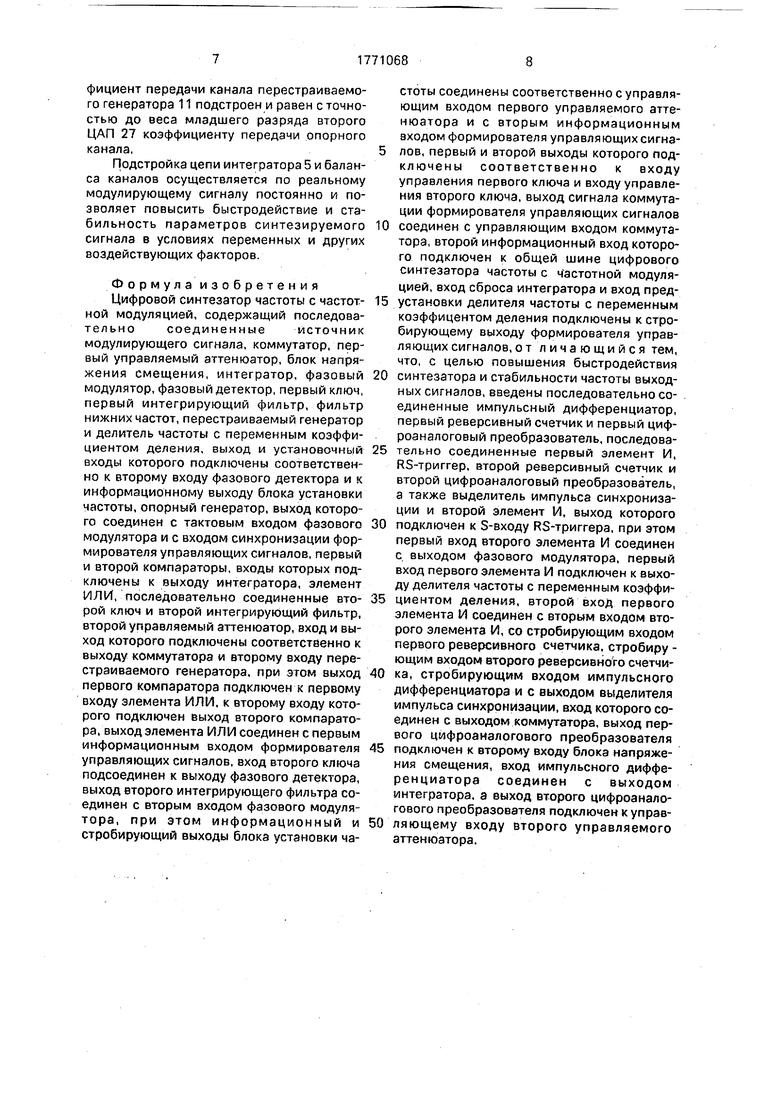

На фиг.1 представлена электрическая структурная схема цифрового синтезатора частоты с частотной модуляцией; на фиг.2 - временные диаграммы работы синтезатора в режиме перехода на новую частоту; на фиг.З - временные диаграммы процесса баланса каналов.

Цифровой синтезатор частоты с частотной модуляцией содержит источник 1 модулирующего сигнала, коммутатор 2, первый управляемый аттенюатор 3, блок напряжения смещения 4, интегратор 5, фазовый модулятор (ФМ) 6, фазовый детектор (ФД) 7, первый ключ 8, первый интегрирующий фильтр 9, фильтр нижних частот (ФНЧ) 10, перестраиваемый генератор 11, делитель частоты с переменным коэффициентом деления (ДПКД) 12, формирователь управляющих сигналов (ФУС) 13, блок установки частоты (БУЧ) 14, второй ключ 15, второй интегрирующий фильтр 16, второй управляемый аттенюатор 17, первый компаратор 18, второй компаратор 19, элемент ИЛИ 20, импульсный дифференциатор (ИД) 21, первый реверсивный счетчик 22, первый цифроаналоговый преобразователь (ЦАП) 23, первый элемент И 24, RS-триггер 25, второй реверсивный счетчик 26, второй ЦАП 27, второй элемент И 28, выделитель импульса синхронизации (ВИС) 29, опорный генератор 30.

Цифровой синтезатор частоты с частотной модуляцией работает следующим образом.

Общий принцип работы при модуляции его выходной частоты состоит в осуществлецифроаналоговый преобразователь (ЦАП) 23, первый элемент И 24, RS-триггер 25, второй реверсивный счетчик 26. второй ЦАП 27, второй элемент И 28, выделитель импульса синхронизации (ВИС) 29, опорный генератор 30. Поставленная цель достигается тем, что подстройка цепи интегратора 5 и баланс каналов подстройки осуществляется постоянно по реальному модулирующему сигналу. 3 ил.

нии режима двухточечной модуляции в кольце фазовой автоподстройки частоты перестраиваемого генератора 11. При этом кольцо автоподстройки периодически размыкается для сброса интегратора, после чего осуществляется привязка разности фаз импульсов на выходе ФД 7 за счет дополнительного кольца фазовой автоподстройки. Одновременно с режимом двухточечной модуляции производится выравнивание коэффициентов передачи опорного канала модуляции и канала подстраиваемого генератора 11 (баланс каналов).

При переходе на новую частоту по стробирующему импульсу с БУЧ 14 (фиг.2а) код новой частоты подается на информационный вход ДПКД 12 и первого управляемого аттенюатора 3. По сигналу с ФУС 13 на выходе коммутатора 2 устанавливается нулевой уровень сигнала (фиг.2в), сбрасывается интегратор 5 и предустанавливается ДПКД 12. После чего начинает работать кольцо привязки разности фаз импульсов на входах ФД 7. Через первый ключ 8 замыкается кольцо фазовой автоподстройки (фиг.2е) и сигнал подстройки через первый ключ 8 и первый интегрирующий фильтр 9 и ФНЧ 10 поступет на вход подстраиваемого генератора 11. Происходит перестройка

синтезатора на новую частоту. Время перехода выбирается из условия максимальной продолжительности переходного процесса в этом кольце автоподстройки и определяется длительностью выходного импульса

ФУС 13. По окончании перехода на новую частоту вновь сбрасывается интегратор 5, предустанавливается ДПКД 12, работает кольцо привязки фаз и синтезатор переходит в режим двухточечной модуляции,одновременно с которым осуществляется подстройка цепи интегратора 5 и баланса каналов. На выход коммутатора 2 поступает

модулирующий сигнал и через первый управляемый аттенюатор 3 и второй управляемый аттенюатор 17 подается в опорный канал и на перестраиваемый генератор 11. Стационарное значение разности фаз им- пульсов на входах ФД 7 равно нулю, так как кольцо фазовой автоподстройки астатическое, При достижении выходным напряжением интегратора 5 порога первого компаратора 18 или второго компаратора 19 (фиг.2 д и 3 б) сигнал об этом че0ез элемент ИЛИ 20 поступает на первый информационный вход ФУС 13, в котором к последующему импульсу опорной частоты формируется сигнал сброса интегратора 5 и предустанов- ки ДПКД 12 (фиг.З е). Одновременно размыкается первый ключ 8 (фиг. 3 ж). По следующему импульсу опорной частоты управляющий сигнал проходит на второй выход управления ФУС 13 и открывается второй ключ 15. Четыре периода опорной частоты работает кольцо привязки, а модуляция вводится в одну точку кольца фазовой автоподстройки - на вход подстраиваемого генератора 11. Напряже- ние в выходе второго интегрирующего фильтра 16 управляет разностью импульсов на выходе и входе ФМ6. Это дополнительное кольцо подстройки фазы является астатическим кольцом первого порядка и за четыре импульса подстройки оно сводит разность фаз импульсов на входах ФД 7 к нулю. После этого второй ключ 15 размыкается и потенциал управления ФМ 6 запоминается во втором интегрирующем фильтре 16, а первый ключ 8 замыкается (фиг.Зж), сигнал с выхода ФД 7 через первый интегрирующий фильтр 9 и ФНЧ 10 поступает на перестраиваемый генератор 11. Таким образом, без паразитных фазовых расстроек замыкается кольцо фазовой автоподстройки и устраняется паразитный переходный процесс, вызванный ненулевой разностью фаз импульсов на входах Ф Д 7 после сброса интегратора 5,

Подстройка интегратора 5 осуществляется тогда, когда выходное напряжение источника 1 равно нулю (фиг.26, 3 а). ВИС 29 вырабатывает управляющий сигнал для этого кольца (фиг.2 г, 3 в). Сигналом с выхода БИС 29 стробируется ИД 21, в первом элементе выборка - хранение которого (на фиг.1 не показан) запоминается значение выходного напряжения интегратора 5. По окончании импульса синхронизации стро- бируется второй элемент выборки - хранения ИД 21 (на фиг.1 не показан), в котором запоминается разность значений напряжений синтегратора в начале и конце синхроимпульса. Знак разности этих напряжений выделяется в ИД 21, выход которого управляет направлением счета реверсивного счетчика 22 (фиг.2 ж). Выходной код реверсивного счетчика 22 преобразуется в аналоговое напряжение в первом ЦАП 23 и суммируется в блоке напряжения смещения 4 с входным сигналом. Подстройка проходит до тех пор, пока напряжение на выходе интегратора 5 будет постоянным во время синхроимпульса. В этом случае частота перестраиваемого генератора 11 будет равна частоте опорного генератора 3CLумноженной на коэффициент деления ДГЖД 12, т.е. достигается высокая долговременная стабильность несущей частоты цифрового синтезатора частоты с частотной модуляцией....

Подстройка баланса каналов также осуществляется во время синхроимпульсов. Сигналы со входов ФД7 (фиг.З г, 3 д) через первый и второй элементы И 24, 28 подаются на R- и S-входы RS-триггера 25, сигнал с выхода которого управляет направлением счета второго реверсивного счетчика 26, выходной код которого преобразуется вторым ЦАП 27 в напряжение (фиг.2 к, 3 к), которое управляет коэффициентом передачи второго управляемого аттенюатора 17. При появлении в модулирующем сигнале синхроимпульса резко меняется напряжение на выходе источника 1. Если нарушен баланс модуляции, то изменение напряжения приведет к отклонению разности фаз от стационарной на входах ФД 7 (фиг.Зг, Зд). Если длительность синхроимпульса менее постоянной времени кольца фазовой автоподстройки, то к концу синхроимпульса кольцо автоподстройки не успевает отработать это отклонение. Первый и второй элементы И 24,28 отключаются сигналом с ВИС 29 по концу синхроимпульса, таким образом RS-триггер 25 остается в таком состоянии (Лог. О и лог.1), какой из импульсов (с первого элемента И 24 или второго элемента И 28) пришел на соответствующие входы RS-триггера 25 последним (фиг.2 н, 3 н). Выходной сигнал RS-триггера 25 определяет знак отклонения разности фаз от стационарной, равной нулю. Второй реверсивный счетчик 26 стробируется задним фронтом сигнала с выхода ВИС 29 и выходной код его изменя- ,ется в зависимости от состояния RS-триггера 25. За каждый синхроимпульс код второго реверсивного счетчика 26 изменяется на единицу, и подстройка осуществляется до тех пор, пока отклонение разности фаз импульсов на входах ФД 7 не будет минимальным.

Таким образом, когда переходный процесс в кольце подстройки баланса каналов закончен, отклонение разности фаз в моменты резких скачков не происходит и коэффициент передачи канала перестраиваемого генератора 11 подстроен и равен с точностью до веса младшего разряда второго ЦАП 27 коэффициенту передачи опорного канала,

Подстройка цепи интегратора 5 и баланса каналов осуществляется по реальному модулирующему сигналу постоянно и позволяет повысить быстродействие и стабильность параметров синтезируемого сигнала в условиях переменных и других воздействующих факторов.

Формула изобретения Цифровой синтезатор частоты с частотной модуляцией, содержащий последовательно соединенные источник модулирующего сигнала, коммутатор, первый управляемый аттенюатор, блок напряжения смещения, интегратор, фазовый модулятор, фазовый детектор, первый ключ, первый интегрирующий фильтр, фильтр нижних частот, перестраиваемый генератор и делитель частоты с переменным коэффициентом деления, выход и установочный входы которого подключены соответственно к второму входу фазового детектора и к информационному выходу блока установки частоты, опорный генератор, выход которого соединен с тактовым входом фазового модулятора и с входом синхронизации формирователя управляющих сигналов, первый и второй компараторы, входы которых подключены к выходу интегратора, элемент ИЛИ, последовательно соединенные второй ключ и второй интегрирующий фильтр, второй управляемый аттенюатор, вход и выход которого подключены соответственно к выходу коммутатора и второму входу перестраиваемого генератора, при этом выход первого компаратора подключен к первому входу элемента ИЛИ, к второму входу которого подключен выход второго компаратора, выход элемента ИЛИ соединен с первым информационным входом формирователя управляющих сигналов, вход второго ключа подсоединен к выходу фазового детектора, выход второго интегрирующего фильтра соединен с вторым входом фазового модулятора, при этом информационный и стробирующий выходы блока установки частоты соединены соответственно с управляющим входом первого управляемого аттенюатора и с вторым информационным входом формирователя управляющих сигналов, первый и второй выходы которого под- ключены соответственно к входу управления первого ключа и входу управления второго ключа, выход сигнала коммутации формирователя управляющих сигналов

соединен с управляющим входом коммутатора, второй информационный вход которого подключен к общей шине цифрового синтезатора частоты с частотной модуляцией, вход сброса интегратора и вход предустановки делителя частоты с переменным коэффицентом деления подключены к стро- бирующему выходу формирователя управляющих сигналов,от личающийся тем, что, с целью повышения быстродействия

синтезатора и стабильности частоты выходных сигналов, введены последовательно соединенные импульсный дифференциатор, первый реверсивный счетчик и первый циф- роаналоговый преобразователь, последовательно соединенные первый элемент И, RS-триггер, второй реверсивный счетчик и второй цифроаналоговый преобразователь, а также выделитель импульса синхронизации и второй элемент И, выход которого

подключен к S-входу RS-триггера, при этом первый вход второго элемента И соединен с выходом фазового модулятора, первый вход первого элемента И подключен к выходу делителя частоты с переменным коэффициентом деления, второй вход первого элемента И соединен с вторым входом второго элемента И, со стробирующим входом первого реверсивного счетчика, стробиру - ющим входом второго реверсивного счетчика, стробирующим входом импульсного дифференциатора и с выходом выделителя импульса синхронизации, вход которого соединен с выходом коммутатора, выход первого цифроаналогового преобразователя

подключен к второму входу блока напряжения смещения, вход импульсного дифференциатора соединен с выходом интегратора, а выход второго цифроаналогового преобразователя подключен к управляющему входу второго управляемого аттенюатора.

фиг. 2

U U.

ш

ч ч а Ч 1 ч з ч 1 ч з з

JLLL1

и

и

.«.

д

ли

I t ifI

а

ч лI

I. i.iI

ж

И

$ИГ.3

| Цифровой синтезатор частоты с частотной модуляцией | 1982 |

|

SU1035776A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1987 |

|

SU1543544A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-10-23—Публикация

1989-12-22—Подача