Изобретение относится к вычислительной технике и ггикроэлектронике и предназначено для построения контролепригодных устройств цифровой обработки информации.

Цель изобретения - упрощение конструкции универсального логического модуля.

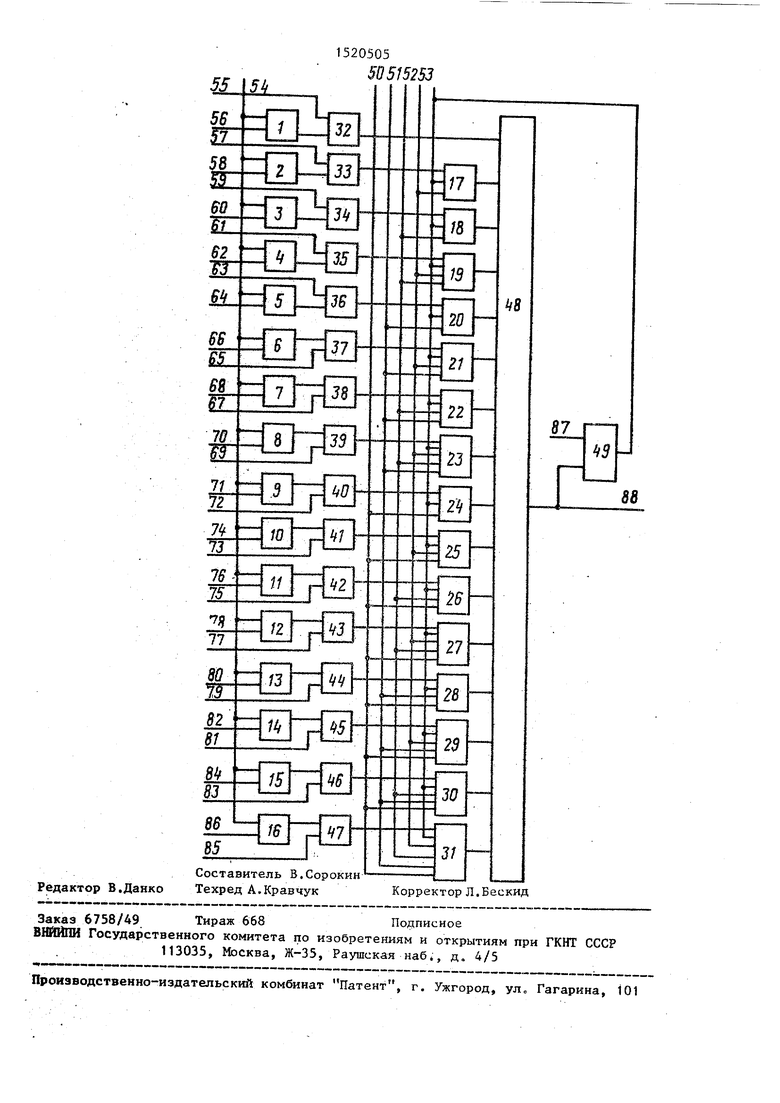

На чертеже представлена схема модуля при .

Модуль содержит 2 16 элементов ИЛИ 1-16, 15 элементов 17- 31 равнозначности, 16 элементов

32 - 47 сложения по модулю два группы, элемент 48 сложения по модулю два, элемент И 49, п « 5 информационных

входов 50-54, 2 32 настроечных . входа 55 - 86, вход 87 задания режима, выход 88.

Модуль работает в двух режимах - рабочем и контроля.

Рабочий режим.

В рабочем режиме на вход 87 задания режим а модуля подается сигнал .Z О, на информационные входы 50 - 54 - двоичные переменные Х,-Х соотсд to

о ел

о

СП

ветственно, на настроечные входы 55 - 86 - компоненты вектора настройки соответственно, значения которых принадлежат множеству {0,1}- На выходе 88 модуля реализуется логическая функция пяти переменных f (Х, X 2, Х}, X4J Ху), определяемая вектором настройки

и (и,, 1, .... из.).

Рассмотрим алгоритм настройки мо дуля для произвольного числа п переменных. Обозначим через Y, значение реализуемой модулем логической функ- ции п переменных f (X,, Xi, ..., Х) на (i-l)-M наборе, i t, 2.

Тогда исходным для нахождения вектора настройки U(U,Ui ,..., Ujn) бу- дет вектор W,, (., 9 Y)

(Z i

1,.

Z°n) где Z Y

17 I , i .

Далее формируется последовательность векторов W, К,..., Wp, компоненты которых вычисляются согласно следуюЕщм рекуррентным соотношениям

Z - Z

7iir, 2imH

® (2iM),+t

где i О, t 1, m; j 1, n.

Вектор настройки составляется из компонент вектора W следующим обра- зом: Ui Z, i 2J-1, j 1, , U; 2;, i 2j, j 1, .

11 p и M 8 p, Найдем вектор настройки U модуля для логической функции f (X,, Хг,Хз, Х4, Х) () (XjV X,v XJ,

Очевидно, что

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1985 |

|

SU1312561A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1520504A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1644125A1 |

| Универсальный логический модуль | 1985 |

|

SU1269121A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1765821A1 |

| Универсальный логический модуль | 1987 |

|

SU1476457A1 |

| Многофункциональный логический модуль двух переменных с самоконтролем | 1984 |

|

SU1275444A1 |

| Дешифратор с самоконтролем | 1988 |

|

SU1614019A1 |

| Универсальный логический модуль | 1984 |

|

SU1218375A1 |

| Универсальный логический модуль | 1984 |

|

SU1216778A1 |

Изобретение относится к области вычислительной техники и микроэлектроники и предназначено для построения контролепригодных устройств цифровой обработки информации. Цель изобретения - упрощение конструкции универсального логического модуля. Цель достигается тем, что универсальный логический модуль, реализующий все логические функции переменных, содержит 2N-1 элементов ИЛИ, элемент сложения по модулю два первой группы, 2N-1 элементов сложения по модулю два второй группы, 2N-1-1 элементов равнозначности и элемент И. Модуль работает в двух режимах - рабочем и контроля. В рабочем режиме на информационные входы модуля подаются двоичные переменные X1X2,...,XN, на настроечные входы - компоненты вектора настройки U = (U1,U2,...,U2N), на выходе модуля реализуется логическая функция F (X1, X2,...,XN), определяемая вектором настройки U. В режиме контроля при отсутствии неисправности на выходе модуля возникает генерация непрерывной последовательности импульсов типа меандр. Появление любой константной неисправности произвольной кратности ведет к срыву генерации. Описывается алгоритм нахождения вектора настройки модуля на произвольную логическую функцию N переменных. 1 ил., 1 табл.

Таким oepasoMf имеем U, О при ie 1,4,5,8,9,11 13,15,20,21,24,28, и и,- t при i е|2,3,6,7,Ю, 12,14,16,17,t8,19,22,23,25,26,27, 30,311.

Режим контроля.

В этом режиме модуль становится самопроверяемым и переводится в этот режим подачей на вход 87 задания режима сигнала /i 1,

Б первом подрежиме контроля на информационные входы 50 - 54 подается сигнал логической единицы, на настроечные входы 55- 86 - сигнал логического нуля. При отсутствии неисправностей на выходе 88 модуля появляется непрерывная последовательность импульсов типа меандр с периодом 41} , где С- задержка на вентиль.

Во втором подрежиме контроля на информа1Ц1ОЯные входы 50 - 54 подается сигнал логического нуля, на настроечные входы 55 - 86 - сигнал логической единицы. При отсутствии неисправностей на его выходе 88 также появляется непрерывная последовательность импульсов с периодом 4 t .

i Появление любой константной неисправности произвольной кратности (за

исключением попарно тождественных константных неисправностей на входах элемента 48 сложения по модулю два, т.е. неисправности типа константа константа О) приводит к срьшу генерации импульсов либо в двух подрежимах контроля, либо в одном из них,

В режиме контроля не проверяется только одна константная неисправность йа входе 87 задания режима (константа о) Поскольку этот вход доступен, то обнаружение ее не вызывает трудностей.

Значения входных си налов модуля приведены в таблице значений входных сигналов модуля для рабочего режима и режима контроля.

Таким образом, модуль, независимо от числа переменных, проверяется все го лишь двумя заранее известнь1ми наборами сигналов на его входах, которые переводят его в режим самоконтроля ,

Формула изобретения

Универсальный логический модуль, содержащий элемент сложения по модулю с два и -1 элементов равнозначное- , ти (п-количество переменных реализуемых логических функций), выход i-ro из которых (i 1,2 -1) соединен с i-M входом элемента сложения по мо- 10 дулю два, выход которого соединен с выходом модуля, п-1 информационных входов которого, взятых в различных сочетаниях С,- (j 1, ,jj,

нозначности, первый вход элемента И соединен с выходом элемента сложения по модулю два, второй вход элемента И соединен с входом задания режима модуля, п-й информационный вход которого соединен с первым входом s-ro элемента ИЛИ (s t, ), второй вход которого соединен с S-M настроечным входом модуля, выход s-ro элемента ИЛИ соединен с первым входом 8-го элемента сложения по модулю два группы, второй вх од которого соединен с ( + s)-M настроечным входом модуля,

соединены с первым входом j-ro элемен 15 выход i-ro элемента сложения по модулю два группы соединен с третьим входом i-ro элемента равнозначности, выход 2 -го элемента сложения по модулю два группы соединен с 2 -м

та равнозначности, отличающийся тем,что, с целью упрощения, он содержит элементов ШШ, элементов сложения по модулю два группы и элемент И, выход которого соеди-20 входом элемента сложения по нен с вторым входом i-ro элемента рав- два.

модулю

Х, ..., Х„ 1 ... 1

О

О

нозначности, первый вход элемента И соединен с выходом элемента сложения по модулю два, второй вход элемента И соединен с входом задания режима модуля, п-й информационный вход которого соединен с первым входом s-ro элемента ИЛИ (s t, ), второй вход которого соединен с S-M настроечным входом модуля, выход s-ro элемента ИЛИ соединен с первым входом 8-го элемента сложения по модулю два группы, второй вх од которого соединен с ( + s)-M настроечным входом модуля,

модулю

Ujh

... О

... 1

f(x,,x

Генерация непрерывной последовательности импульсов

1520505

50515253

Редактор В.Данко

Заказ 6758/49 Тираж 668Подписное

ВНЙЙПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР .113035, Москва, Ж-35, Раушская наб, д, 4/5

| Универсальный логический модуль | 1984 |

|

SU1234825A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Универсальный логический модуль | 1985 |

|

SU1312561A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1988-02-29—Подача