ю

О)

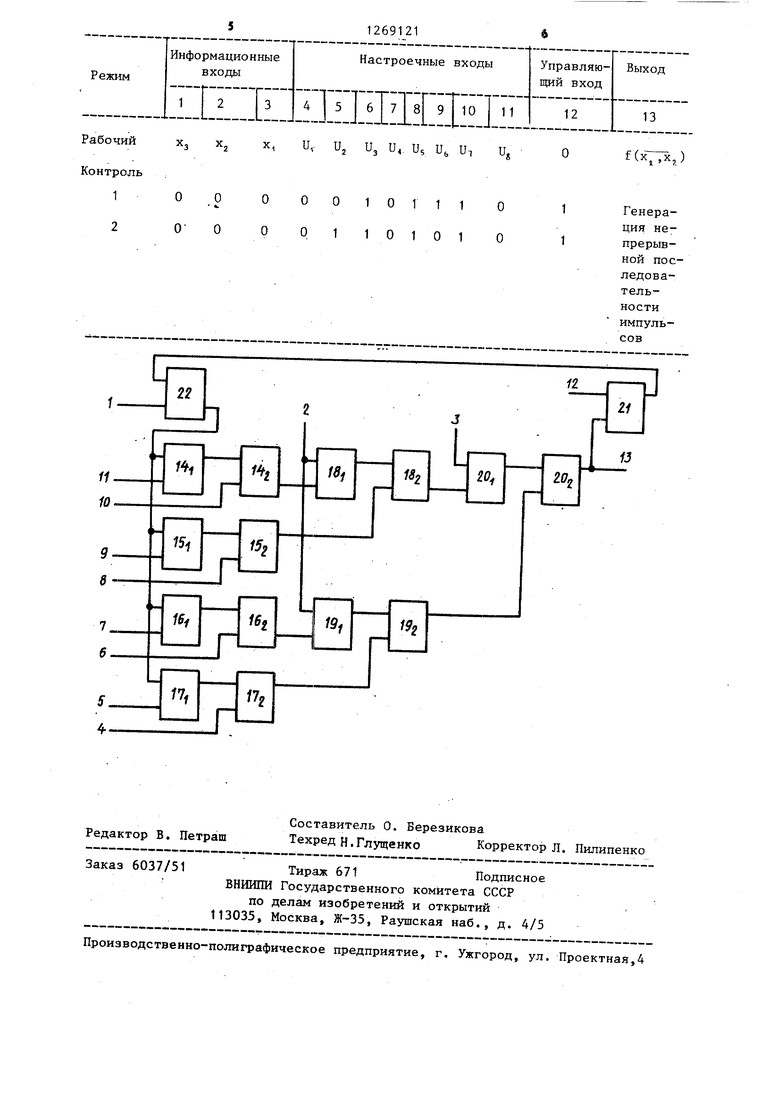

;о 1 Изобретение относится к вычислительной технике и предназначено для реализации всех логических функций п переменных. Цель изобретения - повышение контролепригодности модуля. Модуль строится на основе разложения произвольной логической функции п переменных f (х, ,х,) вида f(x, ,Х) Ч:,(,Х„)ФХ,У ,Х) где () i некоторые логические функции (п-1)-й переменной. Первообразная модуля цояучается путем последовательного п-кратного разложения f(х, ,Хц) согласно (1) по переменным х,. Например, при п 3 первообразная имеет вид f (х, , х, и) Ц Ф UjV хр) XjV (и © х )Ф ©.qv ( Xj@ (U-jSUgVXj ) )(2 где и (U , и„ ,. . . ,U ) -вектор настройки, ,, i 1,8. Универсальный логический модуль с самоконтролем содержит п линеек, каждая i-я (, п) из которых содержит 2 логических ячеек, описы ваемых выражением у t, ©tjVS где .t2 - сигналы на управляющих входах ячейки, S - сигнал на информационно входе ячейки. Структурно логическая ячейка содержит элементы ИЛИ-НЕ и НЕРАВНОЗНА НОСТЬ, соединенные между собой в со ответствии с (3). Информационный вход каждой логической ячейки j-й линейки (j 2, п соединен с j-м информационным входо модуля, на который подается перемен Управляющие входы ячеек первой линейки соединены с настроеч ными входами модуля, на которые под ются сигналы настройки U, Выходы всех ячеек 1-й (, п-1) линейки соединены с управляющими входами логических ячеек (1+1)-й ли нейки, а выход логической ячейки плинейки соединен с выходом модуля. Выход модуля соединен с первым входом элемента И, второй вход кото 212 рого соединен с управляю1цим входом модуля. Выход элемента И соединен с вторым входом элемента ИЛИ, первый вход которого соединен с первым информационным входом модуля (на него подается переменная х), а выход с информационными входами логических ячеек первой линейки. При подаче на управляющий вход модуля сигнала ,, на информационные входы переменных х ,х и на настроечные входы сигналов U, , на выходе модуля реализуется логическая функция () определяемая вектором настройки. При подаче на управляющий вход сигнала модуль переходит в режим контроля. На чертеже приведена схема предлагаемого модуля при , построенного в соответствии с первообразной (2). Модуль содержит информационные входы 1-3, настроечные входы 4-11, управляющий вход 12, выход 13, логические ячейки 14-17 первой линейки (индекс 1 относится к элементам ИЛИ-НЕ соответствующих логических ячеек, а индекс 2 - к элементам НЕРАВНОЗНАЧНОСТЬ этих же ячеек), логические ячейки 18 и 19 второй ш нейки, логическую ячейку 20 третьей линейки, элемент И 21, элемент ИЛИ 22. Модуль работает в двух режимах: рабочем и контроля. В рабочем режиме на управляющий вход 12 подается сигнал , на информационные входы 1-3 - переменные Xj, Xg, их, соответственно, на настроечные входы 4-11 - сигналы настройки Uj , Ug соответственно. На выходе 13 модуля реализуется логическая функция f(х ) которая определяется вектором настройки tj (и, , и ,.„.,и)-. Рассмотрим алгоритм настройки. Обозначим у - значение реализуемой модулем, некоторой логической функции f (х , Хг,) на (1-1)м наборе, i 1,. Исходным для нахождения настройки является вектор W, (V, , i 1, , где v- i i .1, . -I Далее вы полйя тся п шагов преобразований. На каждом i-м шаге (i

3

1, n) получается вектор W; на нове вектора W;, :

0vT, (v, , v ,. , . , v, Z, , Z,, , . . . , Z,; ,

где m ,

Z; V,, ;

1 Г,тп

2) w (v, , V., ,.. ..,v ,p , p

P. 2. 1 .

где 1 ,

P; Vi ® v, ,

r. Z,j5Zf,i ,

i 1, 1, и т.д.

Ha n-M шаге получаем некоторы вектор

(w , w ,... , ) ,

w,

при этом вектор настройки U (w, ,

2 ) l

i 2,2.

Пример. Найти вектор настройки модуля для реализации логической функции f (х ,Х,)

1:

Очевидно, у y,j у у

УТ У, О,

УЬ Уе тогда

W., (0,0,0,1,1,0,1,1),

W-, (0,0,0,1,1,0,1,0),

w-j (0,0,0,1,1,0,0,0),

(0,0,0,1,1,1,0,0),

и (0,1,1,0,0,0,1,1),

откуда

и Us Ufi О,

и,

Ьг Ui и, и, 1. В режиме контроля модуль становится самопроверяемым. В этот режим он переводится подачей на управляющий вход 12 сигнала .

.Значение сигналов на информационных и настроечных входах в режиме контроля приведены в таблице.

При отсутствии неисправностей на выходе 13 модуля в двух подрежимах контроля появляется непрерывная последовательность импульсов типа меандр с периодом Т 2()1

8, гдеП

задержка на вентиль.

Появление любой константной неисправности произвольной кратности приводит к срыву генерации импуль2691214

сов либо в одном подрежиме контроля, либо в обоих. Причем в режиме контроля не проверяются константные неисправности на информационных и 5 настроечных входах модуля. Однако эти входы доступны, и обнаружение указанных неисправностей не выэыва, ет затруднений.

Формула изобретения

1.Универсальный логический модуль, содержащий n групп логических

t5 ячеек, причем информационные входы логических ячеек i-й группы соединены с i-M информационным входом модуля (i 1, п-1), настроечные входы i-й логической ячейки i-й группы

0 соединены с выходами (2j-1)-й и

логических ячеек (i+1)-й группы соответственно (j 1, ),настроечные входы k-й логической ячейки п-й группы соединены с (2k-1)-M и

5 2k-M настроечными входами модуля соответственно, отличающ я тем, что, с целью увеличения контролепригодности, модуль содержит элемент И и элемент ИЛИ, причем ин0 формационные входы логических ячеек п-й группы соединены с выходом элемента ИЛИ, первый вход которого соединен с п-м информационным входом модуля, вход задания режима ра- боты которого соединен с первым входом элемента И, выход которого соединен с вторым входом элемента ИЛИ, второй вход элемента И соединен с выходом логической ячейки первой . 0 группы и является выходом модуля.

2.Модуль поп.1,отличающ и и с я тем, что логическая ячейка содержит элемент ИЛИ-НЕ и эле-.

.мент НЕРАВНОЗНАЧНОСТЬ, причем первые 5 входы элементов ИЛИ-НЕ и НЕРАВНОЗНАЧНОСТЬ являются настроечными входами логической ячейки, информационный вход которой соединен с вторым входом элемента ИЛИ-НЕ, выход которог о соединен с вторым входом злемента НЕРАВНОЗНАЧНОСТЬ, выход которого является выходом логической ячейки.

и, и, и, и,. Us и, UT и.

Хз Xj

0010111 о

О О

о о

«.

О О 0110101 о

f(х,х,)

Генерация непрерывной последовательностиимпульсов

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный логический модуль | 1985 |

|

SU1264336A1 |

| Универсальный логический модуль | 1985 |

|

SU1312561A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1598161A1 |

| Универсальный логический модуль | 1988 |

|

SU1520505A1 |

| Универсальный логический модуль с самоконтролем | 1988 |

|

SU1644125A1 |

| Универсальный логический модуль | 1984 |

|

SU1242930A1 |

| Универсальный логический модуль | 1984 |

|

SU1218375A1 |

| Устройство для полиномиального разложения логических функций | 1988 |

|

SU1550507A1 |

| Многофункциональный логический модуль | 1990 |

|

SU1753589A1 |

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1765821A1 |

Изобретение относится к вычислительной технике и предназначено для реализации всех логических функций п переменных. Цель изобретения - повышение контролепригодности модуля. Универсалышй логический модуль содержит п линеек, построенных из логических ячеек, в состав которых входят элементы Ш1И-НЕ и НЕРАВНОЗНАЧНОСТЬ. В рабочем режиме модуль реализует логические функции,в режиме контроля становится легко тестируемой схемой и при отсутствии неисправностей генерирует непрерыв(Л ную последовательность импульсов типа меандр. 1 з.п. ф-лы, 1 ил.

| Универсальный логический модуль | 1980 |

|

SU947851A1 |

| Универсальный логический модуль | 1983 |

|

SU1119003A1 |

Авторы

Даты

1986-11-07—Публикация

1985-04-08—Подача