Выход (i+6)-ro элемента РАВНОЗНАЧНОСТЬ соединен с j-м входом пятого элемента РАВНОЗНАЧНОСТЬ, третий вход которого соединен с первым входом третьего элемента РАВНОЗНАЧНОСТЬ, (j+1)-u вход которого соединен с выходом (j+9)-ro элемента РАВНОЗНАЧНОСТЬ, четвертый вход которого соединен с четвертым входом пятого элемента РАВНОЗНАЧНОСТЬ и вторым входом задания режима устройства. Первый вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с третьим входом задания режима устройства, а второй вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с вторым информационным входом устройства, вторым входом восьмого элемента РАВНОЗНАЧНОСТЬ и вторым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ. Третий вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с четвертым информационным вхо- дом устройства, третьим входом второго элемента РАВНОЗНАЧНОСТЬ, третьим входом восьмого элемента РАВНОЗНАЧНОСТЬ и третьим входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ. Выход эле- мента НЕРАВНОЗНАЧНОСТЬ соединения с вторым входом (3j+6)-ro элемента РАВНОЗНАЧНОСТЬ, выход которого соединен с пятым входом (7-j)-ro элемента РАВНОЗНАЧНОСТЬ. Выход второго элемента РАВНОЗНАЧНОСТЬ соединен с вторыми входами седьмого и десятого элементов РАВНОЗНАЧНОСТЬ. Первый информационный вход устройства соединен с первым входом (21-1)-го (.2,3,4) элемента ИЛИ, второй вход которого соединен с l-м настроечным входом устройства. Выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом 21-го элемента ИЛИ, второй вход которого соединен с (1-1)-м настроеч- ным входом устройства. Выход j-ro элемента ИЛИ соединен с 0+2)-м входом седьмого элемента РАВНОЗНАЧНОСТЬ. Выход (J+2J- го элемента ИЛИ соединен с 0+2)-ми входа- ми восьмого и девятого элементов РАВНОЗНАЧНОСТЬ. Выход (j+4)-ro элемента ИЛИ соединен с (+2)-ми входами десятого и двенадцатого элементов РАВНОЗНАЧНОСТЬ. Выход (j+6)-ro элемента ИЛИ соединен с (j-KJ)-M входом одиннадца- того элемента РАВНОЗНАЧНОСТЬ.

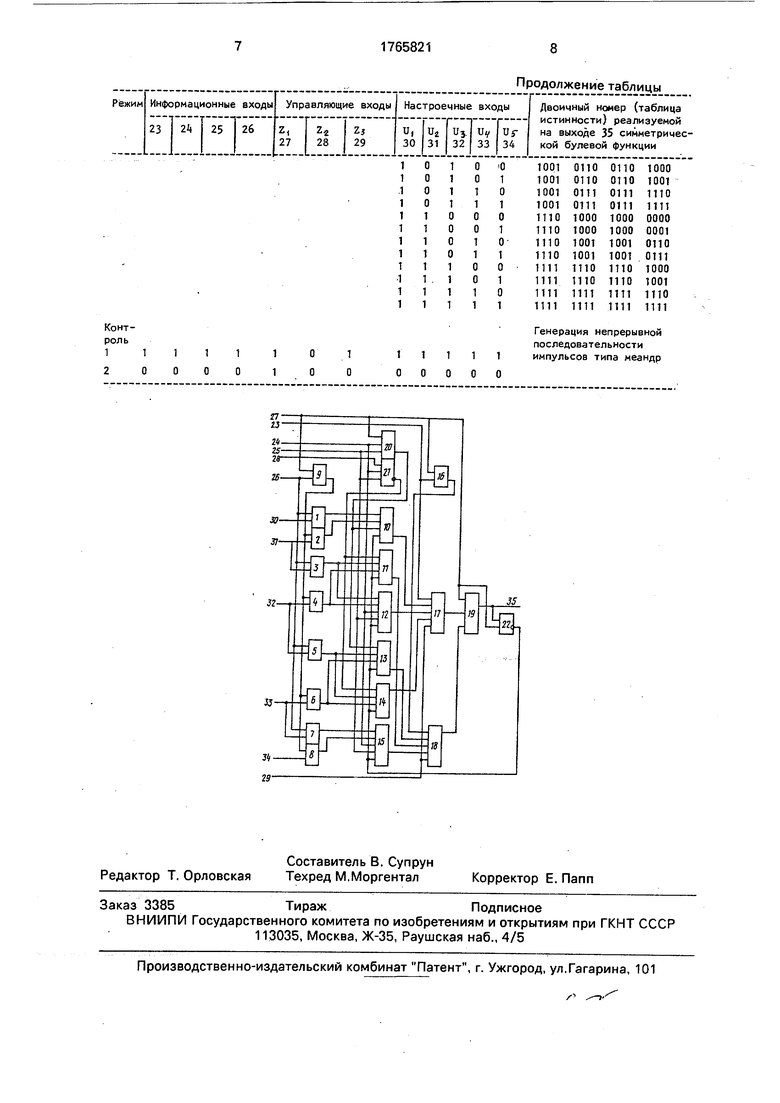

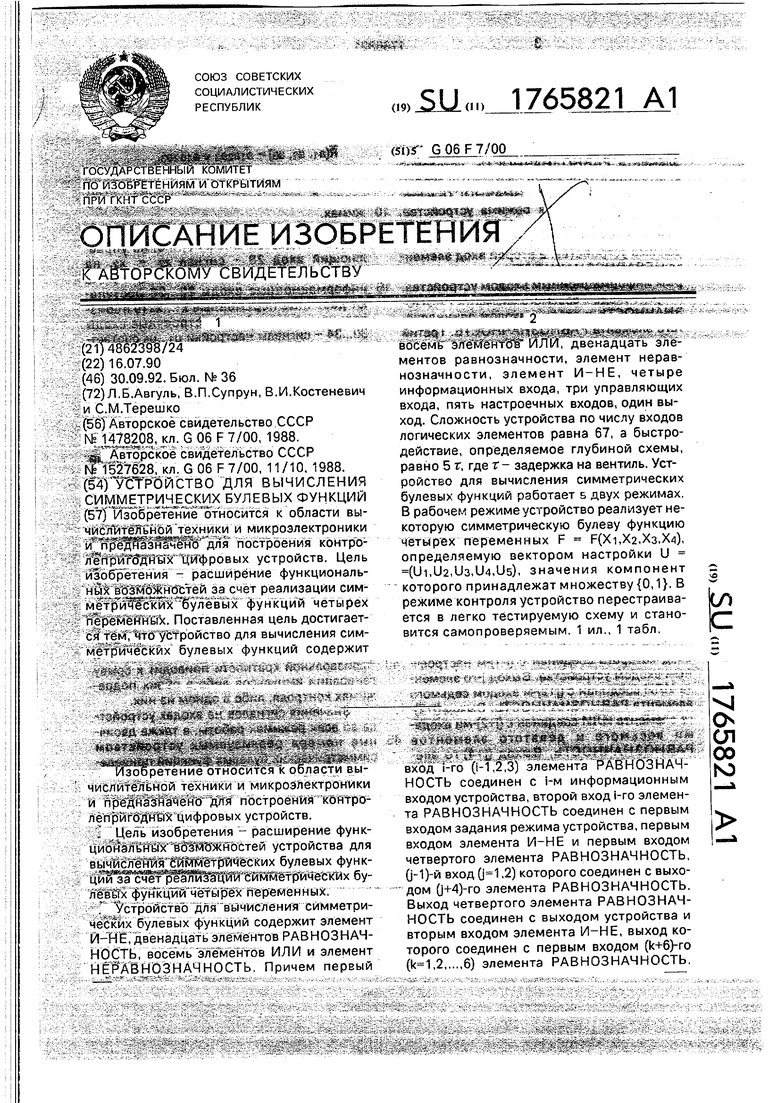

На чертеже представлена схема устройства для вычисления симметричных булевых функций.

Устройство содержит восемь элементов ИЛИ 1...8, двенадцать элементов РАВНОЗНАЧНОСТЬ 9.„20, элемент НЕРАВНОЗНАЧНОСТЬ 21, элемент И-НЕ 22, четыре информационных входа 23...26, три управляющих входа 27,28 и 29, пять настроечных входов 30...34 и один выход 35.

Отметим, что элемент НЕРАВНОЗНАЧНОСТЬ 21 реализует булеву функцию

R(ai, az. аз) 313233 v 313233.

Устройство для вычисления симметрических булевых функций работает в двух режимах.

В рабочем режиме на управляющий вход 27 подается сигнал zi 0, на управляющий вход 28 - сигнал гг Х2, на управляющий вход 29 - сигнал гз 0. На информационные входы 23...26 поступают двоичные переменные xi...x4 (в произвольном порядке), на настроечные входы 30...34 - сигналы настройки ui...us соответственно, значения которых принадлежат множеству {0,1}. На выходе 35 реализуется некоторая симметрическая булева функция F F(xi, X2, хз, x/j), определяемая вектором настройки U (щ, ua, из, U4, иб).

В режим контроля устройство переводится подачей сигналов zi 1 на управляющий вход 27 и сигнала Z2 0 на управляющий вход 28. В первом подрежиме контроля на все информационные 23...26, управляющий 29 и все настроечные входы 30,..34 подаются сигналы логической единицы. Во втором подрежиме контроля на эти входы подаются сигналы логического нуля. При отсутствии неисправностей в устройстве на выходе 35 возникает генерация непрерывной последовательности импульсов типа меандр с периодом 8 т, где т - задержка на вентиль (период определяется удвоенной глубиной схемы по цепи обратной связи). Возникновение любой константной неисправности произвольной кратности приводит к срыву генерации импульсов либо в обоих подрежимах контроля, либо в одном из них.

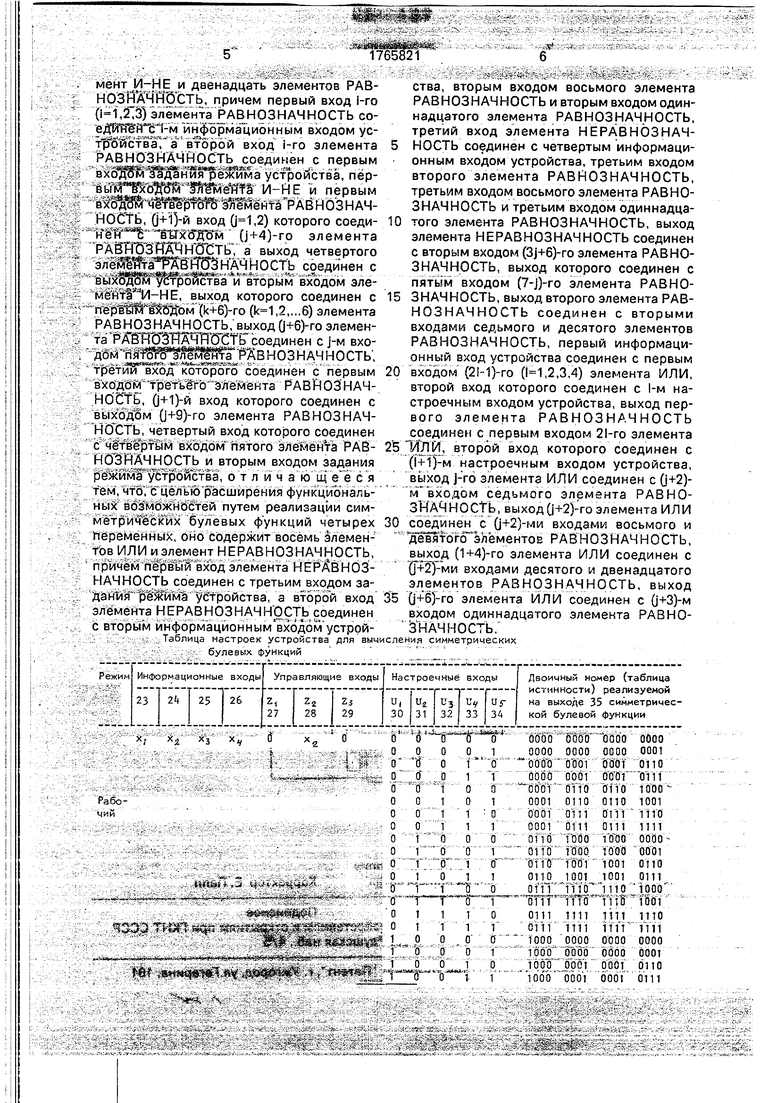

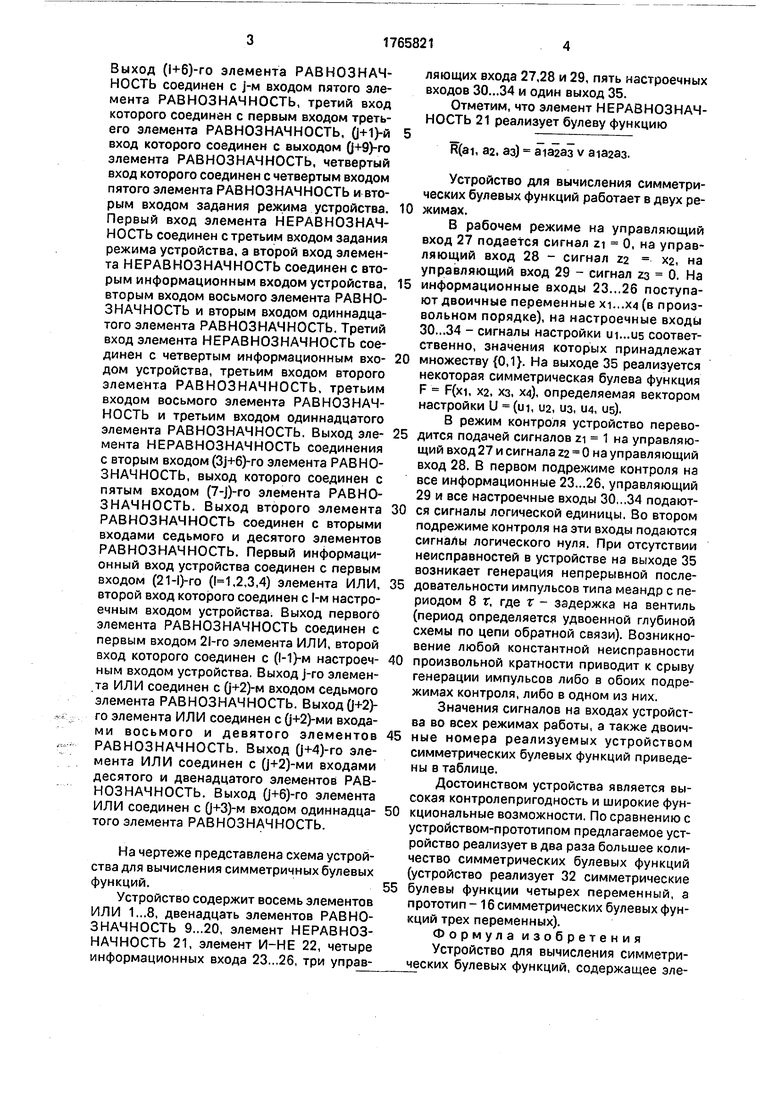

Значения сигналов на входах устройства во всех режимах работы, а также двоичные номера реализуемых устройством симметрических булевых функций приведены в таблице.

Достоинством устройства является высокая контролепригодность и широкие функциональные возможности. По сравнению с устройством-прототипом предлагаемое устройство реализует в два раза большее количество симметрических булевых функций (устройство реализует 32 симметрические булевы функции четырех переменный, а прототип - 1 б симметрических булевых функций трех переменных).

Формула изобретения

Устройство для вычисления симметрических булевых функций, содержащее элемент И-НЕ и двенадцать элементов РАВ- НрЗЙХЧЙ бСТЬ, причем первый вход 1-го (,O) элёментГРАВ НОЗНАЧНОСТЬ со- (Јюрмацио н н ым входом ус- fffotfcfBaTa второй вход 1-го элемента РАВНОЗНАЧНОСТЬ соединен с первым

Н8ЈЬ. ytenttr -«Домик ft.: .,входом заданияГр ежим а устройства, пер- вь Гм ЪЖм э Шие нТЗ И-НЕ и первым в Ш «1Гт1в%р о эЖмёнтГРАЁНйЗНАЧства, вторым входом восьмого элемента РАВНОЗНАЧНОСТЬ и вторым входом одиннадцатого элемента РАВНОЗНАЧНОСТЬ, третий вход элемента НЕРАВНОЗНАЧНОСТЬ соединен с четвертым информационным входом устройства, третьим входом второго элемента РАВНОЗНАЧНОСТЬ, третьим входом восьмого элемента РАВНОЗНАЧНОСТЬ и третьим входом одиннадца- ЯОСТЬ, (|+1)-й вход (,2) которого соеди- 10 того элемента РАВНОЗНАЧНОСТЬ, выход ; (j+4)-ro элемента элемента НЕРАВНОЗНАЧНОСТЬ соединен РА Ш3-ШЭ ть. 1з выход четвертого с вторым входом (3j+6)-ro элемента РАВНОэлёмШга рТЁЙЙЗН АЧНОСТЬ соединен с вьГхдаГЖГ

л &и-ЪЖ- -;,.;: т.-- -.

ойства и вторым входом элеЗНАЧНОСТЬ, выход которого соединен с

,.л. . ...,----пятым входом (7-j)-ro элемента РАВНОмен т И-НЕ, выход которого соединен с 15 ЗНАЧНОСТЬ, выход второго элемента РАВ- пё$ё&&ГШКом (k+6)-ro (,2,...6) элемента РАВНОЗНАЧНОСТЬ, выход 0+6)-го элемента РД ВНО 3 ЙАЧТГО С ТБ соединен с j-м вхо- fl6M rifl fo 3 e M Ta PXBH03HA4HOCTb ,

&вуЬКЪ&&$ - Ыь, %Ь ЪГЧл&Ц-. Чл - - „.третий вход которого соединен с первым входом третьего элемента РАВНОЗНАЧНОСТИ, 0+1)й вход которого соединен с выШдом 0+9)-го элемента РАВНОЗНАЧ- НОСТЬ, четвертый вход которого соединен

НОЗНАЧНОСТЬ соединен с вторыми входами седьмого и десятого элементов РАВНОЗНАЧНОСТЬ, первый информационный вход устройства соединен с первым 20 входом (21-1)-го (,2,3,4) элемента ИЛИ, второй вход которого соединен с l-м настроечным входом устройства, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом 21-го элемента

с четвёртым входом пятого элёШйта РАВ- 25 ШИ, второй вход которого соединен с НО ЗНАЧНрСТЬ и вторым входом задания (Т+Т)-м настроечным входом устройства,

режима устройства, о т л и ч а ю щ е ее я тем, что , с целью расширения функциональных возможностей путем реализации симметрических булевых функций четырех Переменных, оно содержит восемь элемен- То в ИЛИ и элемент НЕРАВНОЗНАЧНОСТЬ, причем первый вход элементаЙЁРДвнбЗ- НАЧНОСТЬ соединен с третьим входом завыход j-ro элемента ИЛИ соединен с Q+2)- м входом седьмого элемента РАВНОЗНАЧНОСТЬ, выход QH-2)-ro элемента ИЛИ 30 соединен с (+2)-ми входами восьмого и девято пГзлементов Р АВ НОЗ Н АЧ Н ОСТЬ, выход (1+4)-го элемента ИЛИ соединен с (Г+2)-ми входами десятого и двенадцатого элементов РАВНОЗНАЧНОСТЬ, выход

дания ре жима устройства, а второй вход 35 (j+6)-ro элемента ИЛИ соединен с 0+3)-м элемента НЕРАВНОЗНАЧН ОСТЬ соединен ,ВХОДОМ одиннадцатого элемента РАВНО- с вторым йнформационным входом устрой- ШАЧНОСТЬ,

Таблица настроек устройства для вычисления симметрических булевых функций

ЗНАЧНОСТЬ, выход второго элемента РАВ-

НОЗНАЧНОСТЬ соединен с вторыми входами седьмого и десятого элементов РАВНОЗНАЧНОСТЬ, первый информационный вход устройства соединен с первым входом (21-1)-го (,2,3,4) элемента ИЛИ, второй вход которого соединен с l-м настроечным входом устройства, выход первого элемента РАВНОЗНАЧНОСТЬ соединен с первым входом 21-го элемента

ШИ, второй вход которого соединен с (Т+Т)-м настроечным входом устройства,

выход j-ro элемента ИЛИ соединен с Q+2)- м входом седьмого элемента РАВНОЗНАЧНОСТЬ, выход QH-2)-ro элемента ИЛИ 30 соединен с (+2)-ми входами восьмого и девято пГзлементов Р АВ НОЗ Н АЧ Н ОСТЬ, выход (1+4)-го элемента ИЛИ соединен с (Г+2)-ми входами десятого и двенадцатого элементов РАВНОЗНАЧНОСТЬ, выход

35 (j+6)-ro элемента ИЛИ соединен с 0+3)-м ,ВХОДОМ одиннадцатого элемента РАВНО- ШАЧНОСТЬ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления симметрических булевых функций | 1990 |

|

SU1789976A1 |

| Устройство для вычисления симметрических булевых функций | 1989 |

|

SU1765820A1 |

| Устройство для вычисления симметрических булевых функций | 1991 |

|

SU1835542A1 |

| Устройство для вычисления симметрических булевых функций | 1987 |

|

SU1478208A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1587489A1 |

| Устройство для выделения симметрических булевых функций | 1991 |

|

SU1833859A1 |

| Программируемое устройство | 1991 |

|

SU1789979A1 |

| Многофункциональный логический модуль | 1985 |

|

SU1247858A1 |

| Устройство для вычисления симметрических булевых функций | 1987 |

|

SU1432500A1 |

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1527628A1 |

ТЯзоВрётен е относйтся к области вы- чисШтШТьйЬЙ техники и микроэлектроники построения контрол епр йТ8ЩЯ ьГх Цифровых устройств. Цель изобретения - расширение функциональнь в о зйо нбЪтей за счет реализации симметр й с1 и1 т6 уле в ых функций четырех ; Ъеремёйных. Поставленная цель достигаетГШтё ЧтЙ тройство для вычисления симf Шт|гичШШх булевых функций содержит Тзобретение относится к области вы- числитё льной техники и микроэлектроники и npe 4Hf3lia4eHO 4/ia построёййя контр0- лепрйгб Дн 1Х цифровых устройств. , Цель изобретения - расширение функ- ционэл6ййГх б8з Шжностей устройства для вь1ч11Сл1|Ш1дс Р|м1Мётр й«1ёских булевых функ- ци Тс из й гШШеТ йчёШйх бу- левьТх функций четы р ёх переменных. Г Устройство для вычисления симметрических булевых функций содержит элемент И-ЯЕ, двенадцать элементов РАВНОЗНАЧНОСТЬ, вЬсемь Элементов ИЛИ и элемент НЕЖВЙ ОЗНАЧНОСТЬ. Причем первый «.« йй- |,|«ЖШ йШЙ ЙИВ &««к « восемь ИЛИ, двенадцать элементов равнозначности, элемент неравнозначности, элемент И-НЕ, четыре информационных входа, три управляющих входа, пять настроечных входов, один выход. Сложность устройства по числу входов логических элементов равна 67, а быстродействие, определяемое глубиной схемы, равно 5 т, где т- задержка на вентиль. Устройство для вычисления симметрических булевых функций работает s двух режимах. В рабочем режиме устройство реализует некоторую симметрическую булеву функцию чётыр ех переменных F F(Xi,X2,X3,X4), определяемую вектором настройки U (Ui,U2,U3,U4,U5), значения компонент которого принадлежат множеству {0,1}. В режиме контроля устройство перестраивается в легко тестируемую схему и становится самопроверяемым. 1 ил., 1 табл. - -.. vi iBiЈT r-; t - --A.V,T V . --- .-..-. -.-. i..j,-. ;W у;; С .v- ;:--..Г:.;,-j.--. ь-.--; .--,.. «ЛГ; Щшш ®-;вщ :-|й |й |Ш Щ й й ;Ш|:; ч : ..,-.; ; 1| «айбШ ййа Ш йз ШаЛййй, ; Фййг } й1вййШЙ Й й ; |Щ ;ЖМййШШ1|8 айг в &ТРго1РТ Г15 га Ш81Шч НОСТЬ соединен с i-м информационным входом устройства, второй вход 1-го элемента РАВНОЗНАЧНОСТЬ соединен с первым входом задания режима устройства, первым входом элемента И-НЕ и первым входом четвертого элемента РАВНОЗНАЧНОСТЬ, (-1)-й вход .2) которого соединен с выходом Q+4)-ro элемента РАВНОЗНАЧНОСТЬ. Выход четвертого элемента РАВНОЗНАЧНОСТЬ соединен с выходом устройства и вторым входом элемента И-НЕ, выход которого соединен с первым входом (к+6)-го (,26) элемента РАВНОЗНАЧНОСТЬ. СЛ с N| О СЛ 00 N3

8Йй|Т ,3 , Ч

$ал( F ffSafa& -

,

i-

, -Sr4, Л. - - ,V r-- fiaSftsrsffi&s SiWSsSMEasiffiSb .ЛС85

Продолжение таблицы

Авторы

Даты

1992-09-30—Публикация

1990-07-16—Подача