Изобретение относится к вычислительной технике и может быть использовано как самостоятельный ассоциативный процессор и как составной элемент матричных ассоциативных вычислительных машин.

Целью изобретения являетя расширение функциональных возможностей за счет использования систем счисления по любому модулю основания.

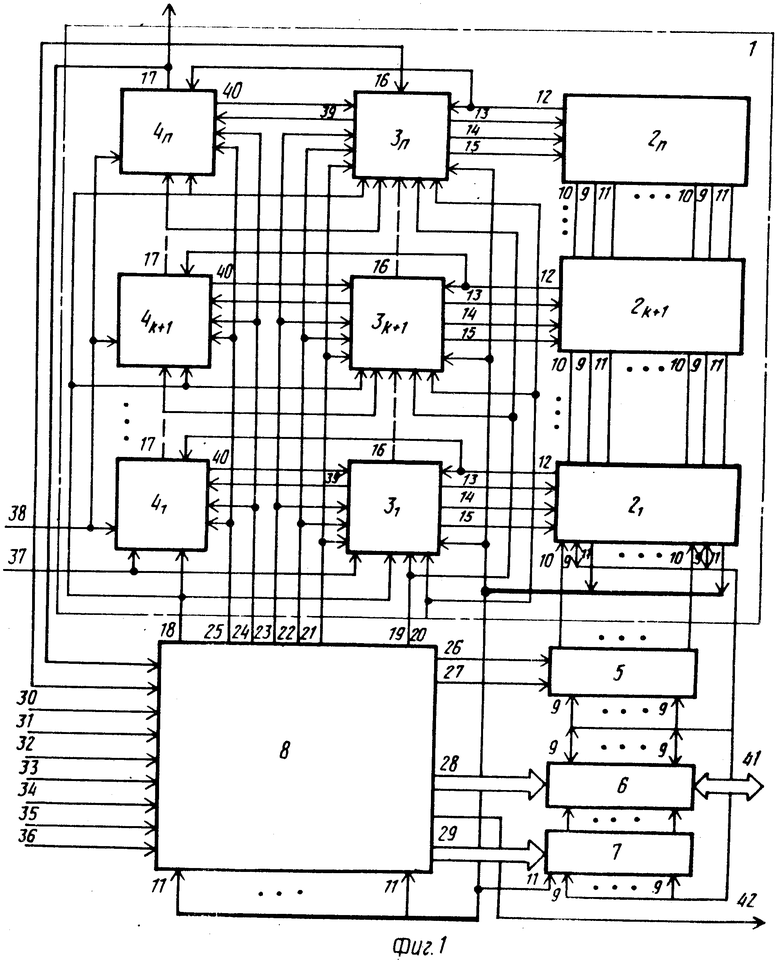

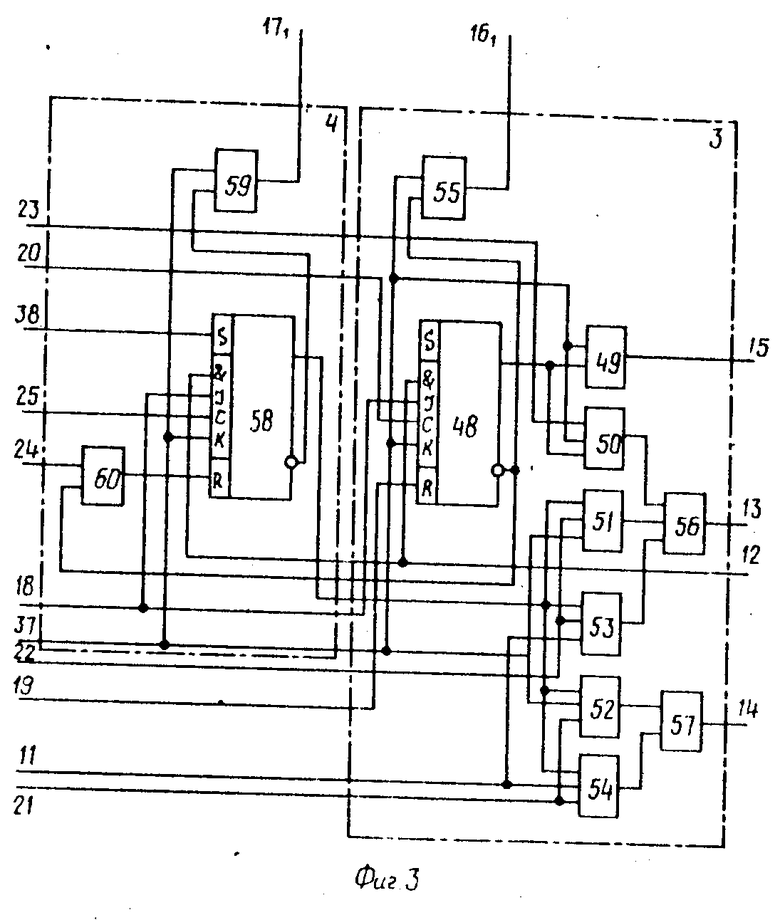

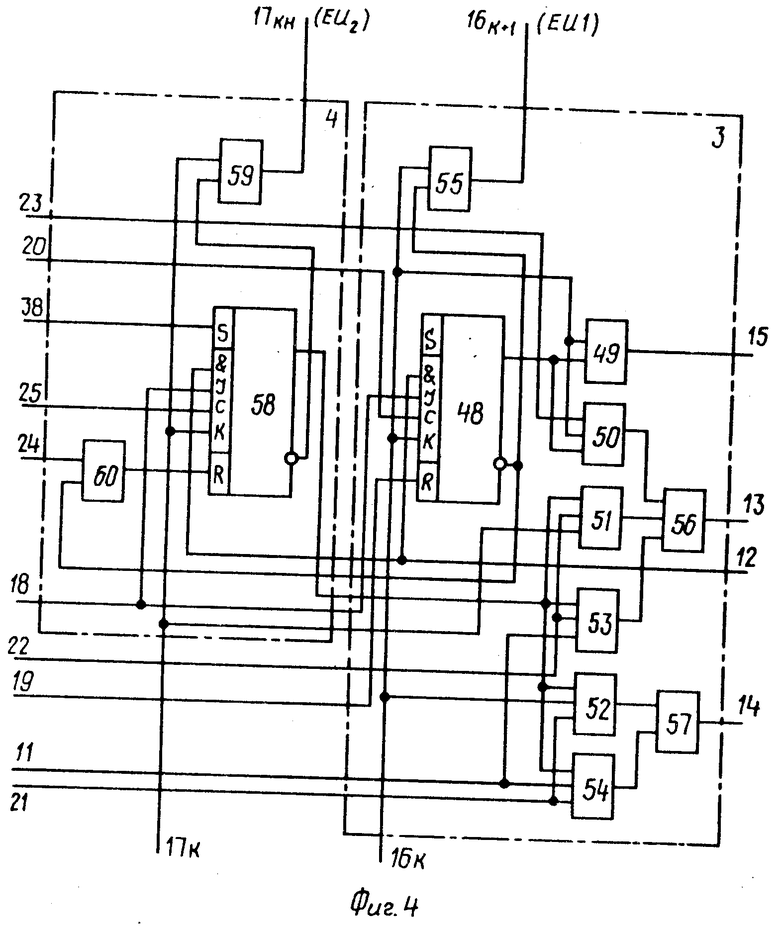

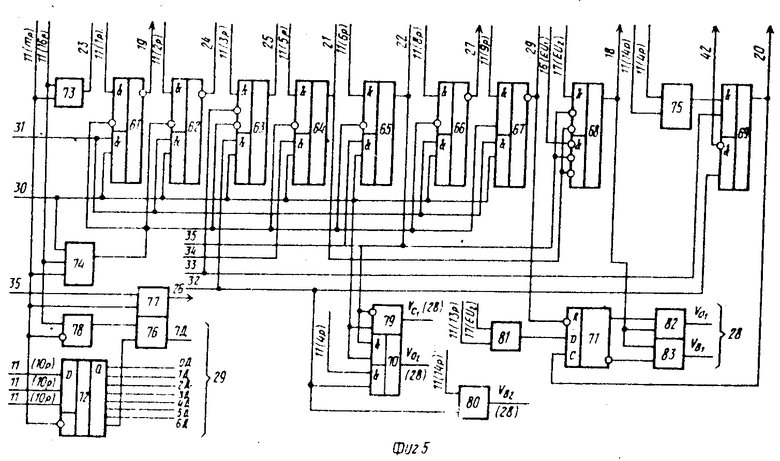

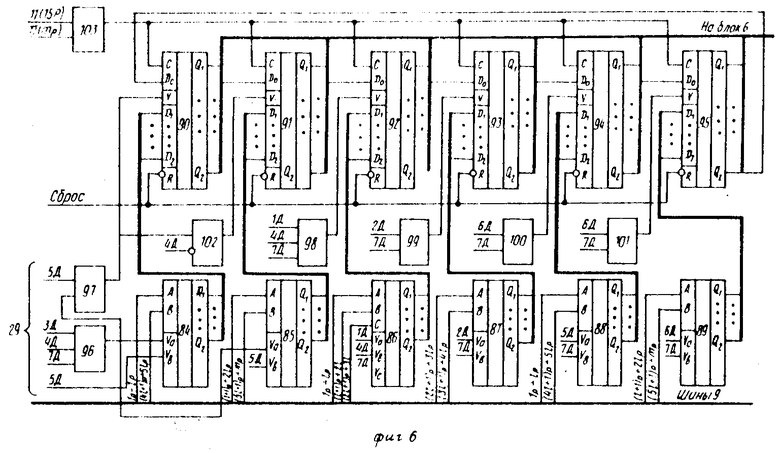

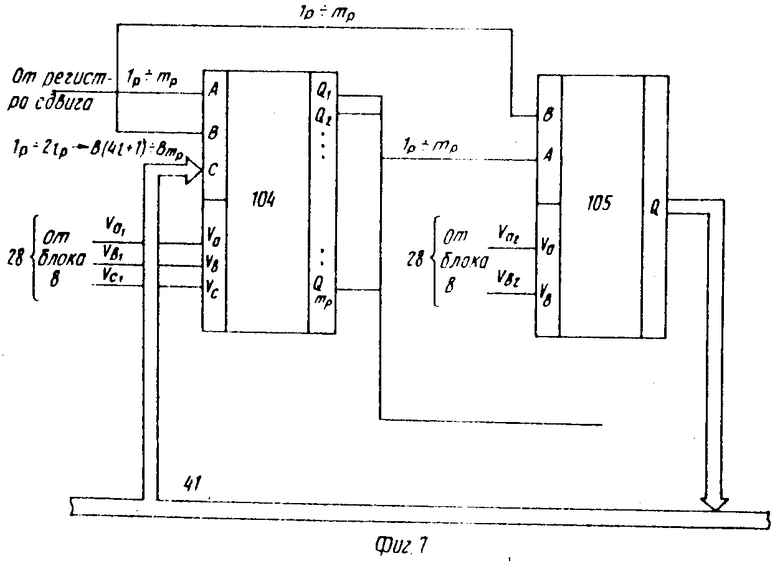

На фиг. 1 приведена функциональная схема предлагаемого ассоциативного процессора; на фиг.2 - функциональная схема ассоциативной ячейки памяти; на фиг.3 - функциональная схема первых блоков управления первой и второй групп ассоциативной матрицы памяти; на фиг.4 - функциональная схема блоков управления с второго по n-й первой и второй групп ассоциативной матрицы памяти; на фиг. 5 - функциональная схема блока управления; на фиг.6 - функциональная схема блока сдвига; на фиг.7 - функциональная схема блока ввода-вывода.

Ассоциативный процессор (см. фиг. 1) содержит ассоциативну матрицу 1 памяти размером nxm из однотипных ассоциативных ячеек памяти, где m - количество разрядов матрицы, n - количество строк матрицы, i-я строка матрицы 1 содержит ассоциативный регистр 2 памяти, i-е блоки 3.i и 4.i управления первой и второй групп, регистр 5 маски, блок 6 ввода-вывода, регистр 7 сдвига, блок 8 управления, информационные входы-выходы 9 ассоциативных ячеек памяти, маскирующие шины 10 ассоциативных ячеек памяти, управляющие шины 11, шина 12 совпадения ассоциативных регистров 2 памяти, выходы 13 разрешения чтения блоков 3 управления, выходы 14 разрешения записи, выходы 15 разрешения выдачи управляющей информации, вход 16 блокировки блока 3 управления, вход 17 блокировки блока 4 управления, с первого по десятый выходы 18-27 блока 8 управления, первую группу 28, вторую группу 29 выходов блока 8 управления, вход 30 признака внешнего управления, вход 31 сброса, вход 32 выборки, тактовый вход 33 ассоциативного процессора, вход 34 записи, вход 35 чтения ассоциативного регистра, вход 36 записи в регистр маски ассоциативного процессора, вход 37 признака блокировки, вход 38 признака установки ассоциативного процессора, входы 39 режима блоков управления первой группы, входы 40 режима блоков управления второй группы, информационный вход-выход 41 ассоциативного процессора, выход 42 запроса на обмен ассоциативного процессора.

Каждая ассоциативная ячейка памяти (см. фиг.2) содержит триггер 43 матрицы nxm, элемент сравнения 44 матрицы размером nxm, элементы И 45, 46 и 47 соответственно первой, второй и третьей матриц размером nxm.

Каждый блок 3 управления (см. фиг.3 и 4) содержит IK-триггер 48, семь элементов И 49-55, два элемента ИЛИ 56-57, каждый блок 4 управления (см. фиг.3 и 4) содержит IK-триггер 58, элемент И 59 и элемент ИЛИ 60.

Блок 8 управления (см. фиг.5) содержит десять элементов 2И-ИЛИ 61-70, триггер 71, дешифратор 72, шесть элементов ИЛИ 73-78 и пять элементов И 79-83.

Регистр 7 сдвига (см. фиг.6) содержит 12 мультиплексоров 84-95, шесть элементов ИЛИ 96-101, два элемента И 102, 103.

Блок 6 ввода-вывода (см. фиг.7) содержит два мультиплексора 104 и 105.

Работа ассоциативного процессора (АП) основана на табличном способе счисления по позициям при помощи программ, причем в качестве таблиц используются элементарные таблицы умножения, деления, сложения, вычитания от 0-9 или любые другие таблицы, причем программы и таблицы хранятся в ассоциативных ячейках памяти.

Управление ассоциативными ячейками осуществляется по двум каналам, один из которых используется для работы управляющей программы, а другой используется управляющей программой для поиска необходимых таблиц, данных и свободных ячеек. Для ввода необходимых программ, элементарных таблиц, а затем массивов данных на шины 30, 38 и 37 подаются единичные сигналы "Управление внешнее", "Установка в единичное состояние" триггеров 58 и "Блокировка". После установки триггеров 58 в единичное состояние сигналы с шины 38 снимаются, подается информация на информационные входы-выходы 41, необходимая для записи в ассоциативный процессор (подпрограмма работы, константы, информация для обработки) и подается сигнал "Запись" на шину 34, при этом запись разрешена только в первую строку, а остальные строки заблокированы триггерами 58 через элементы И 59 и шины 17 предыдущей строки. Через время, необходимое для записи информации в строку, подается единичный импульс выборки по шине 32. По заданному фронту этого импульса триггер 58 блока управления устанавливается в нулевое состояние и снимает блокировку обращения к другим строкам. В следующем такте единичного импульса по шине 32 выборки записывается информация в следующую строку и так далее, пока не закончится запись. Чтение информации с АП осуществляется воздействием уровня логической единицы на входы 30, 37 и 38. Затем по сигналу "Есть информация" (ЕИ2) по шине 17 внешнее устройство управления снимает единичный уровень сигнала с шины 38 и подает уровень логической единицы на шину 35 чтения. Подавая последовательно сигналы "Выборка" по шине 32, на шине 9 будут формироваться с первой до n строки матрицы.

Опрос содержимого ассоциативной матрицы памяти осуществляется подачей уровня логической единицы сигнала "Управление внешнее" по шине 30, кода маски по шине входа-выхода 41 и сигнала "Запись в регистр маски" по шине 36. После записи в регистр маски сигнал "Запись в регистр маски" снимается, при отсутствии на шинах 34 записи, 35 чтения и на шинах 16, 17 (ЕИ1, ЕИ2) высокого уровня на выходе 18 элемента 2И-ИЛИ 68 блока 8 управления установится высокий уровень опроса, на шину 41 подается код аргумента, который может быть меткой программы, на шину 32 подается единичный импульс "Выборка". При совпадении кода аргумента с немаскированной частью информации строк матрицы, на шинах 12 устанавливается уровень логической единицы.

Па заднему фронту импульса "Выборка" фиксируются результаты сравнения на триггерах 58, инверсные выходы этих триггеров 58 устанавливают на выходной шине 17 сигнал "Есть информация", который разрешает обращение к совпавшим строкам по порядку аналогично описанному выше режиму чтения и записи при внешнем управлении. Поле матрицы разделено на части: поле меток, поле информации. Каждая строка подпрограммы кодируется одной меткой. Допустим, подпрограмма сложения кодом "+", умножение кодом "х" и т.д. В режиме "Опрос" подпрограммы участвует поле меток.

Для перехода на управление от подпрограммы, хранящейся в ассоциативной матрице памяти, подается уровень логической единицы сигнала "Управление внешнее" по шине 30, кода маски по шине 41 и сигнала "Запись в регистр маски" по шине 36. После записи в регистр маски сигнал "Запись в регистр маски" снимается, на шину 41 подается код аргумента, который является меткой подпрограммы. На шину 33 подается сигнал логической единицы, по заднему фронту которой устанавливаются в единичное состояние триггеры 48 совпавших строк ячеек, инверсные выходы которых устанавливают в ноль соответствующие им триггеры 58, что обеспечивает чтение первой совпавшей строки по управляющим шинам 11 через элементы И 49 и 47.

По заднему фронту тактового сигнала (ТИ) последовательно читаются по порядку все совпавшие строки.

Внутреннее управление осуществляется при помощи блока 8 управления, на который поступает в позиционном коде информация с управляющих шин 11.

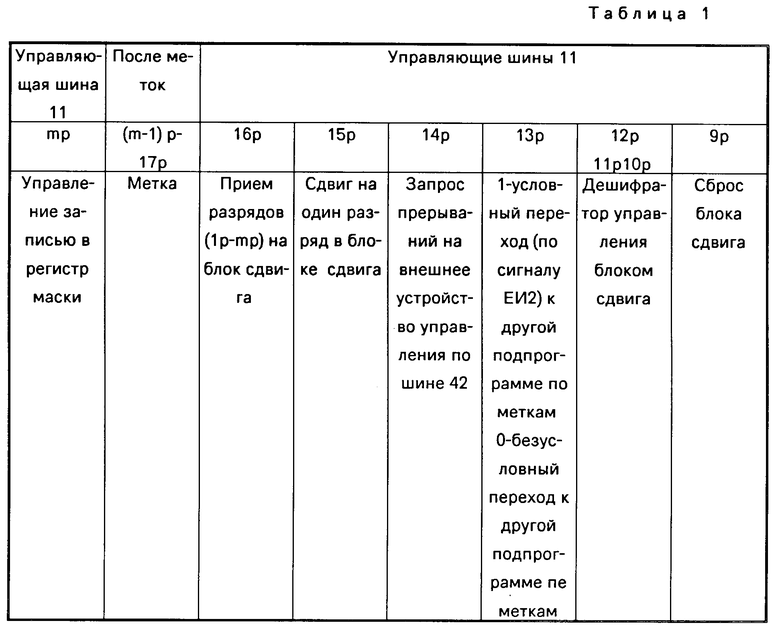

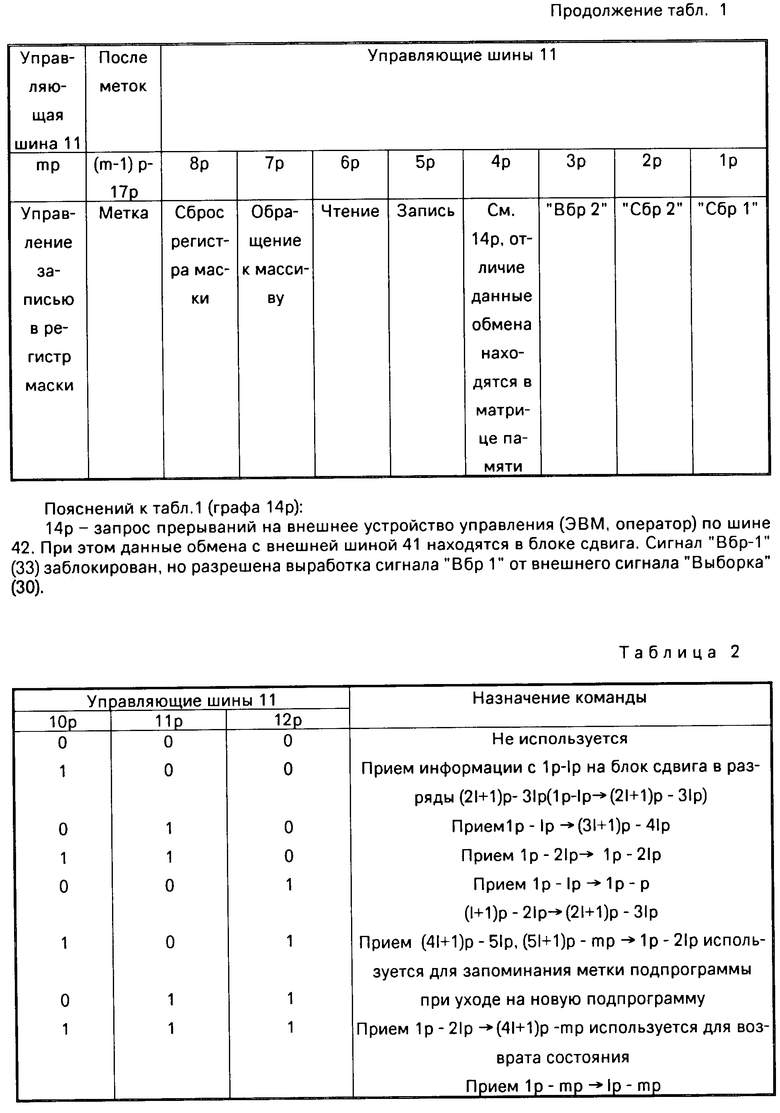

В табл.1 в виде управляющего слова приводится пример распределения управляющих шин по разрядам, в соответствии с которым приведен пример конкретного выполнения устройства.

Дешифратор 72 управления блоком сдвига производит дешифрацию управляющих сигналов в соответствии с табл.2.

В табл.3 приведено назначение управляющих сигналов на V-входах мультиплексоров 104 и 105 блока 6 ввода-вывода.

Логические операции сравнения, умножения и логического сложения осуществляются следующим образом. Операция сложения осуществляется непосредственно при опросе ассоциативной матрицы памяти (АЗУ), операция логического умножения осуществляется путем записи информации в незамаскированные строки, логическое сложение - это запись двух слов в одну ячейку, причем первое записывается без маски, а для второго слова записи маски будет являться код первого слова. Арифметические операции осуществляются табличным способом как по внутренней подпрограмме, так и по внешнему управлению по элементарным таблицам сложения, вычитания, умножения, деления, извлечения квадратного корня и другим, причем вычисления производятся по позициям над числами с произвольной длиной.

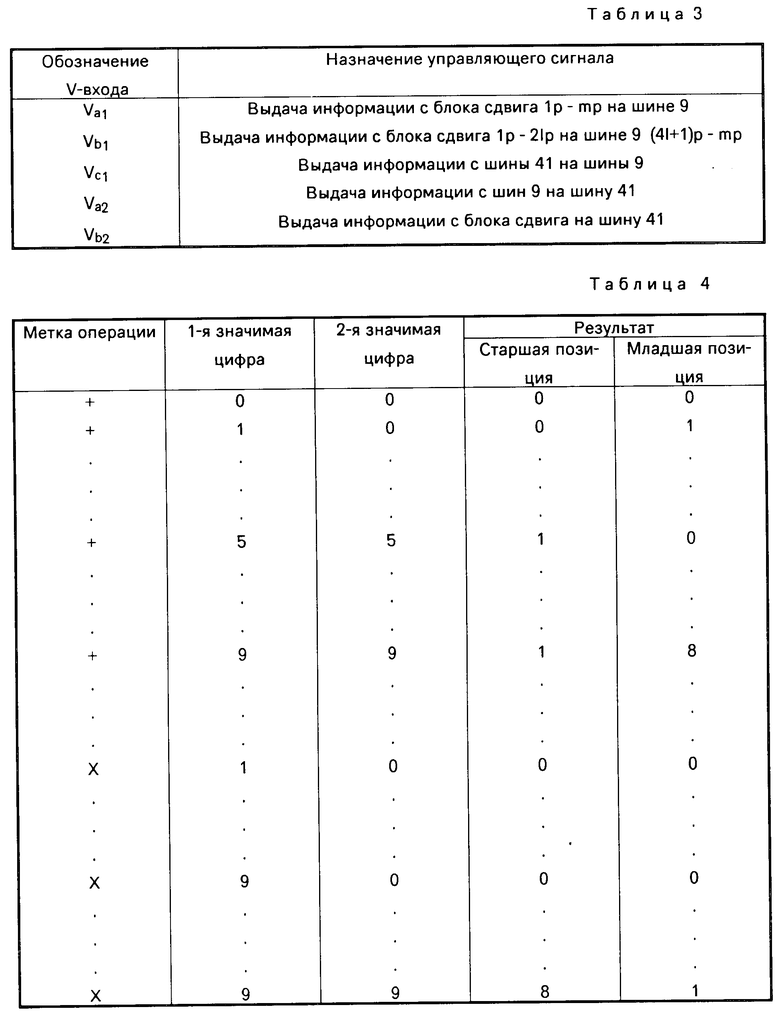

В табл.4 приведен пример записи элементарных таблиц в память АП.

Рассмотрим пример выполнения операции сложения в десятичном счислении. Допустим, вместе с подпрограммами и таблицами ввели два числа, которые необходимо сложить 1345+1942.

При вводе каждая цифра кодировалась своим весом в виде метки: 5 и 2 - весом единиц, 4 кодировалась весом десятки, следующая - сотни и так далее. Подпрограммы могут быть составлены для вычисления со старших или с младших позиций. Допустим, выбрана подпрограмма, начала вычислений с младших позиций.

При появлении на информационных шинах в режиме опроса кода "+" и тактового импульса на шине 33, триггеры 48, информация которых в поле меток совпала с кодом "+", установятся в единичное состояние. На шине ЕИ1 (16) появляется нулевой уровень, АП переходит в режим обработки информации.

По каждому тактовому импульсу на входе 33 при отсутствии блокировки на шине 37 и логического нуля в 4-м и 14-м разрядах управляющего слова (запрос к внешнему устройству) вырабатывается сигнал Вбр1 на шине 20, по которому читаются последовательно команды подпрограммы сложения. По первой команде заносится код на регистр маски для выделения при "опросе" кода веса чисел, затем команда "опроса" чисел с кодом веса единицы. Результат опроса запоминается на триггерах 48. При выполнении этой операции ставится условие, переход к подпрограмме с ЕИ2 по нулю или "1". При наличии чисел с весом "1" в десятичном счислении, в данном случае 2 и 5, на шине ЕИ2 (17) нулевой уровень, т. е. осуществляется переход по нулю, если ЕИ2 равен 1, то осуществляется метка "+" и при условии сигнал ЕИ2 равен нулю, числа 2 и 5 заносятся в блок сдвига и метятся, что они выбраны. Затем заносится код в регистр маски для маскирования результата табличной операции в режиме опроса таблицы. Затем опрашивается таблица сложения от 0-9. Следующая команда читает результат опроса таблицы с занесением его на блок сдвига. Следующие команды заносят старшую позицию результата сложения в свободные строки АЗУ с весом десятки и снова выполняется команда опроса числа с весом единиц. Затем повторяется команда "опроса" чисел с кодом веса единицы. В данном случае больше чисел с весом "1" нет. По этому условию программа сложения переходит к ветви подпрограммы с меткой "+" и при условии ЕИ2 равен единице. По этой ветви подпрограммы результат с блока сдвига, младшая позиция с кодом позиции выбранных чисел записывается в массив выдачи АЗУ и сбрасывается регистр сдвига. В этом случае записывается число 7 с весом кода десятки. Переходят на ветвь метки "+" при условии ЕИ2 равен 0. Числа по результату опроса заносятся в блок сдвига, метятся строки выбранных чисел и опять опрашивается таблица сложения, читается результат сложения. Старшая позиция полученного значения чисел, если она есть, записывается с весом на 1 больше, а младшая остается в блоке сдвига. Если чисел с этим весом больше нет, то результат записывается в массив вывода кодом десятки и программа переходит к опросу чисел с кодом позиции сотни.

В данном примере 4+4=8, записывают 8 с кодом позиции десять, сложение чисел с кодом позиции сто-3 и 9. При опросе таблицы сложения для 3 и 9 и чтения результата сложения, получается число 12, содержащее две позиции, старшую 1 с кодом веса позиции тысяча и младшую 2 с кодом веса позиции сотни. Число "1" старшей позиции записывается в массив выдачи с весом позиции тысяча, а 2 - в массив выдачи с весом сотни, и программа переходит к сложению чисел с кодом веса тысячи. Читают числа с кодом веса тысяча, метят, опрашивают таблицу сложения от 0-9, читают результат и заносят на блок сдвига старшую позицию результата, если она есть, записывают в свободную строку с кодом веса на 1 больше, а младшая остается в блоке сдвига. Затем опрашиваются числа с весом тысяча. Числа с такой позицией есть. Заносят следующее число на блок сдвига. Метят эту строку, затем опрашивают таблицу сложения. Результат операции сложения заносят в блок сдвига, если в результате сложения появляется старшая позиция, записывают ее в свободную ячейку с кодом веса позиции на 1 больше и снова опрашивается входной массив, есть ли числа с позицией тысяча. В данном примере чисел с кодом позиции тысяча больше нет. Результат в данном случае 3 записывается в массив выдачи с кодом веса позиции тысяча и т.д.

В подпрограммах умножения, деления, извлечения квадратного корня и других требуется переходить от одной подпрограммы к другой и вернуться к данному продолжению. В блок сдвига заносится метка новой подпрограммы, а в свободную ячейку, например с меткой "100", записывается метка подпрограммы или ветви подпрограммы, на которую необходимо вернуться. Сбрасываются триггеры 48 и 58, информация с блока сдвига подается на информационные шины, а блок 8 управления вырабатывает сигнал опроса по шине 18 и сигнал выборка-1 (Вбр-1) по ЕИ1, равный 1, так как все триггеры 48 в сброшенном состоянии. При совпадении информации, занесенной в блок сдвига, и информации в строках матрицы АЗУ, триггеры 48 блоков 3 управления установятся в единичное состояние. На шине ЕИ1 (16) установится нулевой уровень, который переводит АП в режим чтения новой подпрограммы. По окончании работы новой подпрограммы читается ячейка с меткой "100". Эту метку заносят в блок сдвига и опрашивают содержимое АЗУ по этой метке, являющейся меткой возврата. Для прерывания или перевода на другой режим, или на другую подпрограмму, используются сигналы на управляющих шинах 14р и 4р, шине 30 "Управление внешнее" и внешние управляющие шины, с выхода 20 блока управления выдается сигнал блокировки, на шины 32 и 30 подается единичный уровень, который переводит АЗУ на управление от внешних сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вероятностная вычислительная машина | 1986 |

|

SU1455344A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2037892C1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2045787C1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| СПОСОБ И МНОГОФУНКЦИОНАЛЬНОЕ АССОЦИАТИВНОЕ МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ ОБРАБОТКИ СТРОКОВЫХ ДАННЫХ И РЕШЕНИЯ ЗАДАЧ РАСПОЗНАВАНИЯ ОБРАЗОВ | 2014 |

|

RU2582053C2 |

| Устройство для определения характеристик связности ориентированного графа | 1983 |

|

SU1133596A1 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА | 1999 |

|

RU2168216C2 |

| АССОЦИАТИВНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА МАСКИРОВАННОГО ПОИСКА ВХОЖДЕНИЙ | 2010 |

|

RU2469425C2 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1824650A1 |

| СПОСОБ ПАРАЛЛЕЛЬНОГО ПОИСКА И ЗАМЕНЫ СТРОКИ И ОДНОРОДНАЯ ЗАПОМИНАЮЩАЯ МАТРИЦА ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2012 |

|

RU2509383C2 |

Изобретение относится к вычислительной технике и может быть использовано как самостоятельный ассоциативный процессор и как составной элемент матричных ассоциативных вычислительных машин. Целью изобретения является расширение функциональных возможностей за счет использования систем счисления по любому модулю основания. Цель достигается тем, что ассоциативный процессор содержит ассоциативную матрицу памяти, содержащую матрицу размером их n m триггеров, первую, вторую и третью матрицы размером n m каждая элементов И, матрицу размером n m элементов сравнения, первую и вторую группы из n блоков управления каждая, блок сдвига, регистр маски, блок управления и блок ввода-вывода. 3 з.п. ф-лы, 4 табл., 7 ил.

| Патент ФРГ N 3216905, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1994-12-30—Публикация

1988-01-04—Подача