Изобретение относится к вычисли- тельной технике и может быть использовано при построении высокопроизводительных вычислительных систем (ВС) в качестве средства для сопряжения центрального процессора (ЦП) с арифметическими процессорами (АП).

Цель изобретения - повьшение быстродействия работы ВС за счет обеспечения переполнения вычислительных операций с программных на аппаратные средства и наоб орот.

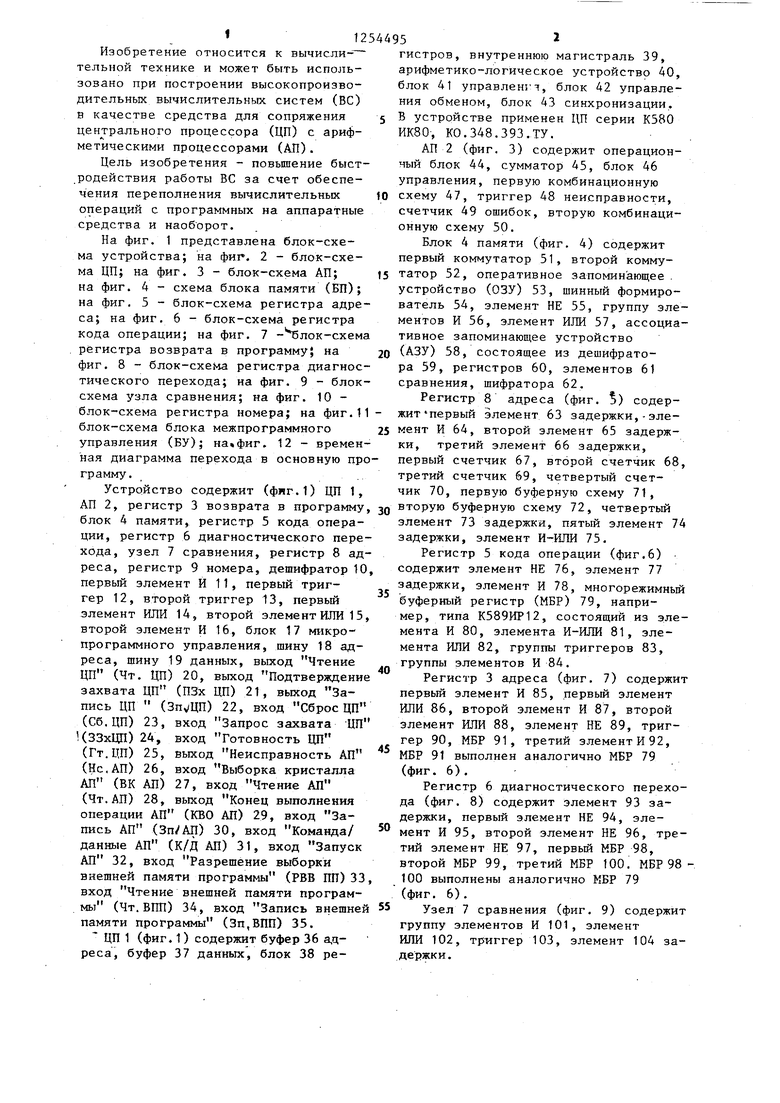

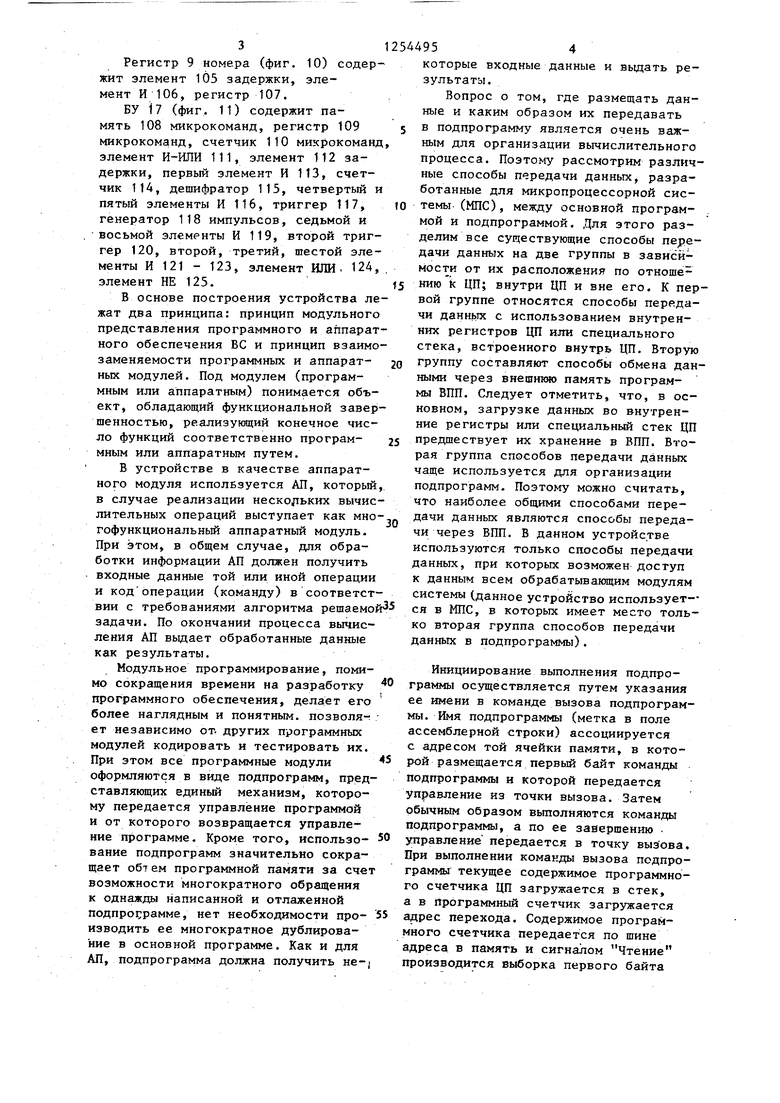

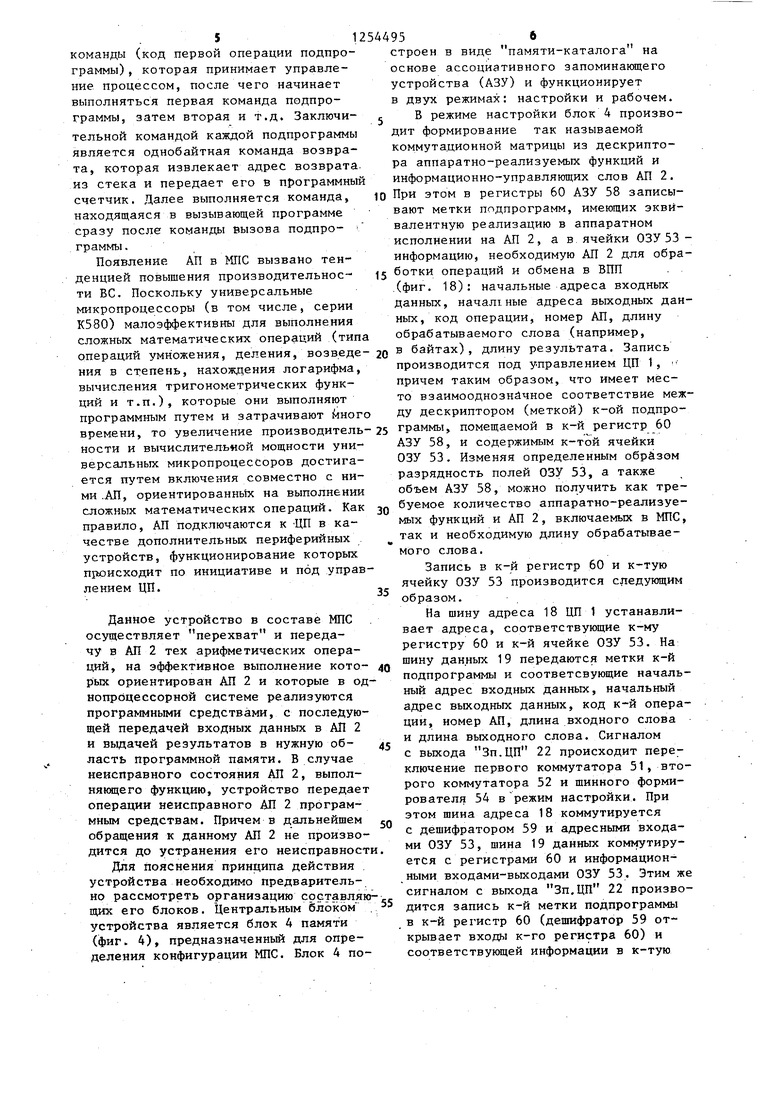

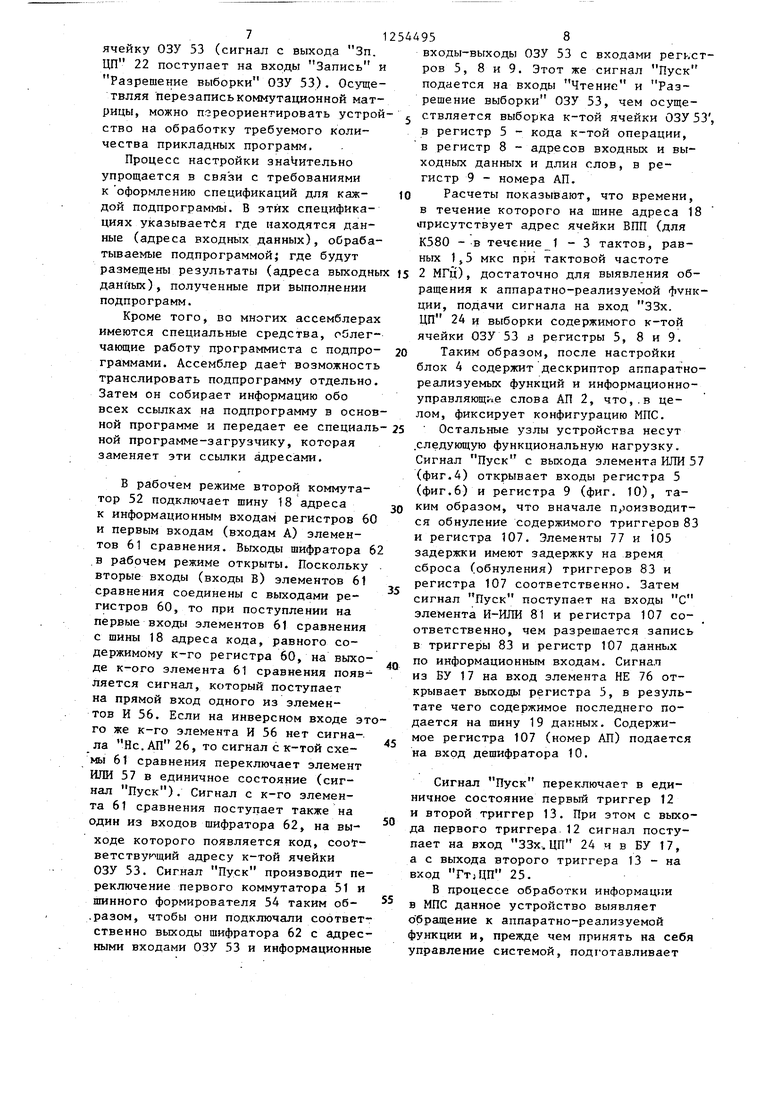

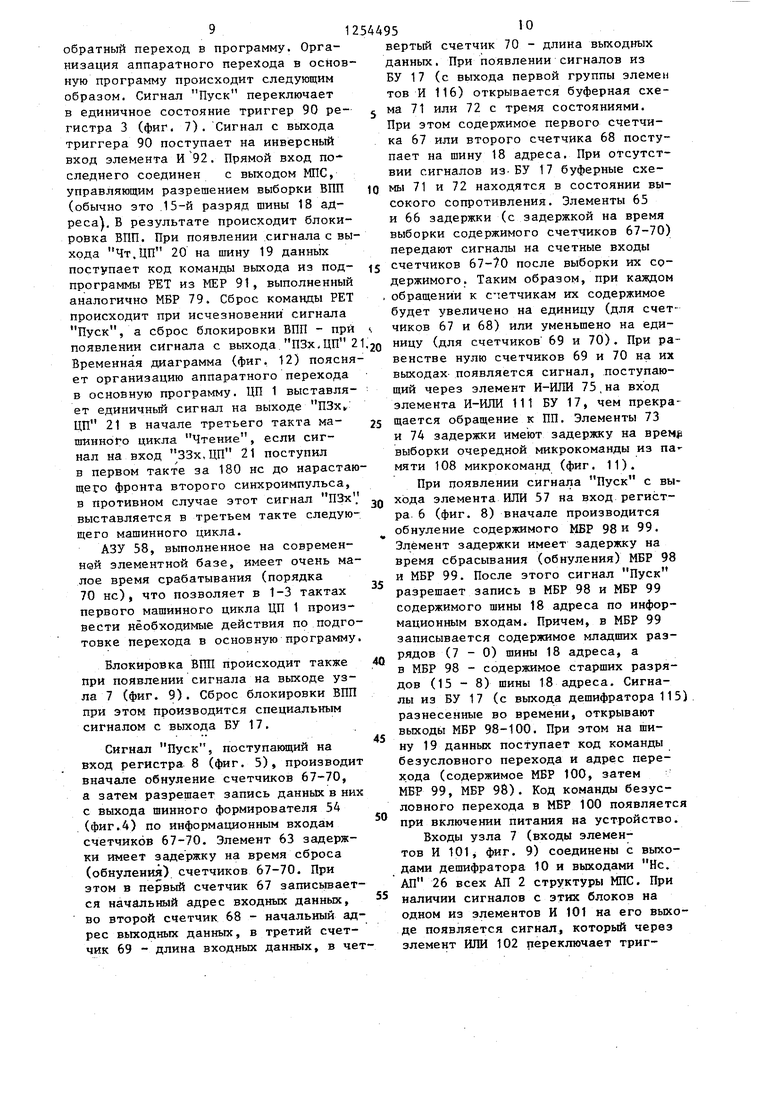

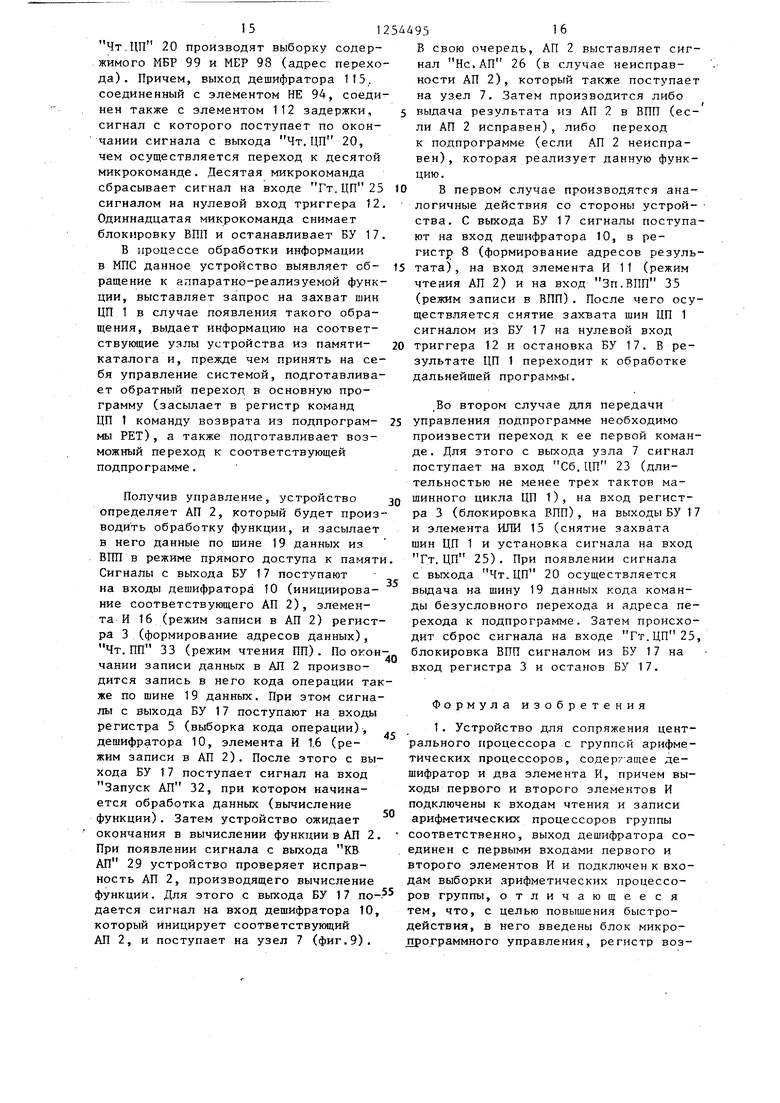

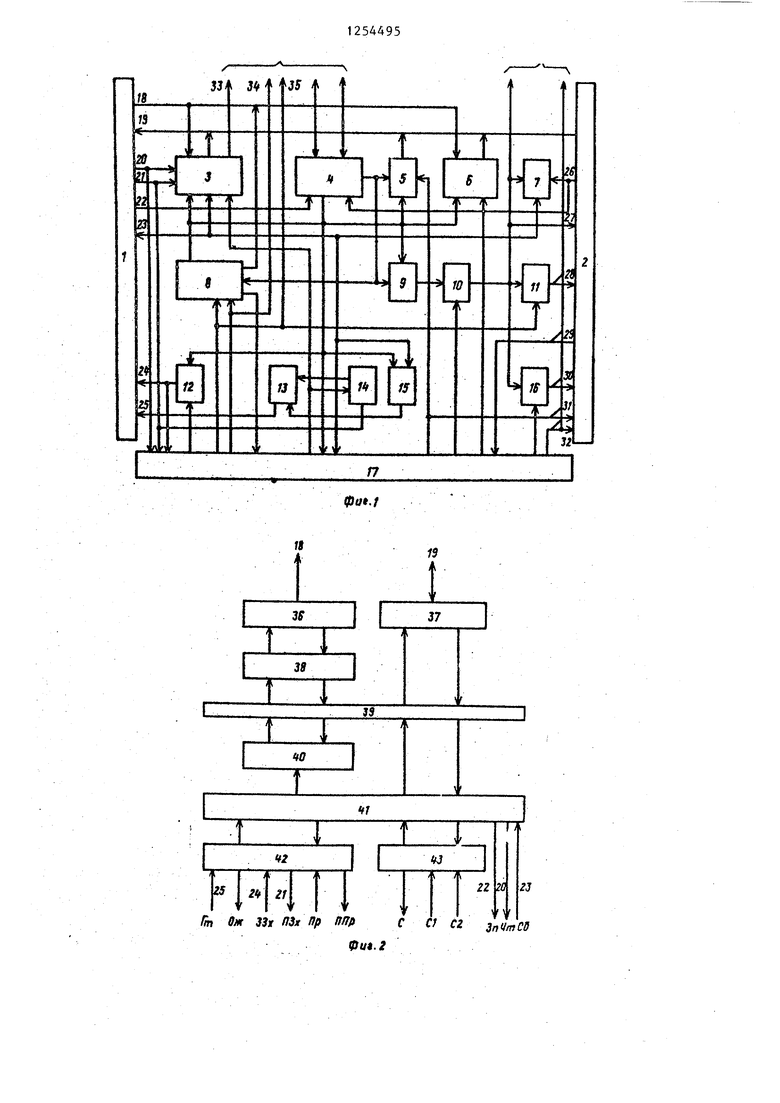

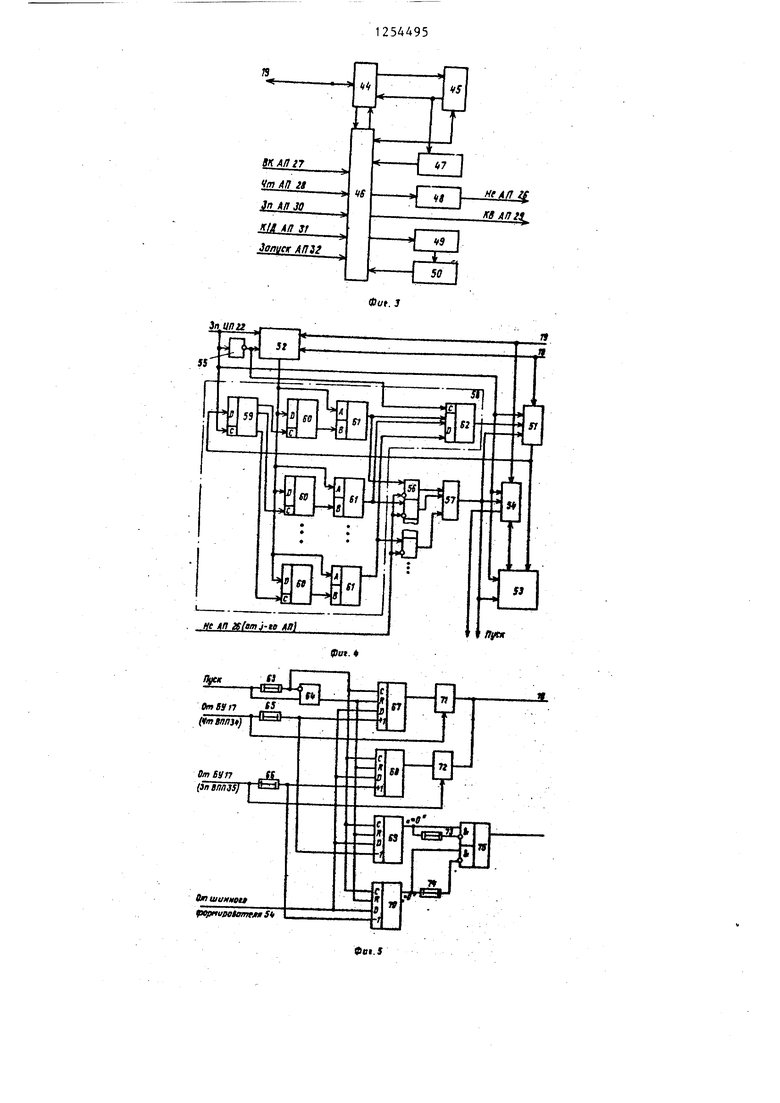

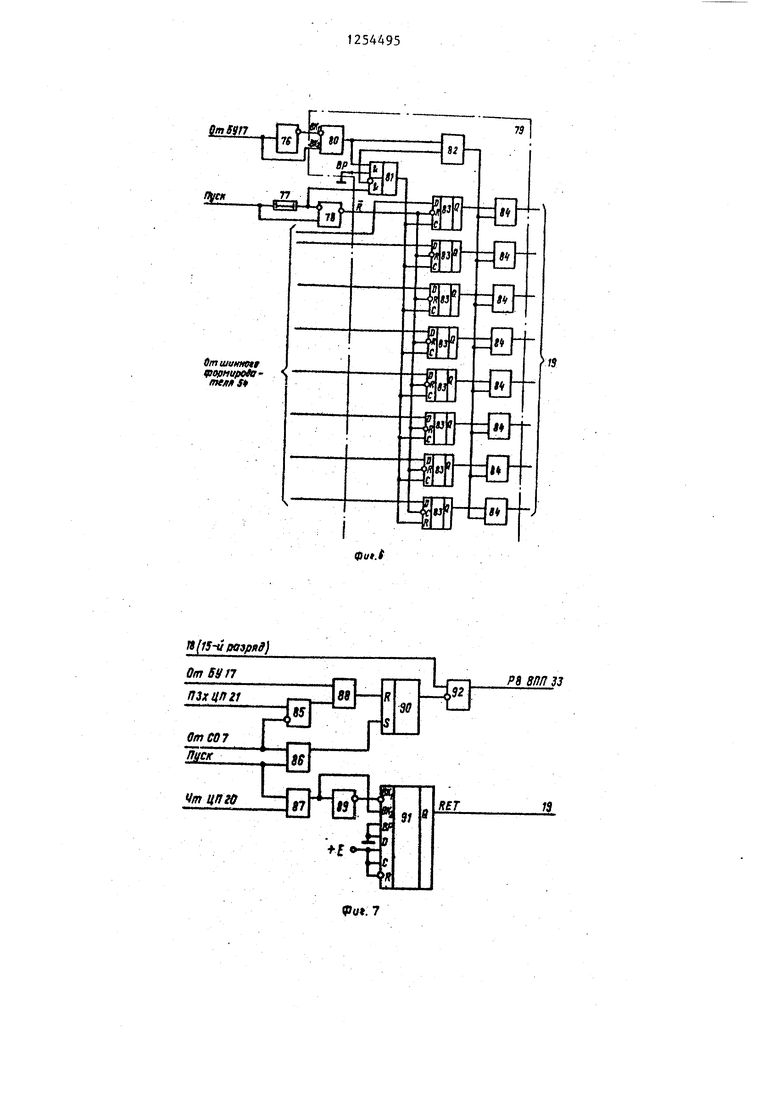

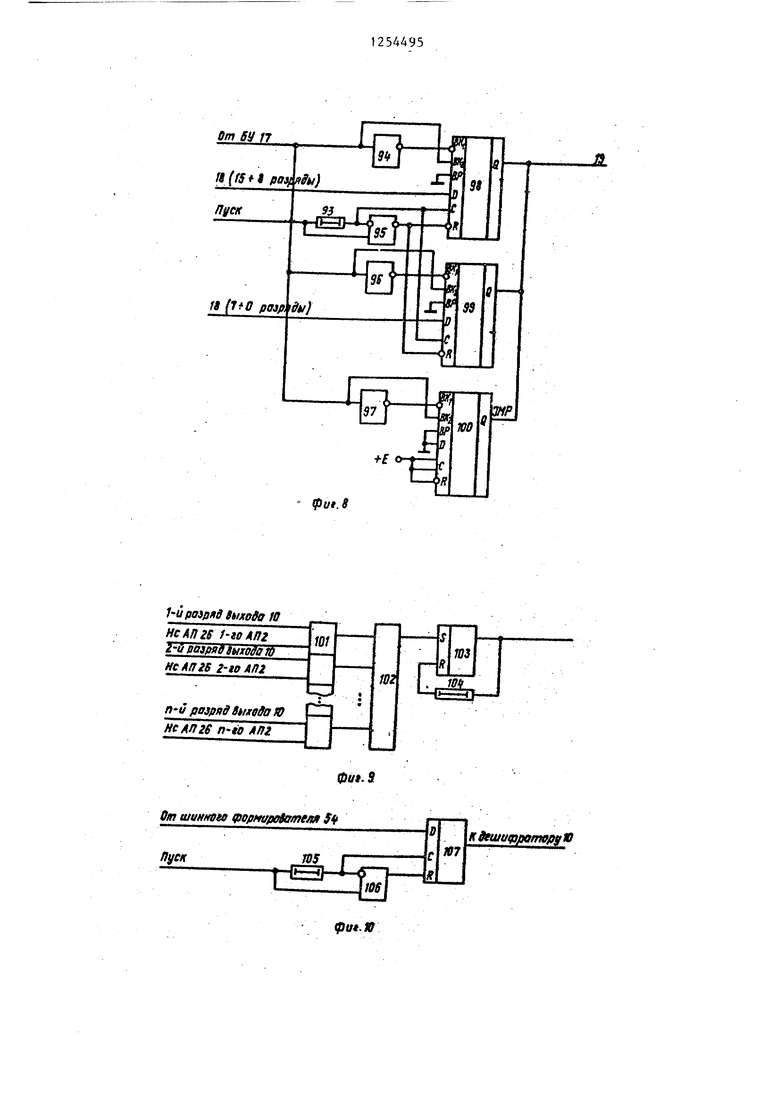

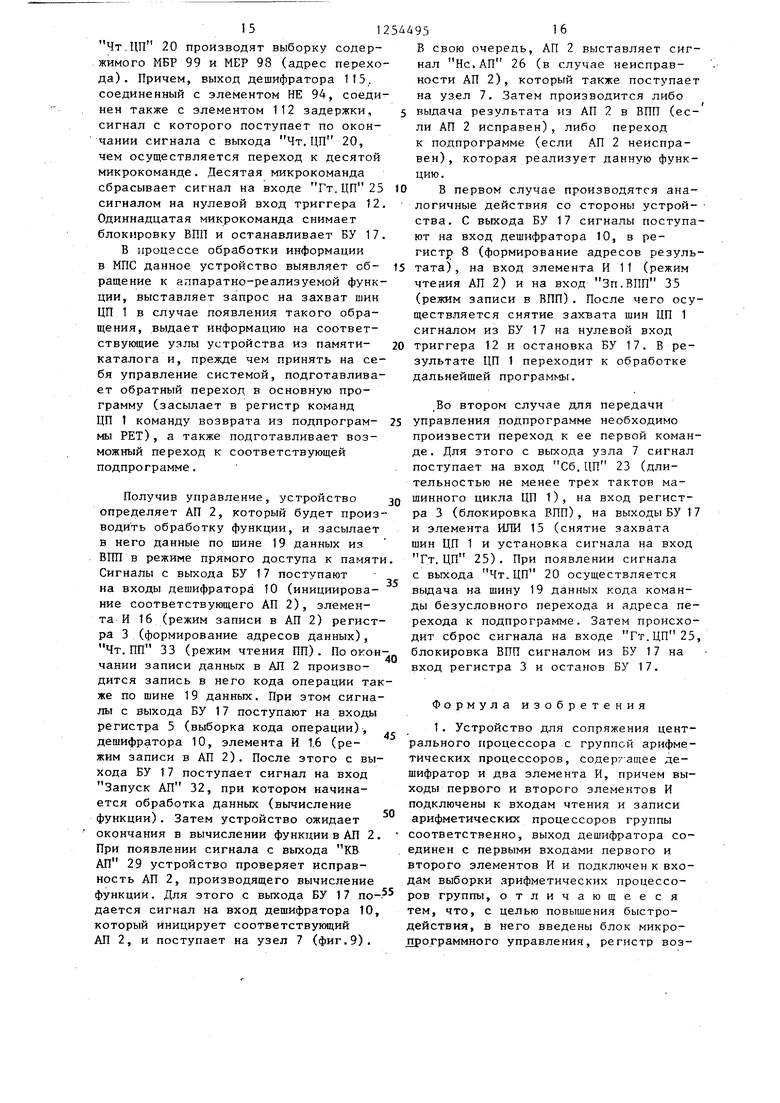

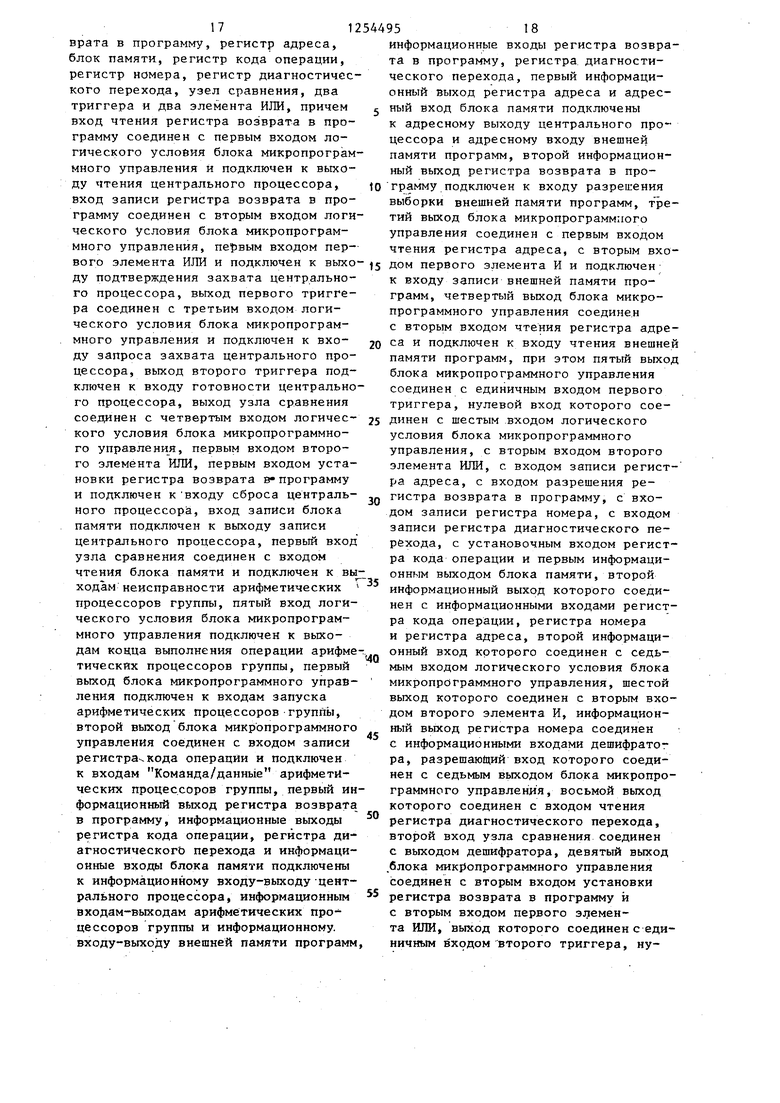

Иа фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема ЦП; на фиг. 3 - блок-схема АП; на фиг. 4 - схема блока памяти (Ш1); на фиг, 5 - блок-схема регистра адреса; на фиг. 6 - блок-схема регистра кода операции; на фиг. 7 - блок-схема регистра возврата в программу} на фиг. 8 - блок-схема регистра диагностического перехода; на фиг. 9 - блок- схема узла сравнения; на фиг. 10 - блок-схема регистра номера; на фиг.11 блок-схема блока межпрограммного управления (БУ); . 12 - временная диаграмма перехода в основную программу... Устройство содержит (фнг.1) ЦП 1, АП 2, регистр 3 возврата в программу блок 4 памяти, регистр 5 кода операции, регистр 6 диагностического перехода, узел 7 сравнения, регистр 8 адреса, регистр 9 номера, дешифратор 10 первый элемент И 11, первый триггер 12, второй триггер 13, первый элемент ИЛИ 14, второй элемент ИЛИ 15 второй элемент И 16, блок 17 микропрограммного управления, шину 18 адреса, шину 19 данных, выход Чтение ЦП (Чт. ЦП) 20, выход Подтверждение захвата ЦП (ПЗх ЦП) 21, вькод Запись ЦП (Зпv ЦП) 22, вход Сброс ЦП (Сб. ЦП) 23, вход Запрос захвата ЦП вход Готовность ЦП

КЗЗхЦП) 24,

(Гт.ЦП) 25, выход Неисправность АП (Нс.АП) 26, вход Выборка кристалла АП (ВК АЛ) 27, вход Чтение АП (Чт.АП) 28, выход Конец выполнения операции АП (КВО АИ) 29, вход Запись АП (Зп/АП) 30, вход Команда/ данные АП (К/Д АП) 31, вход Запуск АП 32, вход Разрешение выборки внешней памяти программы (РВВ ШТ)33 вход Чтение внешней памяти программы (Чт. ВПП) 34, вход Запись внешней памяти программы (Зп,ВПП) 35.

ЦП 1 (фиг. 1) содержит буфер 36 а,ц- реса, буфер 37 данных, блок 38 ре

о

гистров, внутреннюю магистраль 39, арифметико-логическое устройство 40, блок 41 управленп, блок 42 управления обменом, блок 43 синхронизации. В устройстве применен ЦП серии К580 ИК80, КО.348.393.ТУ.

АП 2 (фиг. 3) содержит операционный блок 44, сумматор 45, блок 46 управления, первую комбинационную схему 47, триггер 48 неисправности, счетчик 49 ошибок, вторую комбинационную схему 50.

Блок 4 памяти (фиг. 4) содержит первый коммутатор 51, второй комму- 5 татор 52, оперативное запоминающее . устройство (ОЗУ) 53, шинный формирователь 54, элемент НЕ 55, группу элементов И 56, элемент ИЛИ 57, ассоциативное запоминающее устройство 0 (АЗУ) 58, состоящее из дешифратора 59, регистров 60, элементов 61 сравнения, шифратора 62.

Регистр 8 адреса (фиг. S) содержит первый элемент 63 задержки,эле- 5 мент И 64, второй элемент 65 задержки, третий элемент 66 задержки, первый счетчик 67, второй счетчик 68, третий счетчик 69, четвертый счетчик 70, первую буферную схему 71, вторую буферную схему 72, четвертый элемент 73 задержки, пятый элемент 74 задержки, элемент И-ИЛИ 75.

Регистр 5 кода операции (фиг.6) содержит элемент НЕ 76, элемент 77 задержки, элемент И 78, многорежимньй буферный регистр (МБР) 79, например, типа К589ИР12, состоящий из элемента И 80, элемента И-ИЛИ 81, элемента ИЛИ 82, группы триггеров 83, группы элементов И 84.

Регистр 3 адреса (фиг. 7) содержит первый элемент И 85, первый элемент ИЛИ 86, второй элемент И 87, второй элемент ИЛИ 88, элемент НЕ 89, триггер 90, МБР 91, третий элемент И 92, МБР 91 выполнен аналогично МБР 79 (фиг. 6).

Регистр 6 диагностического перехода (фиг. 8) содержит элемент 93 задержки, первый элемент НЕ 94, эле- мент И 95, второй элемент НЕ 96, третий элемент НЕ 97, первый МБР 98, второй МБР 99, третий МБР 100. МБР 98- 100 выполнены аналогично МБР 79 (фиг. 6).

55 Узел 7 сравнения (фиг. 9) содержит группу элементов И 101, элемент ИЛИ 102, триггер 103, элемент 104 задержки.

5

0

5

Регистр 9 номера (фиг. 10) содержит элемент 105 задержки, элемент И 106, регистр 107.

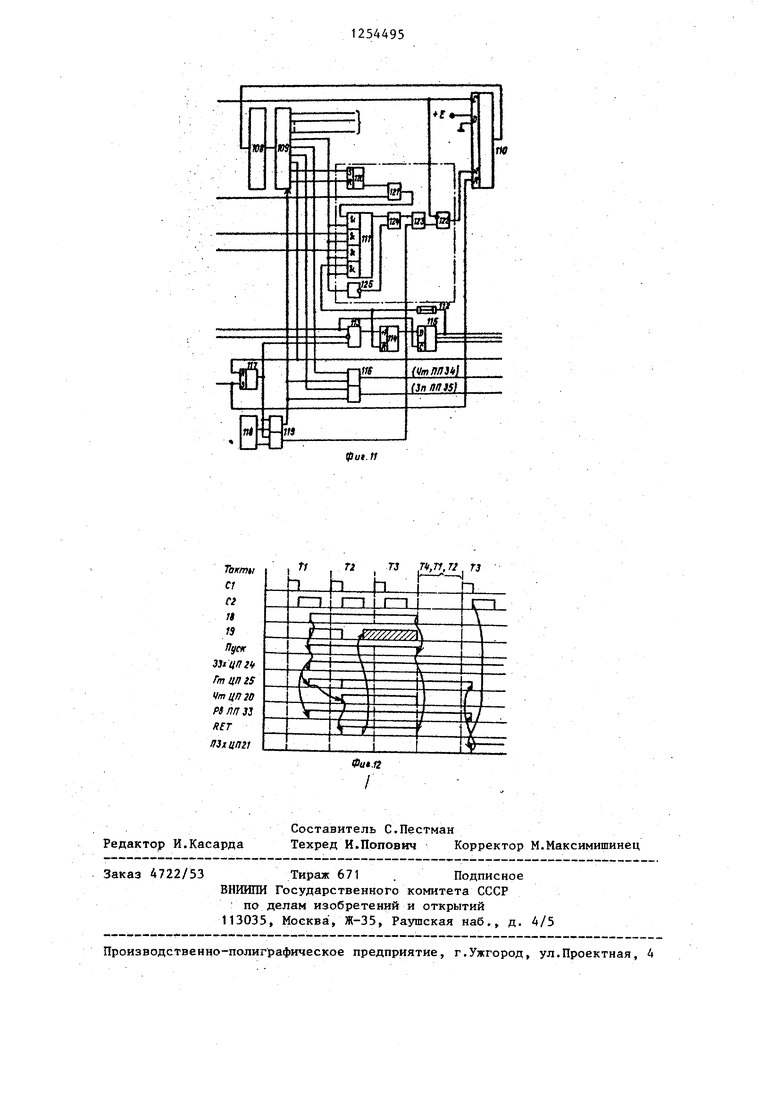

БУ 17 (фиг. 11) содержит память 108 микрокоманд, регистр 109 микрокоманд, счетчик 110 микрокоманд элемент И-ИЛИ 111, элемент 112 задержки, первый элемент И 113, счетчик 114, дешифратор 115, четвертый и пятый элементы И 116, триггер 117, генератор 118 импульсов, седьмой и восьмой элементы И 119, второй триггер 120, второй, третий, тестой элементы И 121 - 123, элемент ШШ. 124, элемент НЕ 125.

В основе построения устройства лежат два принципа: принцип модульного представления программного и аппаратного обеспечения БС и принцип взаимозаменяемости программных и аппарат- ных модулей. Под модулем (программным или аппаратным) понимается объект, обладающий функциональной завершенностью, реализующий конечное число функций соответственно програм- мным или аппаратным путем.

В устройстве в качестве аппаратного модуля исполБзуется АЛ, который, в случае реализации нескольких вычислительных операций выступает как мно

гофункциональный аппаратный модуль. При этом, в общем случае, для обработки информации АП должен получить входные данные той или иной операции и код операции (команду) в соответствии с требованиями алгоритма решаемо задачи. По окончаний процесса вычисления АП выдает обработанные данные как результаты.

Модульное программирование, помимо сокращения времени на разработку программного обеспечения, делает его более наглядным и понятным, позволя- ет независимо от- других программных модулей кодировать и тестировать их. При этом все программные модули оформляются в виде подпрограмм, представляющих единый механизм, которому передается управление программой и от которого возвращается управление программе. Кроме того, использование подпрограмм значительно сокращает обтем программной памяти за счет возможности многократного обращения к однажды написанной и отлаженной подпрог:рамме, нет необходимости про- изводить ее многократное дублирование в основной программе. Как и для АП, подпрограмма должна получить не-(

5 fO t5

2025

30

0

5

5

0

которые входные данные и выдать результаты.

Вопрос о том, где размещать данные и каким образом их передавать в подпрограмму является очень важным для организации вычислительного процесса. Поэтому рассмотрим различные способы передачи данных, разработанные для микропроцессорной системы (МПС), между основной программой и подпрограммой. Для этого разделим все существующие способы передачи даннь1х на две группы в зависимости от их расположения по отношению ic ЦП; внутри ЦП и вне его. К первой группе относятся способы передачи данньтх с использованием внутренних регистров ЦП или специального стека, встроенного внутрь ЦП. Вторую группу составляют способы обмена данными через внешнюю память программы ВПП. Следует отметить, что, в основном, загрузке данных во внутренние регистры или специальный стек ЦП предществует их хранение в ВПП. Вторая группа способов передачи данных чаще используется для организации подпрограмм. Поэтому можно считать, что наиболее общими способами передачи данных являются способы передачи через ВПП. В данном устройстве используются только способы передачи данных, при которых возможен доступ к данным всем обрабатывающим модулям системы (данное устройство используется в МПС, в которых имеет место только вторая группа способов передачи данных в подпрограммы).

Инициирование вьшолнения подпрограммы осуществляется путем указания ее имени в команде вызова подпрограммы. подпрограммы (метка в поле ассемблерной строки) ассоциируется с адресом той ячейки памяти, в которой размещается первый байт команды подггрограммы и которой передается управление из точки вызова. Затем обычным образом вьтолняются команды подпрограммы, а по ее завершению . управление передается в точку выз ова. При выполнении команды вызова подпрограммы текущее содержимое программного счетчика ЦП загружается в стек, а в программный счетчик загружается адрес перехода. Содержимое программного счетчика передается по шине адреса в память и сигналом Чтение производится выборка первого байта

команды (код первой операции подпрограммы) , которая принимает управление процессом, после чего начинает выполняться первая команда подпрограммы, затем вторая и т.д. Заключительной командой каждой подпрограммы является однобайтная команда возврата, которая извлекает адрес возврата, из стека и передает его в программный счетчик. Далее выполняется команда, находящаяся в вызывающей программе сразу после команды вызова подпро- ,граммы.

Появление АП в МПС вызвано тенденцией повышения производительности ВС. Поскольку универсальные микропроцессоры (в том числе, серии К580) малоэффективны для выполнения сложных математических операций (типа

строен в виде памяти-каталога на основе ассоциативного запоминающего устройства (АЗУ) и функционирует в двух режимах: настройки и рабочем.

J В режиме настройки блок 4 произво дит формирование так называемой коммутационной матрицы из дескриптора аппаратно-реализуемых функций и информационно-управляющих слов АП 2.

10 При этом в регистры 60 АЗУ 58 записы вают метки подпрограмм, имеющих экви валентную реализацию в аппаратном исполнении на АП 2, а в ячейки ОЗУ 53 информацию, необходимую АЛ 2 для обр

5 ботки операций и обмена в ВПП

.(фиг. 18): начальные адреса входных данных, начальные адреса вькодных да ных, код операции, номер АП, длину обрабатываемого слова (например.

операций умножения, деления, возведе- 20 байтах), длину результата. Запись ния в степень, нахождения логарифма, производится под управлением ЦП 1,

вычисления тригонометрических функций и т.п.), которые они выполняют программным путем и затрачивают iiHoro времени, то увеличение производитель- ности и вычислительной мощности универсальных микропроцессоров достигается путем включения совместно с ними .АП, ориентированнь1х на выполнении сложных математических операций. Как правило, АП подключаются к ЦП в качестве дополнительных периферийных устройств, функционирование которых происходит по инициативе и под управлением ЦП.

Данное устройство в составе МПС осуществляет перехват и передачу в АП 2 тех арифметических операций, на эффективное выполнение которых ориентирован АП 2 и которые в однопроцессорной системе реализуются программными средствами, с последующей передачей входных данных в АП 2 и вьщачей результатов в нужную область программной памяти. В случае неисправного состояния АП 2, выполняющего функцию, устройство передает операции неисправного .АП 2 программным средствам. Причем в дальнейшем обращения к данному АП 2 не производится до устранения его неисправности

Для пояснения принципа действия устройства необходимо предварительно рассмотреть организацию составляющих его блоков. Центральным блоком . устройства является блок 4 памяти (фиг. 4), предназначенный для определения конфигурации МПС. Блок 4 построен в виде памяти-каталога на основе ассоциативного запоминающего устройства (АЗУ) и функционирует в двух режимах: настройки и рабочем.

J В режиме настройки блок 4 производит формирование так называемой коммутационной матрицы из дескриптора аппаратно-реализуемых функций и информационно-управляющих слов АП 2.

10 При этом в регистры 60 АЗУ 58 записывают метки подпрограмм, имеющих эквивалентную реализацию в аппаратном исполнении на АП 2, а в ячейки ОЗУ 53- информацию, необходимую АЛ 2 для обра 5 ботки операций и обмена в ВПП

.(фиг. 18): начальные адреса входных данных, начальные адреса вькодных данных, код операции, номер АП, длину обрабатываемого слова (например.

причем таким образом, что имеет место взаимооднозначное соответствие между дескриптором (меткой) к-ой подпрограммы, помещаемой в к-й регистр 60 АЗУ 58, и содержимым к-той ячейки ОЗУ 53. Изменяя определенным образом разрядность полей ОЗУ 53, а также объем АЗУ 58, можно получить как требуемое количество аппаратно-реализуемых функций и АП 2, включаемых в МПС, так и необходимую длину обрабатываемого слова.

Запись в к-й регистр 60 и к-тую ячейку ОЗУ 53 производится следующим образом.

На шину адреса 18 ЦП 1 устанавливает адреса, соответствующие к-му регистру 60 и к-й ячейке ОЗУ 53. На шину данных 19 передаются метки к-й подпрограммы и соответсвующие начальный адрес входных данньпс, начальный адрес выходных данных, код к-й операции, номер АП, длина входного слова и длина выходного слова. Сигналом с выхода Зп.ЦП 22 происходит переключение первого коммутатора 51, второго коммутатора 52 и шинного формирователя 54 в режим настройки. При этом шина адреса 18 коммутируется с дешифратором 59 и адресными входами ОЗУ 53, шина 19 данных коммутируется с регистрами 60 и информационными входами-выходами ОЗУ 53. Этим же сигналом с выхода Зп.ЦП 22 производится запись к-й метки подпрограммы в к-й регистр 60 (депгафратор 59 открывает входы к-го регистра 60) и соответствующей информации в к-тую

ячейку ОЗУ 53 (сигнал с выхода Зп. ЦП 22 поступает на входы Запись и Разрешение выборки ОЗУ 53). Осуще- твляя перезапись коммутационной матрицы, можно пзреориентировать устройство на обработку требуемого количества прикладных программ.

Процесс настройки зна11ительно упрощается в связи с требованиями к оформлению спецификаций для каждой подпрограммы. В этих спецификациях указывается где находятся данные (адреса входных данных), обрабатываемые подпрограммой; где будут

размещены результаты (адреса выходных fs 2 МГц), достаточно для выявления обданНых), полученные при выполнении подпрограмм.

Кроме того, во многих ассемблерах имеются специальные средства, облегчающие работу программиста с подпро- граммами. Ассемблер дает возможность транслировать подпрограмму отдельно. Затем он собирает информацию обо всех ссылках на подпрограмму в основной программе и передает ее специаль- ной программе-загрузчику, которая заменяет эти ссылки адресами.

В рабочем режиме второй коммутатор 52 подключает шину 18 адреса к информационным входам регистров 60 и первым входам (входам А) элементов 61 сравнения. Выходы шифратора 6 .в рабочем режиме открыты. Поскольку вторые входы (входы В) элементов 61 сравнения соединены с выходами регистров 60, то при поступлении на первые входы элементов 61 сравнения с шины 18 адреса кода, равного содержимому к-го регистра 60, на выходе к-ого элемента 61 сравнения появляется сигнал, который поступает на прямой вход одного из элементов И 56. Если на инверсном входе этго же к-го элемента И 56 нет сигнала Не. АП 26, то сигнал с к-той схемы 61 сравнения переключает элемент ШШ 57 в единичное состояние (сигнал Пуск). Сигнал с к-го элемента 61 сравнения поступает также на один из входов шифратора 62, на выходе которого появляется код, соот- ветствук1щий адресу к-той ячейки ОЗУ 53. Сигнал Пуск производит переключение первого коммутатора 51 и шинного формирователя 54 таким об- .разом, чтобы они подключаши соответственно выходы шифратора 62 с адресными входами ОЗУ 53 и информационные

2544958

входы-выходы ОЗУ 53 с входами регьст- ров 5, 8 и 9. Этот же сигнал Пуск подается на входы Чтение и Разрешение выборки ОЗУ 53, чем осуще- 5 ствляется выборка к-той ячейки ОЗУ 53, в регистр 5 - кода к-той операции, в регистр 8 - адресов входных и выходных данных и длин слов, в регистр 9 - номера АП.

to Расчеты показывают, что времени, в течение которого на шине адреса 18 присутствует адрес ячейки ВПП (для К580 - в течение 1 - 3 тактов, равных 1,5 МКС при тактовой частоте

20 5

0

5

0

5

0

ращения к аппаратно-реализуемой функции, подачи сигнала на вход ЗЗх. ЦП 24 и выборки содержимого к-той ячейки ОЗУ 53 а регистры 5, 8 и 9. Таким образом, после настройки блок 4 содержит дескриптор аппаратно- реализуемьк функций и информационно- управляющ слова АП 2, что,.в целом, фиксирует конфигурацию МПС.

Остальные узлы устройства несут .следующую функциональную нагрузку. Сигнал Пуск с выхода элементаРШИ 57 (фиг.4) открывает входы регистра 5 (фиг.6) и регистра 9 (фиг. 10), таким образом, что вначале производится обнуление содержимого триггеров 83 и регистра 107. Элементы 77 и 105 задержки имеют задержку на время сброса (обнуления) триггеров 83 и регистра 107 соответственно. Затем сигнал Пуск поступает на входы С элемента И-ИЛИ 81 и регистра 107 соответственно, чем разрешается запись в триггеры 83 и регистр 107 данных по информационным входам. Сигнал из БУ 17 на вход элемента НЕ 76 открывает выходы регистра 5, в результате чего соде ржимое последнего подается на шину 19 данных. Содержимое регистра 107 (номер АП) подается на вход дешифратора 10.

Сигнал Пуск переключает в единичное состояние первый триггер 12 и второй триггер 13. При этом с выхода первого триггера 12 сигнал поступает на вход ЗЗх, ЦП 24 и в БУ 17, а с выхода второго триггера 13 - на вход ГТ}1ДП 25.

В процессе обработки информации в МПС данное устройство выявляет о бращение к аппаратно-реализуемой функции и, прежде чем принять на себя управление системой, подготавливает

обратный переход в программу. Организация аппаратного перехода в основную программу происходит следующим образом. Сигнал Пуск переключает в единичное состояние триггер 90 регистра 3 (фиг. 7). Сигнал с выхода триггера 90 поступает на инверсный вход элемента И 92. Прямой вход последнего соединен с выходом МПС, управляющим разрешением выборки ВПП (обычно это .15-й разряд шины 18 адреса), В результате происходит блокировка ВПП. При появлении сигнала с выхода Чт.ЦП 20 на шину 19 даннь1х

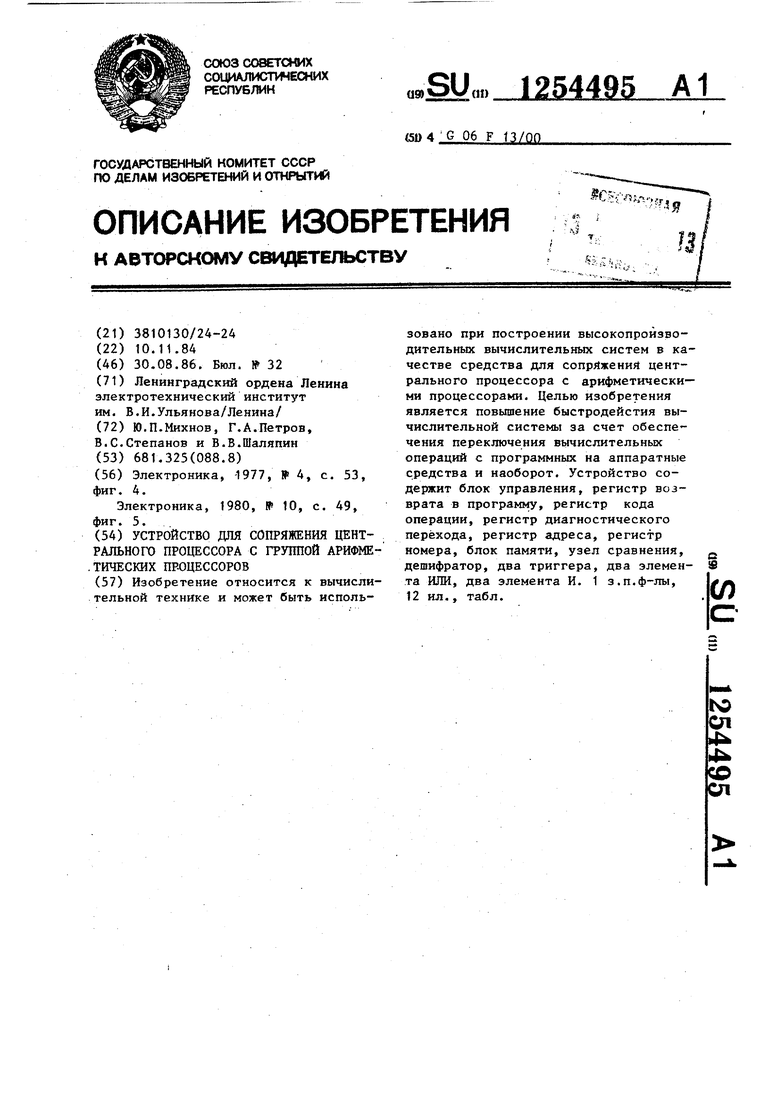

15 счетчиков 67-70 после выборки их содержимого. Таким образом, при каждом . обращении к счетчикам их содержимое будет увеличено на единицу (для счет(, чиков 67 и 68) или уменьшено на едипоступает код команды выхода из подпрограммы PET из МЕР 91, выполненный аналогично МБР 79. Сброс команды PET происходит при исчезновении сигнала Пуск, а сброс блокировки ВПП - при появлении сигнала с выхода П3х ЦП 21,2Q ницу (для счетчиков 69 и 70). При ра- Временная диаграмма (фиг. 12) поясня- венстве нулю счетчиков 69 и 70 на их ет организацию аппаратного перехода выходах появляется сигнал, поступаю- в основную программу. ЦП 1 выставля- щий через элемент И-ИЛИ 75, на вх од ет единичньш сигнал на выходе П3х элемента И-ШШ 111 БУ 17, чем прекра25 щается обращение к ПП. Элементы 73

ЦП 21 в начале третьего такта машинного цикла Чтение, если сигнал на вход ЗЗх,ЦП 21 поступил в первом такте за 180 не до нарастающего фронта второго синхроимпульса, в противном случае этот сигнал ПЗх . выставляется в третьем такте следующего машинного цикла.

АЗУ 58, выполненное на современней элементной базе, имеет очень малое время срабатывания (порядка 70 не), что позволяет в 1-3 тактах первого машинного цикла ЦП 1 произвести необходимые действия по подготовке перехода в основную программу.

Блокировка ВПП происходит также при появлении сигнала на выходе узла 7 (фиг. 9). Сброс блокировки ВПП при этом производится специальным сигналом с выхода БУ 17.

Сигнал Пуск, поступающий на вход регистра 8 (фиг. 5), производит вначале обнуление счетчиков 67-70, а затем разрешает запись данных в них с выхода шинного формирователя 54 (фиг.4) по информационным входам счетчиков 67-70. Элемент 63 задержки имеет задержку на время сброса (обнуления) счетчиков 67-70. При этом в первый счетчик 67 записьшает- ся начальный адрес входных данных, во второй счетчик 68 - начальный адрес выходных данных, в третий счетчик 69 - длина входных данных, в чет35

40

И 74 задержки имеют задержку на врем выборки очередной микрокоманды из па мяти 108 микрокоманд (фиг. 11).

При появлении сигнала Пуск с вы3Q хода элемента ИЛИ 57 на вход регистра 6 (фиг. 8) вначале производится обнуление содержимого МБР 98 и 99. Элемент задержки имеет задержку на время сбрасывания (обнуления) МБР 98 и МБР 99. После этого сигнал Пуск разрешает запись в МБР 98 и МБР 99 содержимого шины 18 адреса по информационным входам. Причем, в МБР 99 записывается содержимое младших разрядов (7 - 0) шины 18 адреса, а в МБР 98 - содержимое старших разрядов (15 - 8) шины 18 адреса. Сигналы из БУ 17 (с выхода дешифратора 115) разнесенные во времени, открывают выходы МБР 98-100. При этом на шину 19 данных поступает код команды безусловного перехода и адрес пере- х.ода (содержимое МБР 100, затем МБР 99, МБР 98). Код команды безусловного перехода в МБР 100 появляется при включении питания на устройство.

Входы узла 7 (входы элементов И 101, фиг. 9) соединены с выходами дешифратора 10 и выходами Не. АП 26 всех АП 2 структуры МПС. При

55 наличии сигналов с этих блоков на

одном из элементов И 101 на его выходе появляется сигнал, который через элемент ИЛИ 102 переключает триг45

50

вертый счетчик 70 - длина выходных данных. При появлении сигналов из БУ 17 (с выхода первой группы элемен тов И 116) открывается буферная схема 71 или 72 с тремя состояниями. При этом содержимое первого счетчика 67 или второго счетчика 68 поступает на шину 18 адреса. При отсутствии сигналов из- БУ 17 буферные схемы 71 и 72 находятся в состоянии высокого сопротивления. Элементы 65 и 66 задержки (с задержкой на время выборки содержимого счетчиков 67-70) передают сигналы на счетные входы

счетчиков 67-70 после выборки их содержимого. Таким образом, при каждом обращении к счетчикам их содержимое будет увеличено на единицу (для счетчиков 67 и 68) или уменьшено на единицу (для счетчиков 69 и 70). При ра- венстве нулю счетчиков 69 и 70 на их выходах появляется сигнал, поступаю- щий через элемент И-ИЛИ 75, на вх од элемента И-ШШ 111 БУ 17, чем прекра

И 74 задержки имеют задержку на врем выборки очередной микрокоманды из па мяти 108 микрокоманд (фиг. 11).

При появлении сигнала Пуск с выхода элемента ИЛИ 57 на вход регистра 6 (фиг. 8) вначале производится обнуление содержимого МБР 98 и 99. Элемент задержки имеет задержку на время сбрасывания (обнуления) МБР 98 и МБР 99. После этого сигнал Пуск разрешает запись в МБР 98 и МБР 99 содержимого шины 18 адреса по информационным входам. Причем, в МБР 99 записывается содержимое младших разрядов (7 - 0) шины 18 адреса, а в МБР 98 - содержимое старших разрядов (15 - 8) шины 18 адреса. Сигналы из БУ 17 (с выхода дешифратора 115) разнесенные во времени, открывают выходы МБР 98-100. При этом на шину 19 данных поступает код команды безусловного перехода и адрес пере- х.ода (содержимое МБР 100, затем МБР 99, МБР 98). Код команды безусловного перехода в МБР 100 появляется при включении питания на устройство.

Входы узла 7 (входы элементов И 101, фиг. 9) соединены с выходами дешифратора 10 и выходами Не. АП 26 всех АП 2 структуры МПС. При

наличии сигналов с этих блоков на

одном из элементов И 101 на его выходе появляется сигнал, который через элемент ИЛИ 102 переключает триг

to

125449512

«

rep 103 в единичное состояние. С вы- в унитарных кодах (каждому разряду хода последнего сигнал подается на входы Сб. ЦП 23, регистра 3, БУ 17 и элемента ИЛИ 15. Элемент 104 задержки задерживает сигнал на время не ме- нее трех тактов работы ЦП 1, необходимое для сброса внутренних регистров ЦП 1 (для К580). После чего сигнал на выходе триггера 103 сбрасывается.

Управляет работой всех блоков устройства в активном режиме блок 17 управления (фиг. 11). В качестве синхронизирующего эпемента использует двухтактный ГИ 118, синхросигналы с которого поступают на блоки МПА после появления сигнала Пуск на единичный вход триггера 117. Этим же сигналом производится начальная уста- . ,

новка (обнуление) счетчика 110, С вы- 20 вход триггера 117. ходов элементов И 119 тактовые импуль- При наличии единицы в нулевом раз- сы поступают: первый - на вход записи регистра 109 и элементы И 116, второй - на элемент И 123. По первому синхроимпульсу производится запись 25 При нулевом состоянии этого разряда и выдача управляющих сигналов из ре- в очередном такте производится при- гистра 109 на внутренние узлы БУ и в узлы устройства.- По второму синхро-. импульсу происходит прибавление

ч п

30

единицы к содержимому счетчика 110 и выборка микрокоманды из памяти 108 микрокоманд. На вход БУ, помимо сигнала Пуск, поступают сигналы с вы- :ходов узла 7, Чт.ЦП 20, n3xi/Un 21 (фиг. 1), регистра 8 (фиг.5), КВО АП 29, а также сигнал с выхода элемента 112 задержки. Последние четыре сигнала предназначены для определения времени выборки очередной микрокоманды .

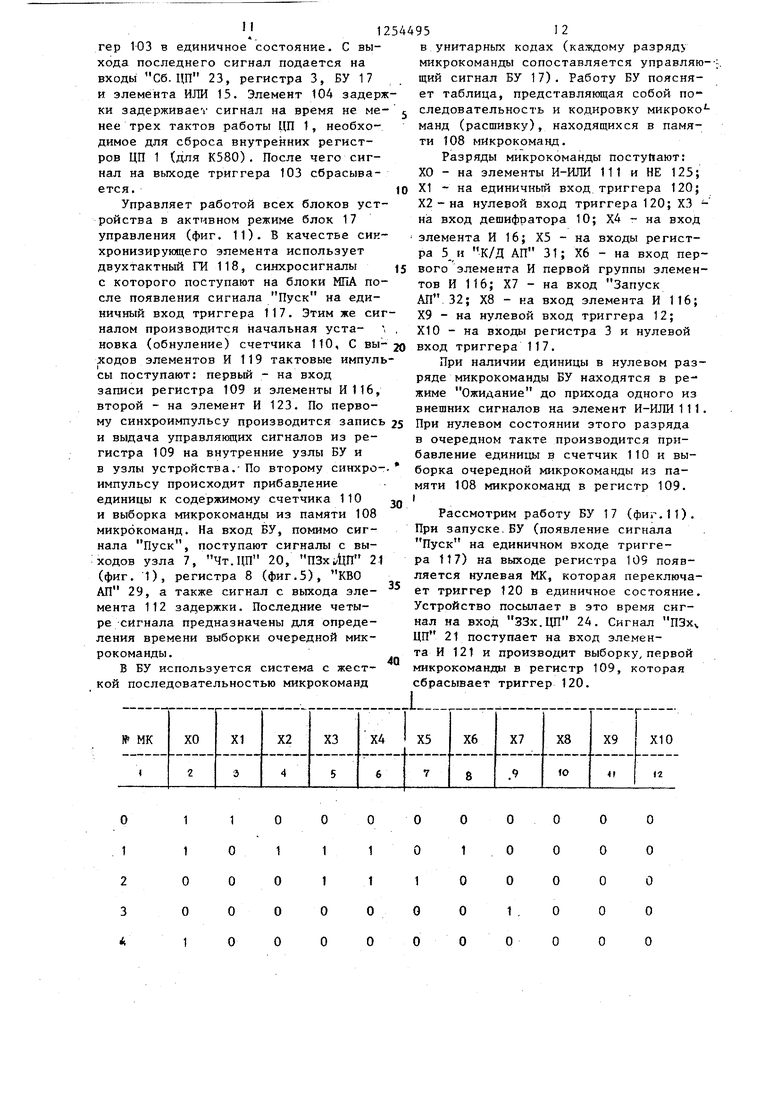

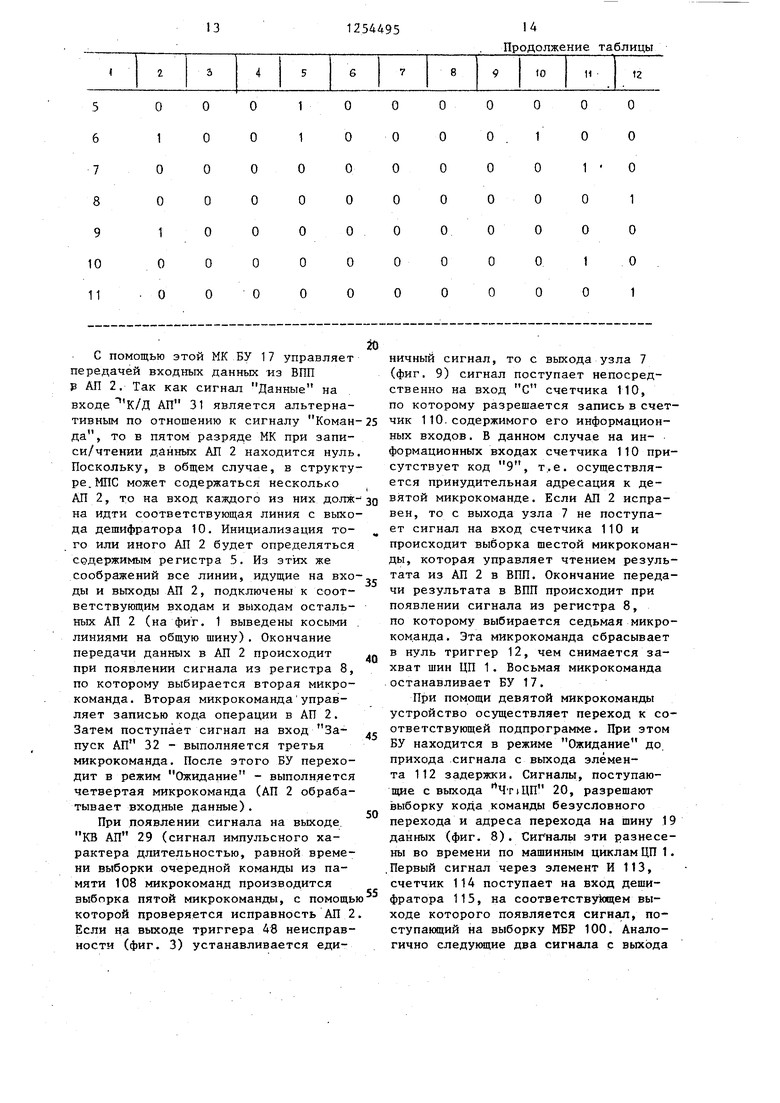

В БУ используется система с жесткой последовательностью микрокоманд

микрокоманды сопоставляется управляющий сигнал БУ 17). Работу БУ поясняет таблица, представляющая собой по следовательность и кодировку микроко - манд (расшивку), находящихся в памяти 108 микрокоманд.

Разряды микрокоманды поступают: ХО - на элементы И-ИЛИ 111 и НЕ 125; Х1 на единичный вход триггера 120; Х2 - на нулевой вход триггера 120; ХЗ на вход дешифратора 10; Х4 - на вход элемента И 16; Х5 - на входы регистра К/Д АП 31; Х6 - на вход пер- 15 вого элемента И первой группы элементов И 116; Х7 - на вход Запуск АП 32; Х8 - на вход элемента И 116; Х9 - на нулевой вход триггера 12; XIО - на входы регистра 3 и нулевой

ряде микрокоманды БУ находятся в режиме Ожидание до прихода одного из внешних сигналов на элемент И-ИЛИ 111.

бавление единиць: в счетчик 110 и выборка очередной микрокоманды из памяти 108 микрокоманд в регистр 109.

35

4Q

Рассмотрим работу БУ 17 (фиг.11). При запуске. БУ (появление сигнала Пуск на единичном входе триггера 117) на выходе регистра 109 появляется нулевая МК, которая переключает триггер 120 в единичное состояние. Устройство посылает в это время сигнал на вход ЗЗх.Щ 24. Сигнал ПЗх,. ЦП 21 поступает на вход элемента И 121 и производит выборку, первой микрокоманды в регистр 109, которая сбрасывает триггер 120.

О

1 2 3

А

в унитарных кодах (каждому разряду

вход триггера 117. При наличии единицы в нулевом раз- При нулевом состоянии этого разряда в очередном такте производится при-

микрокоманды сопоставляется управляю- щий сигнал БУ 17). Работу БУ поясняет таблица, представляющая собой по следовательность и кодировку микроко - манд (расшивку), находящихся в памяти 108 микрокоманд.

Разряды микрокоманды поступают: ХО - на элементы И-ИЛИ 111 и НЕ 125; Х1 на единичный вход триггера 120; Х2 - на нулевой вход триггера 120; ХЗ на вход дешифратора 10; Х4 - на вход элемента И 16; Х5 - на входы регистра К/Д АП 31; Х6 - на вход пер- вого элемента И первой группы элементов И 116; Х7 - на вход Запуск АП 32; Х8 - на вход элемента И 116; Х9 - на нулевой вход триггера 12; XIО - на входы регистра 3 и нулевой

вход триггера 117. При наличии единицы в нулевом раз- При нулевом состоянии этого разряда в очередном такте производится при-

ряде микрокоманды БУ находятся в режиме Ожидание до прихода одного из внешних сигналов на элемент И-ИЛИ 111.

вход триггера 117. При наличии единицы в нулевом раз- При нулевом состоянии этого разряда в очередном такте производится при-

бавление единиць: в счетчик 110 и выборка очередной микрокоманды из памяти 108 микрокоманд в регистр 109.

Рассмотрим работу БУ 17 (фиг.11). При запуске. БУ (появление сигнала Пуск на единичном входе триггера 117) на выходе регистра 109 появляется нулевая МК, которая переключает триггер 120 в единичное состояние. Устройство посылает в это время сигнал на вход ЗЗх.Щ 24. Сигнал ПЗх,. ЦП 21 поступает на вход элемента И 121 и производит выборку, первой микрокоманды в регистр 109, которая сбрасывает триггер 120.

С помощью этой МК БУ 17 управляет

передачей входных данных -кз ВПП р АП 2. Так как сигнал Данные на входе К/Д АП 31 является альтернативным по отношению к сигналу Коман да, то в пятом разряде МК при записи/чтении данных АП 2 находится нуль Поскольку, в общем случае, в структуре. МПС может содержаться несколько АП 2, то на вход каждого из них долж на идти соответствующая линия с выхода дешифратора 10. Инициализация то- го или иного АП 2 будет определяться содержимым регистра 5. Из зтих же соображений все линии, идущие на вхо ды и выходы АП 2, подключены к соответствующим входам и выходам остальных АП 2 (на фиг. 1 выведены косыми линиями на общую щину). Окончание передачи данных в АП 2 происходит при появлении сигнала из регистра 8, по которому выбирается вторая микрокоманда. Вторая микрокоманда управляет записью кода операции в АП 2. Затем поступает сигнал на вход Запуск АП 32 - выполняется третья микрокоманда. После этого БУ переходит в режим Ожидание - выполняется четвертая микрокоманда (АП 2 обрабатывает входные данные).

При появлении сигнала на выходе. KB АП 29 (сигнал импульсного характера длительностью, равной времени выборки очередной команды из памяти 108 микрокоманд производится выборка пятой микрокоманды, с помощь которой проверяется исправность АП 2 Если на выходе триггера 48 неисправности (фиг. 3) устанавливается еди

о

Q

5

0

5

ничный сигнал, то с выхода узла 7 (фиг. 9) сигнал поступает непосредственно на вход с счетчика 110, по которому разрешается запись в счетчик 110.содержимого его информационных входов. В данном случав на информационных входах счетчика 110 присутствует код 9, т..е. осуществляется принудительная адресация к девятой микрокоманде. Если АП 2 исправен, то с выхода узла 7 не поступает сигнал на вход счетчика 110 и происходит выборка шестой микрокоманды, которая управляет чтением результата из АП 2 в ВПП. Окончание передачи результата в ВПП происходит при появлении сигнала из регистра 8, по которому выбирается седьмая микрокоманда. Эта микрокоманда сбрасывает в нуль триггер 12, чем снимается захват шин ЦП 1. Восьмая микрокоманда останавливает БУ 17.

При помощи девятой микрокоманды устройство осуществляет переход к соответствующей подпрограмме. При этом БУ находится в режиме Ожидание до прихода .сигнала с выхода элемента 112 задержки. Сигналы, поступающие с выхода MTiHn 20, разрещают выборку кода команды безусловного перехода и адреса перехода на шину 19 данных (фиг. 8). Сигналы эти разнесены во времени по машинным циклам ЦП 1. .Первый сигнал через элемент И 113, счетчик 114 поступает на вход дешифратора 115, на соответствующем выходе которого появляется сигнал, поступающий на выборку МБР 100. Аналогично следукнцие два сигнала с выхода

15125 i49516

Чт.ЦП 20 производят выборку содер- В свою очередь, АП 2 выставляет сиг- жимого МБР 99 и МБР 98 (адрес перехо- нал Нс.АП 26 (в случае неисправда). Причем, выход дешифратора 115, соединенный с элементом НЕ 94, соединен также с элементом 112 задержки, сигнал с которого поступает по окончании сигнала с выхода Чт.ЦП 20, чем осуществляется переход к десятой микрокоманде. Десятая микрокоманда сбрасывает сигнал на входе Гт. сигналом на нулевой вход триггера 12. Одиннадцатая микрокоманда снимает блокировку ВПП и останавливает БУ 17. В процессе обработки информации

10 В первом случае производятся аналогичные действия со стороны устрой- ства, С выхода БУ 17 сигналы поступают на вход дешифратора 10, в регистр 8 (формирование адресов резульв МПС данное устройство выявляет об- is тата), на вход элемента И 11 (режим

чтения АП 2) и на вход Зп.ВПП 35 (режим записи в ВПП). После чего осуществляется снятие захвата шин ЦП 1 сигналом из БУ 17 на нулевой вход триггера 12 и остановка БУ 17. В результате ЦП 1 переходит к обработке

ращение к аппаратно-реализуемой функции, выставляет запрос на захват шин ЦП 1 в случае появления такого обращения, выдает информацию на соответствующие узлы устройства из памяти- 20 каталога и, прежде чем принять на себя управление системой, подготавливает обратный переход в основную программу (засылает в регистр команд

ЦП 1 команду возврата из подпрограм- 25 управления подпрограмме необходимо

МЫ РЕТ), а также подготавливает возможный переход к соответствующей подпрограмме.

Получив управление, устройство определяет АП 2, который будет производить обработку функции, и засылает в него данные по шине 19 данных из ВПП в режиме прямого доступа к памят Сигналы с выхода БУ 17 поступают на входы дешифратора 10 (инициирование соответствующего АП 2), элемента И 16 (режим записи в АП 2) регистра 3 (формирование адресов данных), Чт.ЦП 33 (режим чтения ПП). По окончании записи данных в АП 2 производится запись в него кода операции также по шине 19 данных. При этом сигналы с выхода БУ 17 поступают на входы регистра 5 (выборка кода операции), дешифратора 10, элемента И 1.6 (режим записи в АП 2). После этого с выхода БУ 17 поступает сигнал на вход Запуск АП 32, при котором начинается обработка данных (вычисление функции). Затем устройство ожидает окончания в вычислении функции в АП 2. При появлении сигнала с выхода КБ АП 29 устройство проверяет исправность АП 2, производящего вычисление функции. Для этого с выхода БУ 17 подается сигнал на вход дешифратора 10, который иницирует соответствующий АП 2, и поступает на узел 7 (фиг.9).

ности АП 2), который также поступает на узел 7. Затем производится либо выдача результата из АП 2 в ВПП (если АП 2 исправен), либо переход к подпрограмме (если АП 2 неисправен), которая реализует данную функцию.

В первом случае производятся анаогичные действия со стороны устрой- ства, С выхода БУ 17 сигналы поступают на вход дешифратора 10, в регистр 8 (формирование адресов резульдальнейшей программы.

Во втором случае для передачи

0

5

.

5

0

произвести переход к ее первой команде. Для этого с выхода узла 7 сигнал поступает на вход Сб.ЦП 23 (длительностью не менее трех тактов машинного цикла ЦП 1), на вход регистра 3 (блокировка ВПП), на выходы БУ 17 и элемента ИЛИ 15 (снятие захвата шин ЦП 1 и установка сигнала на вход Гт. ЦП 23). При появлении сигнала с выхода Чт.ЦП 20 осуществляется вьщача на шину 19 данных кода команды безусловного перехода и адреса перехода к подпрограмме. Затем происходит сброс сигнала на входе Гт., блокировка ВПП сигналом из БУ 17 на вход регистра 3 и останов БУ 17.

Формула изобретения

1. Устройство для сопряжения центрального процессора с группой арифметических процессоров, содер -ащее дешифратор и два элемента И, причем выходы первого и второго элементов И подключены к входам чтения и записи арифметических процессоров группы соответственно, выход дешифратора соединен с первыми входами первого и второго элементов И и подключен к вхо дам выборки арифметических процессоров группы, отличающееся тем, что, с целью повышения быстродействия, в него введены блок микропрограммного управления, регистр возврата в программу, регистр адреса, блок памяти, регистр кода операции, регистр номера, регистр диагностического перехода, узел сравнения, два триггера и два элемента ИЛИ, причем вход чтения регистра возврата в программу соединен с первым входом логического условия блока микропрограммного управления и подключен к выходу чтения центрального процессора, вход записи регистра возврата в программу соединен с вторым входом логического УСЛОВИЯ блока микропрограммного управления, первым входом первого элемента ИЛИ и подключен к выходу подтверждения захвата центрального процессора, выход первого триггера соединен с третьим входом логического условия блока микропрограммного управления и подключен к входу запроса захвата центрального процессора, выход второго триггера подключен к входу готовности центрального процессора, выход узла сравнения соединен с четвертым входом логического условия блока микропрограммного управления, первым входом второго элемента ИЛИ, первым входом установки регистра возврата в-программу и подключен к входу сброса центрального процессора, вход записи блока памяти подключен к выходу записи центрального процессора, первый вход узла сравнения соединен с входом чтения блока памяти и подключен к вы ходам неисправности арифметических процессоров группы, пятый вход логического условия блока микропрограммного управления подключен к выходам коцца выполнения операции арифметических процессоров группы, первый выход блока микропрограммного управления подключен к входам запуска арифметических процессоров группы, второй выход блока микропрограммного управления соединен с входом записи регистра- кода операции и подключен к входам Команда/данные арифметических процессоров группы, первый информационный вьгход регистра возврата в программу, информационные выходы регистра кода операции, регистра ди- агностическогЬ перехода и информационные входы блока памяти подключены к информационному входу-выходу -центрального процессора, информационным входам-выходам арифметических процессоров группы и информационному, входу-выходу внешней памяти программ

o

5

0

5

0

5

0

5

0

5

информационные входы регистра возврата в программу, регистра диагностического перехода, первый информационный выход регистра адреса и адресный вход блока памяти подключены к адресному выходу центрального процессора и адресному входу внешней памяти программ, второй информационный выход регистра возврата в про- грамму подключен к входу разрешения выборки внешней памяти программ, тре- тий выход блока микропрограммного управления соединен с первым входом чтения регистра адреса, с вторым входом первого элемента И и подключен к входу записи внешней памяти программ, четвертый выход блока микропрограммного управления соединен с вторым входом чтения регистра адреса и подключен к входу чтения внешней памяти программ, при этом пятый выход блока микропрограммного управления соединен с единичным входом первого триггера, нулевой вход которого соединен с шестым входом логического условия блока микропрограммного управления, с вторым входом второго элемента ИЛИ, с входом записи регистра адреса, с входом разрешения регистра возврата в программу, с входом записи регистра номера, с входом записи регистра диагностического перехода, с установочным входом регистра кода операции и первым информационным выходом блока памяти, второй информационный выход которого соединен с информационными входами регистра кода операции, регистра номера и регистра адреса, второй информационный вход которого соединен с седьмым входом логического условия блока микропрограммного управления, шестой выход которого соединен с вторым входом второго элемента И, информационный выход регистра номера соединен с информационными входами дешифратора, разрешаю(дий вход которого соединен с седьмым выходом блока микропрограммного управления, восьмой выход которого соединен с входом чтения регистра диагностического перехода, второй вход узла сравнения соединен с выходом дешифратора, девятый выход .блока микропрограммного управления соединен с вторым входом установки регистра возврата в программу и с вторым входом первого элемента ИЛИ, выход которого соединен с единичным входом второго триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ.

2. Устройство по п. 1, о т л и - чающееся тем, что блок микропрограммного управления содержит память микрокоманд, регистр микрокоманд, счетчик микрокоманд, два триггера, счетчик, дешифратор, генератор импульсов, элемент задержки, восемь

10

элементов И, элемент ИЛИ, элемент И- ИЛИ, элемент НЕ, причем первый вход первого элемента И соединен с тактовым входом дешифратора и является первым входом логического условия блока, первый вход второго элемента И является вторым вхо дом логического условия блока, второй вход первого элемента И является третьим входом логического условия блока, син- хровход счетчика микрокоманд соединен Q выход которого соединен с четвертым

мента И-ИЛИ, выход которого соедине с первым входом элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, выход которого соединен с вторь м входом третьего элемента И, выход которого соединен со счетным входом счетчика микроко- .манд, выход которого соединен с адресным входом памяти микрокоманд, информационный выход которой соединен с информационным входом регистр 55 микрокоманд, седьмой и восьмой выхо которого соединены соответственно с единичным и нулевьгм входами второ го триггера, выход которого соедине с вторым входом второго элемента И,

25

30

с первым входом третьего элемента И и является четвертым входом логического условия блока, первый вход элемента И-ИЛИ является пятым входом логического условия блока, единичный вход первого триггера соединен с нулевым входом счетчика микрокоманд и является шестым входом логического условия блока, второй вход элемента И-ИЛИ является седьмь М входом ло- гич еского условия блока, первый, второй, третий, четвертый и пятый выходы регистра микрокоманд являются пер- .вым, вторым пятым, шестым, седьмым выходами блока соответственно, выходы четвертого и пятого элементов И явля- ются третьим и четвертым выходами блока соответственно, шестой выход регистра микрокоманд соединен с нулевым входом первого триггера и является девятым выходом блока, первый, второй и третий выходы дешифратор образуют восьмой выход блока, при . этом в блок е микропрограммного управ- лрння первый выход дешифратора соеди40

входом элемента И-ИЛИ, пятый, шестой седьмой и восьмой входы которого сое динены с девятым выходом регистра микрокоманд и входом элемента НЕ, вы ход которого соединен с вторым входом элемента ИЛИ,- второй вход шестого элемента И соединен с выходом сед мого элемента И, первый вход которог соединен с первым входом восьмого элемента И, с Ьыходом первого тригге ра и с третьим входом первого элемен та И, выход -которого соединен со сче ным входом счетчика, выход которого соединен с информационным входом дешифратора, первый и второй выходы генератора импульсов соединены соответственно с вторыми входами седьмого и восьмого элементов И,, вькод восьмого элемента И соединен с первыми входами четвертого и пятого эле ментов И и с входом записи регистра микрокоманд, десятый и одиннадцать выходы которого соединены с вторыми входами четвертого и пятого элементов И соответственно.

элемента задержки, вы- соединен с нулевым вхо- и третьим входом эле

выход которого соединен с четвертым

нен с входом ход которого дом счетчика

мента И-ИЛИ, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с первым входом шестого элемента И, выход которого соединен с вторь м входом третьего элемента И, выход которого соединен со счетным входом счетчика микроко- .манд, выход которого соединен с адресным входом памяти микрокоманд, информационный выход которой соединен с информационным входом регистра микрокоманд, седьмой и восьмой выходы которого соединены соответственно с единичным и нулевьгм входами второго триггера, выход которого соединен с вторым входом второго элемента И,

5

0

входом элемента И-ИЛИ, пятый, шестой, седьмой и восьмой входы которого соединены с девятым выходом регистра микрокоманд и входом элемента НЕ, выход которого соединен с вторым входом элемента ИЛИ,- второй вход шестого элемента И соединен с выходом седьмого элемента И, первый вход которого соединен с первым входом восьмого элемента И, с Ьыходом первого триггера и с третьим входом первого элемента И, выход -которого соединен со счетным входом счетчика, выход которого соединен с информационным входом дешифратора, первый и второй выходы генератора импульсов соединены соответственно с вторыми входами седьмого и восьмого элементов И,, вькод восьмого элемента И соединен с первыми входами четвертого и пятого элементов И и с входом записи регистра микрокоманд, десятый и одиннадцать выходы которого соединены с вторыми входами четвертого и пятого элементов И соответственно.

II

1

I . 7j

j..-.,p-

,

Г: I I . f /I

ЖШ ТТГ Йftj Лиг 33 ПЗж Up ItffftС f/ CZ ЗпИтСО

19

Я

8К Afl 17 Чт АП а

Зп АП 30

т Л/1 УГ

Золиаг АП32

««

45

4S

-CZ

-

KB Ami

5

-,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Микропрограммный процессор со средствами быстрого прерывания | 1982 |

|

SU1116432A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем в качестве средства для сопряжений центрального процессора с арифметическими процессорами. Целью изобретения является повышение быстродейстия вычислительной системы за счет обеспечения переключения вычислительных операций с программных на аппаратные средства и наоборот. Устройство содержит блок управления, регистр возврата в программу, регистр кода операции, регистр диагностического перехода, регистр адреса, регистр номера, блок памяти, узел сравнения, дешифратор, два триггера, два элемента ИЛИ, два элемента И. 1 з.п.ф-лы, 12 ил., табл. § (Л

)пипи

55 ,

ТН

57

-

1, / tfl

г-I

tfl

t-f

1571

Чй

J9

да Jiff Xfamj-tt Ml

OmSSnfJ

IftmBnnjt)

(JnemiSJ

Яуся

вя шинной

fcpftupolamfM S

.ff

Т W

cf

6miuant№tt цюрнирова- meafS

От бУ J7

tfiut.S

1-й разцяа SHxodo Ю

iput. Iff

| Электроника, -1977, № 4, с | |||

| Веникодробильный станок | 1921 |

|

SU53A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Электроника, 1980, № 10, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-08-30—Публикация

1984-11-10—Подача