; Изобретение относится к вычислительной технике и предназначено для |решения задач методом статистических |испытаний,

Цель изобретения - повьппение быстродействия.

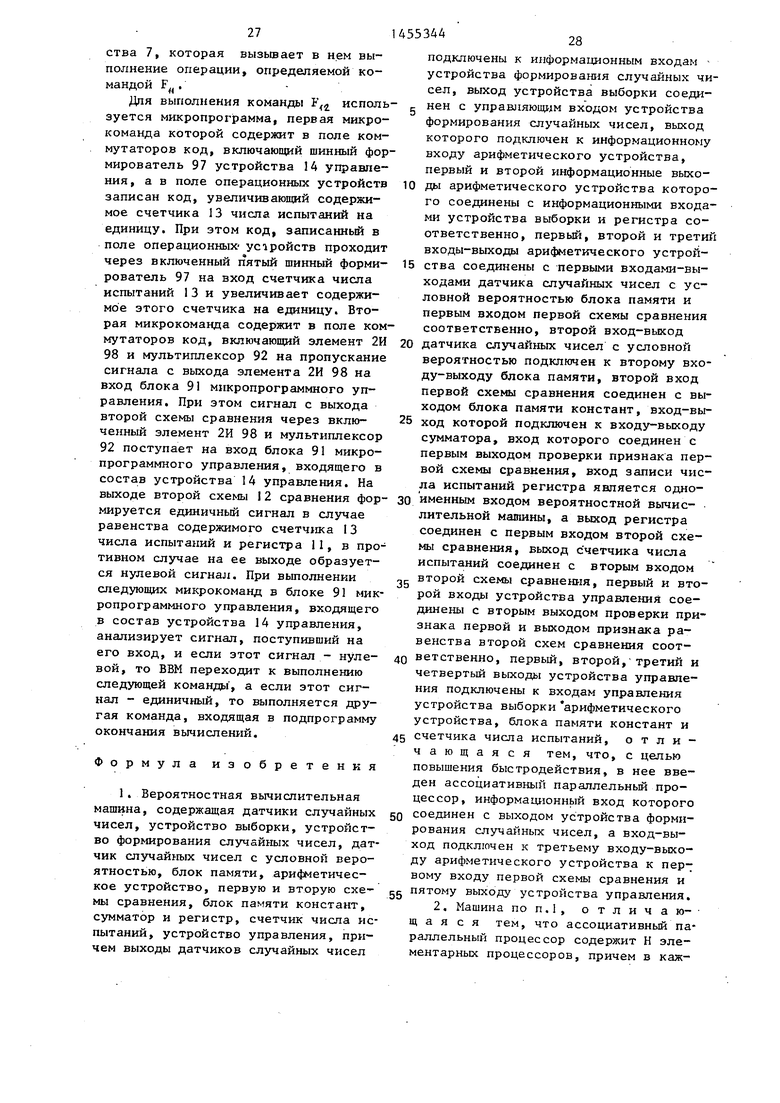

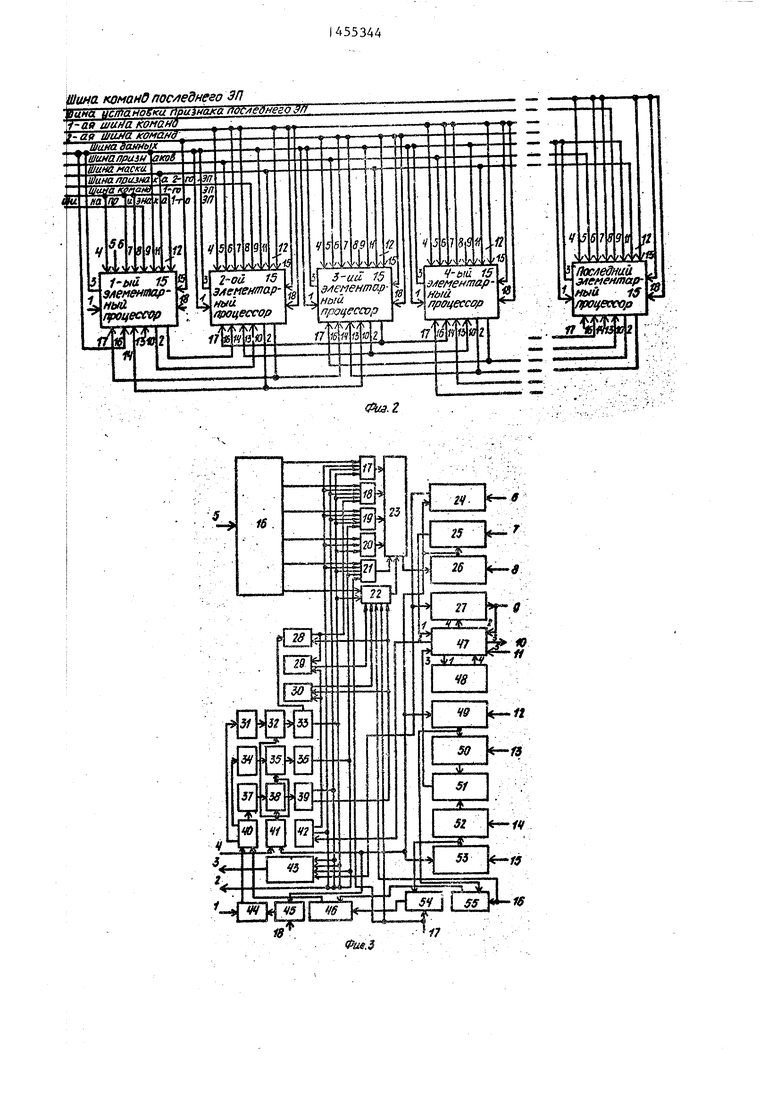

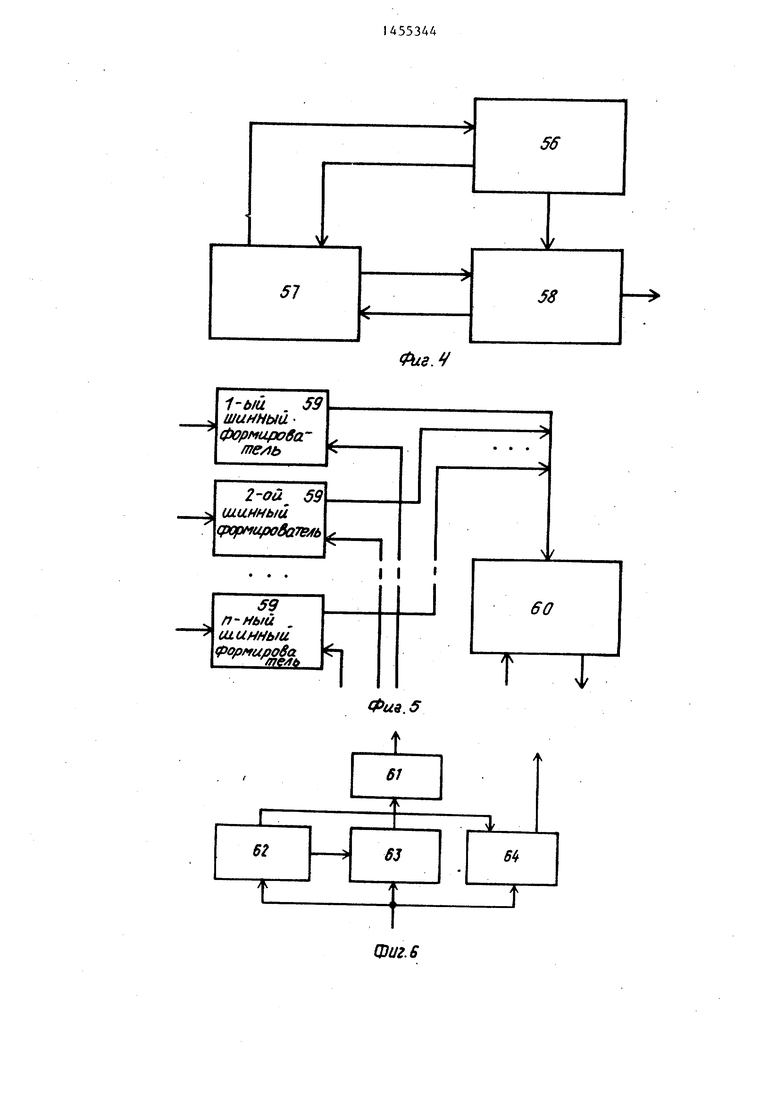

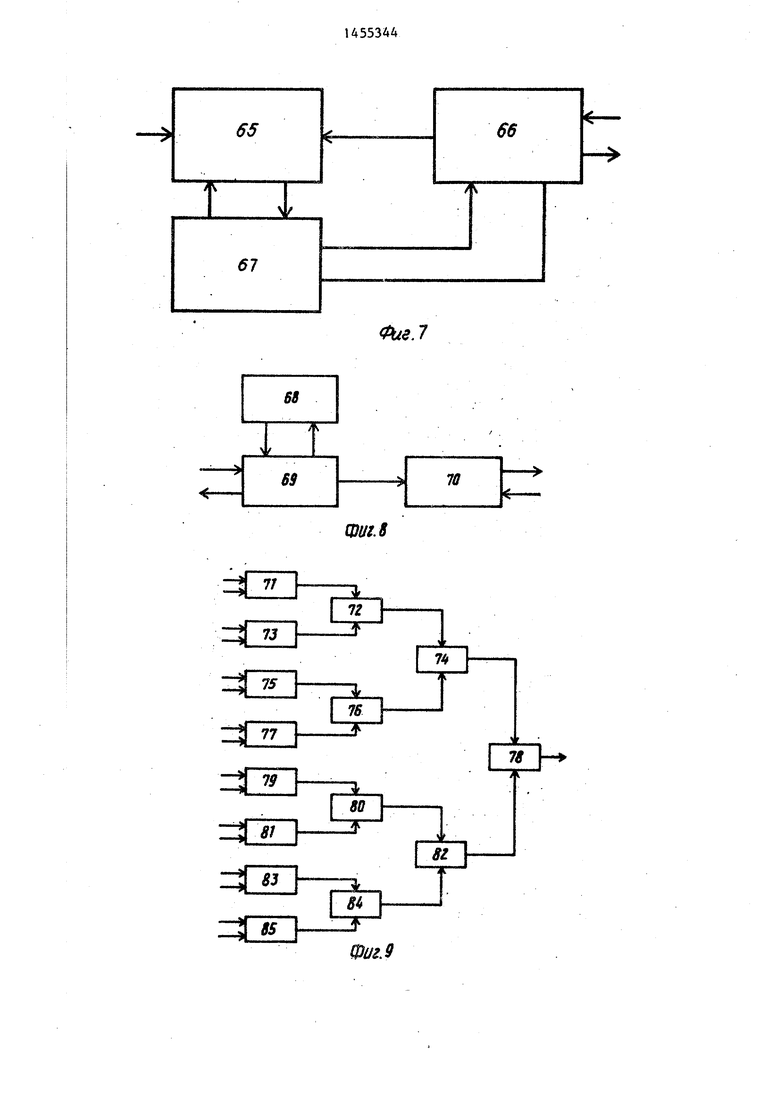

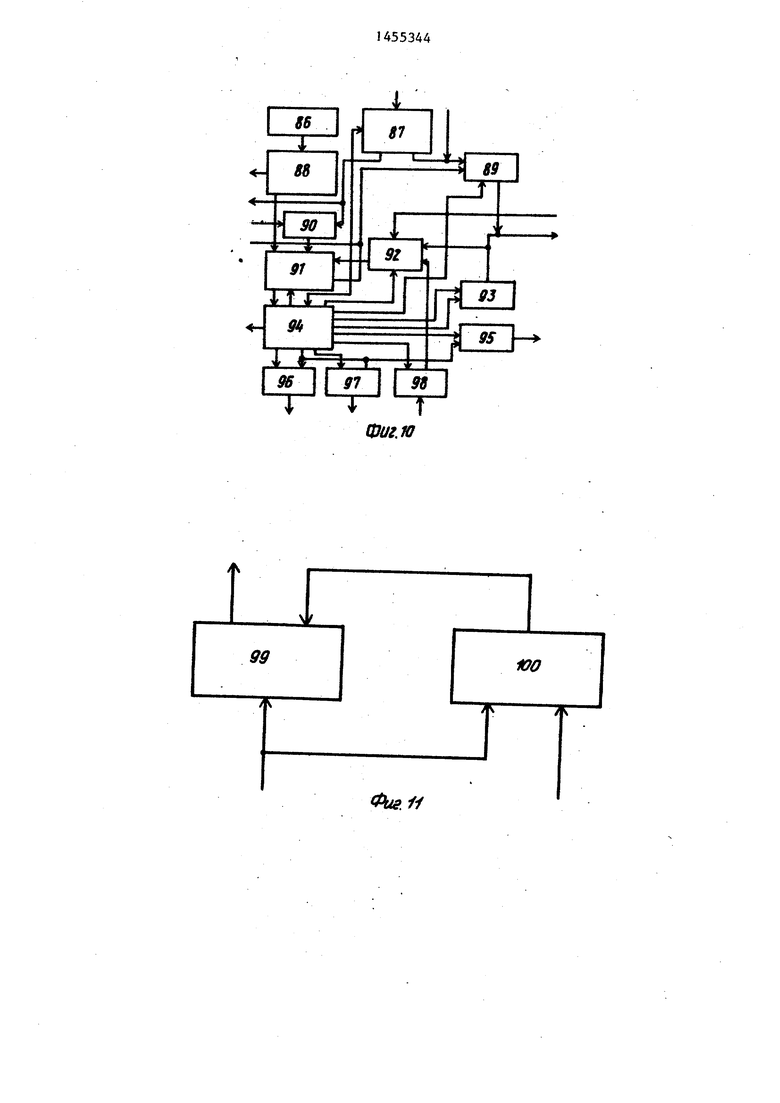

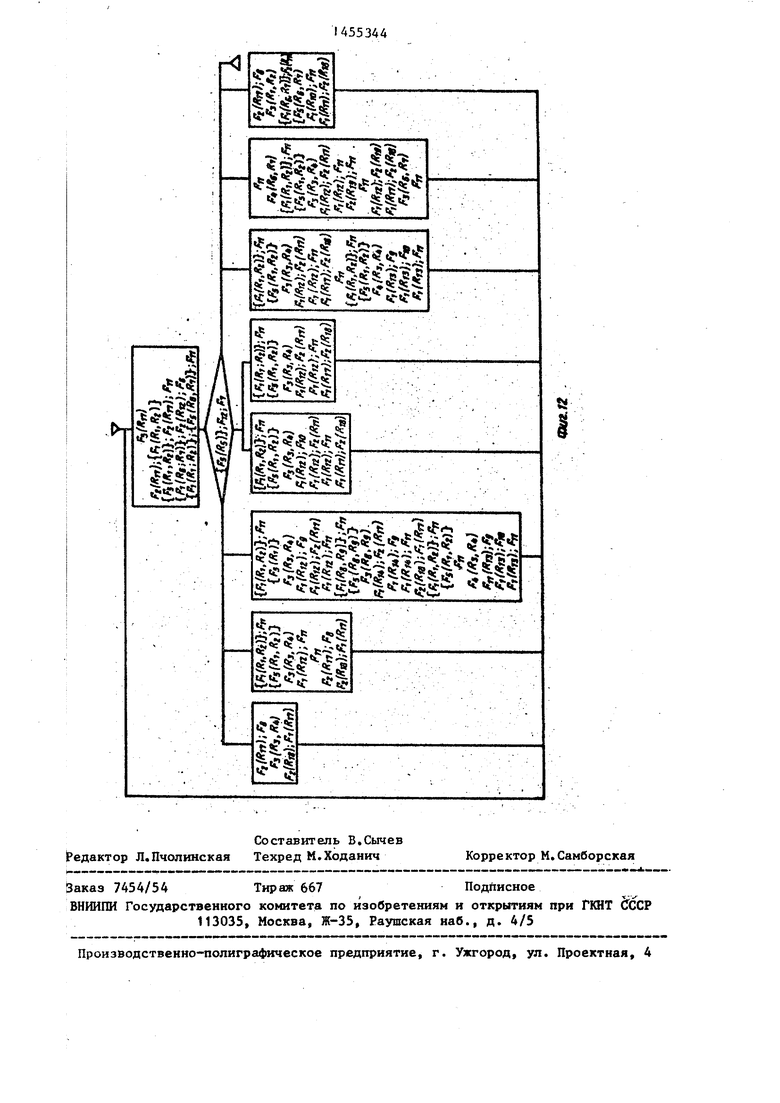

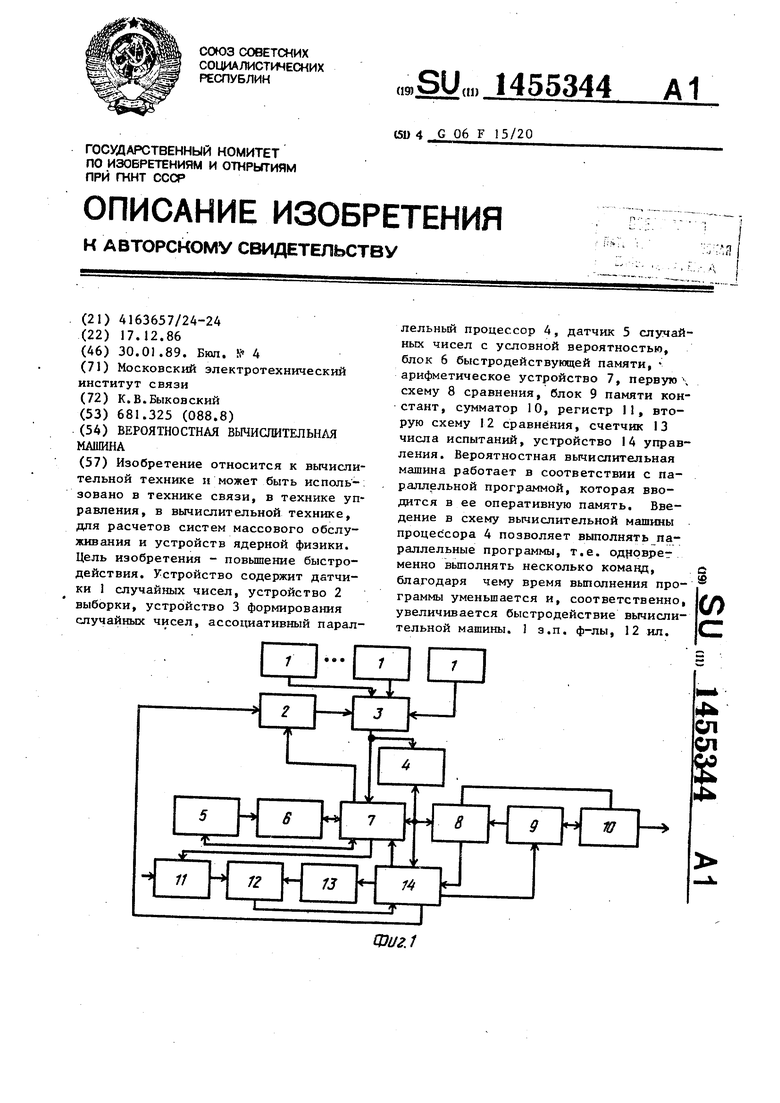

I На фиг. 1 представлена блок-схема |вероятностной вычислительной машины; |на фиг. 2 - ассоциативный параллель- |ный процессор} на фиг, 3 - элементар- 1ный процессор; на фиг, 4 - датчик случайных чисел; на фиг, 5 - смесительное устройство; на фиг. 6 - устройство выборки; на фиг, 7 - датчик случайных чисел с условной вероятностью; на фиг, 8 - устройство блока памяти констант; на фиг, 9 - вторая схема сравнения; на фиг, 10 - устройство управления; на фиг, 11 - первая схема сравнения; на фиг,. 12 - блок- схема программы решения задачи массо- JBoro обслуживания,

I Вероятностная вычислительная маши- |на (ВВМ) содержит датчики 1 случай- |ных чисел, устройство 2 выборки, уст- |ройство 3 формирование случайных чи- |сел, ассоциативный параллельный про- |цессор 4, датчик 5 случайных чисел с

тельного выполнения арифметических операций с фиксированной запятой. С помощью шинных формирователей, входящих в состав арифметического устройства, осуществляется сопряжение арифметического устройства с другими блоками ВВМ. Первая схема сравнения 8 используется для выборочной записи чисел в сумматор 10. Блок 9 памяти констант служит дпя хранения результатов вычислений. Сумматор 10 предназначен для получения окончательных результатов вычислений. Регистр I1 служит для хранения числа статистических испытаний, которые необходимо осуществить в соответствии с условиями решаемой задачи. Счетчик -13 числа испытаний предназначен для счета количества проведенных статистических испытаний. Вторая схема 12 сравнения служит для определения равенства чисел, хранящихся в регистре Пив счетчике числа испытаний 13, Устройство 14 управления предназначено для управления работой ВВМ.

Ассоциативный параллельный процессор 4 содержит последовательно соединенные многоразрядными шинами и под

| название | год | авторы | номер документа |

|---|---|---|---|

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Ассоциативный процессорный модуль | 1981 |

|

SU1015390A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство для приема информации | 1982 |

|

SU1084857A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

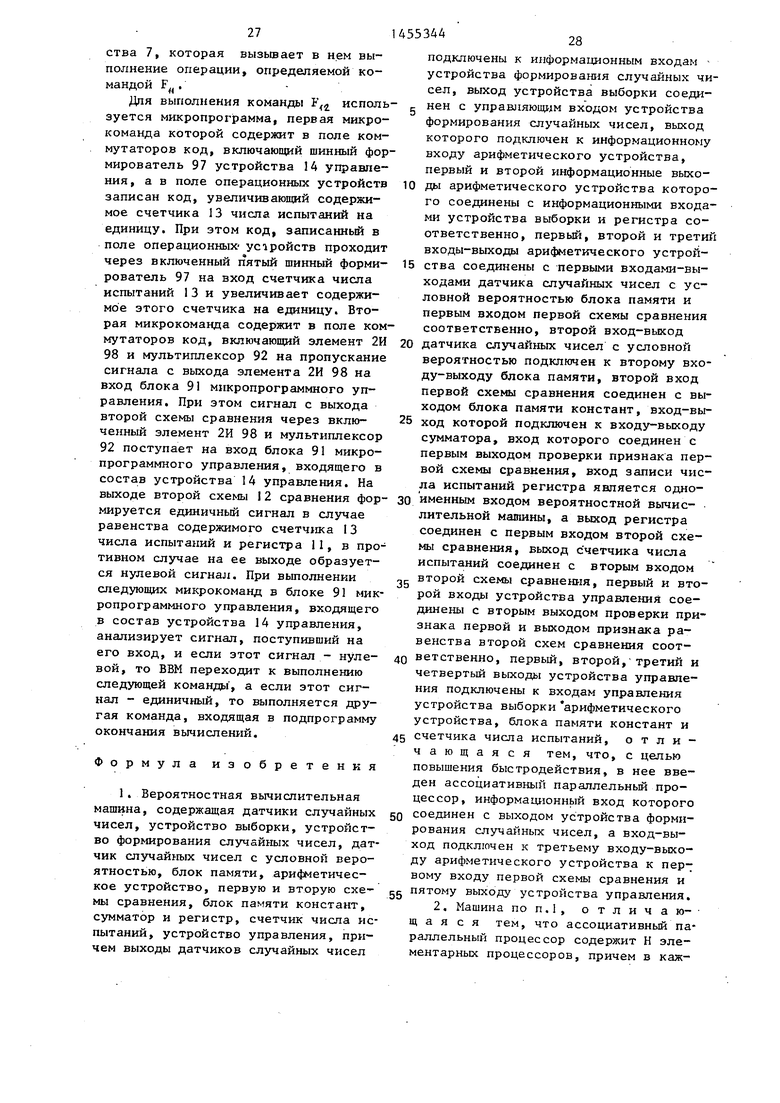

Изобретение относится к вычислительной технике и может быть исполь-; зовано в технике связи, в технике управления, в вычислительной технике, для расчетов систем массового обслуживания и устройств ядерной физики. Цель изобретения - повьшение быстродействия. Устройство содержит датчики 1 случайных чисел, устройство 2 выборки, устройство 3 формирования случайных чисел, ассоциативный параллельный процессор 4, датчик 5 случайных чисел с условной вероятностью, блок 6 быстродействующей памяти, - арифметическое устройство 7, первую схему 8 сравнения, блок 9 памяти констант, сумматор 10, регистр II, вторую схему 12 сравнения, счетчик 13 числа испытаний, устройство 14 управления. Вероятностная вычислительная машина работает в соответствии с параллельной программой, которая вводится в ее оперативную память. Введение в схему вычислительной машины процессора 4 позволяет выполнять параллельные программы, т.е. одррврег менно вьшолнять несколько команд, благодаря чему время вьтолнения программы уменьшается и, соответственно, увеличивается быстродействие вычислительной машины. 1 з.п. ф-лы, 12 ил. (Л

{условной вероятностью, блок 6 быстро-jO ключенные к общим многоразрядным ши|действунщей памяти, арифметическое |устройство 7, первую схему 8 сравне- |ния, блок .19 памяти констант, сумма- |тор 10, регистр 11, вторую схему 12

нам элементарные процессоры 15,

Элементарный процессор 15 содержит дешифратор 16, два элемента 2-2-2- ЗИ-4ИПИ-НЕ 17 и 18, .три элемента 3Iсравнения, счетчик 13 числа испытаний«« ЗИ-2ИЛИ-НЕ 19 - 21, элемент 4-4И- |и устройство 14 управления, 2Ш1И-НЕ 22, элемент 6И-НЕ 23, два

: Датчики 1 случайных чисел предназ- ;начены для получения случайных чисел ;с элементарными законами распределе- ния. Устройство 3 формирования случайных чисел служит для получения случайных чисел со сложными законами распределения. Устройство 2 выборки осуществляет управление получением случайных чисел в устройстве 3, Ассоциативный параллельный процессор 4 предназначен для одновременного выполнения требуемых вычислительных операций. Датчик 5 случайных чисел с условной вероятностью предназначен для получения случайньос чисел с заданной вероятностью, определяемой условиями решаемой задачи. Блок б быстродействующей памяти необходимым дпя хранения результатов, получаемых в арифметическом устройстве 7 и в датчике 5 случайных чисел с условной вероятностью, Ари етическое устройство 7 предназначено дпя последованам элементарные процессоры 15,

Элементарный процессор 15 содержит дешифратор 16, два элемента 2-2-2- ЗИ-4ИПИ-НЕ 17 и 18, .три элемента 35

элемента 2И 24 и 25, первый элемент 2ИЛИ 26, первый щинн формирователь 27, третий элемент 2И 28, второй 29 0 и третий 30 элементы 2ИЛИ, первый триггер 31, четвертьй элемент 2И 32, четвертый 33 и второй 34 триггеры, пятый элемент 2И 35, пятый 36 и третий 37 триггеры, шестой элемент 2И 38, шестой триггер 39, второй блок элементов ИЛИ 40, седьмой элемент 2И 41, седьмой триггер 42, второй шинг шли формирователь 43, третий коммутатор 44, 4eTBepTbrii элемент 2ИЛИ 45, третий блок элементов ШШ 46, центральный процессорный элемент 47, схему 48 ускоренного переноса, восьмой элемент 2И, первьгй коммутатор 50, первый блок элементов ИЛИ 51, второй коммутатор 52, девять1й элемент 2И, четвертый 54 и пятый 55 коммутаторы.

Дешифратор 16 предназначен для оп деделения одного из 16 признаков . (R f гб) закодированных четырехраз0

5

рядным двоичным кодом, подаваемым на шину признаков. По этим признакам элементарные процессоры выполняют команды, поступающие на входы, соединенные с шиной, команд

Элементы 17-23 образуют логическую схему,.определяющую наличие проверяемых признаков в данном элементарном процессоре 15. При наличии в данном элементарном процессоре- 15 проверяемого признака на выходе элемента 6И-НЕ 23 появляется сигнал, который, пройдя через первый элемент 2ИЛИ 26, включает элементы 2И 24, 25, 4, 49 и 53, которые пропускают сигналы с -ВХОДОВ, подкпюченньпс к шине команд, благодаря чему этот элементарный процессор может выполнять команды, подаваемые на шину команд.

Элементы 2И 24, 25, 41, 49 и 53 служат для передачи сигналов с внешних входов элементарного процессора 15 на его внутренние элементы только в случае выполнения в данном элементарном процессоре 15 проверяемых признаков.

Элементы 32, 35 и 38 предназначены для перезаписи признаков из триггера 31 в триггер 33, из триггера 34 в триггер 36 и из триггера 37 в триггер 39 по сигналу, поступающему на четвертый вход элементарного процессора 15.

Элемент 2И 28 предназначен для предварительного формирования сигна- ; ла выполнения в элементарном процессоре 15 двух признаков. Элемент 2ШШ 26 предназначен для объединения выхо-. да элемента 6И-НЕ 23 и восьмого вхо- да элементарного процессора 15.

Элементы 2ИЛИ -29 и 30 предназначены для предварительного формирования сигналов выполнения признаков в эле1455344

реноса пред11азначена для ускорен вьтолнения) вычислительных опера и центральном процессорном элеме 47. Первый шинный формирователь предназначен для выдачи данных и центрального процессорного элеме 47 на общую шину данных, второй ный формирователь 43 - для выдач 10 признаков, хранящихся в элемента процессоре 15, на общую шину данн Коммутатор 50 служит для коммутац данных, поступаюащх от левого сос него элементарного процессора 15 15 вход центрального процессорного э мента 47 данного элементарного пр цессора 15, коммутатор 52 - для к мутации данных, поступающих от пр го соседнего элементарного процес 20 Ра 15 на вход центрального процес ного элемента 47 данного элемента го процессора 15, коммутатор 44 - для коммутации кода трех признако поступакнцих с шины данных на вхо 25 триггеров 31, 34 и 37 элементарно процессора 15, коммутатор 54 - дл коммутации кода трех признаков, по ступающих от правого соседнего эл ментарного процессора 15 на выходы триггеров 31, 34 и 37 данного элем тарного процессора 15, коммутатор для коммутации хода трех признако поступакщих от левого соседнего эл ментарного процессора 15 на входы триггеров 31, 34 и 37 данного элем тарного процессора 15. Первый блок элементов ИЛИ 51 предназначен для объединения выходов коммутаторов 5 и 52J второй блок элементов ИЛИ 4 для объединения выходов блока элем тов ИЛИ 46 и коммутатора 44, трети блок элементов ИЛИ 46 - дпя объеди ния выходов коммутаторов 54 и 55. Каждый датчик 1 случайных чисел

30

35

40

г г«

вого элемента..2ИЛИ 26 и восемнадцато- -. ° которого

го входа элементарного процессора 15 Триггеры 31 34 и 37 предназначены для временного хранения трех признаков в элементарном процессоре 15. Триггеры 33, 36, 39 и 42 предназначены для постоянного хранения .четырех признаков в элементарном процессоре 15.

Центральный процессорный элемент 47 предназначен для выполнения вычислительных операций в злементарном процессоре. Схема 48 ускоренного песоединен с входом постоянного запоминающего устройства (ПЗУ) 56, первый выход которого подключен к перв

50 входу блока 57 микропрограммного управления, а второй его выход соед нен с первым входом центрального пр цессорного элемента 58, второй вход которого соединен с вторым выходом

gg блока 57 микропрограммного управления, а его выход подключен к втором входу блока 57.

Устройство 3 состоит из нескольких шинных формирователей 59, выходы

1455344

реноса пред11азначена для ускорения вьтолнения) вычислительных операций и центральном процессорном элементе 47. Первый шинный формирователь 27 предназначен для выдачи данных из центрального процессорного элемента 47 на общую шину данных, второй шинный формирователь 43 - для выдачи 10 признаков, хранящихся в элементарном процессоре 15, на общую шину данных. Коммутатор 50 служит для коммутации данных, поступаюащх от левого соседнего элементарного процессора 15 на 15 вход центрального процессорного элемента 47 данного элементарного процессора 15, коммутатор 52 - для коммутации данных, поступающих от правого соседнего элементарного процессо- 20 Ра 15 на вход центрального процессорного элемента 47 данного элементарного процессора 15, коммутатор 44 - для коммутации кода трех признаков, поступакнцих с шины данных на входы 25 триггеров 31, 34 и 37 элементарного процессора 15, коммутатор 54 - для коммутации кода трех признаков, поступающих от правого соседнего элементарного процессора 15 на выходы триггеров 31, 34 и 37 данного элементарного процессора 15, коммутатор 55- для коммутации хода трех признаков, поступакщих от левого соседнего элементарного процессора 15 на входы триггеров 31, 34 и 37 данного элементарного процессора 15. Первый блок элементов ИЛИ 51 предназначен для объединения выходов коммутаторов 50 и 52J второй блок элементов ИЛИ 40 - для объединения выходов блока элементов ИЛИ 46 и коммутатора 44, третий блок элементов ИЛИ 46 - дпя объединения выходов коммутаторов 54 и 55. Каждый датчик 1 случайных чисел

0

5

0

-. ° которого

соединен с входом постоянного запоминающего устройства (ПЗУ) 56, первый выход которого подключен к перво50 входу блока 57 микропрограммного управления, а второй его выход соединен с первым входом центрального процессорного элемента 58, второй вход которого соединен с вторым выходом

gg блока 57 микропрограммного управления, а его выход подключен к второму входу блока 57.

Устройство 3 состоит из нескольких шинных формирователей 59, выходы

которых соединены с входом М цент- . рального процессорного элемента 60.

Устройство выборки 2 содержит триггер 62, прямой выход которого подключен к входу второго шинного , формирователя 64, а инверсньм выход соединен с входом первого шинного формирователя 63, вькод которого подключен к входу регистра 61.

Датчик случайных чисел с условной вероятностью 5 имеет блок 65 микророграммного управления, первый вход оторого соединен с первым выходом центрального процессорного элемента 66, второй вход подключен к первому выходу ПЗУ 67, а выход соединен с ервым входом ПЗУ 67, второй выход которого подкпючен к входу центрального процессорного элемента 66, а ; второй вход соединен с вторым выходом центрального процессорного элемента 66.

Блок 9 памяти констант содержит ПЗУ 69, вход которого подключен к выходу блока 68 микропрограммного управления, первый выход соединен с входом блока 68 микропрограммного управления, а второй выход подключен к входу оперативного запоминающего устройства (ОЗУ) 70.

Вторая схема 12 сравнения содержит первый 71 и второй 73 элементы- 155ЛИ1, выходы которых соединены с входами первого элемента К155ЛЛ1.72, третий 75 и четвертый 77 элементы К155ЛИ1, выходы которых подключены к входам второго элемента К155ЛЛ1 76, пятый 79 и шестой 81 элементы К155ЛИ1, выходы которых соединены с входами третьего элемента К155ЛЛ1 80, едьмой 83 и восьмой 85 элементы К155ЛИ1 , выходы которых подключены к входам четвертого элемента К155ЛЛ1

84, причем выходы первого 72 и второ- 45 Формирователя 99.

го 76 элементов К155ЛЛ1 соединены с Для одновременного выполнения ко- входами первого элемента КМ155ЛР4 7Д, а выходы третьего 80 и четвертого 84 элементов К155ЛП 1 соединены с входами второго элемента КМ155ЛР4 82, выход которого подключен к первому входу элемента 2И 78, второй вход которого соединен с выходом первого элемента КМ155ЛР4 74. Элемент 2И 7ё выполнен на микросхеме К155ЛИ1.

Устройство 14 управления содержит генератор 86 синхроимпульсов, выход которого соединен с входом многофункционального синхронизирующего

манд в ВВМ введен ассоциативный параллельный процессор. В ряде задач (в таких, как расчет систем массово- gQ го обслуживания или определение критичности ядерных реакторов) статистические испытания зависимы, поэтому их нельзя выполнять одновременно. В таких задачах ускорения выполнения программы возможно лишь за счет одновременного выполнения команд при вьтол- нении одного статистического испытания. В ряде других задач, решаемых методом статистического моделирова55

устройства 88, выход которого подключен к первому входу блока 91 микропрограммного управления, второй вход которого с выхоДом первого мультиплексора 90, третий вход подключен к выходу второго мультиплексора 92, четвертый вход соединен с первым выходом ПЗУ 94, первый выход подключен к второму входу первого шинного формирователя 89, второй выход соединен с входом ПЗУ 94, второй выход соединен.с первым выходом ОЗУ 87, третий выход подключен к третьему

входу первого шинного формирователя 89, четвертый выход соединен с первым входом второго шинного формирователя 93, пятый выход подключен к второму входу второго шинного формирователя 93, шестой выход соединен с первым входом третьего шинного формирователя 95, седьмой выход подключен к первому входу элемента 2И 98 (выход которого соединен с третьим входом

второго мультиплексора 92), восьмой выход соединен с первым входом пятого шинного формирователя 97, девятый выход подключен к вторым входам третье-- го 95, четвертого 96 и пятого 97 шинных формирователей, десятый выход соединен с первым входом четвертого шинного формирователя 96, а одиннадцатый выход подключен к первому входу второго мультиплексора 92,-второй

вход которого соединен с выходом первого шинного формирователя 89, первый вход которого подключен к второму входу ОЗУ 87, выход которого соединен С входом первого мультиплексора 90.

Первая схема 8 сравнения содержит шинный формирователь 99 и схему 100 совпадения, первые входы-которых соединены, а выход схемы 100 совпадения соединен с управляющим входом шинного

Для одновременного выполнения ко-

манд в ВВМ введен ассоциативный параллельный процессор. В ряде задач (в таких, как расчет систем массово- Q го обслуживания или определение критичности ядерных реакторов) статистические испытания зависимы, поэтому их нельзя выполнять одновременно. В таких задачах ускорения выполнения программы возможно лишь за счет одновременного выполнения команд при вьтол- нении одного статистического испытания. В ряде других задач, решаемых методом статистического моделирова5

10

7 1455344

ния (в таких, как, например, вычисление определенных интегралов в шумах) статистические испытания неза- висимы и их можно осуществлять одновременно. Одновременность вьтолнения статистических испытаний определяет возможность распараллеливания программ решения таких задач и возможность ускоренного их решения на ВВМ как за счет одновременного выполнения комачд программы одного статистического .испытания, так и за счет одновременного выполнения пдрграмм нескольких статистических испытаний. 15 вычислений блок 57 микропрограммного

Рассмотрим подробнее процесс реше- управления, входящий в состав датчика -ния задачи массового обслуживания методом статистических испытаний на ВШ на примере вычисления функции распределения времени ожидания канала связи абонентами телефонной сети и функции распределения времени занятия каналов связи, если известно число абонентов их обслуживания, вероятностные характеристики потока заявок 25 „ает на вход соответствующего DOIHHO- от абонентов на обслуживание, число го формирователя 59 смесительного каналов связи и структура сети связи. Программа решения такой задачи на ВВМ приведена на фиг. 12. Эта программа

является циклической. Число циклов, 30 входящего в состав устройства 2 вы- выполняемых в соответствии с програм- борки. При поступлении включающего мой, равно числу статистических испы таний. В этой программе имеются части, которые можно выполнять одновременно, а именно, команды F, записанные в одной строке какого-либо блока программы, выполняются одновременно. Команда fp, записанная в фигурных

ру 4, соответствует некоторое сочетание признаков R;, команда записьгоает- ся в виде Fr(R; ).

Исходные данные для проведения каждого статистического испытания являются случайными величинами, которые генерируются датчиками 1 случайных чисел. Каждый датчик 1 вьфабатьшает числа со j своим законом распределения. В каждом датчике 1 хранится своя микропрограмма вычисления чисел с требуемым законом распределения, которая записана в ПЗУ 56. .С начала

1 случайных чисел, начинает последовательно считьшать микрокоманды микропрограммы, -записанной в ПЗУ 56, и 20 выполнять их в центральном процессорном элементе 58. В результате выполнения этой микропрограммы в центральном процессорном элементе 58 образуется случайное число, которое постуустройства 3. Шинные формирователи 59 смесительного устройства 3 управляются сигналами с выхода регистра 61,

35

скобках, означает, что это макрокоманда, т.е. что она эквивалентна нескольким одинаковым командам F, выполняемым одновременно. Число команд F, выполняемых одной макрокомандой F j, зависит от конкретных условий решаемой задачи, т.е. от числа каналов связи, от числа узлов связи, от структуры сети связи и т.п. Кроме того, в программе содержатся команды РЗ и 4 которые являются макрокомандами, поскольку они эквивалентны нескольким командам F. Команды, составляющие макрокоманду, выполняются одновременно несколькими элементарными процессорами 15, обладающими одинаковыми сочетаниями признаков R-. Поэтому в программе решения задачи массового обслуживания каждой команде или макрокоманде, относящейся к ас социативному параллельному процессосигнала от устройства 2 выборки соответствующий шинный формирователь 59, входящий в состав устройства 3, пропускает случайное число от датчика 1 случайньЕх чисел на вход центрального процессорного элемента 60 смесительного устройства 3. От первого 63..или второго 64 шинного формирователя, 40 входящего в состав устройства 2 выборки, на вход центрального процессорного элемента 60 смесительного устройства 3 поступают микрокоманды, которые выполняют операции в этом 45 центральном процессорном элементе 60 над случайными числами, поступающими от датчиков 1, благодаря чему образуются случайные числа с заданными законами распределения, которые из 50 центрального процессорного элемента 60 подаются в требуемый блок вычислительной машины.

Сигналы, поступающие из регистра 61 устройства 2 выборки в смеситель- 55 ное устройство 3, записываются в этом регистре 61 из устройства 14 управления вычислительной машины. Триггер 62 предназначен для включения требуемого шинного формирователя устройства 2

вычислений блок 57 микропрограммного

ру 4, соответствует некоторое сочетание признаков R;, команда записьгоает- ся в виде Fr(R; ).

Исходные данные для проведения каждого статистического испытания являются случайными величинами, которые генерируются датчиками 1 случайных чисел. Каждый датчик 1 вьфабатьшает числа со j своим законом распределения. В каждом датчике 1 хранится своя микропрограмма вычисления чисел с требуемым законом распределения, которая записана в ПЗУ 56. .С начала

управления, входящий в состав датчик 25 „ает на вход соответствующего DOIHHO- го формирователя 59 смесительного

1 случайных чисел, начинает последовательно считьшать микрокоманды микропрограммы, -записанной в ПЗУ 56, и 20 выполнять их в центральном процессорном элементе 58. В результате выполнения этой микропрограммы в центральном процессорном элементе 58 образуется случайное число, которое постууправления, входящий в состав датчика „ает на вход соответствующего DOIHHO- го формирователя 59 смесительного

входящего в состав устройства 2 вы- борки. При поступлении включающего

устройства 3. Шинные формирователи 59 смесительного устройства 3 управляются сигналами с выхода регистра 61,

30 входящего в состав устройства 2 вы- борки. При поступлении включающего

35

сигнала от устройства 2 выборки соответствующий шинный формирователь 59, входящий в состав устройства 3, пропускает случайное число от датчика 1 случайньЕх чисел на вход центрального процессорного элемента 60 смесительного устройства 3. От первого 63..или второго 64 шинного формирователя, 40 входящего в состав устройства 2 выборки, на вход центрального процессорного элемента 60 смесительного устройства 3 поступают микрокоманды, которые выполняют операции в этом 45 центральном процессорном элементе 60 над случайными числами, поступающими от датчиков 1, благодаря чему образуются случайные числа с заданными законами распределения, которые из 0 центрального процессорного элемента 60 подаются в требуемый блок вычислительной машины.

Сигналы, поступающие из регистра 61 устройства 2 выборки в смеситель- 5 ное устройство 3, записываются в этом регистре 61 из устройства 14 управления вычислительной машины. Триггер 62 предназначен для включения требуемого шинного формирователя устройства 2

9U5534A10

выборки. На 9ХОД первого шинного фор- статистических испытаний, которое мирователя 63 поступают микрокоманды увеличивается на единицу в начале из арифметического устройства 7, а каждого цикла выполнения программы, на вход второго шинного формирователя Если в счетчике 13 числа испытаний 64 и на вход триггера 62 поступают меньше числа, записанного в регистре микрокоманды от устройства 14. Мик- 11 , то вьтолнение программы продолжа- рокоманды, поступающие из арифмети- ется, если же числа станут равными, ческого устройства 7 или из устрой- то выполнение программы прекращается, ства 14, составляют микропрограмму ю Работа ВВМ начинается с включе- получения случайных чисел с требуемым нием напряжения питания, при STOMJ законом распределения.запускается генератор 86 синхроимДатчик 5 случайных чисел с услов- пульсов, который через многофункцио- ной вероятностью вьфабатывает случай- нальное синхронизирующее устройство ные числа с условной вероятностью в 15 88 переводит блок 91 микропрограммно- соответствии с микропрограммой, хра- го управления устройства 14 управле- нящейся в ПЗУ устройстве 67, входя- ния в режим ожидания исполнения ко- щем в состав этого датчика 5. С нача- манд. С внешнего устройства ввода-вы- лом вычислений блок 65 микропрограм- вода через первый мультиплексор 90 в много управления, входящий в состав 20 блок 91 микропрограммного управления, датчика 5, начинает последовательно входящий в состав устройства 14, посчитывать микрокоманды микропрограм- ступает команда записи программы ре мы, записанной в ПЗУ 67, и выполнять шения задачи в ОЗУ 87 устройства 14. их в центральном процессорном элемен- При этом блок 91 микропрограммного те 66. При этом используется числа, 25 управления находит в ПЗУ 94 устрой-, хранящиеся в блоке 6 быстродействую- ства 14 программу управления записью щей памяти. В результате вьтолнения программы в ОЗУ 87 и начинает ее вы- этой микропрограммы в центральном полнять. В процессе выполенния этой процессорном элементе 66 образуется управляющей программы команды, посту- случайное число, которое затем пере- 30 пающие с внешнего устройства ввода- писывается в блок 6 быстродействунлцей вывода, записываются в ОЗУ 87. В ре- памяти. зультате выполнения управляющей прогПрограмма описанной задачи вьшол- раммы в ОЗУ 87 оказывается записан- няется в основном н ассоциативном па- ной программа решения требуемой зада- раллельном процессоре 4. В конце каж- 35 массового обслуживания, а блок 91 дого цикла программы полученные ре- оказывается в состоянии ожидгшия при- зультаты из ассоциативного параллель- хода следующей команды с внешнего кого процессора 4 по щине данных по- устройства ввода-вывода, ступают на вход первой схемы 8 срав- Чтобы начать выполнение программы нения, которая пропускает эти резуль- 40 решения задачи массового обслуживания таты - в сумматор 10, если выполняется с внешнего устройства ввода-вывода, требуемое соотношение между этими ре- в блок 91 микропрограммного управле- зультатами и данных, хранящимися в ния устройства 14 поступает команда блоке 9 памяти констант. В суммато- начала выполнения этой программы, заре 10 при необходимости эти результа- 45 писанной в ОЗУ 87. При этом блок 91 ты могут быть преобразованы. Из сум- микропрограммного управления начина- матора 10 полученные результаты запи- ет последовательно считывать микро- сьшаются в блок 9 памяти констант. команды соответствующей микропрограм- Таким образом происходит накопле- мы, записанной в ПЗУ 94. Эти микроко- нйе результатов статистическшс испы- 60 манды поступают н-а вход арифметичес- таний.кого устройства 7, в котором в реВ процессе выполнения программы зультате выполнения этих микрокоманд решения задачи осуществляется подсчет записывается адрес первой команды количества проведенных статистичес- программы решаемой задачи, который ких испытаний. При этом в регистре 1 1 55 поступает на адресный вход ОЗУ 87. должно быть записано число статисти- Эта первая команда, считанная нз ОЗУ ческих испытаний,- которое необходимо 87 через первый мультиплексор 90, осуществить, а в счетчике 3 числа поступает на вход блока 91 микропрог-, испытаний хранится число проведенных раммного управления, который прн этом

чI45534A

начинает последовательно считывать из ПЗУ 94 микропрограмму, соответствующую поступившей команде. Эти микрокоманды через соответствующие шинные формирователи поступают на вход арифметического устройства 7, либо на входы других блоков вычислительной машины и вьтолняются ими. С окончанием выполнения последней микрокоманды микропрограммы в арифметическом устройстве 7 формируется адрес следукицей команды, причем эта команда поступает на вход блока 91.,Процесс, описанный ранее, повторяется.

Каждая микрокоманда, считываемая из ПЗУ 94 содержит четыре поля команд, поле признаков, два поля маски, поле коммутаторов, поле ари метичес12

При вычислениях ассоциативного па раллельного процессора 4 используетс поле коммутаторов, четыре поля команд, поле признаков и два поля маски. Кода, записанные в этих полях, поступают в ассоциативный параллельный процессор 4 на входы его общих шин через второй шинный формирователь 93, поскольку в поле коммутаторов записан код, открывающий этот формирователь 93, причем на каждую из четырех шин комавд подается код соответствующего поля команд, на ши 15 ГНУ признаков подается код поля признаков,а на шину маски подается первое поле маски.

Каждый элементарный процессор 15

10

„„ „ - может осуществлять следующие семь

кого устройства, поле ОЗУ и поле one- 20 видов операциймаГс.ж Г ° - Р« информации с общей ши- манд содержит код микрокоманды центрального процессорного элемента 47 элементарного процессора 15 и ход режима элементарного процессора 15. Та- 25 кая структура микрокоманды обеспечивает одновременное выполнение операций в ассоциативном устройстве и бо в .устройстве выборки, либо в счетчике, либо в таблице, причем в ас- 30 социативном ла раллельнсм процессоре могут одновременно выполняться несколько команд.

Если микрокоманда используется для управления устройствами вычислительной машины за исключением управления ассоциативным параллельным процессором 4, то она содержит в поле операционных устройств команду управления требуемым устройством вычислительной машины, а в поле управления коммутаторами содержит код, при котором включен либо третий 95, либо четвертый 96, либо пятый 97 шинный формирователь, пропускакяций код команды на вход соответствующего устройства вычислительной машины. Этот код записан в поле операционных устройств.

ны данных;

Sj - выдачу информации на общую шину данных;

S - прием информации от левого соседнего элементарного процессора

5;

4 прием информации от правого соседнего элементарного процессора -5;

. Sy - выдачу информации в левый и правый соседние элементарные процессоры 15;

Sg - внутренние операции;

S - перезапись признаков.

Для осуществления всех этих операций необходимо включить требуемые элементарные процессоры 15, для чего каждая микрокоманда должна содержать 40 .в поле признаков код признаков, вы35

полнякнцихся в требуемых элементарных процессорах 15. Код, устанавливаемый микрокомандой на шине признаков, подключает элементарные процессоры 15,

45 в которых выполняются эти признаки, к общим шинам ассоциативного параллельного процессора 4. Это подключе-, ние элементарных процессоров 15 осуществляется благодаря тому, что пятые

Если микрокоманда, считываемая из ПЗУ 94, предназначена для управления работой арифметического устройства 7, то она в поле арифметического устройства содержит код нужной микрокоманды, а во втором поле маски содержит требуемый код маски. При поступлении этих кодов на вход арифметического устройства 7, последнее выполняет требуемую микрокоманду.

534A

12

При вычислениях ассоциативного параллельного процессора 4 используется поле коммутаторов, четыре поля команд, поле признаков и два поля маски. Кода, записанные в этих полях, поступают в ассоциативный параллельный процессор 4 на входы его общих шин через второй шинный формирователь 93, поскольку в поле коммутаторов записан код, открывающий этот формирователь 93, причем на каждую из четырех шин комавд подается код соответствующего поля команд, на ши- 5 ГНУ признаков подается код поля признаков,а на шину маски подается первое поле маски.

Каждый элементарный процессор 15

0

- Р« информации с общей ши-

25 30

ны данных;

Sj - выдачу информации на общую шину данных;

S - прием информации от левого соседнего элементарного процессора

5;

4 прием информации от правого соседнего элементарного процессора -5;

. Sy - выдачу информации в левый и правый соседние элементарные процессоры 15;

Sg - внутренние операции;

S - перезапись признаков.

Для осуществления всех этих операций необходимо включить требуемые элементарные процессоры 15, для чего каждая микрокоманда должна содержать 0 .в поле признаков код признаков, вы35

полнякнцихся в требуемых элементарных процессорах 15. Код, устанавливаемый микрокомандой на шине признаков, подключает элементарные процессоры 15,

5 в которых выполняются эти признаки, к общим шинам ассоциативного параллельного процессора 4. Это подключе-, ние элементарных процессоров 15 осуществляется благодаря тому, что пятые

0 входы всех элементарных процессоров 15 соединены с шиной признаков. Код признаков, появлякнцихся на пятом входе элементарного процессора 15, поступает в устройство проверки выпол5 нения признаков в данном элементарном процессоре 15, которое выполнено на дешифраторе 16, на первом 17, втором 18, третьем 19, четвертом 20, пятом 21 и шестом 22 элементах и на злемен

Те 6И-НЕ 23. Если проверяемые признаки вьшолняются, то на выходе элемента 2ИЛИ 26, с выхода которого сигнал проходит на управляющие входы элементов 2И 24, 25, 41, 49 и 53 и на второй вход элемента 2ИЛИ 45, в результате чего эти элементы оказываются во включенном состоянии и пропускают на свои выходы сигналы, поступающие на их входы с общих шин ассоциативного параллельного процессора. При этом код микрокоманды центрального процессорного элемента 47 с седьмого входа элементарного процессора через второй элемент 2И 25 проходит на вход центрального процессорного элемента 47j, который выполняет эту микрокоманду. Если с общей шинш команд подается сигнал на восьмой вход элементарного процессора 15, то этот сигнал посту- |пает на те же логические элементы, |что и сигнал с выхода элемента 6И-НЕ 23 в предыдущем случае. При этом элементарный процессор 15 может также участвовать в вычислительном процессоре. Если проверяемые признаки I не выполняются ипи на пятый вход эле |ментарного процессора 15 сигнал не I подается, то на управляющие входы элементов 2И 24, 25, 41, 49 и 53 и на второй вход четвертого элемента 2ИЛИ 45 сигнал не поступает, они оказываются в выключенном состоянии и данный элементарный процессор 15 в вычислительном процессе не участвует Коды признаков, возникающие на шине признаков, поступают на все элементарные процессоры 15. Поскольку проверяемые признаки могут выполнять ся в нескольких элементарных процессорах 15, то команды, поступающие на шины команд могут выполняться одновременно несколькими элементарными процессорами 15. Наличие в ассоциа- тивном параллельном процессоре 4 дву шин команд, к первой из которых подключены элементарные процессоры 15 с нечетными номерами, а ко второй шине - элементарные процессоры 15с- четными номерами, позволяет нескольким элементарным процессорам 15 с нечетными номерами, в которых вьшолня ется проверяемый признак, одновременно выполнять одну и ту же операцию, в то время как элементарные процессоры 15 с четными номерами, в которых выполняется тот же. признак, могут в то же время .одновременно выполнять

0

20

25

30

15 40 45 50

другую операцию. Кроме того, поскольку в схеме ассоциативного парадшель- ного процессора 4 имеются шины команд нулевого и последнего элементарных процессоров 15, то одновременно с выполнением двух операций двумя группами элементарных процессоров 15 первый и последний элементарные процессоры 15 могут выполнять еще два другие различные операции.

В процессорах 4 могут проверяться следующие сочетания признаков:

R, - номер элементарного процессора 15 четный И в нем выполняется 1-и признак;

Rj - номер элементарного процессора 15 нечетный и в нем выполняется 1-й признак;

R- - номер элементарного процессора 15 четный и в нем выполняется 1-й и 4-й признаки;

Кд - номер элементарного процессора 15 нечетный, и в нем выполняются 1-й и 4-й признаки;

Ry - выполнение в элементарном процессоре 15 1-го и 3-го признаков;

Rg - номер элементарного процессо- ра 15 четный и в нем выполняется 2-й признак;

R - номер элементарного процессора 15 нечетный и в нем выполняется 2-й признак;

Rg - номер элементарного процессо- 35 ра 15 четный и в нем вьшолняются 2-й и 4-й признаки;

R,, - номер элементарного процессора 15 нечетный и в нем вьшолняются 2-й и 4-й признаки;

R,j, - выполнение в элементарном процессоре 15 2-го и 4-го признаков;

R,, - выполнение в элементарном процессоре 15 2-го и 3-го признаков;

R - выполнение в элементарном процессоре 15 4-го признака, а в правом соседнем элементарном процессоре 15 - невыполнение 4-го признака;

R - невыполнение в элементарном процессоре 15 4-го признака и выполнение 4-го признака в левом соседнем элементарном процессоре 15;

R, - невьшолнение 4-го признака в

элементарном процессоре 15 и выполнение 4-го признака в правом соседнем элементарном процессоре J5;

R,j- вьшолнение в элементарном процессоре 15 4-го признака;

R,g - невьшолнение в элементарном процессоре 15 четырех признаков;

5 1Д5534416

pa fi p ° P/ « P«°ro процессо-ного процессорного элемента 47 в его

R - «г,«,,л аккумулятор и регистр. Благодаря тора 5%авен 2 процессо-му, что в поле признаков микрокоманR - нпмвт г.„ «5 устройства управления 1А записан

ра i З MaKcI LeH признаков, выполняющихся в данном

R s-3wr,w элементарном процессоре 15, элемент

15 Р° --Р-2И 25 открыт и микрокоманд приема

для 1-го признака пред-информации проходит с седьмого входа

хр: : Г2-гп ° элементарного npS eccopa 5 и пос уS3- ™ si-. i.

..--.-..гг:: 4 s si: Е:™„™Ег:ггг

.. „ SEiE-:: ErH;:

э е н Г 7 2 Гпоо ° логическихцатый вход требуемого

перечи ен в выполненияпроцессора 15 и далее на пятый вход

ков сочетаний призна-центрального процессорного элемента

чет;ния по накоГ , код, осуществляющий тре6И-т 23 по«« «ь«оДе элемента 25буемое маскирование информации.

6И НЕ 23 появляется сигнал. Триггерытриггеры 31, 34 и 37 в то жГвремГ

предназначены для предва-необходимо записать код пр знакоГс

котоГ - ° - « - комавд кото- знаков, которые в дальнейшем могутрое подается на требуемый элементар39 На вхГГ процессор 15,аписывае;сГ д 39. На входы элементов 2 и 22 посту- режима элементарного процессора 1 пает сигнал 4-го признака с правогосодержащий в разряде, который пост;соседнего элементарного процессора - пает на восемнадцатый вход требуемого 15, а на вход элемента 22 - сигнапэлементарного п цессора 5 единГщу

Г.---г, -- 3. 4iiF ° ::i.T-JЬ г «:™гг„-:г-Z г;

шины могут выполнять как регистрыэлемента 2ИЛИ 45 и на управляющий

центрального процессорного элементавход коммутатора 44

oc;nL Tj; признаков общей щ че«aZ комьогтатор 44 поступает на первый

нации с общей шины данных устройство45 вход схемы 40 объединения проходит

, элементарный ее и поступает на S: т иггерГз , процессор 15 микрокоманду, содержащук 34 и 37 признаков, в которых он запи- в поле коммутаторов код, включающийсывается . Если в трйггеры изнакоТ

93 уст-записывать информацию не

четьше поля Г ° -«« Р- четыре поля комавд, поле маски и попе тарного процессора 15 записываются признака подаются на соответствующиенулизаписываются

ноГпГе с:ГГГ ° ° Р - ь-в любом элементарном процессоре

ного процессора. При этом в поле ко-для выполнения операции S, , т.е для

нуТманГ° Г ° ° ™-55 осуществления выдачи нфо, нГ

ну команд, соединенную с требуемым:общую шину данных, необходимЬ чтобы

но семГ. пРОЦ-сором 15, записа-устройство 14 управления в а о к Формац и с ВТО Р « -Рокоманду, которая должна содержать

информации с второго входа централь-в поле коммутаторов код, включающий

второй шинный формирователь 93 устройства управления 14,через который четыре поля команд, поле маски и поле признаков подаются на соответствующие общие щины ассоциативного параллельного процессора 15. При этом в поле команды, которое подается на общую шину команд, соединенную с тре буемым элементарным процессором 15 содержится код микрокоманды вьвдачи информации на выход центрального элемента 47, Так как в поле признаков микрокоманды устройства 14 управления записан код признаков, выполняющихся в данном элементарном процессоре 15, то второй 2И 25 открыт и микрокоманда выдачи информации проходит с седьмого входа требуемого элементарного процессора 15, поступает через второй элемент 2И 25 на первый вход центрального процессорного элемента 47 и выполняется им. Поле команд, которое подается на данный элементарный процессор 15, также содержит код режима элементарного процессора 15, содержащий в разряде, поступающем на шестой вход элементарного процессора 15, единицу, а в остальных разрядах - нули. Единичный сигнал с шестого входа подается на второй вход первого элемента 2И 24, на первьй вход которого поступает также единичный сигнал с выхода элемента 2ИЛИ 26, проходит через этот элемент 2И 25 и поступает на управляюпще входы шинных преобразователей 27 и 43, включая их. Тогда информация с четвертого выхода центрального процессорного элемента 47 через включенный шинный преобразователь 27 и код признаков из триггеров 33, 36 и 39 через включенный шинный формирователь 43 поступают соответственно на девятый вход-выход и третий выход элементарного процессора 15, соединенные с общей шиной данных.

Для вьшолнения операции S, . для осуществления приема информации элементарным процессором 15 от левого соседнего элементарного процессора 15, устройство 14 управления вьща- ет микрокоманду, содержащую в поле коммутаторов код, вклн чанщий шинный формирователь 93 устройства 14 управ10

20

торое подается на общую шину команд, соединенную с требуемым элементарным процессором 15, содержится код микрокоманды приема информации с третьего входа центрального процессорного элемента 47. В поле признаков микроко- . манды устройства 14 управления записан код признаков, выполняющихся в данном элементарном процессоре 15, поэтому второй элемент 2И 25 открыт и микрокоманда приема информации проходит с седьмого входа элементарного процессора 15 и поступает через вто15 рой элемент 2И 25 на первьй вход центрального процессорного элемента 47 и выполняется им. В поле команд, которое подается на данный элементарный процессор 15, записан код режима элементарного процессора 15, содержа- в разряде, поступакяцем на двенадцатый вход элементарного процессора 15, единицу, а в остальных разрядах - нули. Единичный сигнал с двенадцатого

25 входа поступает на второй вход элемента 2И 49, на первый вход которого также подается -единичный сигнал с выхода первого элемента 2ИЛИ 26, проходит через этот элемент 2И 49, посту-

30 пает на управляющий вход первого 50 и пятого 55 коммутаторов и включает их. При этом информация из регистров центрального процессорного элемента 47 левого элементарного процессора 15

„с поступает на тринадцатый вход нужоЬ,

ного элементарного процессора 1э, проходит через включенный коммутатор 50 и через блок элементов ИЛИ 51, поступает на третий вход центрального

40 процессорного элемента 47 и записывается в его регистрах, la информация из триггеров 33, 36 и 39 левого соседнего элементарного процессора 15 поступает с шестнадцатого входа рас45 сматриваемого элементарного процессора 15 на информационный вход включенного коммутатора 55, проходат через него, поступает на первый вход блока элементов ИЛИ 46, с выхода которого проходит на второй вход блока элементов ИЛИ 40,.с выходов которого поступает на входы триггеров 31, 34 и 37 и записывается в них.

При выполнении операции S, т.е.

50

ления, через который четыре поля ко- осуществлении приема информации

манд, поле маски и поле признаков по-элементарным процессором 15 от праводаются на соответствующие общие шиныго соседнего элементарного процессоассоциативного параллельного процес-ра 15, устройство 14 управления выдасора 4. При этом в поле комацды, ко- :ет микрокоманду, содержащую в поле

0

торое подается на общую шину команд, соединенную с требуемым элементарным процессором 15, содержится код микрокоманды приема информации с третьего входа центрального процессорного элемента 47. В поле признаков микроко- . манды устройства 14 управления записан код признаков, выполняющихся в данном элементарном процессоре 15, поэтому второй элемент 2И 25 открыт и микрокоманда приема информации проходит с седьмого входа элементарного процессора 15 и поступает через вто5 рой элемент 2И 25 на первьй вход центрального процессорного элемента 47 и выполняется им. В поле команд, которое подается на данный элементарный процессор 15, записан код режима элементарного процессора 15, содержа- в разряде, поступакяцем на двенадцатый вход элементарного процессора 15, единицу, а в остальных разрядах - нули. Единичный сигнал с двенадцатого

5 входа поступает на второй вход элемента 2И 49, на первый вход которого также подается -единичный сигнал с выхода первого элемента 2ИЛИ 26, проходит через этот элемент 2И 49, посту-

0 пает на управляющий вход первого 50 и пятого 55 коммутаторов и включает их. При этом информация из регистров центрального процессорного элемента 47 левого элементарного процессора 15

с поступает на тринадцатый вход нужЬ,

ного элементарного процессора 1э, проходит через включенный коммутатор 50 и через блок элементов ИЛИ 51, поступает на третий вход центрального

0 процессорного элемента 47 и записывается в его регистрах, la информация из триггеров 33, 36 и 39 левого соседнего элементарного процессора 15 поступает с шестнадцатого входа рас45 сматриваемого элементарного процессора 15 на информационный вход включенного коммутатора 55, проходат через него, поступает на первый вход блока элементов ИЛИ 46, с выхода которого проходит на второй вход блока элементов ИЛИ 40,.с выходов которого поступает на входы триггеров 31, 34 и 37 и записывается в них.

При выполнении операции S, т.е.

50

19

коммутаторов код, включающий второй шинный формирователь 93 устройства 1 управления, через который четыре поля команд, поле маски и поле признаков подаются на соответствующие шины ассоциативного процессора 4. При это в поле команды, которое подается на общую шину команд, соединенную с требуемым элементарным процессором 1 5, содержится код микрокоманды приема информации с третьего входа центрального процессорного элемента 37. В поле признаков микрокоманды устройства 14 управления записан код признаков, вьтолняющихся в требуемом элементар ном процессоре 15, поэтому элемент 2 25 открыт и микрокоманда приема информации проходит с седьмого входа элементарного процессора 15 и поступает через элемент 2И 25 на первый вход центрального процессорного элемента 47 и выполняется им. В поле команд, которое поступает на данньш элементарный процессор 15, записан код режима элементарного процессора 15, содержащий в разряде, поступаняце на пятнадцатый вход элементарного процессора 15, единицу, а в остальных разрядах - нули. Единичный сигнал с пятнадцатого входа поступает на второй вход элемента 2И 53, на первый вход которого также подается единичный сигнал с выхода элемента 2ИЛИ 26, При этом на выходе элемента 2И 53 возникает единичный сигнал, который поступает на управляющие входы коммутаторов 52 и 54, в результате чего оба коммутатора оказываются во включенном состоянии. Тогда информация из регистров центрального процессорного элемента 47 правого элементарного процессора 5 проходит через коммутатор 52 и блок элементов ИЛИ 51, поступает на третий вход центрального процессорного элемента 47 и записывается в его регистрах, а информация из триггеров 33, 36 и 39 правого соседнего элементарного процессора 15 поступает с семнадцатого входа требуемого элементарного процессора 15 на вход включенного четвертого коммутатора 54, проходит через него, поступает на второй вход третье го блока элементов ИЛИ 46, с-.

выхода которого проходит на второй вход блока элементов ИЛИ 40, с выходов которого поступает на входы тригге- ров 31 ,34 и 37 и записьшается в них.

34420

При выполнении операции Sj. в любом элементарном процессоре 15,т.е. при осуществлении выдачи информации в ле- вый и правый соседние элементарные процессоры 15, устройство 14 управления вьщает микрокоманду, содержащую в поле коммутаторов код, включающий рлинный формирователь 93 устройства 14

управления, через который четыре поля команд, поле маски и поле признаков подаются на соответствующие общие шины ассоциативного параллельного процессора 4. При этом в поле команды,которое поступает на общую шину микрокоманд, соединенную с требуемым элементарным процессором 15, содержится код микрокоманды выдачи информации на третий выход центрального

процессорного элемента 47, который соединен с десятым выходом элементарного процессора 15. В поле признаков записан код признаков, выполняющихся в данном элементарном процессоре 15,

поэтому элемент 2И 25 открыт и микрокоманда вьщачи 1шформации в соседние элементарные процессоры 15 проходит с седьмого входа элементарного процессора 15 и поступает через элемент

2И 25 на первый вход центрального

процессорного элемента 47 и выполня- i ется им, в результате чего на десятом выходе элементарного процессора 15 появляется информация из регистров

центрального процессорного элемента 47. Десятый требуемого элементарного процессора 15 соединен с четырнадцатым выходом левого соседнего элементарного процессора 15 и тринадцатым входом правого соседнего элементарного процессора 15, поэтому информация из регистров центрального процессорного элемента 47 требуемого элементарного процессора 15 поступает на указанные входы соседних элементарных процессоров 15. Выходы : триггеров 33, 36 и 39 требуемого элементарного процессора 15 соединены с вторым выходом элементарного процессора 15, который подключен к семнадцатому входу левого соседнего элементарного процессора I5 и шестнадцатому входу правого соседнего элементарного процессора 15, благодаря чему

информация из этих триггеров поступает на указанные соседних элементарных процессоров 15. В поле команды, которое поступает на данный элементарный процессор 15, записан

21

К1)Д режима элементарного процессора 1$, содержащий во всех разрядах нули.

Операции S являются внутренними операциями элементарного процессора 1$, которые выполняются в самом элементарном процессоре 15 без взаимо- дфйствия с другими элементарными про- ц ссорами 15, либо без взаимодействия с другими вычислительными блоками ВJM. При выполнении этих операций устройство 14 управления выдает микрокоманду, содержащую в поле коммутаторов код, включающий шинный

145534422

элемента 2И 41 поступает единичный . сигнал с выхода первого элемента 2ИЛИ 26. С четвертого входа элементарного процессора 15 единичный сигнал поступает на первый вход элемента 2И 41, При этом на выходе элемента 2И 41 образуется единичный сигнал, который поступает на вторые входы элементов 10 2И 32, 35 и 38, благодаря чему информация, .хранящаяся в триггерах 31, 34 и 37 и подающаяся на первые входы соответственно элементов 2Н 32, 35 и 38, проходит через эти элементы и

20

ф,рмирователь 93 устройства 14 управ- 15 поступает на входь, соответственно 4ния; через который четьфе поля ко-триггеров 33, 36 и 39 и записывается

м|анд, поле маски и поле признаков по- iдаются на соответствующие общие шины ассоциативного п&раллельного процессора 4. При этом в поле команды, кот 1 рое подается на общую шину микроманд, соединенную с требуемым эле- . нтарным процессором 15, содержится Код микрокоманды, необходимый для вы- п|олнения требуемой операции. В поле физнаков записан код признаков, вы- 1(олняющихся в данном элементарном Процессоре 15, поэтому элемент 2И 25

f - г

в НИХ. Центрапьный процессорньй элемент 47 данного элементарного процессора 15 может в это время вьшолнять операцию, соответствующую микрокоманде, подающейся на седьмой вход элементарного процессора 5.

ВВМ выполняет следующие команды: 25 F - прием кода элементарным процессором 15 с общей шинь: данных;

F - выдача кода из элементарного процессора 15 на общую шину данных;

с|ткрыт и микрокоманда для элементарF - сдвиг информации, записанной

ткрыт и микрокоманда для элементар- j ... ,

.его. процессора 15 проходит с седьмо- 30 в-;-«-Р™1ГГ-Г.:;;. Г входа элементарного процессора I) поступает через второй элемент 2И

один элементарный процессор i 5 в сторону первого элементарного процессо5 на первый вход центрального про- ра 1 „««г й

рессорного элемента 47 и вьшолняется сдвиг информации,записанной L. В данном случае в поле комавд за- 35 элементарных процессорах 15 на . |исан код режима элементарного про- один элементарный процессор . 5 в сто рессора 15, содержащий во всех разря- kax нули.

При вьшолнении операции S, т.е. Йри осуществлении перезаписи призна- 40 «сов, устройство 14 управления вьщает микрокоманду, содержащую в поле ком- Мутаторов код, включающий шинньй формирователь 93 устройства 14 управления, через который четыре поля ко- , 45 Манд, поле маски и поле признаков Подаются на соответствующие общие шины параллельного процессора 4, При этом в поле команд, которое подается на общую шину команд, соединенную с 50 требуемым элементарным процессором 15, содержится код режима элементарного процессора 15, содержащий в разряде , поступающем на четвертый вход элементарного процессора 15, единицу, 55 а в остальных разрядах - нули. В поле признаков записан код признаков, выполняющихся в данном элементарном процессоре 15, поэтому на второй вход

рону последнего элементарного процессора 15;

F - вычисления в ассоциативном параллельном процессоре 4;

F, - запись информации из ассоциативного параллельного процессорного 4 ;в арифметическое устройство 7;

F- - запись информации из арифметического устройства 7 в ОЗУ 87 устройства 14 управления;

F. - запись информации из ассоциативного параллельного процессора 4 в

таблицу 9;

Fq выдача случайных чисел в требуемое устройство вычислительной машины;

F,g - выдача случайных чисел с заданной вероятностью в требуемое устройство вычислительной машины;

F, - команда для арифметического устройства 7;

поступает на входь, соответственно триггеров 33, 36 и 39 и записывается

f - г

в НИХ. Центрапьный процессорньй элемент 47 данного элементарного процессора 15 может в это время вьшолнять операцию, соответствующую микрокоманде, подающейся на седьмой вход элементарного процессора 5.

ВВМ выполняет следующие команды: 25 F - прием кода элементарным процессором 15 с общей шинь: данных;

F - выдача кода из элементарного процессора 15 на общую шину данных;

F - сдвиг информации, записанной

j ... ,

30 в-;-«-Р™1ГГ-Г.:;;. Г

сдвиг информации,записанной элементарных процессорах 15 на . один элементарный процессор . 5 в сто

рону последнего элементарного процессора 15;

F - вычисления в ассоциативном параллельном процессоре 4;

F, - запись информации из ассоциативного параллельного процессорного 4 ;в арифметическое устройство 7;

F- - запись информации из арифметического устройства 7 в ОЗУ 87 устройства 14 управления;

F. - запись информации из ассоциативного параллельного процессора 4 в

таблицу 9;

Fq выдача случайных чисел в требуемое устройство вычислительной машины;

F,g - выдача случайных чисел с заданной вероятностью в требуемое устройство вычислительной машины;

F, - команда для арифметического устройства 7;

23

F,j, - команда проверки условия разветвления программы по содержимому счетчика числа испытаний 13.

14

Команда F, содержит указание о вы- полнении операции S,

Команда F содержит указание о выполнении операции S.

При вьшолнении команды Fj информация, хранящаяся в регистрах центрального процессорного элемента 47 каждого элементарного процессора 15, в котором выполняются требуемые признаки, переписьшается в левый соседний

операцию S, процессоры I5 операцию

S5 выполняют элементарные с четными номерами, а с нечетными номерами.

g На третьем этапе всеми элементарным

п р оце ее ор ами 15 ются операции Sg Операция S, в

одновременно выполн и S, . данном случае закл

10

элементарный проце-ссор 15. Вьшолнение 15 информация.

чается в переписывании вновь записа ной ин.формации из регистров централ ных процессорных элементов 47, куда она быпа записана, в регистры тех ж центральных процессорных элементов 47, в которых быпа записана прежняя

этой команды происходит последовательно в три этапа. На первом этапе происходит одновременное выполнение операции S и S двумя равными группами элементарных процессоров 15, причем операцию S вьшолняют элементарные процессоры 15 с нечетными номерами, а операцию S - с четными но мерами. На втором этапе осуществляется одновременное выполнение этих же операций, однако в этом случае операцию S вьтолняют элементарные 15

Команда Fg. содержит указание о в полнении операции Sg.

Дпя выполнения команды F в поле арифметического устройства 7 записан

20 код микрокоманды записи информации, поступающей на вход арифметического устройства 7 с общей шины данных ассоциативного параллельного процессора 4, и код маски. При этом информа25 ция из ассоциативного параллельного процессора 4 записывается в регистрах арифметического устройства 7.

процессоры 15 с четными номерами, а операцию Sj - с нечетными номерами. На третьем этапе всеми элементарными 30 процессорами 15 одновременно выполняются операции Sg и S. Операция Sg в данном случае заключается в переписывании вновь записанной информации . , „„. .

из регистров центральных процессорных 35 ать информацию из арифметического элементов 47 элементарных процессо- устройства 7. Сформированный таким ров 15, в которых она быпа записана, в регистры центральных процессорных элементов 47, в которых хранилась

Для выполнения команды F в полях арифметического устройства 7 первых микрокоманд записаны коды микрокоманд и коды маски, необходимые для формирования адреса ячейки ОЗУ 87, входящего в состйв устройства 14 управления, в которую необходимо запипрежняя: (информация,

При выполнении команды F информация, хранящаяся в регистрах центрального процессорного элемента 47 каждого элементарного процессора 15, в

образом адрес ячейки заносится в регистр адреса арифметического устройства 7. Следующая микрокоманда содер 40 жит в поле ОЗУ 87 код, переводящий это устройство в режим приема информации, а в поле арифметического устройства 7 содержится код микрокоманды выдачи информации на выход арифме

котором выполняются требуемые призна- 45 тического устройства 7, который подки, переписывается в правый соседний элементарный процессор 15, в котором также выполняются эти признаки. Выполнение этой команды происходит последовательно в три этапа. На первом этапе: происходит одновременное выполнение операций S, и 8 двумя разными группами элементарных процессоров 15, причем операцию 8 выполняют элементарные процессоры 15 с нечетными

S

номерами, а операцию 8 - с четными

номерами. На втором этапе осуществляется одновременное вьшолнение этих же операций, однако в этом случае

ключен к информационному входу ОЗУ 87, адресный вход которого подключен к вькоду арифметического устройства 7, и информация из арид етического

50 устройства 7 переписывается в ОЗУ 87 по нужному адресу.

Для выполнения команды Fg в поле коммутаторов записан код, включающий второй 93 и третий 95 шинные форми55 рователи, в поле операционных устройств записан код, переводящий блок памяти констант 9 в режим приема информации, а в поле команд записан код команды выдачи чисел ассоциатив

55344

операцию S, процессоры I5 операцию

24

S5 выполняют элементарные с четными номерами, а с нечетными номерами.

g На третьем этапе всеми элементарными

п р оце ее ор ами 15 ются операции Sg Операция S, в

одновременно выполня- и S, . данном случае заклю

информация.

чается в переписывании вновь записанной ин.формации из регистров центральных процессорных элементов 47, куда она быпа записана, в регистры тех же центральных процессорных элементов 47, в которых быпа записана прежняя

Команда Fg. содержит указание о выполнении операции Sg.

Дпя выполнения команды F в поле арифметического устройства 7 записан

0 код микрокоманды записи информации, поступающей на вход арифметического устройства 7 с общей шины данных ассоциативного параллельного процессора 4, и код маски. При этом информа5 ция из ассоциативного параллельного процессора 4 записывается в регистрах арифметического устройства 7.

0 . , „„. .

Для выполнения команды F в полях арифметического устройства 7 первых микрокоманд записаны коды микрокоманд и коды маски, необходимые для формирования адреса ячейки ОЗУ 87, входящего в состйв устройства 14 управления, в которую необходимо запи35 ать информацию из арифметического устройства 7. Сформированный таким

образом адрес ячейки заносится в регистр адреса арифметического устройства 7. Следующая микрокоманда содер- 40 жит в поле ОЗУ 87 код, переводящий это устройство в режим приема информации, а в поле арифметического устройства 7 содержится код микрокоманды выдачи информации на выход арифме45 тического устройства 7, который под45 тического устройства 7, который подключен к информационному входу ОЗУ 87, адресный вход которого подключен к вькоду арифметического устройства 7, и информация из арид етического

50 устройства 7 переписывается в ОЗУ 87 по нужному адресу.

Для выполнения команды Fg в поле коммутаторов записан код, включающий второй 93 и третий 95 шинные форми55 рователи, в поле операционных устройств записан код, переводящий блок памяти констант 9 в режим приема информации, а в поле команд записан код команды выдачи чисел ассоциатив25

Ного параллельного процессора 4. Код tionn операционных устройств, являю- |цийся командой для блока памяти кон- 1станТу через включенный шинный форми- |рователь 95 поступает на вход команд блока 68 MHKponpprpaMfffloro управпе- с; ния, входящего в состав блока памяти юнстант. При этом блок 68 микропрограммного управления считывает :i3 ПЗУ 69 код адреса нужной ячейки ОЗУ 70, входящего в состав блока па- пяти констант. Этот.код адаеса по- :тупает на адресный вход ОЗУ 70 и далее осуществляется считывание числа, хранящегося в ОЗУ 70 по этому адресу. Это число поступает на вто- юй вход первой схемы 8 сравнения. Ход, записанный в поле команд, вызывает выдачу числа из ассоциативного параллельного процессора,4 на его шину данных, которая подключена к пер- иому входу первой схемы 8 сравнения. Число из ОЗУ 70 блока памяти констант число из ассоциативного параллель- ijioro процессора 4 поступают на входы (|:хемы 100 совпадения, входящей в сос- первой схемы 8 сравнения. При Совпадении значений требуемых разря- ов этих чисел на выходе схемы 100 Совпадения возникает единичный сигнал, йоторый поступает на управляю- ций вход шинного формирователя 99, входящего в состав первой схемы 8 сравнения, и включает ее, благодаря г ему Число с первого входа первой схемы 8 сравнения проходит на ее ии- ход и далее поступает в сумматор 10. i сумматоре 10 в случае необходимости производится необходимая операция этим числом, после чего оно из Сумматора 10 поступает на вход ОЗУ 70, входящего в состав блока памяти Констант, и записывается в нем по ; дресу, определяемому микрокомандой, (Считываемой блоком 68 микропрограммного управления из ПЗУ 69. Если же значение разрядов сравниваемых чисел, йоступайщих на входа первой схемы 8 уравнения, не совпадают,т.о на выходе фхемы 100 совпадений, входящий в сос- taB первой схемы 8 сравнения, возникает нулевой сигнал, который выключа- йт.шинный формирователь 99, и число ассоциативного параллельного профессора 4 не проходит на вход сумма- topa 10 и, следовательно, не записы- Дается в ОЗУ 70, входящем в состав Йлока .памяти констант.

145534426

Для выполнения команды F. в поле

25

коммутаторов микрокоманды устройства 14 управления записан код, включаю- щий шинный формирователь 96, а в по- , ле операционных устройств записан I код перевода смесительного устройства 3 в режим вьщачи случайных чисел. Этот код Поля операционных устройств

fO поступает из ПЗУ 94, входящего в

состав 14 управления, через включенный шинный формирователь 96 в устрой ство 2 выборки, которое переводит смесительное устройство 3 в режим вы

15 дачи случайных чисел.

Дпя выполнения команда F используется микропрограмма, вызываемая этой командой из ПЗУ 94, входящего в состав устройства 14 управления.

20 Первые микрокоманды этой микропрограммы формируют в арифметическом устройстве 7 адрес случайного числа с заданной вероятностью, хранящегося в блоке 6 быстродействующей памяти, для чего эти микрокоманда допяаш содержать в .поле ари(етического устройства 7 коды , соответствующие микрокомандам формирования адреса чисел, хранящихся в ОЗУ 87, входящем

30 в состав устройства 14 управления, я необходимых для формирования адреса случайного числа с заданной вероятностью, а в папе ОЗУ 87 должны быть записаны коды, определяющие адреса и

35 режим выдачи чисел из ОЗУ 87 в арифметическое устройство 7, где эти чис ла преобразуются з адрес случайного числа с заданной вероятностью, который остается в регистре адаеса ариф40 метического устройства 7. Следующая микрокоманда считывает случайное чис ло из блока 6 быстродействующей памяти в ари етическое устройство 7, для чего в поле арифметического устройст45 за 7 должен быть записан код, соответствующий микрокоманде записи информации в арифметическое устройство 7 из блока 6 быстродействующей памяти. Последняя микрЪкоманда микропрог50 раммы должна содержать в поле арифметического устройства 7 код, соот- ветствуниций микрокоманде выдачи случайного числа с заданной вероятностью из арифметического устройства 7

55 в требуемое устройство ВБМ.

Для выполнения команды V .в поле арифметического устройства 7 должен быть записан код, соответствующий микрокоманде арифметического устрой5

коммутаторов микрокоманды устройства 14 управления записан код, включаю- щий шинный формирователь 96, а в по- , ле операционных устройств записан I код перевода смесительного устройства 3 в режим вьщачи случайных чисел. Этот код Поля операционных устройств

O поступает из ПЗУ 94, входящего в

состав 14 управления, через включен . ный шинный формирователь 96 в устройство 2 выборки, которое переводит смесительное устройство 3 в режим вы5 дачи случайных чисел.

Дпя выполнения команда F используется микропрограмма, вызываемая этой командой из ПЗУ 94, входящего в состав устройства 14 управления.

0 Первые микрокоманды этой микропрограммы формируют в арифметическом устройстве 7 адрес случайного числа с заданной вероятностью, хранящегося в блоке 6 быстродействующей памяти, для чего эти микрокоманда допяаш содержать в .поле ари(етического устройства 7 коды , соответствующие микрокомандам формирования адреса чисел, хранящихся в ОЗУ 87, входящем

0 в состав устройства 14 управления, я необходимых для формирования адреса случайного числа с заданной вероятностью, а в папе ОЗУ 87 должны быть записаны коды, определяющие адреса и

5 режим выдачи чисел из ОЗУ 87 в арифметическое устройство 7, где эти чис - ла преобразуются з адрес случайного числа с заданной вероятностью, который остается в регистре адаеса ариф0 метического устройства 7. Следующая микрокоманда считывает случайное число из блока 6 быстродействующей памяти в ари етическое устройство 7, для чего в поле арифметического устройст5 за 7 должен быть записан код, соответствующий микрокоманде записи информации в арифметическое устройство 7 из блока 6 быстродействующей памяти. Последняя микрЪкоманда микропрог0 раммы должна содержать в поле арифметического устройства 7 код, соот- ветствуниций микрокоманде выдачи случайного числа с заданной вероятностью из арифметического устройства 7

5 в требуемое устройство ВБМ.

Для выполнения команды V .в поле арифметического устройства 7 должен быть записан код, соответствующий микрокоманде арифметического устрой27

ства 7, которая вызьшает в нем выполнение операции, определяемой командой F .

Для выполнения команды Ъ исполь зуется микропрограмма, первая микрокоманда которой содержит в поле коммутаторов код, включающий шинный фор мирователь 97 устройства 14 управпе- ния, а в поле операционных устройств записан код, увеличивающий содержимое счетчика 13 числа испытаний на единицу. При этом код, записанный в поле операционных- усгройств проходит через включенный пятый шинный формирователь 97 на вход счетчика числа испытаний 13 и увеличивает содержимое этого счетчика на единицу. Вторая микрокоманда содержит в поле коммутаторов код, включающий элемент 2И 98 и мультиплексор 92 на пропускание сигнала с выхода элемента 2И 98 на вход блока 91 микропрограммного управления. При этом сигнал с выхода второй схемы сравнения через включенный элемент 2И 98 и мультиплексор 92 поступает на вход блока 91 микропрограммного управления, входящего в состав устройства 14 управления. На выходе второй схемы 12 сравнения формируется единичный сигнал в случае равенства содержимого счетчика 13 числа испытаний и регистра 11, в противном случае на ее выходе образуется нулевой сигнал. При вьтолнении следующих микрокоманд в блоке 91 микропрограммного управления, входящего в состав устройства 14 управления, анализирует сигнал, поступивший на его вход, и если этот сигнал - нулевой, то ВВМ переходит к выполнению следующей команды , а если этот сигнал - единичный, то выполняется другая команда, входящая в подпрограмму окончания вычислений.

Формула изобретения

1455344

28

подключены к информационным входам - устройства формирования случайных чисел, выход устройства выборки соеди- g нен с управляющ1ж входом устройства формирования случайных чисел, выход которого подключен к информационному входу арифметического устройства, первый и второй информационные выхо- 10 ды арифметического устройства которого соединены с информационными входами устройства выборки и регистра соответственно, первый, второй и третий входы-выходы арифметического устрой- 15 ства соединены с первыми входами-выходами датчика случайных чисел с условной вероятностью блока памяти и первым входом первой схемы сравнения соответственно, второй вход-выход 20 датчика случайных чисел с условной вероятностью подключен к второму входу-выходу блока памяти, второй вход первой схемы сравнения соединен с выходом блока памяти констант, вход-вы- 25 ход которой подключен к входу-выходу сумматора, вход которого соединен с первым выходом проверки признака первой схемы сравнения, вход записи числа испытаний регистра является одно- 30 именным входом вероятностной вычис- лительной машины, а выход регистра соединен с первым входом второй схемы сравнения, выход счетчика числа испытаний соединен с вторым входом 3g второй схемы сравнения, первый и второй входы устройства управления соединены с вторым выходом проверки признака первой и выходом признака равенства второй схем сравнения соот- 40 ветственно, первый, второй,-третий и четвертый выходы устройства управления подключены к входам управления устройства выборки арифметического устройства, блока памяти констант и 5 счетчика числа испытаний, отличающаяся тем, что, с целью повышения быстродействия, в нее введен ассоциативный параллельный процессор, информационный вход которого 0 соединен с выходом устройства формирования случайньпх чисел, а вход-выход подключен к третьему входу-выходу арифметического устройства к первому входу первой схемы сравнения и 5 пятому выходу устройства управления.

дом М-М элементарном процессоре (М 2,.,.,Н) вход данных, вход-выход данных и выход данных через шину данных подключены к информационному вхо- ду ассоциативного параллельного Процессора, вход признаков от (H-l)-ro элементарного процессора, вход-выход данных и выход данных первого элементарного процессора подключены через шину данных к информационному входу ассоциативного параллельного процессора, ВХОДО1 команд первого элементарного процессора через шину команд первого элементарного процессора, входы команд каждого К-го элементарного процессора (К 2Н, 2 К Н) через первую шину команд, входы команд каждого R-ro элементарного процессора (R 2H+I, ) через вторую шину команд, входы команд Н-го элементарного процессора через шину команд последнего элементарного процес- 1 сора соеданены с соответствующими I разрядами комацд входа-выхода ассо- Iциативного параллельного Процессора, I вход признака первого элементарного I процессора через шину признака перво- |го элементарного процессора, вход I признака второго элементарного про- |цессора через шину признака второго элементарного процессора, вход признаков каждого L-ro элементарного Iпроцессора () через шину прия

jзнаков, вход признака, последнего эле- 35 Ризнака первого и второго элементар|ментарного процессора через шину ус- Iтановки признака Последнего элемен- I тарного процессора подключены к соот- Iветствующим разрядам признаков входа- ; выхода ассоциативного пар-аллельного процессора, вход маски каждого Н-го элементарного процессора через шину маски соединен с разрядом маски входа-выхода ассоциативного параллельного процессора, выход данных к соседним элементарным процессорам каждого Р-го элементарного процессора (2 Р Н) соединен с соответствующими входами (P-l)-ro и (Р+1)-го элементар- ных процессоров, выход данных к соседним элементарным процессорам первого элементарного процессора соединен с соответствующим входом второго элементарного процессора, выход данных процессоров, а выход соединен с первыми входами первого, второго, седьмого, восьмого, девятого элементов 2И и четвертого элемента ,

40 вторые входы которых являются соот- ветствующими входами команд элементарного процессора, выход первого элемента 2И подключен к первым управ лякяцим входам первого и второго шин-

45 ных формирователей, выход второго элемента 2И подключен к управляющему входу центрального процессорного элемента, выход седьмого элемента 2И соединен с первыми входами четверто50 го, пятого и шестого элементов 2И, выход восьмого элемента 2И подключен к первым входам первого и пятого коммутаторов, выход девятого элемента 2И соединен с первыми входами второго и

ных к соседним элементарным процессо- 55 четвертого коммутаторов, выход чет- рам последнего Н-го элементарного - вертого элемента 2ШШ подключен к процессора соединен с соответствующим входом (H-l)-ro элементарного процессора, выход признаков к элеменпервому входу третьего коммутатора, второй вход которого является входом признаков элементарного процессора.

10

g

5534430

тарным процессорам каждого Р-го элементарного процессора подключен к со- ответствумцим Входам (P-l)-ro и (Р+1)-го элементарных процессоров, выход признаков к элементарным процессорам первого элементарного процессора подключен к соответствующему входу второго элементарного процессора, выход признаков к элементарным процессорам последнего Н-го элементарного процессора подключен к соответствующему входу (H-l)-ro элементарного процессора, причем каждый

15 элементарный процессор содержит дешифратор, два элемента 2-2-2-ЗИ-4ИЛИ- НЕ, три элемента 3-ЗИ-2ИЛИ-НЕ, элемент 4-4И-2ИЛИ-НЕ, элемент 6И-НЕ, девять элементов 2И, четыре элемен20 та 2ИЛИ, первый и второй шинные формирователи, семь триггеров, три блока элементов ИЛИ, пять коммутаторов, центральный процессорный элемент и схему ускоренного переноса, причем

25 вход признаков L-ro элементарного процессора соединен с входом дешифратора, выходы которого подключены к первым входам соответствукщих элемен- тов 2-2-2-ЗИ-4ИЛИ-НЕ, 3-ЗИ-2ШШ-НЕ,

30 4-4И-2ИЛИ-НЕ, выходы которых соединены с соответствуищими входами элемента 6И-НЕ, выход которого подключен к первому входу первого элемента 2Ш1И, второй вход которого является входом

ных процессоров, а выход соединен с первыми входами первого, второго, седьмого, восьмого, девятого элементов 2И и четвертого элемента ,

вторые входы которых являются соот- ветствующими входами команд элементарного процессора, выход первого элемента 2И подключен к первым управ лякяцим входам первого и второго шин-

ных формирователей, выход второго элемента 2И подключен к управляющему входу центрального процессорного элемента, выход седьмого элемента 2И соединен с первыми входами четвертого, пятого и шестого элементов 2И, выход восьмого элемента 2И подключен к первым входам первого и пятого коммутаторов, выход девятого элемента 2И соединен с первыми входами второго и

четвертого коммутаторов, выход чет- вертого элемента 2ШШ подключен к

первому входу третьего коммутатора, второй вход которого является входом признаков элементарного процессора.

31

а выход соединен с первым входом вто-, роге блока элементов ИЛИ, первый, второй и третий выходы второго блока элементов ИЛИ подключены к установочным входам первого, второго и третьего триггеров соответственно, выходы которых соединены с вторыми входами четвертого, пятого и шестого элементов 2И соответственно, выходы которых подключены к установочным входам четвертого, пятого и шестого триггеров соответственно, вход-выход данных элементарного процессора соединен с входом данных центрального процессорного элемента и выходом данных -первого шинного формирователя, второй вход которого подключен к выходу данных центрального процессорного элемента, вход маски элементарного процессора является входом маски центрального процессорного элемента, вход и выход переноса которого соединены с выходом и входом схемы уско10

145534432

блока элементов ШШ, выход которог подключен к второму входу второго блока элементов ИЛИ, выход данных н элементарные процессоры центральног процессорного элемента является одноименным выходом элементарного про цессора, выход признака центральног процессорного элемента соединен с установочным входом седьмого тригге ра, прямой выход которого соединен вторыми входами схем 2-2-2-ЗИ-4ИЛИ- НЕ, 3-ЗИ-2ИЛИ-НЕ и выходом признако к элементарным процессорам, инверс 5 ный выход седьмого триггера соедине с первыми входами второго и третьег элементов ИЛИ, прямой выход шестого триггера подключен к третьим входам элементов 2-2-2-ЗИ-4ИЛИ-НЕ, первого 20 элемента 3-ЗИ-2ИЛИ-НЕ, первому вход второго шинного формирователя и выходу признаков к элементарным проце сорам, инверсный выход шестого триг гера соединен с вторыми входами тре

30

панЗ°оГ Г|Г . «-°Д 25 ,,его элемента 2И, третьего элемен- I f -« н Рного про- ,а 2ИПИ и седььш,м входом элемента цессора является вторым входом перво- го коммутатора, выход которого соединен с первым входом первого блока элементов ИЛИ, вход данных от (Р+1)- го элементарного процессора является вторым входом второго коммутатора, выход которого соединен с вторым входом первого блока элементов ИЛИ, выход которого подключен к входу данных от элементарных процессоров центрального процессорного элемента,вход признаков от (P-l)-ro элементарного процессора соединен с пятым входом элемента 4-4И-2ИЛИ-НЕ и с вторым входом пятого коммутатора, выход которого соединен с первым входом третьего блока элементов ИЛИ, вход признаков от (Р+1)-го элементарного процессора соединен с шестым входом элемента 4-4И-2ИЛИ-НЕ, пятым входом третьего элемента 3-ЗИ-2ИЛИ-НЕ и вторым входом четвертого коммутатора, выход которого соединен с вторым входом третьего