Изобре -ение относится к измерительной гехнике и может быть использовано в качестве канала измерительной системы для контроля цифровых микросхем и блоков с двунаправленными выводами. .

Цель изобретения - повьпиение быстродействия и точности контроля за счет согласования выходного сопротивления усгройства с волновым сопротивлением линии передачи как при задании стимулирующих воздействий, так и при приеме ответного сигнала контролируемой схемы.

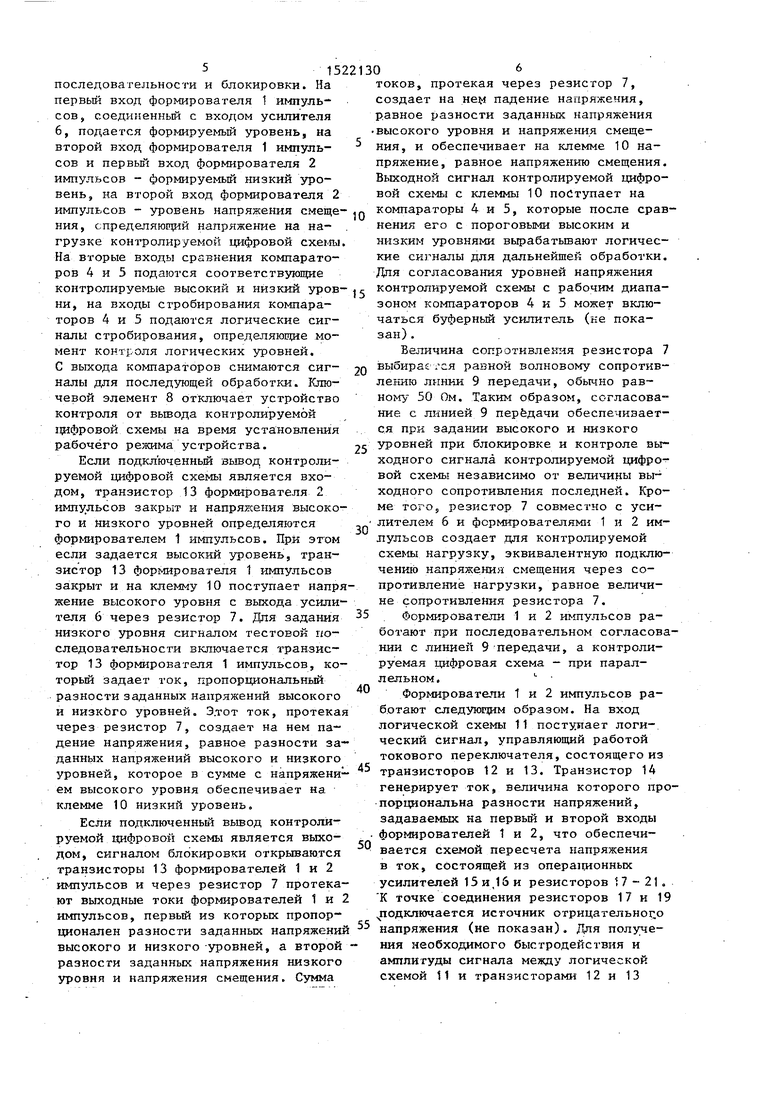

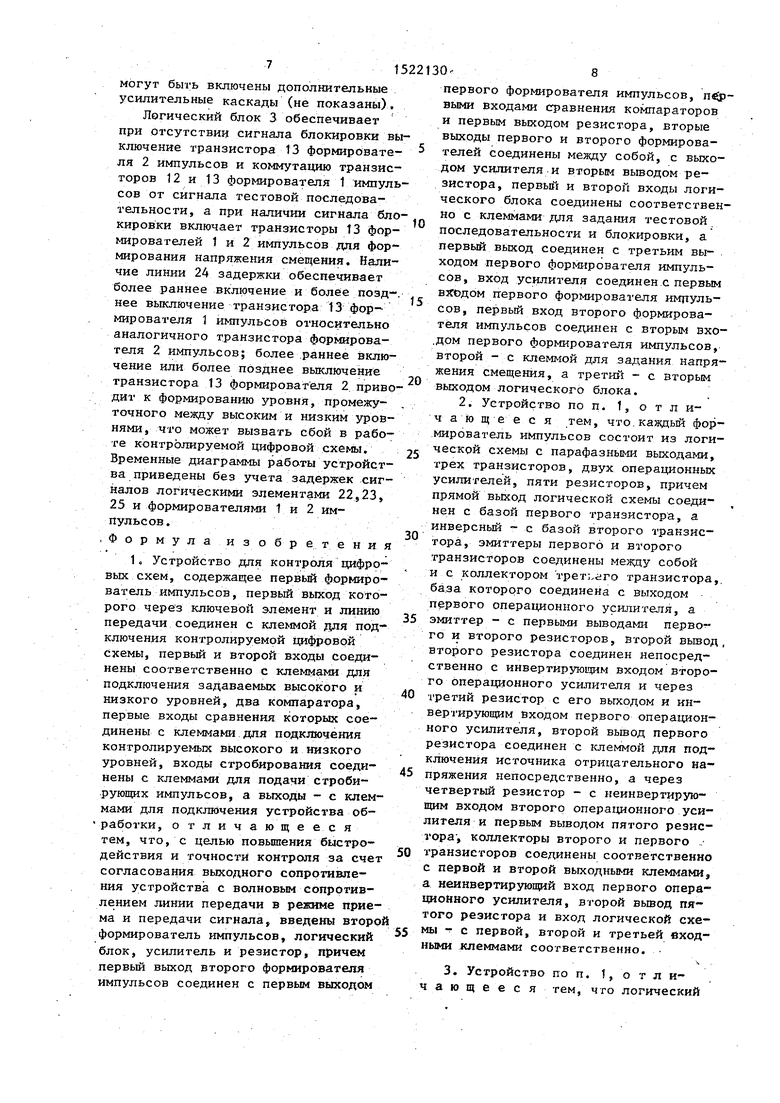

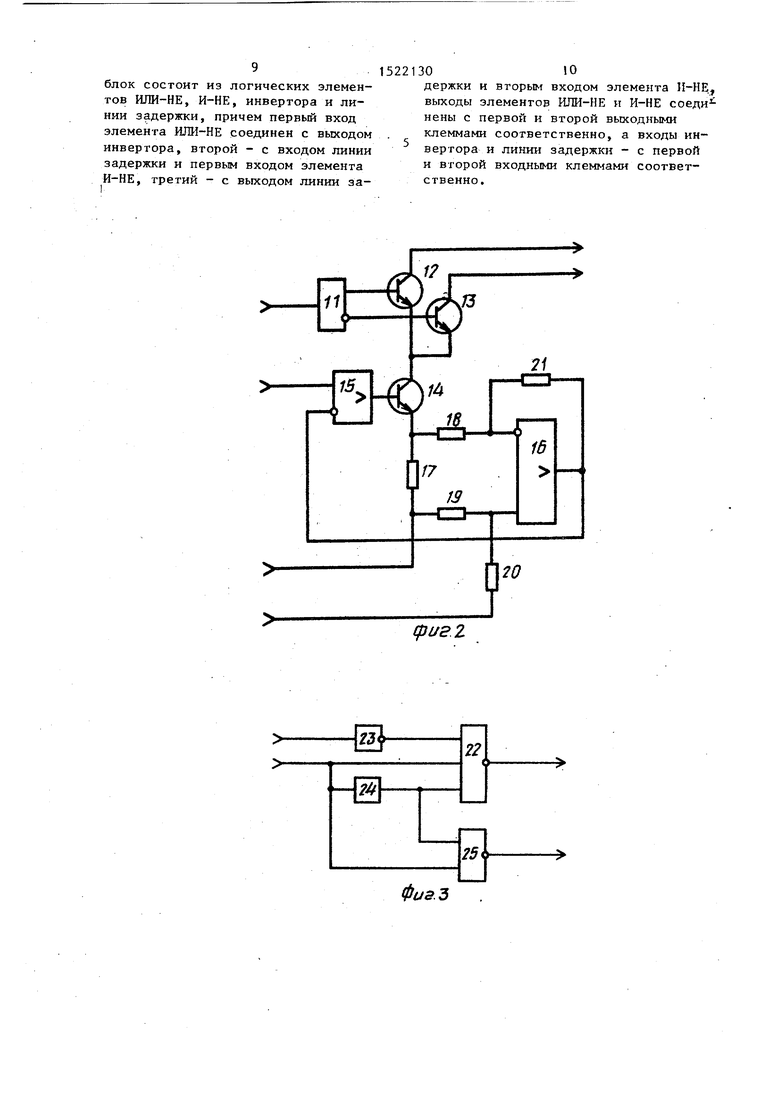

На фиг. 1 представлена структурная схема усч ройстпа; на фиг. 2 - схема формирователя импульсов; на фиг, 3 - схема логического блока; на фиг. 4 - временные диаграммы работы устройства.

Устройство содержит формирователи 1 и 2 импульсов, логический блок 3, ком параторы 4 и 5, усилитель 6, резистор

10

1522130. л

торов А и 5 соединены соответственно с входными клеммами для подключения контролируемых высокого и низкого уровней, входы стробирования соединены с соответствующими входными клеммами для подачи стробирующих импульсов, а выходы - с выходнь1ми клеммами для подключения устройства обработки.

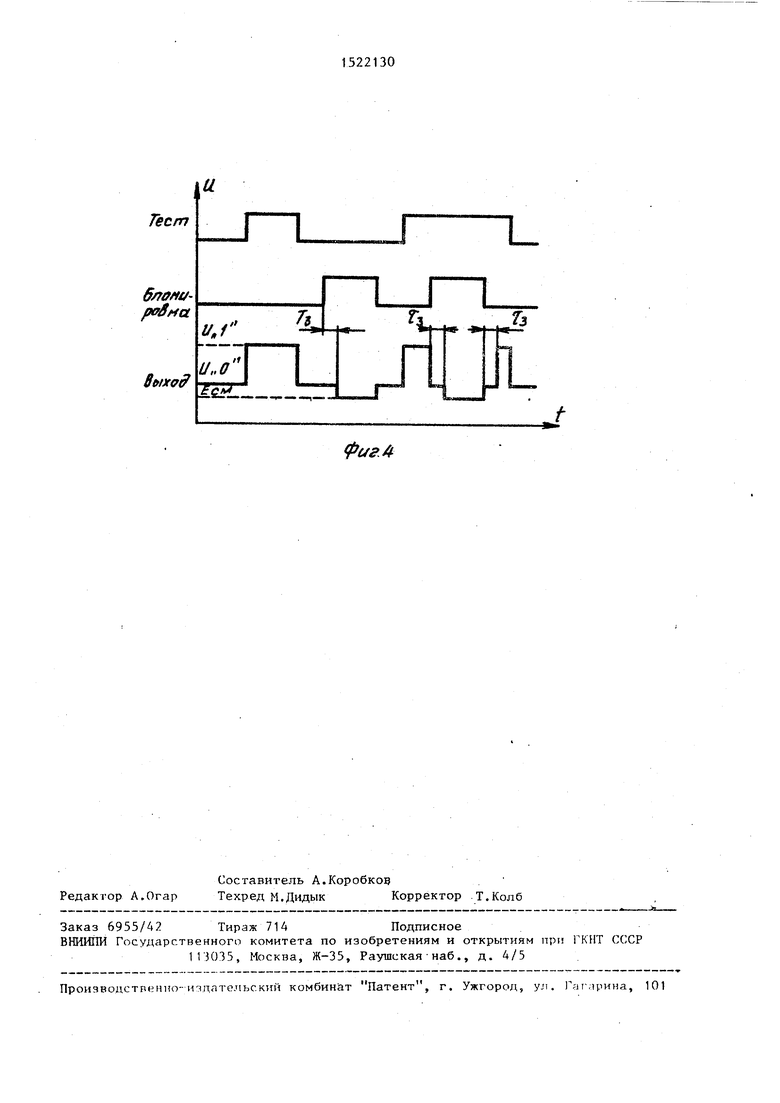

Прямой выход логической схемы 11 соединен с базой транзистора 12, а инверсньш - с базой транзистора 13, эмиттеры транзисторов 12 и 13 соединены между собой и с коллектором транзистора 14, база которого соединена с выходом операционного усилителя 15, а эмиттер - с первыми вьшо- дами резисторов 17 и 18, второй вывод резистора 18 соединен непосред- ственно с инвертирующим входом операционного усилителя 16 и через резистор 21 - с его выходом, которьш соединен также с инвертируюп им входом операхщоннрго усилителя 15, второй

7, ключевой элемент 8, линию 9 передачи и клемму .10. Формирователь 1 (2) 25 вывод резистора. 17 соединен непо- импульсов состоит из логической схемы средственно с клеммой для подключе- 11, транзисторов 12 - 14, операздионных ния источника отрицательного напря- усилителей 15 и 16, резисторов 17-21. жения и через резистор 19 с инвер- Логич:еский блок 3 вьшолнен в виде элемента ГШИ-НЕ 22, инвертора 23,

30

тируюишм входом операционного усилителя 16 и первым выводом резистора 20, коллекторы транзисторов 13 и 12 соединены соответственно с первой и второй выходными клеммами фop иpoвa- теля, а вход логической схемы 11, неинвертирующий вход операционного

30

линии 24 задержки и элемента И-НЕ 25

Первые выходы формирователей 1 и 2 импульсов соединены между собой, с первыми входами сравнения компара - торов 4 и 5, первыми выводами резистора 7 и ключевого элемента 8, второй 35 усилителя 15 и второй вывод резис- выход которого через линию 9 передачи тора 20 - с первой, второй и третьей

выходными клеммами формирователя

тируюишм входом операционного усилителя 16 и первым выводом резистора 2 коллекторы транзисторов 13 и 12 соединены соответственно с первой и второй выходными клеммами фop иpoвa- теля, а вход логической схемы 11, не инвертирующий вход операционного

соединен с клеммой 10 для подключения контролируемой цифровой схемы, вторые выходы формирователей 1 и 2 соединены между собой, с выходом усилителя 6 и вторым выводом резистора 7, первый и второй входы логического блока 3 соединены соответственно с клеммами для задания тестовой послесоответственно .

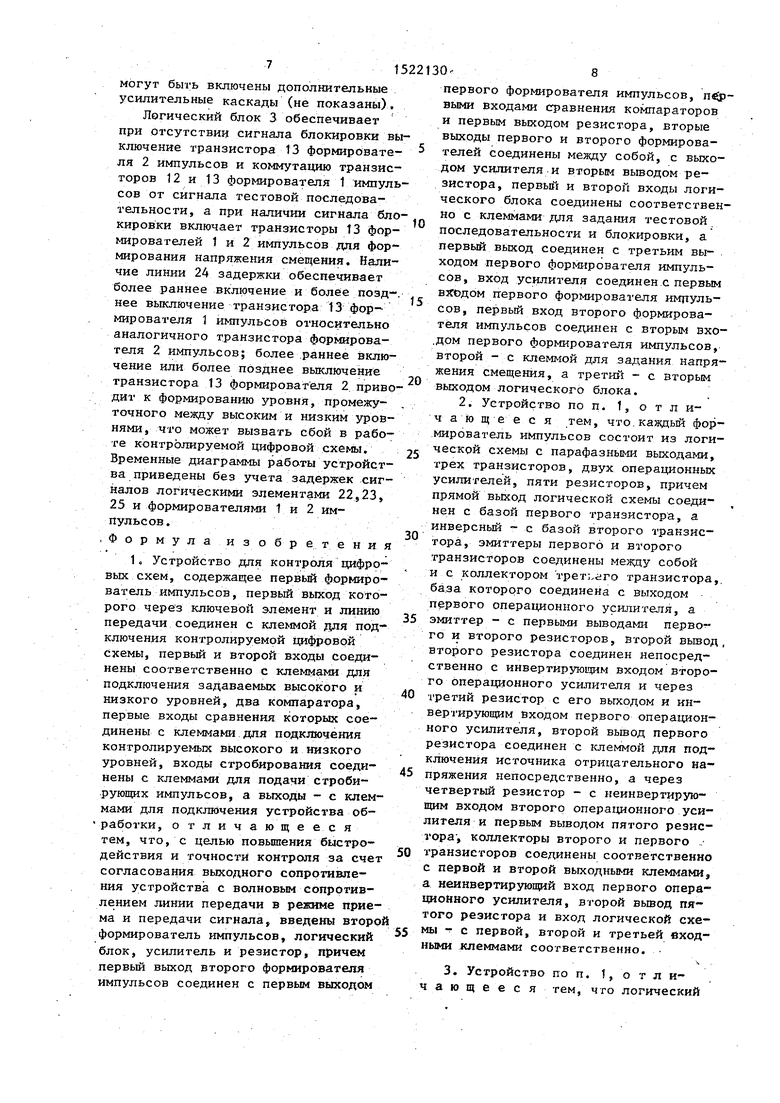

Первый вход элемента НЛИ-НЕ 22 со- 40 единен с выходом инвертора 23, второй - с входом линии 24 задержки и первым входом элемента И-ПЕ 25, третий - с выходом линии 24 задержки и вторым входом элемента Я-11Е 25, выдовательности и блокировки, а первый ходы элементов НЛИ-НЕ 22 и И-НЕ 25

соединены с первой и второй вькодны- ми клеммами логического блока соответственно, а входы инвертора 23 и линии 24 задержки - с первой и второй входными клеммами логического блока соответственно.

и второй выходы соединены с третьими входами формирователей 1 и,2 импульсов соответственно, вход усилителя 6 соединен с первым.входом формирователя- 1 импульсов и клеммой для под- ключения задаваемого высокого уровня, первый вход формирователя 2 импульсов соединен с вторы входом формирователя 1 импульсов и входной клеммой для подключения задаваемого низ-, кого уровня, а второй - с входной клеммой для задания напряжения смещения, вторые входы сравнения компаравывод резистора. 17 соединен непо- средственно с клеммой для подключе- ния источника отрицательного напря- жения и через резистор 19 с инвер-

усилителя 15 и второй вывод резис- тора 20 - с первой, второй и третьей

тируюишм входом операционного усилителя 16 и первым выводом резистора 20, коллекторы транзисторов 13 и 12 соединены соответственно с первой и второй выходными клеммами фop иpoвa- теля, а вход логической схемы 11, неинвертирующий вход операционного

соответственно .

Первый вход элемента НЛИ-НЕ 22 со- единен с выходом инвертора 23, второй - с входом линии 24 задержки и первым входом элемента И-ПЕ 25, третий - с выходом линии 24 задержки и вторым входом элемента Я-11Е 25, вы

соединены с первой и второй вькодны- ми клеммами логического блока соответственно, а входы инвертора 23 и линии 24 задержки - с первой и второй входными клеммами логического блока соответственно.

Устройство работает следующим образом.

К клемме 10 подключается вывод контролируемой гщфровой схемы. Натретьи входы фop шpoвaтeлeй 1 и 2 импульсов с логического блока 3 подаются преобразованные сигналы тестовой

1522130

последовательности и блокировки. На первый вход формирователя 1 ньтуль сов, соединениьш с входом усилителя 6, подается формируемьш уровень, на второй вход формирователя 1 импульсов и nepBbrii вход формирователя 2 импульсов - формируемьй низкий зфо- вень, на второй вход формирователя 2 импульсов - уровень напряжения смещения, спределягощий напряжение на на- . грузке контролируемой цифровой сх.емы. На вторые входы сравнения компараторов 4 и 5 подаются соответствующие

130

10

токов, протекая через резистор 7, создает на нем падение напряжения, равное разности заданных напряжения высокого уровня и напряжения смещения, и обеспечивает на клемме 10 напряжение, равное напряжению смещения. Выходной сигнал контролируемой цифровой схемы с клеммы 10 поступает на компараторы 4 и 5, которые после сравнения его с пороговыми высоким и низким уровнями вырабатьшают логические сигналы для дальнейшей обработки. Дпя согласования уровней напряжения

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1988 |

|

SU1619208A1 |

| УСТРОЙСТВО АНАЛОГОВОГО ДАТЧИКА УГЛА ФАЗОВОГО СДВИГА МЕЖДУ НАПРЯЖЕНИЕМ И ТОКОМ | 2011 |

|

RU2492572C2 |

| Устройство для измерения сопротивления изоляции сетей постоянного тока | 1983 |

|

SU1142804A2 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Поплавковый уровнемер | 1990 |

|

SU1783312A1 |

| Формирователь импульсов | 1981 |

|

SU995297A1 |

| Устройство измерения времени установления выходного напряжения быстродействующих операционных усилителей | 1986 |

|

SU1318939A1 |

| Устройство для контроля электронных схем | 1985 |

|

SU1270732A1 |

| Устройство автоматического контроля и отбраковки резисторов | 1987 |

|

SU1531026A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

Изобретение относится к измерительной технике и может быть использовано в каналах измерительных систем для контроля цифровых микросхем и блоков с двунаправленными выводами. Цель изобретения - повышение быстродействия и точности контроля - достигается путем согласования выходного сопротивления устройства с волновым сопротивлением линии передачи как при задании стимулирующих воздействий, так и при приеме ответного сигнала контролируемой схемы. Для достижения цели в устройство дополнительно введены второй формирователь импульсов, логический блок, усилитель и резистор. Величина сопротивления резистора выбирается равной волновому сопротивлению линии передачи. 2 з.п.ф-лы, 4 ил.

контролируемые высокий и низкий уров-. контролируемой схемы с рабочим диапани, на входы стробирования компараторов 4 и 5 подаются логические сигналы стробирования, определяющие момент контроля логических уровней. С выхода компараторов снимаются сигналы для последующей обработки. Ключевой элемент 8 отключает устройство контроля от вывода контролируемой 1ЩФРОВОЙ схемы на время установления рабочего режима устройства.

Если подключенньй вывод контролируемой цифровой схемы является входом, транзистор 13 формирователя 2 импульсов закрыт и напряжения высокого и низкого уровней определяются формирователем 1 импульсов. При этом если задается высокий уровень, транзистор 13 формирователя 1 импульсов закрыт и на клемму 10 поступает напряжение высокого уровня с выхода усили теля 6 через резистор 7. Дпя задания низкого зфовня сигналом тестовой последовательности включается транзистор 13 формирователя 1 импульсов, который задает ток, пропорциональный разности заданных напряжений высокого и низк&го уровней. Э.тот ток, протекая через резистор 7, создает на нем падение напряжения, равное разности за данных напряжений высокого и низкого уровней, которое в сумме с напряжением высокого уровня обеспечивает на клемме 10 низкий уровень.

Если подключенный вьшод контролируемой цифровой схемы является выходом, сигналом блокировки открываются транзисторы 13 формирователей 1 и 2 импульсов и через резистор 7 протекают выходные токи формирователей 1 и 2 импульсов, первый из которых пропор ционален разности заданных напряжений высокого и низкого уровней, а второй - разности заданных напряжения низкого уровня и напряжения смещения. Сумма

20

25

30

зоном компараторов 4 и 5 может включаться буферный усилитель (ке показан) .

Величина сопротивления резистора 7 выбирае равной волновому сопротивлению линии 9 передачи, обычно равному 50 Ом. Таким образом, согласование с линией 9 передачи обеспечивается при задании высокого и низкого уровней при блокировке и контроле выходного сигнала контролируемой цифро вой схемь независимо от величины выходного сопротивления последней. Кроме того, резистор 7 совместно с усилителем 6 и формирователям 1 и 2 им- лульсов создает для контролируемой схемы нагр|узку, эквивалентную подключению напряжения смещения через сопротивление нагрузки, равное величине сопротивления резистора 7.

Формирователи 1 и 2 импульсов работают при последовательном согласова нии с линией 9 передачи, а контролируемая цифровая схема - при параллельном.

Формирователи 1 и 2 импульсов работают следующим образом. На вход логической схемы 11 постуиает логический сигнал, управляющий работой токового переключателя, состоящего из транзисторов 12 и 13. Транзистор 14 генерирует ток, величина которого про порциональна разности напряжений, задаваемых на первьй и второй входы фop щpoвaтeлeй 1 и 2, что обеспечивается схемой пересчета напряжения в ток, состоящей из операзщонных усилителей 15 и J 5 и резисторов 17-21. К точке соединения резисторов 17 и 19 подключается источник отрицательног,о 5 напряжения (не показан). Для получения необходимого быстродействия и амплитуды сигнала между логической схемой 11 и транзисторами 12 и 13

35

40

45

50

контролируемой схемы с рабочим диапа

зоном компараторов 4 и 5 может включаться буферный усилитель (ке показан) .

Величина сопротивления резистора 7 выбирае равной волновому сопротивлению линии 9 передачи, обычно равному 50 Ом. Таким образом, согласование с линией 9 передачи обеспечивается при задании высокого и низкого уровней при блокировке и контроле выходного сигнала контролируемой цифро вой схемь независимо от величины выходного сопротивления последней. Кроме того, резистор 7 совместно с усилителем 6 и формирователям 1 и 2 им- лульсов создает для контролируемой схемы нагр|узку, эквивалентную подключению напряжения смещения через сопротивление нагрузки, равное величине сопротивления резистора 7.

Формирователи 1 и 2 импульсов работают при последовательном согласовании с линией 9 передачи, а контролируемая цифровая схема - при параллельном.

Формирователи 1 и 2 импульсов работают следующим образом. На вход логической схемы 11 постуиает логический сигнал, управляющий работой токового переключателя, состоящего из транзисторов 12 и 13. Транзистор 14 генерирует ток, величина которого пропорциональна разности напряжений, задаваемых на первьй и второй входы фop щpoвaтeлeй 1 и 2, что обеспечивается схемой пересчета напряжения в ток, состоящей из операзщонных усилителей 15 и J 5 и резисторов 17-21. К точке соединения резисторов 17 и 19 подключается источник отрицательног,о напряжения (не показан). Для получения необходимого быстродействия и амплитуды сигнала между логической схемой 11 и транзисторами 12 и 13

могут быть включены дополнительные усилительные каскады (не показаны).

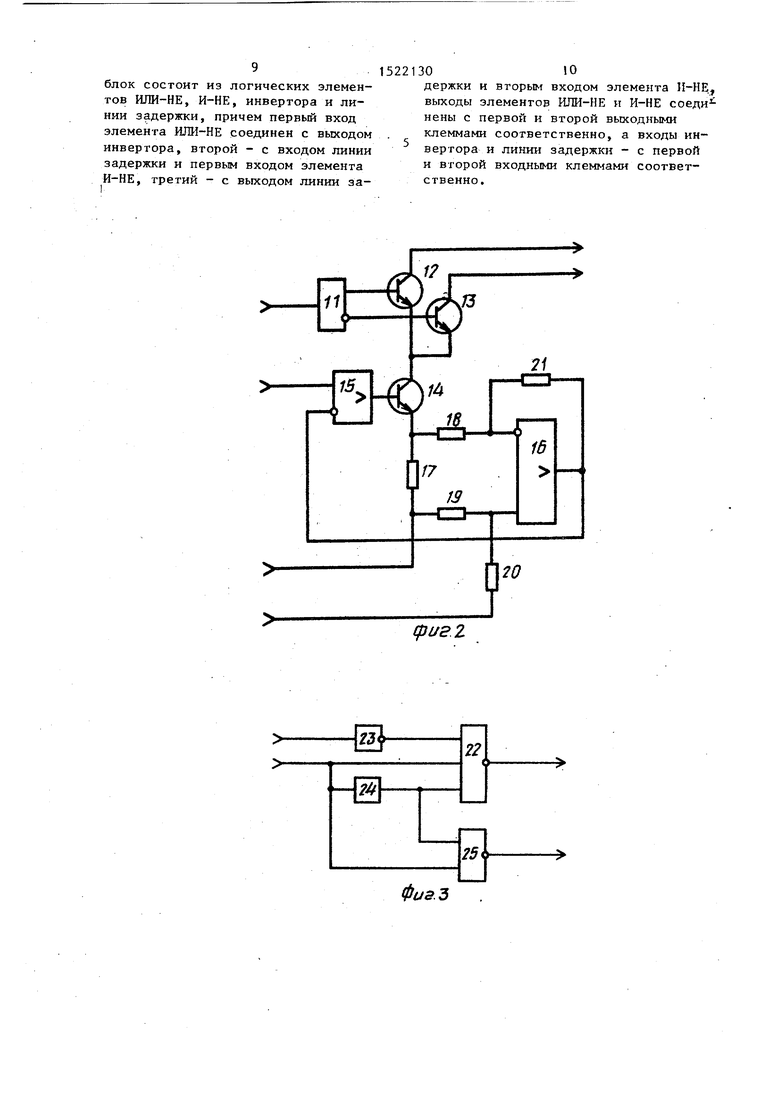

Логический блок 3 обеспечивает при отсутствии сигнала блокировки выключение транзистора 13 формирователя 2 импульсов и коммутацию транзисторов 12 и 13 формирователя 1 импульсов от сигнала тестовой последовательности, а при наличии сигнала блокировки включает транзисторы 13 формирователей 1 и 2 импульсов для формирования напряжения смещения. Наличие линии 24 задержки обеспечивает более раннее включение и более позд. нее выключение транзистора 13 формирователя 1 импульсов относительно аналогичного транзистора формирователя 2 импульсов; более .раннее включение или более позднее выключение транзистора 13 формирователя 2. приводит к формированию уровня, промежу- . точного между высоким и низким уровнями, что может вызвать сбой в работе контролируемой цифровой схемы, ; Временные диаграммы работы устройства приведены без учета задержек сигналов логическими элементами , 25 и формирователями 1 и 2 импульсов.

Ф о р м у л а и 3 обретения 1. Устройство для контроля цифровых схем, содержащее первый формирователь импульсов, первый выход которого через ключевой элемент и линию передачи соединен с клеммой для подключения контролируемой гщфроврй схемы, первый и второй входы соединены соответственно с клеммами для подключения задаваемых высокого и низкого уровней, два компаратора, первые входы сравнения которых соединены с клеммами для подключения контролируемых высокого и низкого уровней, входы стробирования соединены с клеммами для подачи строби- рующих импульсов, а выходы - с клеммами для подклк чения устройства об-

работки, отличающееся там, что, с целью повьшения быстродействия и точности контроля за счет согласования выходного сопротивления устройства с волновым сопротивлением линии передачи в режиме приема и передачи сигнала, введены второй формирователь импульсов, логический блок, усилитель и резистор, причем первый выход второго формирователя импульсов соединен с первым выходом

o

5

0

5

0

5

0

5

0

5

первого формирователя импульсов, выми входами сравнения компараторов и первым выходом резистора, вторые выходы первого и второго формирователей соединены между собой, с выходом усшштеля и вторым выводом резистора, первый и второй входы логического блока соединены соответственно с клеммами для задания тестовой последовательности и блокировки, а первый вьпсод соединен с третьим вы- ходом первого формирователя импульсов, вход усили7 еля соединен с первым входом первого формироваг еля импульсов, первый вход второго формирователя импульсов соединен с вторым вхо- .дом первого формирователя импульсов, второй - с клеммой для задания напряжения смещения, а третий - с вторым выходом логического блока,

блок состоит из логических элементов ИЛИ-НЕ, И-НЕ, инвертора и линии задержки, причем первый вход элемента ИЛИ-НЕ соединен с выходом инвертора, второй - с входом линии задержки и первым входом элемента И-НЕ, третий - с выходом линии за152213010

держки и вторым входом элемента И-НЕ,, выходы элементов ИЛИ-НЕ и И-НЕ соеди нены с первой и второй выходными клеммами соответственно, а входы инвертора и линии задержки - с первой и второй входными клеммами соответственно.

ср1/г.2

Физ.з

Тест

poSna

Swxffff

фиг. 4

| Устройство для контроля электронных схем | 1977 |

|

SU716266A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Уплотнение цилиндров гидропрессов, работающих на высоких давлениях | 1959 |

|

SU124761A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1989-11-15—Публикация

1986-08-07—Подача