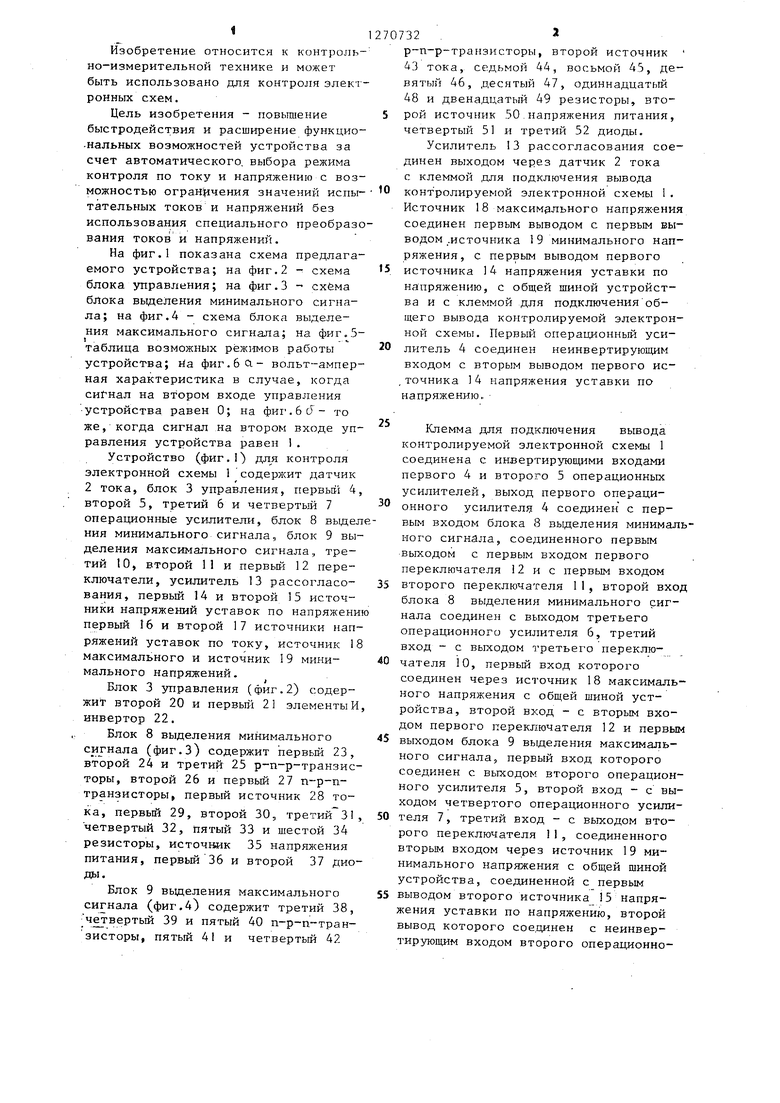

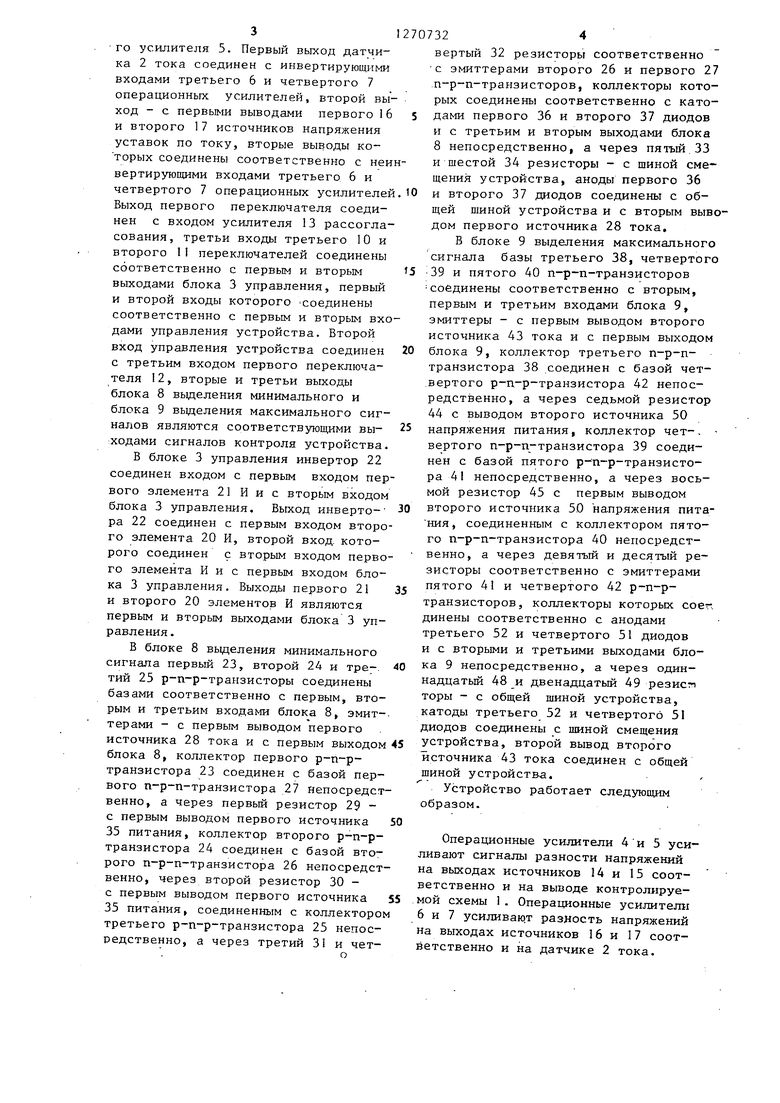

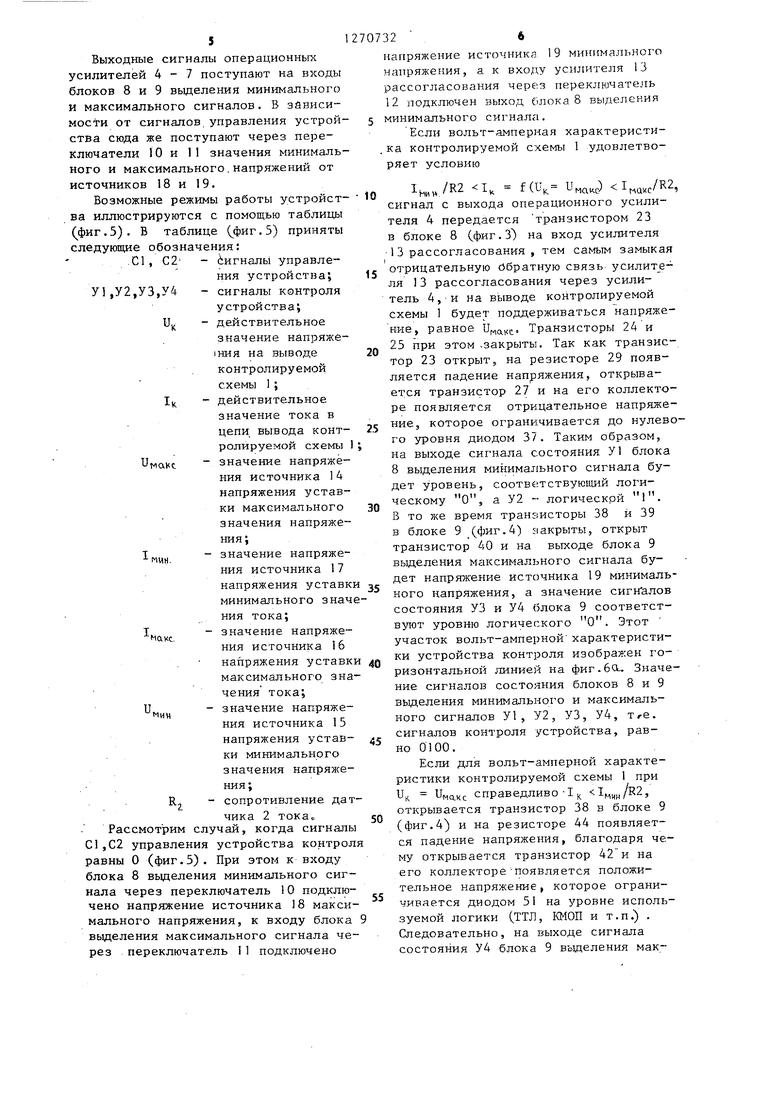

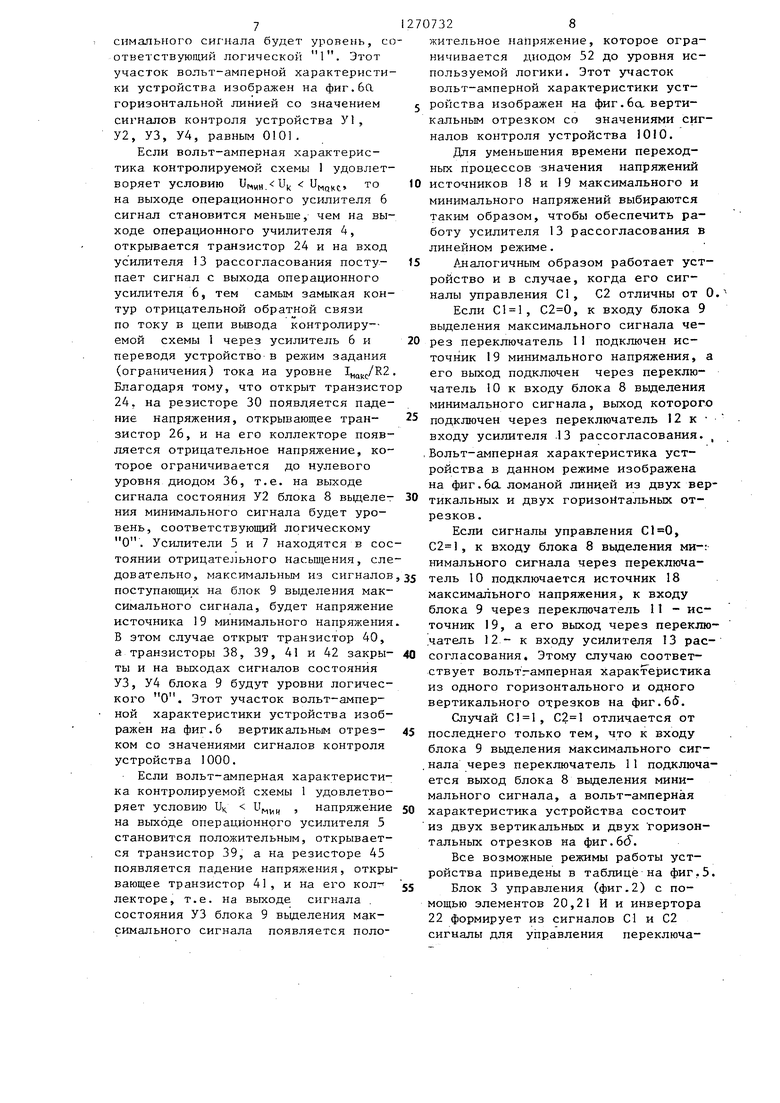

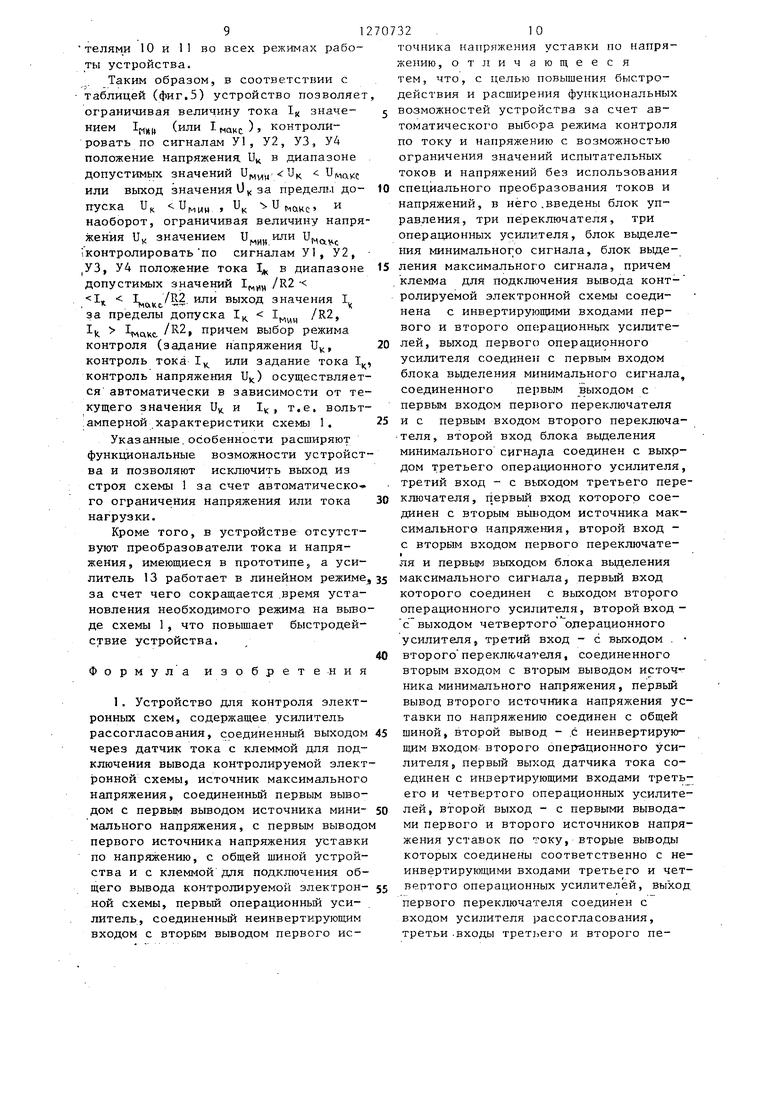

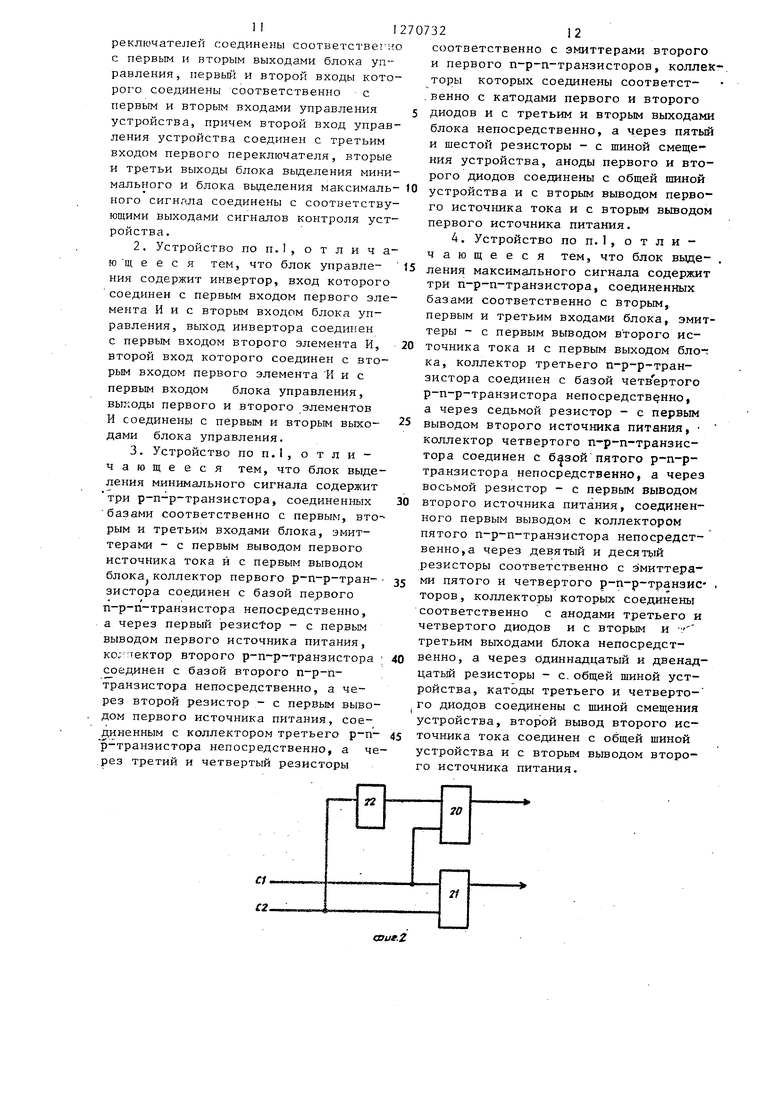

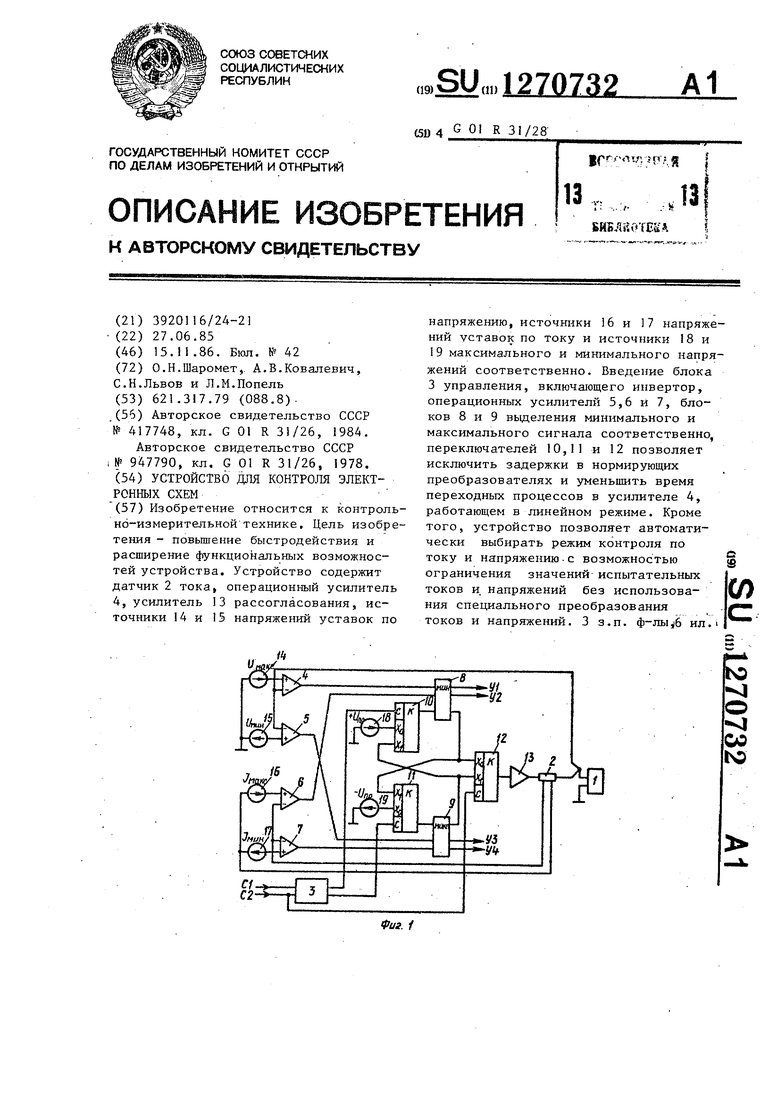

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля элект ронных схем. Цель изобретения - повышение быстродействия и расширение функциональных возможностей устройства за счет автоматического, выбора режима контроля по току и напряжению с возможностью ограничения значений испытательных токови напряжений без использования специального преобразо вания токов и напряжений. На фиг.1 показана схема предлагаемого устройства; на фиг. 2 - схема блока управления; на фиг.З схема блока выделения минимального сигнала; на фиг.4 - схема блока выделения максимального сигнала; на фиг,51 таблица возможных режимов работы устройства; ria фиг.бсх- вольт-амперная характеристика в случае, когда на втором входе управления устройства равен 0; на фиг.бсУ- то же, когда сигнал на втором входе управления устройства равен 1 . Устройство (фиг,1) для контроля электронной схемы 1содержит датчик 2 тока, блок 3 управления, первьш 4 второй 5, третий 6 и четвертьш 7 операционные усилители, блок 8 выдел ния минимального сигнала, блок 9 вы деления максимального сигнала., третий 10, второй 11 и первый 12 переключатели, усилитель 13 рассогласования, первый 14 и второй 15 источники напряжений уставок по напряжени первый 16 и второй 17 источники нап ряжений уставок по току, источник 1 максимального и источник I9 минимального напряжений. Блок 3 управления (фиг.2) содержит второй 20 и первый 21 элементы И инвертор 22. Блок 8 выделения минимального cиJнaлa (фиг.З) содержит первый 23, второй 24 и третий 25 р-п-р транзис торы, второй 26 и первый 27 п-р-птранзисторы, первый источник 28 тока, первый 29, второй 30, третий 31 четвертый 32, пятый 33 и шестой 34 резисторы, источник 35 напряжения питания, первый 36 и второй 37 дио ды. Блок 9 вьщеления максимального сигнала (фиг.4) содержит третий 38, четвертый 39 и пятый 40 п-р-п-транзисторы, пятый 41 и четвертый 42 32 . р-п-р-транзисторы, второй источник 43 тока, седьмой 44, восьмор 45, девятый 46, десятый 47, одиннадцатый 48 и двенадцатый 49 резисторы, второй источник 50.напряжения питания, четвертый 51 и третий 52 диоды. Усилитель 13 рассогла.сования соединен выходом через датчик 2 тока с клеммой для подключения вывода контролируемой электронной, схемы 1 . Источник 18 максимального напряж ения соединен первым выводом с первым выводом ..источника 19 минимального напряжения, с первым выводом первого источника 14 напряжения уставки по напряжению, с общей шиной устройства и с клеммой для подключенияобщего вывода контролируемой электронной схемы. Первый операционный усилитель 4 соединен неинвертирующим входом с вторым выводом первого источника 14 напряжения уставки по напряжению ,Клемма для подключения вывода контролируемой электронной схемы 1 соединена с инвертирующими входами первого 4 и второго 5 операционных усилителей, выход первого операционного усилителя 4 соединен с первым входом блока 8 выделения минимального сигнала, соединенного первым выходом с первым входом первого переключателя I2 и с первым входом второго переключателя 11, второй вход блока 8 выделения минимального сигнала соединен с выходом третьего операционного усилителя 6, третий вход - с выходом третьего переключателя 10, первый вход которого соединен через источник 18 максимального напряжения с общей шиной устройства, второй вход - с вторым входом первого переключателя 12 и первым выходом блока 9 выделения максимального сигнала, первый вход которого соединен с выходом второго операционного усилителя 5, второй вход - с выходом четвертого операционного усилителя 7, третий вход - с выходом второго переключателя 1, соединенного вторым входом через источник 19 минимального напряжения с общей шиной устройства, соединенной с первым выводом второго источника 15 напряжения уставки по напряжению, второй вывод которого сое.динен с неинвертирующим входом второго операдионного усилителя 5. Первый выход датчика 2 тока соединен с инвертирующими входами третьего 6 и четвертого 7 операционных усилителей, второй выход - с первыми выводами первого 16 и второго 17 источников напряжения уставок по току, вторые выводы которых соединены соответственно с неивертирующими входами третьего 6 и четвертого 7 операционных усилителей Выход первого переключателя соединен с входом усилителя 13 рассогласования, третьи входы третьего 10 и второго 11 переключателей соединены соответственно с первым и вторым выходами блока 3 управления, первый и второй входы которого соединены соответственно с первым и вторым входами управления устройства. Второй вход управления устройства соединен с третьим входом первого переключателя 12, вторые и третьи выходы блока 8 вьщеления минимального и блока 9 выделения максимального сигналов являются соответствующими выходами сигналов контроля устройства.

В блоке 3 управления инвертор 22 соединен входом с первым входом первого элемента 21 И и с вторым входом блока 3 управления. Выход инвертора 22 соединен с первым входом второго элемента 20 И, второй вход, которого соединен с вторым входом первого элемента И и с первым входом блока 3 управления. Выходы первого 21 и второго 20 элементов И являются первым и вторым выходами блока 3 управления .

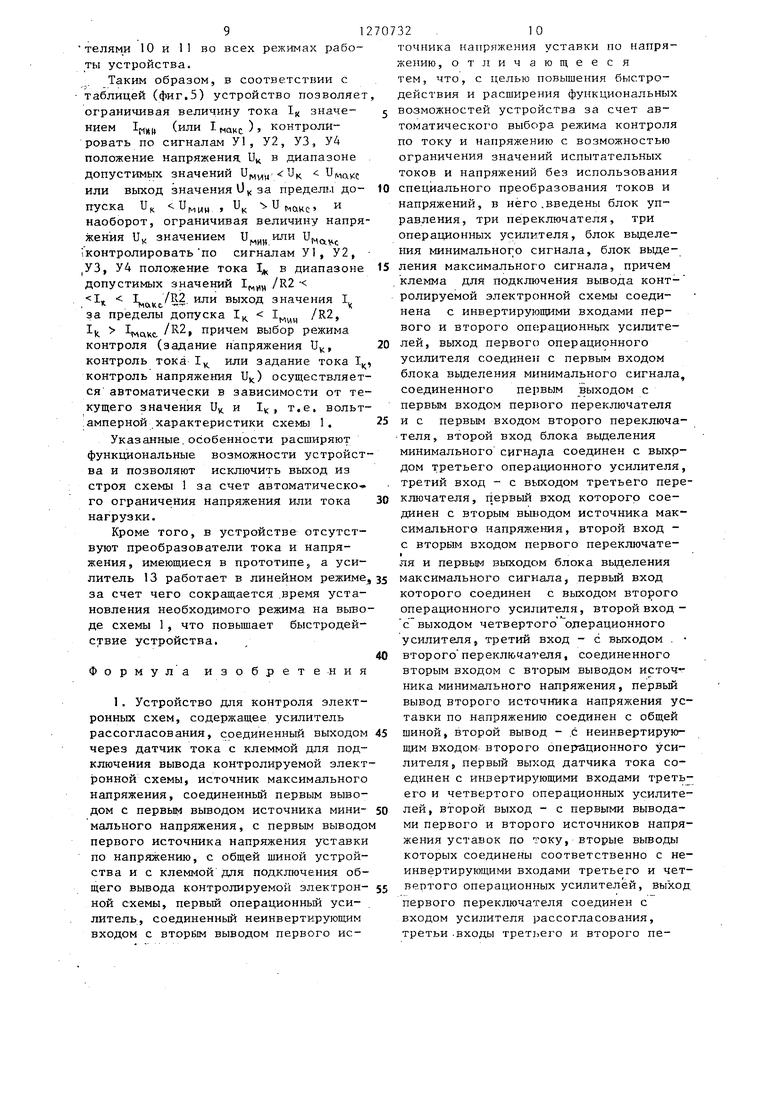

В блоке 8 выделения минимального сигнала первый 23, второй 24 и тре-. тий 25 р-п-р-транзисторы соединены баэами соответственно с первым, вторым и третьим входами блока 8, эмиттерами - с первым выводом первого источника 28 тока и с первым выходом блока 8, коллектор первого р-п-ртранзистора 23 соединен с базой первого п-р-п-транзистора 27 непосредственно, а через первый резистор 29 с первым выводом первого источника 35 питания, коллектор второго р-п-ртранзистора 24 соединен с базой второго п-р-п-транзистора 26 непосредственно, через второй резистор 30 с первым выводом первого источника 35 питания, соединенным с коллекторо третьего р-п-р-транзистора 25 непосредственно, а через третий 31 и четвертый 32 резисторы соответственно с эмиттерами второго 26 и первого 27 п-р-п-транзисторов, коллекторы которых соединены соответственно с катодами первого 36 и второго 37 диодов и с третьим и вторым выходами блока 8 непосредственно, а через пятый 33 и шестой 34 резисторы - с шиной смещения устройства, аноды первого 36 и второго 37 диодов соединены с общей шиной устройства и с вторым вывдом первого источника 28 тока,

В блоке 9 выделения максимального сигнала базы третьего 38, четвертог 39 и пятого 40 п-р-п-транзисторов соединены соответственно с вторым, первым и третьим входами блока 9, эмиттеры - с первым выводом второго источника 43 тока и с первым выходом блока 9, коллектор третьего п-р-птранзистора 38 соединен с базой четвертого р-п-р-транзистора 42 непосредственно, а через седьмой резистор 44 с выводом второго источника 50 напряжения питания, коллектор чет-. вертого п-р-п-транзистора 39 соединен с базой пятого р-п-р-транзистора 41 непосредственно, а через восьмой резистор 45 с первым выводом второго источника 50 напряжения питания, соединенным с коллектором пятого п-р-п-транзистора 40 непосредственно, а через девятый и десятый резисторы соответственно с эмиттерами пятого 41 и четвертого 42 р-п-ртранзисторов, коллекторы которых сое динены соответственно с анодами третьего 52 и четвертого 51 диодов и с вторыми и третьими выходами блока 9 непосредственно, а через одиннадцатый 48 и двенадцатый 49 резисп торы - с общей шиной устройства, катоды третьего 52 и четвертого 51 диодов соединены с шиной смещения устройства, второй вывод второго источника 43 тока соединен с общей шиной устройства.

Устройство работает следующим образом.

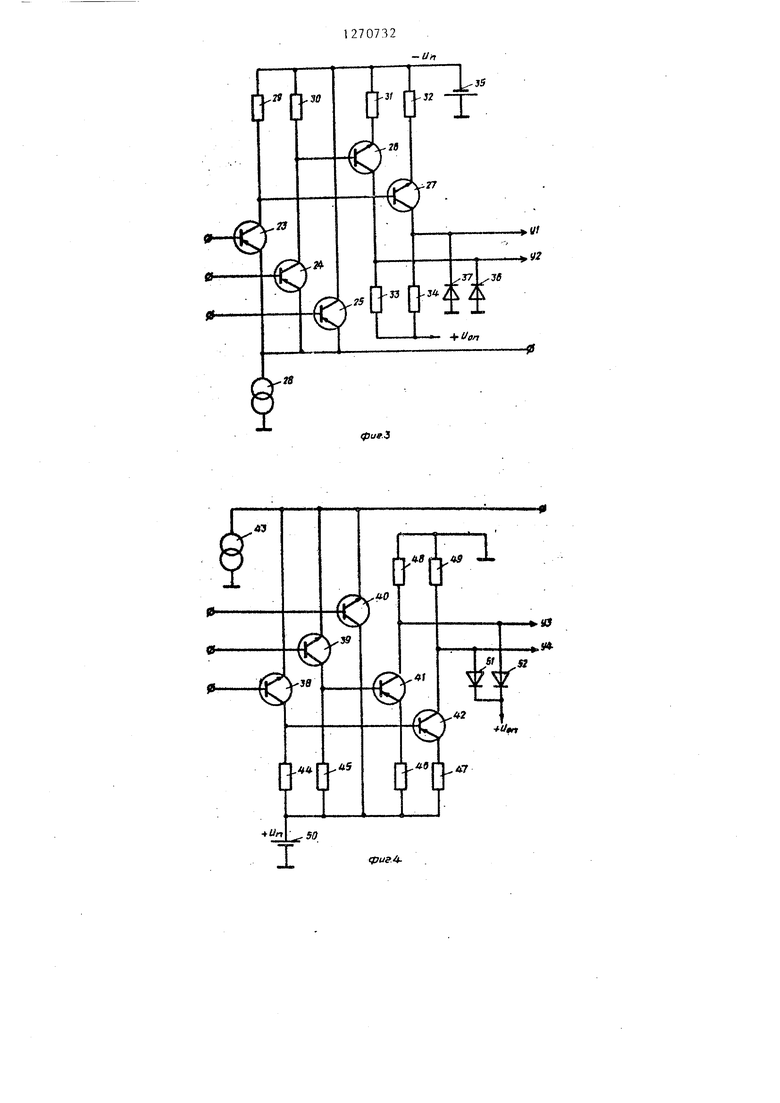

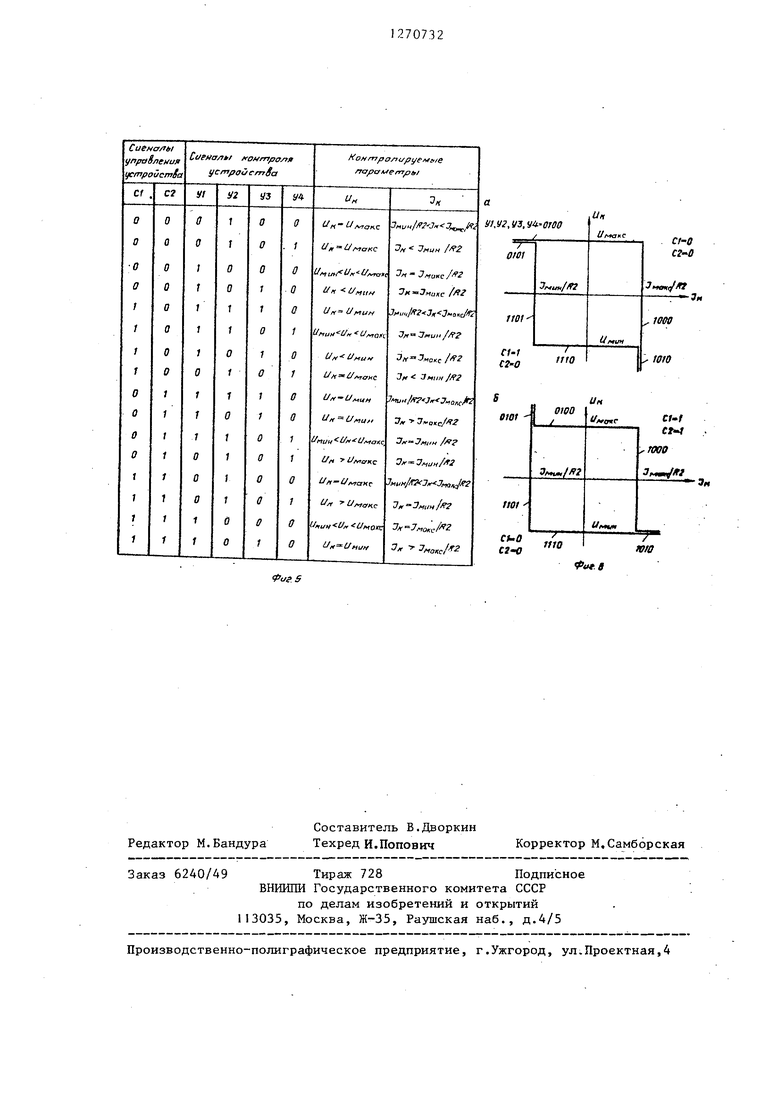

Операционные усилители 4и 5 усиливают сигналы разности напряжений на выходах источников 14 и 15 соответственно и на выводе контролируемой схемы 1. Операционные усилители 6 и 7 усиливают разность напряжений на выходах источников 16 и 17 соответственно и на датчике 2 тока. Выходные сигналы операционньк усилителей 4-7 поступают на входы блоков 8 и 9 вьщеления минимального и максимального сигналов. В эййисимости от сигналов управления устройства сюда же поступают через переключатели 10 и 11 значения минимального и максимального,напряжений от источников 18 и 19. Возможные режимы работы устройства иллюстрируются с помощью таблицы (фиг. 5) . В таблице (фиг. 5) приняты следующие обозначения; .С1, С2 - Сигналы управления устройства; У1,У2,УЗ,У4 - сигналы контроля устройства; U|( - действительное значение напряже1НИЯ на выводе контролируемой схемы 1; 1ц - действительное значение тока в цепи, вывода контролируемой схемы UfvicxKt значение напряжения источника 14 напряжения уставки максимального значения напряжения ; -значение напряжения источника 17 напряжения уставк минимального знач ния тока; -значение напряжения источника 16 напряжения уставк максимального зна чения тока; -значение напряжения источника 15 напряжения уставки минимального значения напряжения ; R - сопротивление дат чика 2 тока,, Рассмотрим случай, когда сигналы С1,С2 управления устройства контрол равны О (фиг.5). При этом к входу блока 8 выделения минимального сигнала через переключатель О подключено напряжение источника 18 максимального напряжения, к входу блока выделения максимального сигнала через переключатель I1 подключено апряжение источника 19 минимального апряжения, а к входу усилителя 13 ассогласования через переключатель 12 подключен выход блока 8 выделения инимального сигнала. Если вольт-амперная характеристика контролируемой схемы 1 удовлетворяет условию 1, f(lV UHCVKC) 1гла., сигнал с выхода операционного усилителя 4 передается транзистором 23 в блоке В (фиг.З) на вход усилителя 13 рассогласования , тем самым замыкая отрицательную Обратную связь усилит еля 13 рассогласования через усилитель 4,-и на выводе контролируемой схемы 1 будет поддерживаться напряжение, равное U|v,ci.Kf Транзисторы 24 и 25 при этом -закрыты. Так как транзистор 23 открыт,, на резисторе 29 появляется падение напряжения, открывается транзистор 27 и на его коллекторе появляется отрицательное напряжение, которое ограничивается до нулевого уровня диодом 37. Таким образом, на выходе сигнала состояния У1 блока 8 выделения минимального сигнала будет Уровень, соотве.тствующий логическому О, а У2 - логической 1. В то же время транзисторы 38 и 39 в блоке 9 (фиг.4) закрыты, открыт транзистор 40 и на выходе блока 9 вьщеления максимального сигнала будет напряжение источника 19 минимального напряжения, а значение сигналов состояния УЗ и У4 блока 9 соответствуют уровню логического О. Этот участок вольт-амперной характеристики устройства контроля изображен горизонтальной линией на фиг.бо. Значение сигналов состояния блоков 8 и 9 выделения минимального и максимального сигналов У1 , У2, УЗ, У4, т/-е. сигналов контроля устройства, равно 0100. Если для вольт-амперной характеристики контролируемой схемы 1 при UK UMCLKC справедливо-11 , открывается транзистор 38 в блоке 9 (фиг.4) и на резисторе 44 появляется падение напряжения, благодаря чему открывается транзистор 42 и на его коллектореПоявляется положительное напряжение, которое ограничивается диодом 51 на уровне используемой логики (ТТЛ, КМОП и т.п.) . Следовательно, на выходе сигнала состояния У4 блока 9 вьщеления макснмального сигнала будет уровень, с ответствугощий логической 1. Этот участок вольт-амперной характеристи ки устройства изображен на фиг.бй горизонтальной линией со значением сигналов контроля устройства У1, У2, УЗ, У4, равным 0101. Если вольт-амперная характеристика контролируемой схемы 1 удовлет воряет условию Омин U| то на выходе операционного усилителя 6 сигнал становится меньше, чем на вы ходе операционного училителя 4, открывается транзистор 24 и на вход усилителя 13 рассогласования поступает сигнал с выхода операционного усилителя 6, тем самым замыкая кон тур отрицательной обратной связи по току в цепи вьшода контролиру-емой схемы i через усилитель 6 и переводя устройство в режим задания (ограничения) тока на уровне Благодаря тому, что открыт транзисто 24, на резисторе 30 появляется падение напряжения, открывающее транзистор 26, и на его коллекторе появляется отрицательное напряжение, которое ограничивается до нулевого уровня диодом 36, т.е. на выходе сигнала состояния У2 блока 8 вьщеления минимального сигнала будет уровень, соответствующий логическому О. Усилители 5 и 7 находятся в сос тоянии отрицательного насьш1ения, сле довательно, максимальным из сигналов поступающих на блок 9 выделения максимального сигнала, будет напряжение источника 19 минимального напряжения В этом случае открыт транзистор 40, а транзисторы 38, 39, 41 и 42 закрыты и на выходах сигналов состояния УЗ, У4 блока 9 будут уровни логического О. Этот участок вольт-амперной характеристики устройства изображен на фиг.6 вертикальньм отрезком со значениями сигналов контроля устройства 1000. Если вольт-амперная характеристика контролируемой схемы 1 удовлетворяет условию UK , , напряжение на выходе операционного усилителя 5 становится положительным, открывается транзистор 39, а на резисторе 45 появляется падение напряжения, откры вающее транзистор 41, и на его коллекторе, т.е. на выходе сигнала состояния УЗ блока 9 вьщеления максимального сигнала появляется положительное напряжение, которое ограничивается диодом 52 до уровня используемой логики. Этот участок вольт-амперной характеристики устройства изображен на фиг.бо. вертикальным отрезком со значениями сигналов контроля устройства 1010. Для уменьшения времени переходных процессов значения напряжений источников 18 и 19 максимального и минимального напряжений выбираются таким образом, чтобы обеспечить работу усилителя 13 рассогласования в линейном режиме. Аналогичным образом работает устройство и в случае, когда его сигналы управления С1, С2 отличны от 0. Если , , к входу блока 9 выделения максимального сигнала через переключатель 11 подключен источник 19 минимального напряжения, а его выход подключен через переключатель 10 к входу блока 8 вьщеления минимального сигнала, выход которого подключен через переключатель 12 к входу усилителя .13 рассогласования. , Вольт-амперная характеристика устройства в данном режиме изображена на фиг.ба. ломаной линией из двух вертикальных и двух горизонтальных отрезков. Если сигналы управления , С2, к входу блока 8 выделения ми-: нимального сигнала через переключатель 10 подключается источник 18 максимального напряжения, к входу блока 9 через переключатель 11 - источник 19, а его выход через переклю.чатель 12- к входу усилителя 13 рассогласования. Этому случаю соответствует вольтгамперная характеристика из одного горизонтального и одного вертикального отрезков на фиг.65. Случай С , отличается от последнего только тем, что к входу блока 9 вьщеления максимального сигнала через переключатель 11 подключается выход блока 8 вьщеления минимального сигнала, а вольт-амперная характеристика устройства состоит из двух вертикальных и двух горизонтальных отрезков на фиг.6(У. Все возможные режимы работы устройства приведены в таблице на фиг.5. Блок 3 управления (фиг.2) с помощью элементов 20,21 И и инвертора 22 формирует из сигналов С1 и С2 сигналы для управления нереключателями 10 и 11 во всех режимах работы устройства.

Таким образом, в соответствии с таблицей (фиг.5) устройство позволяет ограничивая величину тока 1 значе(или I .t ) 5 контролинием

тм

ровать по сигналам У1 , У2, УЗ., УА положение напряжения U в диапазоне допустимых значений и„,ц.иц U civic или выход значенияUц за пределы допуска и , и « наоборот, ограничивая величину напряжения Цц значением или и,,,,, 1контролироватьпо сигналам У1, У2, ,УЗ, У4 положение тока 1 в диапазоне допустимых значений /R2 - 1ц -HuKt S - выход значения I за пределы допуска 1 1, /R2, 1 /R2, причем выбор режима контроля (задание напряжения , контроль тока 1 или задание тока 1, контроль напряжения U) осуществляется автоматически в зависимости от текущего значения U и , т.е. вольт, амперной характеристики схемы 1.

Указанные.особенности расширяют функциональные возможности устройства и позволяют исключить выход из строя схемы 1 за счет автоматическое го ограничения напряжения или тока нагрузки.

Кроме того, в устройстве отсутствуют преобразователи тока и напряжения, имеющиеся в прототипе; а усилитель 13 работает в линейном режиме за счет чего сокращается .время установления необходимого режима на вьшоде схемы 1, что повышает быстродействие устройства. Формула изобретения

1. Устройство для контроля электронных схем, содержащее усилитель рассогласования, соединенный выходом через датчик тока с клеммой для подключения вывода контролируемой электронной схемы, источник максимального напряжения, соединенный первым выводом с первым выводом источника минимального напряжения, с первым выводо первого источника напряжения уставки по напряжению, с общей шиной устройства и с клеммой для подключения общего вывода контролируемой электронной схемы, первый операционный усилитель, соединенньм неинвертирующим входом с BTOpbiM выводом первого источника напряжения уставки по напряжению, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей устройства за счет автоматического выбора режима контроля по току и напряжению с возможностью ограничения значений испытательных токов и напряжений без использования специального преобразования токов и напряжений, в него.введены блок управления, три переключателя, три операционных усилителя, блок вьщеления минимального сигнала, блок выделения максимального сигнала, причем , клемма для подключения вывода контролируемой электронной схемы соединена с инвертирующими входами первого и второго операционньпс усилителей, выход первого операционного усилителя соединен с первым входом блока выделения минимального сигнала, соединенного первым выходом с первым входом первого переключателя и с первым входом второго переключаТеля, второй вход блока вьщеления минимального сигна;1а соединен с выхрдом третьего операционного усилителя, третий вход - с выходом третьего переключателя, п ервый вход которого соединен с вторым выводом источника максимального напряжения, второй вход с вторым входом первого переключателя и nepBbjM выходом блока выделения максимального сигнала, первый вход которого соединен с выходом второго операционного усилителя, второй входс выходом четвертого олерационного усилителя, третий вход - с выходом . второгопереклюнагеля, соединенного вторым входом с вторым выводом источт ника минимального напряжения, первьй вывод второго источника напряжения уставки по напряжению соединен с общей шиной, второй вывод - .с неинвертирующкм входом второго операционного усилителя 5 первый выход датчика тока соединен с инвертирующими входами третьего и четвертого операционных усилителей, второй выход - с первыми выводами первого и второго источников напряжения уставок по току, вторые вьшоды которых соединены соответственно с неинвертирующими входами третьего и четвертого операционных усилителей, выход первого переключателя соединен с входом усилителя рассогласования, третьи .входа третьего и второго переключателеи соединены соответствегно с первым и вторым выходами блока, управления, первьш и второй входы которого соединены соответственно с первым и вторым входами управления устройства, причем второй вход управления устройства соединен с третьим входом первого переключателя, вторые и третьи выходы блока выделения минимального и блока выделения максималького сигнала соединены с соответствующими выходами сигналов контроля устройства.

2.Устройство по п.1, о т л и ч аю щ е е с я тем, что блок управления содержит инвертор, вход которого соединен с первым входом первого элемента И и с вторым входом блока управления, выход инвертора соединен с первым входом второго элемента И, второй вход которого соединен с вторым входом первого элемента Икс первым входом блока управления, выходы первого и второго элементов И соединены с первым и вторым выходами блока управления.

3.Устройство по п.1, о т л и чающееся тем, что блок вьщеления минимального сигнала содержит

три р-п-р-транзистора, соединеннь х базами соответственно с первым, вторым и третьим входами блока, эмиттерами - с первым выводом первого источника тока и с первым выводом блока коллектор первого р-п-р-тран- зистора соединен с базой первого п-р-п-транзистора непосредственно, а через первый pesHcfop - с первым выводом первого источника питания, ко:::тектор второго р-п-р-транзистора соединен с базой второго п-р-птранзистора непосредственно, а через второй резистор - с первым выводом первого источника питания, соединенным с коллектором третьего р-пр-транзистора непосредственно, а через третий и четвертый резисторы

соответственно с эмиттерами второго и первого п-р-п-транзисторов, коллекторы которых соединены соответст.венно с катодами первого и второго диодов и с третьим и вторым выходами блока непосредственно, а через пятый и шестой резисторы - с шиной смещения устройства, аноды первого и второго диодов соединены с общей шиной устройства и с вторым выводом первого источника тока и с вторым выводом первого источника питания.

4. Устройство по п.1, о т л и - чающееся тем, что блок вьщеления максимального сигнала содержит три п-р-п-транзистора, соединенных базами соответственно с вторым, первым и третьим входами блока, эмиттеры - с первым выводом второго источника тока и с первым выходом блог ка, коллектор третьего п-р-р-транзистора соединен с базой четвертого р-п-р-транзистора непосредственно, а через седьмой резистор - с первым выводом второго источника питания, коллектор четвертого п-р-п-транзистора соединен с пятого р-п-ртранзистора непосредственно, а через восьмой резистор - с первым выводом второго источника питания, соединенного первым выводом с коллектором пятого п-р-п-транзистора непосредственно,а через девятый и десятый резисторы соответственно с эмиттерами пятого и четвертого р-п-р-транзисторов, коллекторы которых соединены соответственно с анодами третьего и четвертого диодов и с вторым и / третьим вьпгодами блока непосредственно, а через одиннаддатый и двенадцатьй резисторы - с, общей шиной устройства, катоды третьего и четвертого диодов соединены с шиной смещения устройства, второй вывод второго источника тока соединен с общей шиной устройства и с вторым вьшодом второго источника питания.

70

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электронных схем | 1984 |

|

SU1302870A1 |

| Устройство для контроля электронных схем | 1986 |

|

SU1431505A1 |

| Нагрузочное устройство для контроля источников питания | 1987 |

|

SU1430896A1 |

| Устройство для измерения параметров рассеяния транзисторов | 1982 |

|

SU1084709A1 |

| Устройство для контроля цифровых схем | 1986 |

|

SU1522130A1 |

| Многоканальный аналого-цифровой преобразователь малых постоянных сигналов | 1986 |

|

SU1381710A1 |

| Стабилизатор постоянного тока | 1979 |

|

SU851377A1 |

| Логарифмический усилитель | 1982 |

|

SU1088019A1 |

| Мажоритарное устройство | 1981 |

|

SU970701A1 |

| Вычислительное устройство | 1985 |

|

SU1282163A1 |

Изобретение относится к контрольно-измерительной технике. Цель изобретения - повьшение быстродействия и расширение функциональных возможностей устройства. Устройство содержит датчик 2 тока, операционный усилитель 4, усилитель 13 рассогласования, источники 14 и 15 напряжений уставок по напряжению, источники 16 и 17 напряжений уставок по току и источники 18 и 19 максимального и минимального напряжений соответственно. Введение блока 3 управления, включающего инвертор, операционных усилители 5,6 и 7, блоков 8 и 9 выделения минимального и максимального сигнала соответственно, переключателей 10,11 и 12 позволяет исключить задержки в нормирующих преобразователях и уменьшить время переходных процессов в усилителе 4, работаюш;ем в линейном режиме. Кроме того, устройство позволяет автоматически выбирать режим контроля по § току и напряжению - с возможностью ограничения значений испытательных (Л токов и. напряжений без использования специального преобразования токов и напряжений. 3 з.п. ил. ю 1 о со ю

С1. С2.

21

УО

a

У

.-С

Vje

- 4ГЬА5

гУлт

.yS

3t П-зг

Т

&

-(//

tf

Лв

-J7

j3 2

4-i/tf/T

-0

О tj42

Wt

I

47

UH а„„с

0100

Cl-f

et

ПЮО J«.,/W

7м

1110

то

| 1972 |

|

SU417748A1 | |

| Устройство для контроля электрических параметров электронных схем | 1978 |

|

SU947790A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-11-15—Публикация

1985-06-27—Подача