U

:л

ND

N::) :/о

00

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательности импульсов | 1987 |

|

SU1503069A1 |

| Счетный элемент с контролем | 1988 |

|

SU1569974A1 |

| Устройство для контроля последовательности импульсов | 1980 |

|

SU869052A1 |

| Устройство для контроля последовательности импульсов | 1990 |

|

SU1791957A1 |

| Устройство для контроля серий импульсов | 1988 |

|

SU1555841A2 |

| Делитель частоты с нечетным коэффициентом деления | 1984 |

|

SU1213540A1 |

| Устройство для контроля серий импульсов | 1984 |

|

SU1175022A1 |

| Преобразователь импульсов датчика перемещения | 1984 |

|

SU1226505A1 |

| Кольцевой счетчик | 1980 |

|

SU947970A1 |

| Резервированный делитель частоты | 1984 |

|

SU1188882A1 |

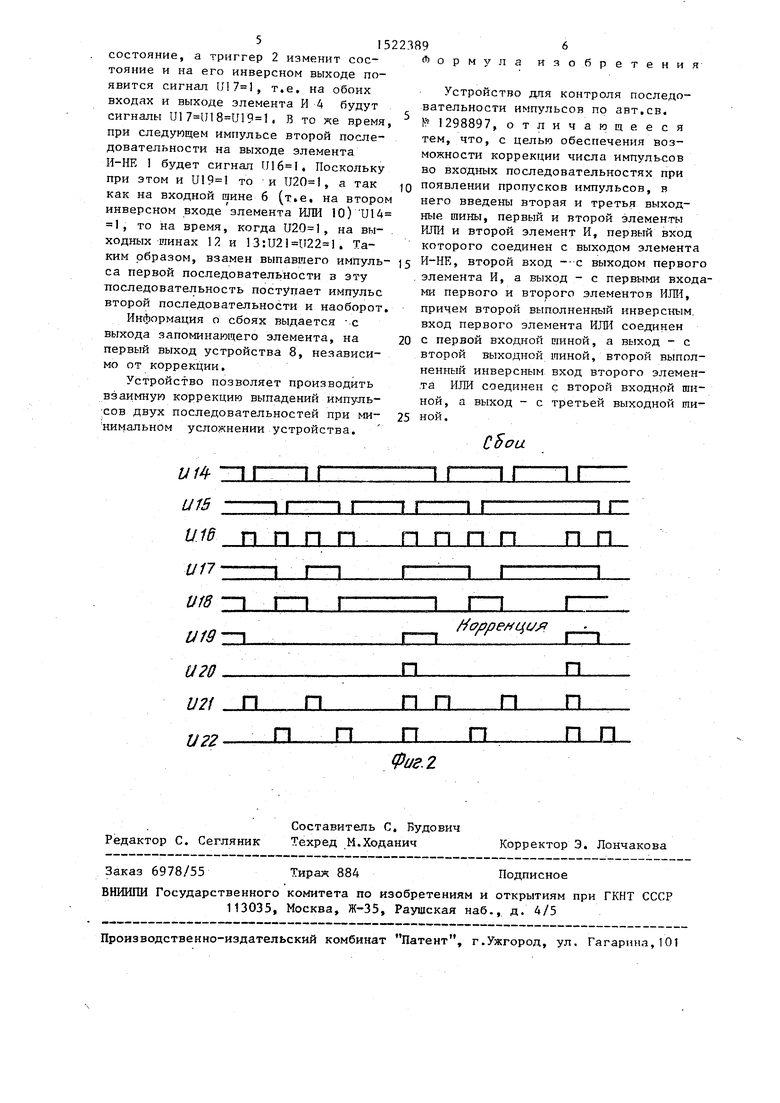

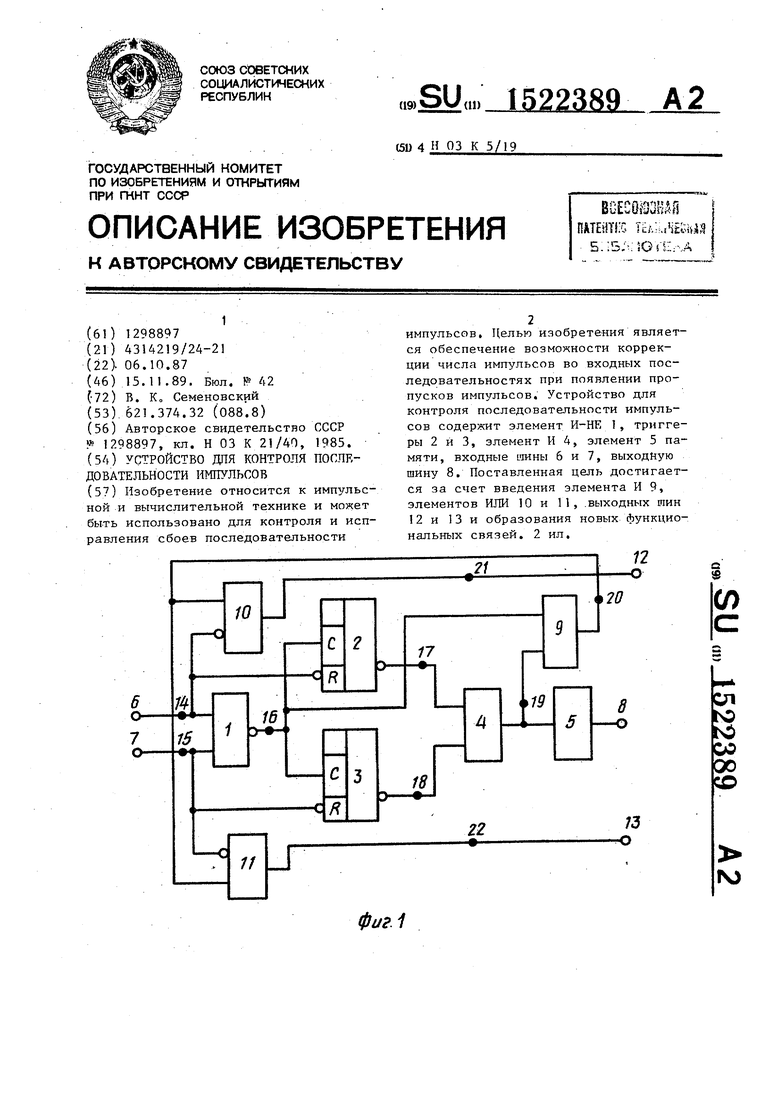

Изобретение относится к импульсной и вычислительной технике и может быть использовано для контроля и исправления сбоев последовательности импульсов. Целью изобретения является обеспечение возможности коррекции числа импульсов во входных последовательностях при появлении пропусков импульсов. Устройство для контроля последовательности импульсов содержит элемент И-НЕ 1, триггеры 2 и 3, элемент И 4, элемент 5 памяти, входные шины 6 и 7, выходную шину 8. Поставленная цель достигается за счет введения элемента И 9, элементов ИЛИ 10 и 11, выходных шин 12 и 13 и образования новых функциональных связей. 2 ил.

го

фаг.1

Изобретение относится к импульсной и вычислительной технике и может быть использовано для контроля и исправления сбоев последовательности импульсов.

Цель изобретения - обеспечение возмож юсти коррекции числа импульсов во входных последоватетьностях при появлении пропусков импульсов,

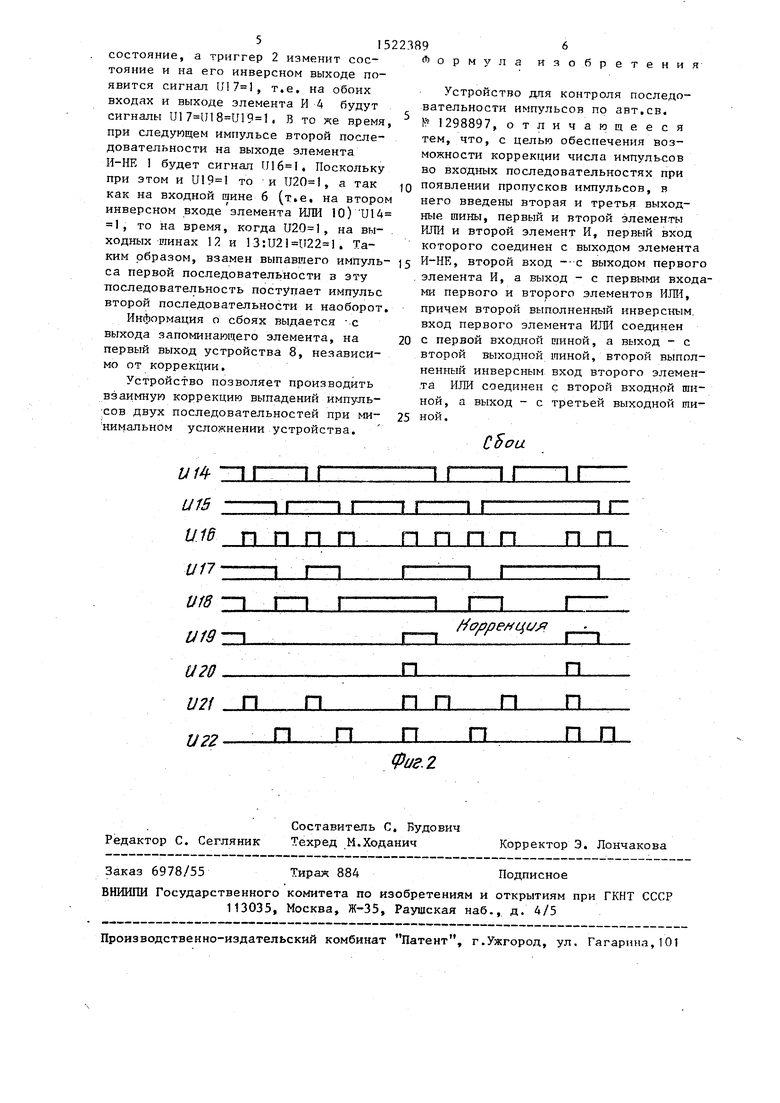

.На фиг.I показана структурная электрическая схема устройства; на фиг.2 - временные диаграммы, поясняющие его работу.

Устройство (fmr.lj содержит элемент И-НЕ 1, выход которого соединил с С-входами первого и второго триггеров 2 и 3, инверсные выходы которых соединены.соответственно с первым и- вторым входам первого элемента 4 И выход которого соединен со входом элмента 5 памяти. Первый и второй входы элемента И-НЕ 1 соединены соответ ственно с первой и,.второй входными птинами & и 7, а выход элемента 5 памяти с первой выходной шиной 8. Выход элемента Й-НЕ 1.соединен с первым входом второго элемента И 9, выход которого соединен с первыми входами первого и второго элементов ИЛИ 10 и П. Выход элемента ИЛИ 10, соединен со второй выходной пшной 12 а выход элемента ИЛИ 11 - с третьей выходной шиной 13. Выход элемента И. соединен со вторым-входом элемента И 9, первый вход элемента Й-НЕ 1 со

вторым, выполненным инверсным входом элемента ИЛИ 10 и с триггера 2, а второй вход элемента И-НЕ 1 - со вторым выполненным инверсным вхо- дом элемента ИЛИ 11 и с R-входом триггера 3.

Устройство работает следующим образом. .

В исходном состоянии (цепи уста- НОНКИ в исходное состояние не показаны) на входных шинах 6 и 7 уровни ло; гической 1 (фиг.2, 14 и 15), т.е. на R-входак триггеров 2 и 3 - логическая Ч, а на С-входах (фиг.2-16) логический О, на инверсных выходах триггеров 2 и 3, .т.е. на первом входе (фиг.2-17) и втором входе (Лиг.2- 18) элемента И 4 -г логическая 1, на выходе элемента И 4 (фиг,2-19) и на шине 8 устройства - логическая I, на выходе элемента И 9 - логический О (фиг.2-20), на второй и третьей выходных шинах 12 и 13

0

0

Q

(фиг.2-21 и 22) - логический О. Для определенности считаем, что оба триггера 2 и 3 таковы, что производят счет по переднему фронту импульсов подаваемых на П-входы, при разрешающем сигнале (уровень логической I) на R-входах; устанавливаются в исходные состояния уровнем логического 0 на R-входах и любом сигнале на С-входах.

При .поступлении на шину 6 сигнала первой последовательности U14 О (фиг.2-14), на шине 7 (фиг.2-15) сох- 5 раняется сигнал логической 1 , а на Н-вход триггера 2 будет подан сигнал логического О, подтверждающий исходное состояние триггера 2, а на Н-входе триггера 3 по-прежнему присутствует логическая I, и передний фронт 1116 перебросит триггер 3 в состояние, при котором сигнал на его инверсном выходе примет значение (фиг.2-16,17 и 18).

При поступлении на шину 7 импульса второй последовательности (когда.уже опять ) триггер 2 перебросится в состояние передним фронтом сигнала , поступившим .на его С-вход, а триггер 3 вернется в исходное состояние сигналом и так далее.

В обоих случаях при правильном чередовании импульсор обеих последовательностей они будут воспроизводить- ся соответственно на выходных шинах 12 и 13.

Пусть теперь в первой последовательности импульсов на шине 6 произошел сбой в виде пропуска очередного импульса (фиг.2-14). Тогда после прихода сигнала второй последовательности триггер 3 останется в исходном состоянии и на его инверсном

5

0

5

выходе будет уровень логической 1 , а триггер 2 будет работать в счетном режиме и на его инверсном выходе сменяется сигнал логической Г, на логический О, и следовательно, на выходе элемента И 4 сигнал и 19 сменится с логического О на логическую 1. При этом после прохождения последнего импульса второй цоследо- вательности перед пропуском импульса в первой последовательности триггер 2 бедут в состоянии, ког,.ч сигнал на его инверсном выходе равен . С приходом следующего импульса на шину 7 устройства триггер 3 сохраняет свое

состояние, а триггер 2 изменит состояние и на его инверсном выходе появится сигнал , т.е. на обоих входах и выходе элемента И 4 будут сигналы . В то же время, при следующем импульсе второй последовательности на выходе элемента И-НЕ 1 будет сигнал . Поскольку при этом и то и , а так как на входной шине б (, на втором инверсном входе элемента ИЛИ 10) 1114 1, то на время, когда , на выходных шинах 12 и 13:U2 U22 1. Та

КИМ образом, взамен выпавшего импуль- 5 И-НЕ, второй вход --с выходом первого

са первой последовательности з эту последовательность поступает импульс второй последовательности и наоборот.

Информация о сбоях выдается -с выхода запоминающего элемента, на 20 первый выход устройства 8, независимо от коррекции.

Устройство позволяет производить взаимную коррекцию выпадений импуль- сов двух последовательностей при ми- 25 нимальном

элемента И, а выход - с первыми входами первого и второго элементов lOTi, причем второй выполненный инверсным, вход первого элемента ИЛИ соединен с первой входной шиной, а выход - с второй выходной ииной, второй выполненный инверсным вход второго элемента ИЛИ соединен с второй входной шиной, а выход - с третьей выходной тиной.

Редактор С. Сегляник

Составитель С, Будович Техред М.Ходанич

Заказ 6978/55

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Лормула изобретения

Устройство для контроля последовательности импульсов по авт.ев, Р 1298897, отличающееся тем, что, с целью обеспечения возможности коррекции числа импульсов во входных последовательностях при появлении пропусков импульсов, в него введены вторая и третья выходные шины, первый и второй элементы ИЛИ и второй элемент И, первый вход которого соединен с выходом элемента

элемента И, а выход - с первыми входами первого и второго элементов lOTi, причем второй выполненный инверсным, вход первого элемента ИЛИ соединен с первой входной шиной, а выход - с второй выходной ииной, второй выполненный инверсным вход второго элемента ИЛИ соединен с второй входной шиной, а выход - с третьей выходной тиной.

Корректор Э. Лончакова

Подписное

| Устройство для контроля последовательности импульсов | 1985 |

|

SU1298897A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1987-10-06—Подача