(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ

ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения свойств полноты логических функций | 1984 |

|

SU1170446A1 |

| Устройство для автоматической компенсации емкостного тока однофазного замыкания на землю | 1982 |

|

SU1107214A1 |

| Устройство для контроля последовательности импульсов | 1984 |

|

SU1175030A1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| Устройство для контроля последовательности импульсов | 1987 |

|

SU1503069A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU934554A1 |

| РЕЛЕ ЧАСТОТЫ ИЛИ ФАЗЫ | 1993 |

|

RU2056693C1 |

| Устройство для расширения временных интервалов | 1986 |

|

SU1406561A1 |

| Устройство для программного управления механизмами | 1986 |

|

SU1409972A1 |

| Формирователь сигналов специальной формы | 1988 |

|

SU1550604A1 |

1

Изобретение относится к импульсной технике и предназначено для контроля последовательности входных импульсов.

Известно устройство для контроля . последовательности импульсов, содержащее триггеры контроля и элемент памяти tl Х

Недостатком этого устройства является недостаточно высокая точность контроля.

Наиболее близким по технической сущности к изобретению является устройство для контроля последовательности импульсов.содержащее триггеры

и запоминающий элемент 21. .,. .

Недостатком известного устройства является недостаточно высокая точность контроля.

Цель изобретения - повышенке точности контроля.

Поставленная цель достигается тем, что в устройство для контроля последовательности импульсов, содержащее

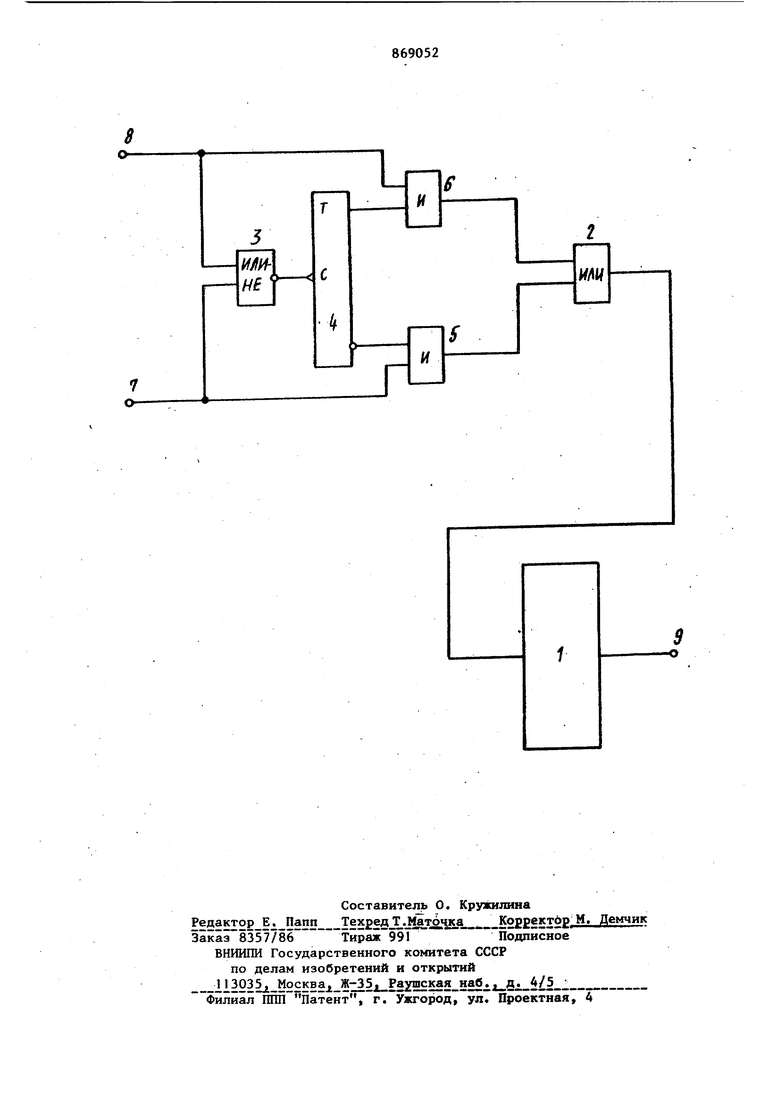

триггер и запоминающий элемент, введены элементы И, элемент ИЛИ, элемент ИЛИ-НЕ, первый и второй входы которого соединены с первыми входа ми соответственно первого и второго элементов И и соответствующими входными шинами, а выход - со счетным входом триггера, прямой и инверсный выходы которого соединены со вторьп и входами соответственно первого и второго элементов И, выходы которых через элемент ИЛИ подключены ко входу запоминающего элемента.

На чертеже представлена структурная схема устройства.

Оно содержит запоминающий элемент 1, элемент ИЛИ 2, элемент ИЛИ-НЕ 3, триггер-4, элементы И 5 и 6, входные нтны 7 и 8 и выходную шину 9.

Устройство работает следующим образом.

В исходном состоянии на выходной шине 9 запоминающего элемента логический , на выходе элемента 3 ИЛИ-НЕ 3 логическая единица, на прямом выходе триггера 4 логический нуль , на инверсном выходе логическая единица. Причем триггер срабатывает при переходе сигнала на счетном входе с логического нуля в логическую единицу. Когда на шине 8 появляется логическая единица, на выходе элемента И 6 сохраняется логический нуль, так как с прямого выхода триггера 4 снимается логический нуль. Когда на шине 8 устанавливается логический нуль, триггер 4 перебрасывается,на прямом его выходе устанавливается логическая единица, на выходе элемента И 6 сохраняется логический нуль, на инверсном выходе триггера 4 устанавливается логический нуль. Когда сигнал, соответствугощрта уро ню логической единицы поступает на ши ну 7, на выходе элемента И 5 сохраняется логический нуль, а триггер 4 находится в состоянии, когда с инверсного выхода снимается сигнал, соответствующий уровню логического нуля. С окончгнием сигнала логической единицы, на иине 7 триггер 4 перебрасывается в исходное состояние. Допустим еперь, что устройство находится в исходном состоянии и на шине 8 логическая единица не появляется, тогда с приходом импульса на шину 7 элемент И 5 открывается, так как на инверсном выходе триггера 4 сохраняется сигнал, соответствующий ypoBifio логической единицы. Сигнал с выхода элемента И 5 через элемент ИЛИ 2 поступает на вход элемента 1. На шине 9 фиксируется сигнал неисправности. Если в процессе работы устройства после появления импульса на шине 8 не появляется импульс на шине 7, то следующий импульс, поступающий на шину 8, открывает элемент И 6, и на шине 9 устанавливается сигнал неисправности. Предлагаемое устройство позволяет в заданный промежуток времени фиксировать отсутствие импульса или наличие импульсов более одного независимо по какому входу произошел сбой информации. Использование устройства в импульсной технике повышает точность контроля, так как позволяет своевременно обнаружить отказ источников импульсов. Формула изобретения Устройство для контроля последовательности импульсов, содержащее триггер и запоминающий элемент, отличающееся тем, что, с целью повышения точности контроля, в него введены элементы И, элемент ИЛИ, элемент ИЛИ-НЕ, первый и второй входы которого соединены с первьми входами соответственно первого и второго элементов И и соответствующими входными шинами, а выход со счетным входом триггера, прямой и инверсный выходы которого соединены со вторыми входами соответственно первого и второго элементов И, выходы которых через элeмeнt ИЛИ подключены ко входу запоминающего эле мента. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 371691, кл. И 03 К 21/34, 1971. 2.Авторское свидетельство СССР № 558402, кл. Н 03 К 21/34, 1974.

ww

Авторы

Даты

1981-09-30—Публикация

1980-01-24—Подача