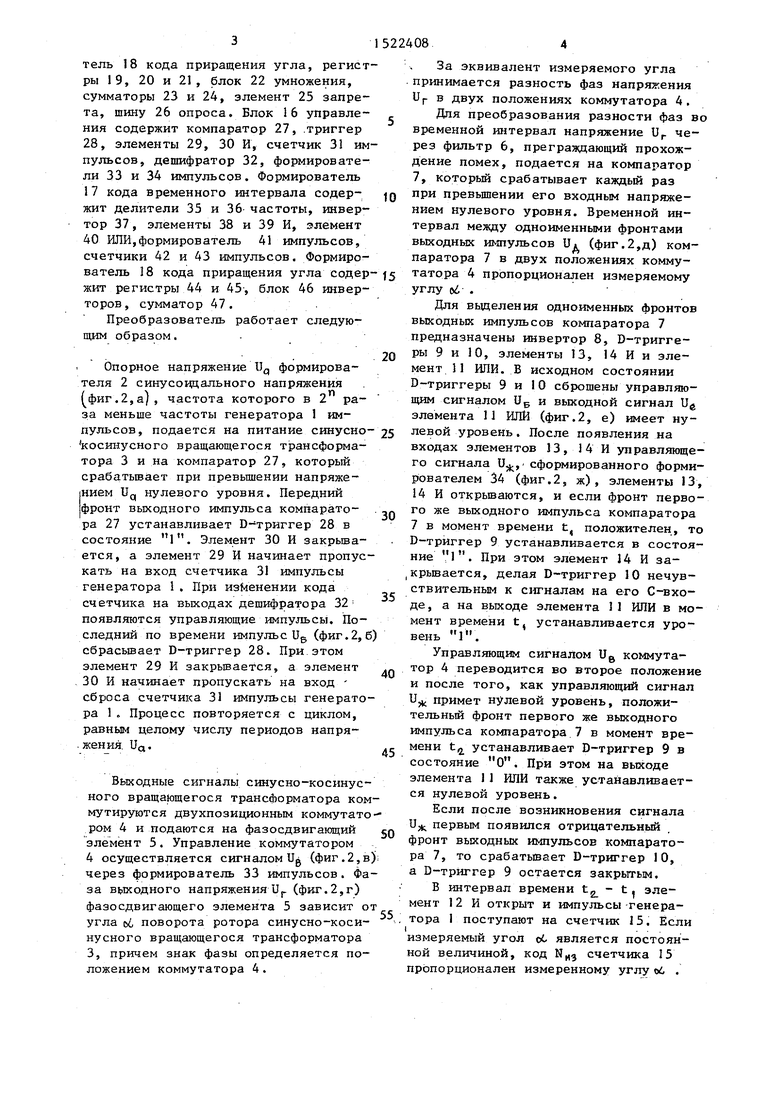

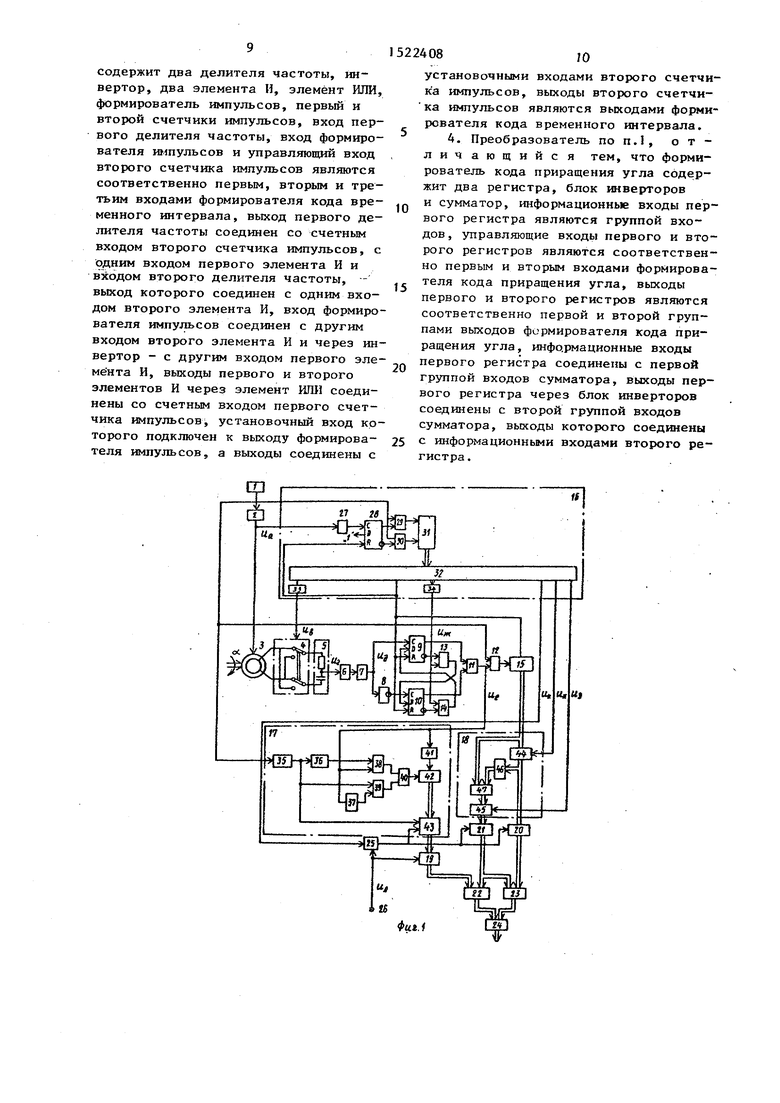

тель 18 кода приращения угла, регистры 19, 20 и 21 , блок 22 умножения, сумматоры 23 и 24, элемент 25 запрета, шину 26 опроса. Блок 16 управления содержит компаратор 27, .триггер 28, элементы 29, 30 И, счетчик 31 импульсов, дешифратор 32, формирователи 33 и 34 импульсов. Формирователь 17 кода временного интервала содер- жит делители 35 и 36 частоты, инвертор 37, элементы 38 и 39 И, элемент 40 ИЛИ,формирователь 41 импульсов, счетчики 42 и 43 импульсов. Формирователь 18 кода приращения угла содер- жит регистры 44 и 45, блок 46 инверторов, сумматор 47. .

Преобразователь работает следующим образом.

.

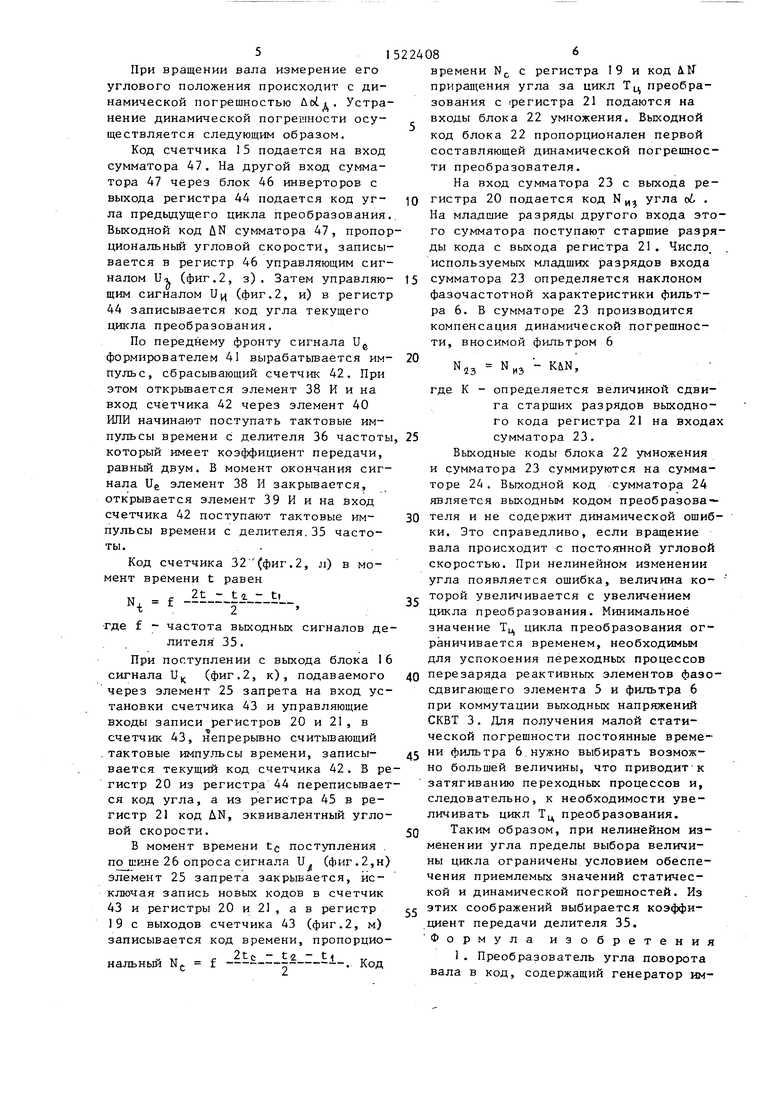

Опорное напряжение U, формирователя 2 синусоидального напряжения (фиг.2,а), частота которого в 2 раза меньше частоты генератора 1 импульсов, подается на питание синусно- косинусного вращающегося трансформатора 3 и на компаратор 27, который срабатьгоает при превьшении напряжением Uq нулевого уровня. Передний фронт выходного импульса компаратора 27 устанавливает В- триггер 28 в состояние 1. Элемент 30 И закрьша- ется, а элемент 29 И начинает пропускать на вход счетчика 31 импульсы генератора 1. При изменении кода счетчика на выходах дешифратора 32- появляются управляющие импульсы. Последний по времени импульс Ug (фиг.2, б сбрасьшает D-триггер 28. При этом элемент 29 И закрывается, а элемент 30 И начинает пропускать на вход сброса счетчика 31 импульсы генератора I. Процесс повторяется с циклом, равным целому числу периодов напря- . . UQ.

Выходные сигналы синусно-косинусного вращающегося трансформатора коммутируются двухпозиционным коммутатором 4 и Подаются на фазосдвигающий элемент 5. Управление коммутатором 4 осуществляется сигналом Ug (фиг.2,в через формирователь 33 импульсов. Фаза вьтходного напряжения Up (фиг.2,г) фазосдвигающего элемента 5 зависит о угла di поворота ротора синусно-коси- нусного вращающегося трансформатора 3, причем знак фазы определяется положением коммутатора 4 .

Q 5

0

5 с

0

5

За эквивалент измеряемого угла принимается разность фаз напряжения Up Б двух положениях коммутатора 4.

Дпя преобразования разности фаз во временной интервал напряжение U. через фильтр 6, преграждающий прохождение помех, подается на компаратор 7, который срабатывает каждый раз при превьшении его входным напряжением нулевого уровня. Временной интервал между одноименными фронтами выходных импульсов Од (фиг.2,д) компаратора 7 в двух положениях коммутатора 4 пропорционален измеряемому углу oi- .

Для выделения одноименных фронтов выходных импульсов компаратора 7 предназначены инвертор 8, D-тригге- ры 9 и 10, элементы 13, 14 И и элемент П ИПИ. В исходном состоянии D-триггеры 9 и 10 сброшены управляющим сигналом Up и вькодной сигнал Ug элемента И ИЛИ (фиг.2, е) имеет нулевой уровень. После появления на входах элементов J3, 14 И управляющего сигнала U.J-, сформированного формирователем 34 (фиг.2, ж), элементы 13, 14 И открьшаются, и если фронт первого же выходного импульса компаратора 7 в Момент времени t положителен, то D-триггер 9 устанавливается в состояние 1. При этом элемент 14 И за- |Крьюается, делая D-триггер 10 нечувствительным к сигналам на его С-вхо- де, а на выходе элемента 11 ИПИ в мо5с

Q

0

мент времени It t II

t устанавливается уровень

Управляющим сигналом Ug коммутатор 4 переводится во второе положение и после того, как управляющий сигнал и примет нулевой уровень, положительный фронт первого же выходного импульса компаратора 7 в момент времени t устанавливает D-триггер 9 в состояние О. При этом на выходе элемента 11 ИЛИ также устанавливается нулевой уровень.

Если после возникновения сигнала Ujt; первым появился отрицательный фронт выходных импульсов компаратора 7, то срабатьюает D-триггер 10, а D-триггер 9 остается закрытым.

В интервал времени t - t элемент 12 И открыт и импульсы генератора 1 поступают на счетчик 15. Если измеряемый угол ot является постоянной величиной, код N счетчика 15 пропорционален измеренному углу об .

При вращении вала измерение его углового положения происходит с динамической погрешностью L Устранение динамической погрешности осуществляется следующим образом.

Код счетчика 15 подается на вход сумматора 47, На другой вход сумматора 47 через блок 46 инверторов с выхода регистра 44 подается код угла предыдущего цикла преобразования Выходной код UN сумматора 47, пропор циональньй угловой скорости, записывается в регистр 46 управляющим сигналом U-i (фиг.2, з) . Затем управляю- щим сигналом } (фиг.2, и) в регистр 44 записывается код угла текущего цикла преобразования.

По переднему фронту сигнала Ug формирователем 41 вырабатьгоается импульс, сбрасывающий счетчик 42. При этом открьшается элемент 38 И и на вход счетчика 42 через элемент 40 ИЛИ начинают поступать тактовые импульсы времени с делителя 36 частоты который имеет коэффициент передачи, равньй двум. В момент окончания сигнала Ug элемент 38 И закрьшается, открывается элемент 39 И и на вход счетчика 42 поступают тактовые импульсы времени с делителя.35 частоты..

Код счетчика 32(фиг.2, л) в момент времени t равен

N,

Ч

где f - частота выходных сигналов де

лителя 35. При поступлении с выхода блока

сигнала U| (фиг.2, к), подаваемого через элемент 25 запрета на вход установки счетчика 43 и управляющие входы записи регистров 20 и 21, в счетчик 43, непрерывно считывающий тактовые импульсы времени, записывается текущий код счетчика 42. В регистр 20 из регистра 44 переписьгоает ся код угла, а из регистра 45 в регистр 21 код AN, эквивалентный угловой скорости.

В момент времени t поступления . 26 опроса сигнала U. (фиг.2,н) элемент 25 запрета закрывается, исключая запись новых кодов в счетчик 43 и регистры 20 и 2, а в регистр 19 с выходов счетчика 43 (фиг.2, м) записывается код времени, пропорцио- - 2tc: - te - ti

нальный N,

Код

10

, - 15

, 20

25

-

времени N с регистра 19 и код МГ приращения угла за цикл Т ц преобразования с регистра 21 подаются на входы блока 22 умножения. Выходной код блока 22 пропорционален первой составляющей динамической погрешности преобразователя.

На вход сумматора 23 с выхода регистра 20 подается код N , угла oL . На младшие разряды другого входа этого сумматора поступают старшие разряды кода с выхода регистра 21 . Число. . используемых младших разрядов входа сумматора 23 определяется наклоном фазочастотной характеристики фильтра 6. В сумматоре 23 производится компенсация динамической погрешности, вносимой фильтром 6

Н„ N,3 - K&N,

где К - определяется величиной сдвига старших разрядов выходного кода регистра 21 на входах сумматора 23.

Выходные коды блока 22 умножения и сумматора 23 суммируются на сумматоре 24 . Выходной код сумматора 24 является выходным кодом преобразовав теля и не содержит динамической ошибки. Это справедливо, если вращение вала происходит с постоянной угловой скоростью. При нелинейном изменении угла появляется ошибка, величина ко- торой увеличивается с увеличением цикла преобразования. Минимальное значение Тц цикла преобразования ограничивается временем, необходимым для успокоения переходных процессов

40 перезаряда реактивных элементов фазо- сдвигающего элемента 5 и фильтра 6 при коммутации выходных напряжений СКВТ 3, Для получения малой статической погрешности постоянные време45 ни фильтра 6.нужно выбирать возможно большей величины, что приводит-к затягиванию переходных процессов и, следовательно, к необходимости увеличивать цикл Тц преобразования,

50 Таким образом, при нелинейном изменении угла пределы выбора величины цикла ограничены условием обеспечения приемлемых значений статической и динамической погрешностей. Из

ГС ЭТИХ соображений выбирается коэффициент передачи делителя 35. Формула изобретения

1, Преобразователь угла поворота вала в код, содержащий генератор им30

35

пульсов, выход которого соединен с первыми входами блока управления и первого элемента И и входом формирователя синусоидального напряжения, выход которого соединен с входом си- нусно-косинусного вращающегося трансформатора и вторым входом блока управления, выходы синусно-косинусного вращающегося трансформатора соедрш.ены с информационными входами коммутатора, выходы коммутатора соединены с входами фазосдвигающего элемента, фильтр, выход которого через компаратор соединен с входом инвертора, первый и второй триггеры, прямые выходы которых соединены с входами элемента ШИ, а инверсные выходы соединены с первыми входами соответственно второго и третьего элементов И, выход элемента ИЛИ соединен с вторым входом первого элемента И, выход которого соединен со счетным входом счетчика импульсов, первый и второй выходы блока управления соединены соответственно с управляющим входом коммутатора и входами установки первого и второго триггеров, отличающийся тем, что, с целью уменьшения динамической погрешности преобразователя, в него введены формирователь кода временногоинтервала формирователь кода приращения угла, три регистра, два сумматора, блок умножения, элемент запрета и шина опроса, которая соединена с управляющими входами элемента запрета и первого регистра, выходы генератора импульсов , элемента ИЛИ и элемента запрета соединены соответственно с первым, вторьм и третьим входами формирователя кода временного интервала, выходы которого соединены информационными входами первого регистра, третий и четвертый выходы блока управления и группа выходов счетчика импульсов соединены соответственно с первым и вторым входами и группой входов формирователя кода приращения угла, первая и вторая группы вь ходов которого соединены с информационными вхо дами соответственно второго и третье го регистров, пятьй выход блока управления соединен с информационным ВХОДОМ элемента запрета, выход которого соединен с управляющими входами второго и третьего регистров, выходы первого и третьего регистров соединены с входами блока умножения.

10

15

20

25

30

35

40

45

50

55

выходы второго регистра и выходы старших разрядов третьего регистра соединены с входами первого сумматора, выходы которого и выходы блока умножения соединены с входами второго сумматора, выходы которого являются выходами преобразователя, тестой выход блока управления соединен с вторыми входами второго и третьего элементов И, выходы которых соединены с информационными входами соответственно второго и первого триггеров, выходы компаратора и инвертора соединены с управляющими входами соответственно первого и второго триггеров, второй выход блока управления соединен с установочным входом счетчика импульсов, а выход фазосдвигающего элемента соединен с входом фильтра.

2.Преобразователь по п. 1 , отличающийся тем, что блок управления содержит компаратор, триггер, два элемента И, счетчик импульсов, дешифратор и два формирователя импульсов, один вход первого элемента И и вход компаратора являются соответственно первым и вторым входами блока управления, один вход первого элемента И соединен с одним входом второго элемента Н, выход компаратора соединен с управляющим входом триггера, информационный вход которого подключен к шине логической единицы, прямой и инверсный выходы триггера соединены с другими входами первого и второго элементов И соответственно, выходы первого и второго элементов И соединены соответственно со счетным и установочным входами счетчика импульсов, выходы разрядов счетчика импульсов соединены с входами дешифратора, первый выход дешифратора соединен с входом первого формирователя импульсов, выход которого является первым выходом блока управления, второй, третий, четвертый и пятый выходы дешифратора являются соответственно вторьм, третьим, четвертым и пятым выходами блока управления, шестой выход дешифратора соединен с входом второго формирователя импульсов, вькод которого является шестым выходом блока управления, а второй выход дешифратора соединен с установочным входом триггера.

3.Преобразователь по п.1, отличающийся тем, что формирователь кода временного интервала

Фut.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь углового перемещения в код | 1985 |

|

SU1279070A1 |

| Преобразователь угол-код | 1984 |

|

SU1179540A1 |

| Преобразователь угол-фаза-код | 1984 |

|

SU1185608A1 |

| Преобразователь угла поворота вала в код | 1978 |

|

SU763938A1 |

| Генератор псевдослучайной М-последовательности | 1985 |

|

SU1264317A2 |

| Устройство для преобразования частоты следования импульсов | 1978 |

|

SU764114A1 |

| Измеритель параметров качества электроэнергии трехфазной сети | 1979 |

|

SU1164616A1 |

| Способ преобразования угла поворота вала в код и устройство для его осуществления | 1985 |

|

SU1295521A1 |

| Многоканальное измерительное устройство | 1988 |

|

SU1617430A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью уменьшения динамической погрешности в преобразователь угла поворота вала в код, содержащий генератор импульсов, формирователь синусоидального напряжения, синусно-косинусный вращающийся трансформатор (СКВТ), коммутатор, фазосдвигающий элемент, фильтр, компаратор, инвертор, два триггера, элемент ИЛИ, три элемента И, счетчик импульсов, блок управления, введены формирователь кода временного интервала, формирователь кода приращения угла, три регистра, блок умножения, два сумматора, элемент запрета и шина опроса. В двух положениях коммутатора выходные сигналы СКВТ подаются на входы фазосдвигающего элемента, в результате чего в счетчике формируется код мгновенного значения угла поворота. В формирователе кода временного интервала формируется код, соответствующий временному интервалу между серединой интервала формирования кода в счетчике и импульсом опроса. В формирователе кода приращения угла формируется разность между текущим и предыдущим значениями кода в счетчике, которая является эквивалентом кода скорости вала. В блоке умножения выходные коды двух формирователей перемножаются, в результате чего выделяется составляющая динамической погрешности, которая суммируется с выходным кодом счетчика. 3 з.п. ф-лы, 2 ил.

,2

| Преобразователь угол-код | 1973 |

|

SU487405A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь угол-фаза-код | 1984 |

|

SU1185608A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-11-15—Публикация

1988-02-25—Подача