Изобретс1гие относится к автоматике и вычислительной технике, в частности к функцио.пальиым преобразователям напряжения в код, работа которых, основана на уравновешивании входного напряжения развертывающим ступенчатым напряжением.

Цель изобретения - расширение области применения путем вычисления разнести нелинейных преобразований в рднократном и периодическом режимах.

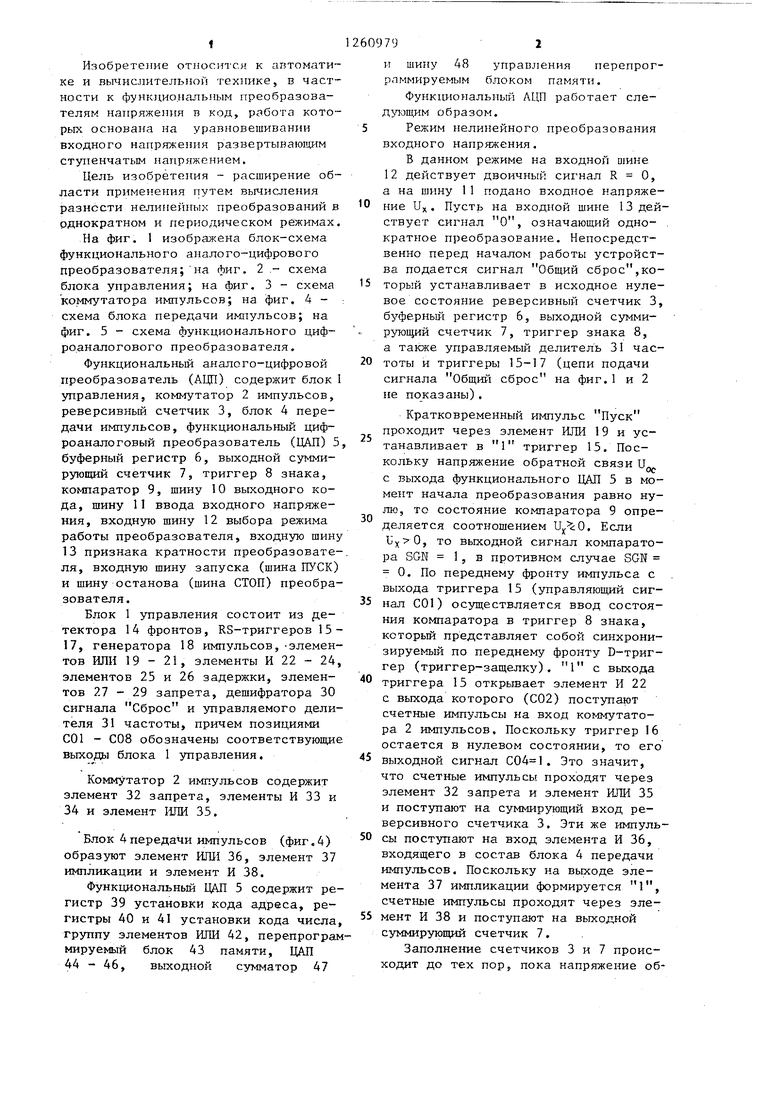

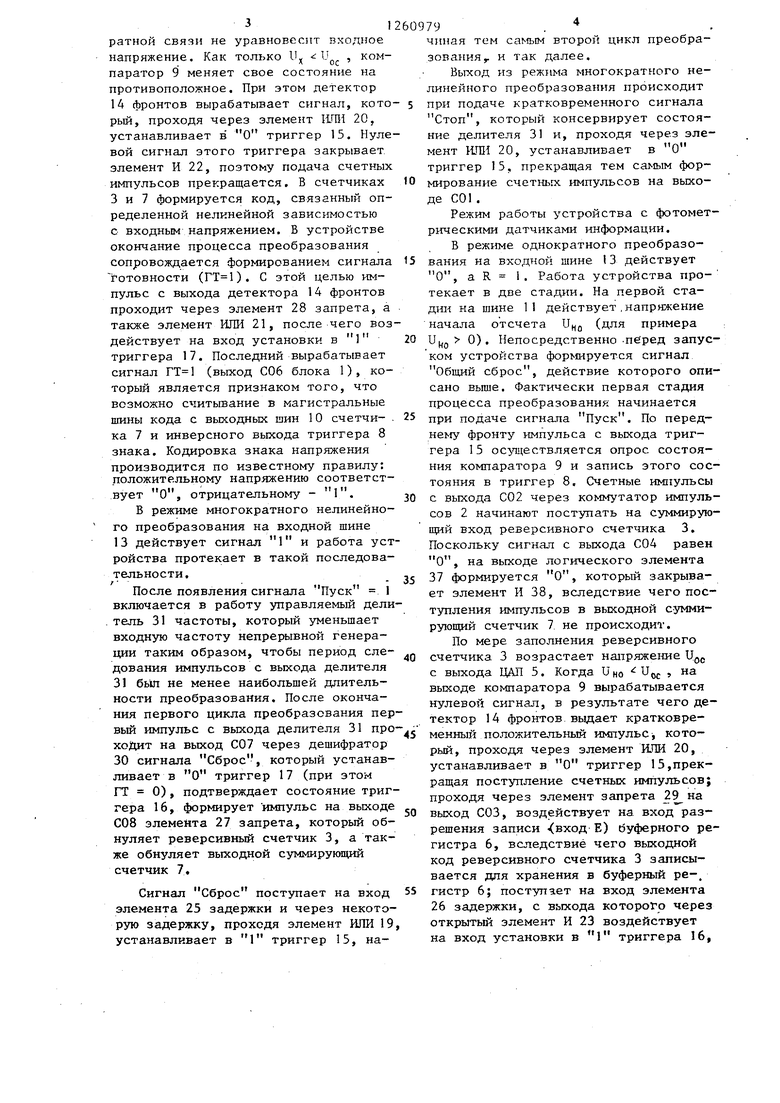

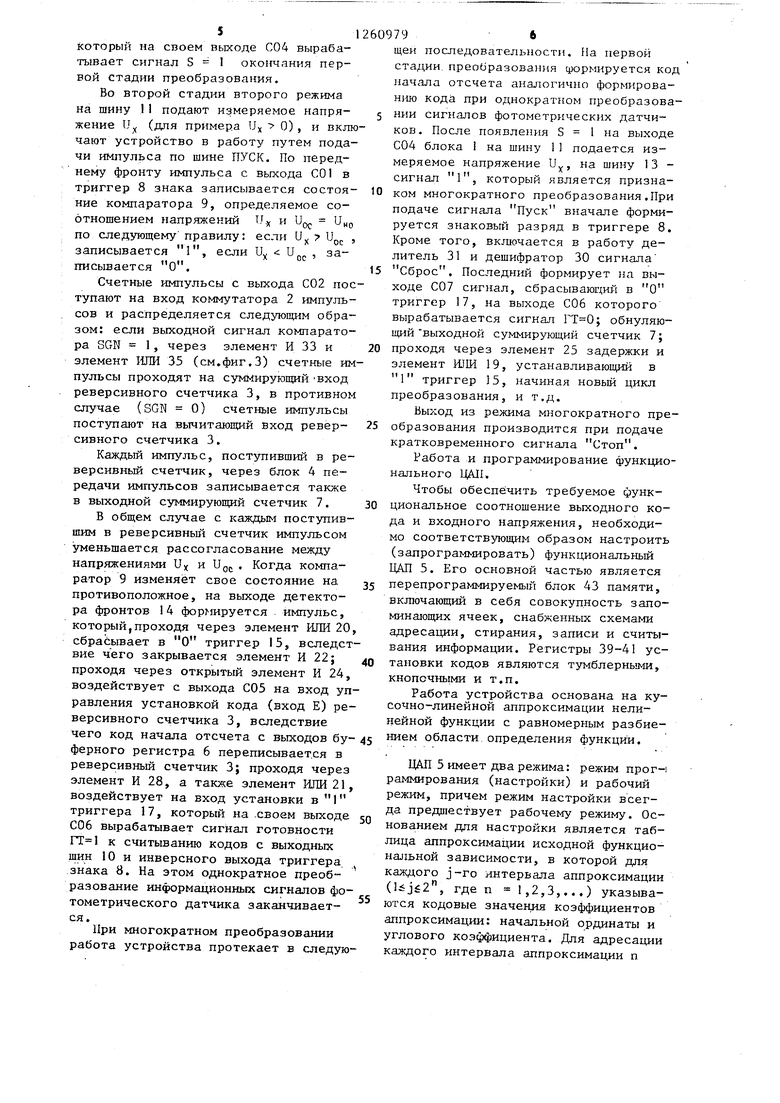

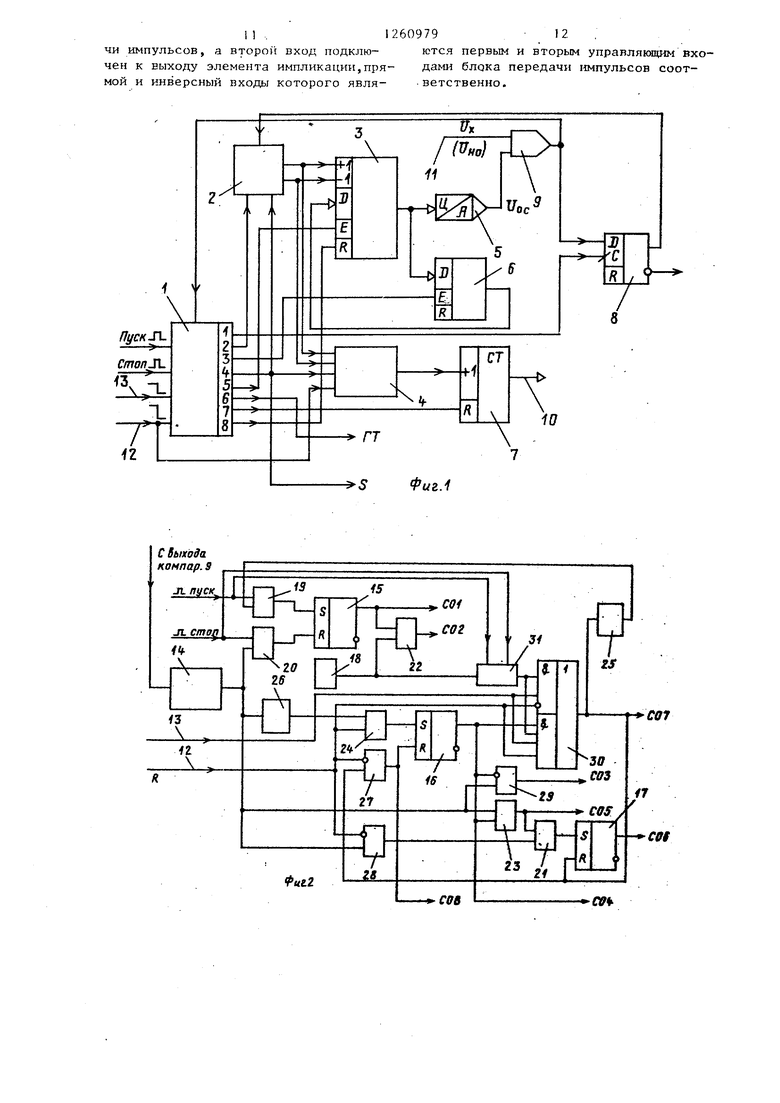

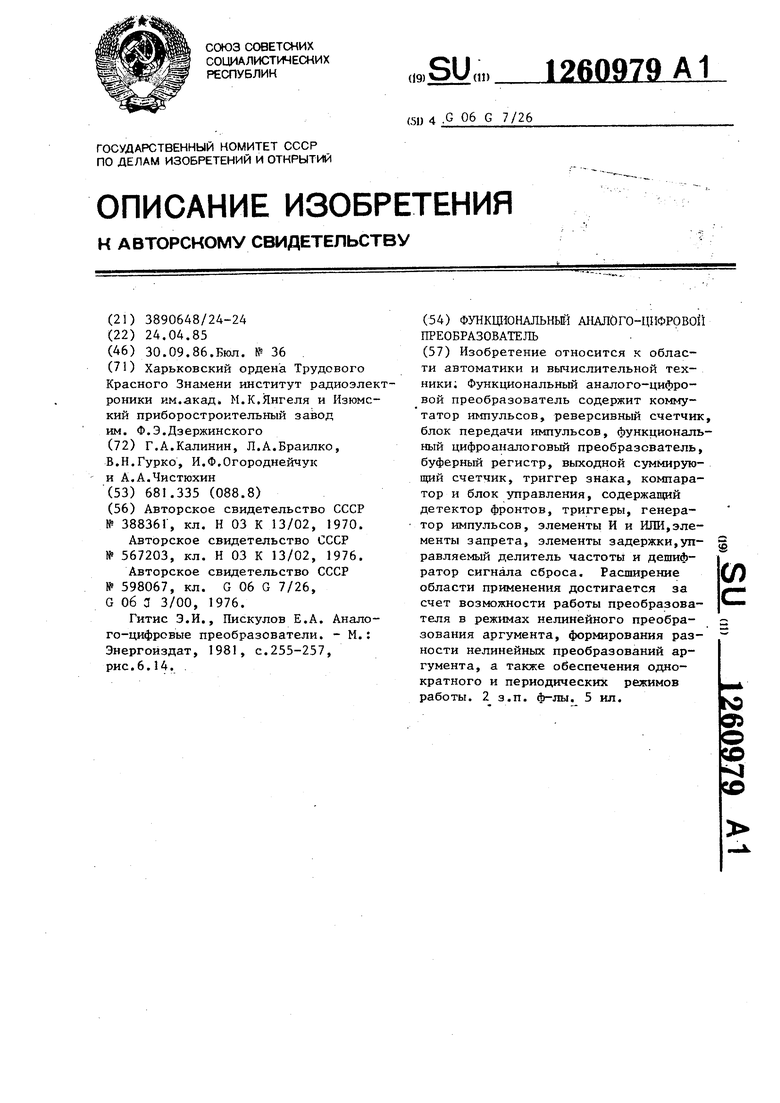

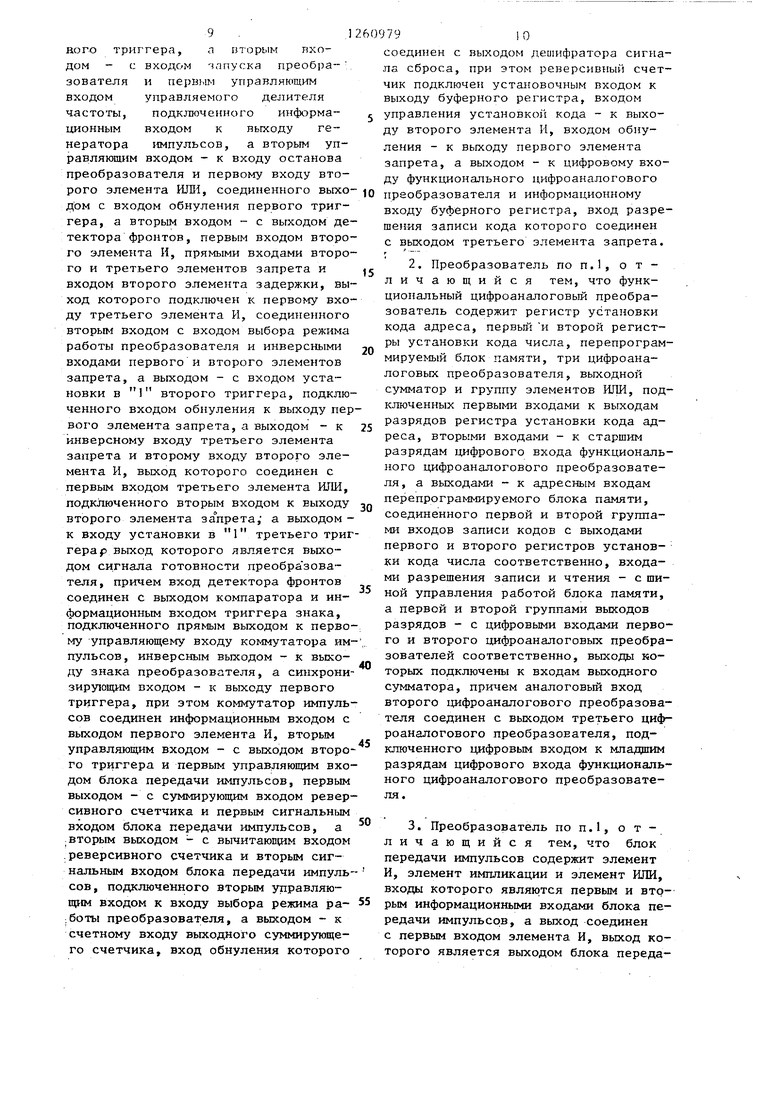

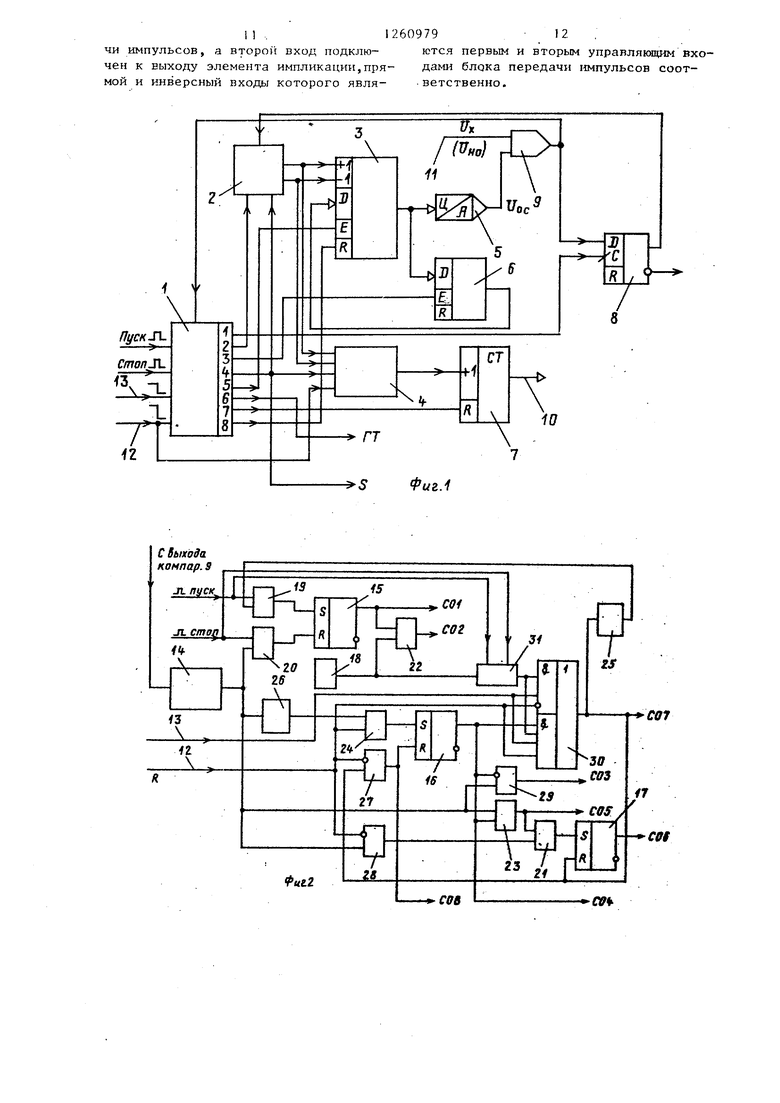

На фиг. 1 изображена блок-схема функционального аналого-цифрового преобразователя; на фиг. 2 .- схема блока управления; на фиг. 3 - схема коммутатора импульсов; на фиг. 4 - схема блока передачи импульсов; на фиг. 5 - схема функционального диф- роаналогового преобразователя.

Функциональньм аналого-цифровой преобразователь (АЦП) содержит блок 1 управления, коммутатор 2 импульсов, реверсивный счетчик 3, блок 4 передачи импульсов, функциональный циф- роаналоговый преобразователь (ДАЛ) 5 буферный регистр 6, выходной суммирующий счетчик 7, триггер 8 знака, компаратор 9, шину 10 выходного кода, шину 11 ввода входного напряжения, входную шину 12 выбора режима работы преобразователя, входную шину 13 признака кратности преобразователя, входную шину запуска (шина ПУСК) и шину останова (шина СТОП) преобразователя.

Блок 1 управления состоит из детектора 14 фронтов, RS-триггеров 15- 17, генератора 18 импульсов,-элементов ИЛИ 19 - 21, элементы И 22 - 24, элементов 25 и 26 задержки, элементов 27 - 29 запрета, дешифратора 30 сигнала Сброс и управляемого делителя 31 частоты, причем позициями С01 - С08 обозначены соответствующие выходы блока 1 управления.

Коммутатор 2 импульсов содержит элемент 32 запрета, элементы И 33 и 34 и элемент ИЖ 35.

Блок 4передачи импульсов (фиг,4) образуют элемент ИЛИ 36, элемент 37 импликации и элемент И 38.

Функциональный ЦАП 5 содержит регистр 39 установки кода адреса, регистры 40 и 41 установки кода числа группу элементов ИЛИ 42, перепрограммируемый блок 43 памяти, ЦАП 44 - 46, выходной сумматор 47

609792

и шину 48 управления перепрог- рлммируемым блоком памяти.

Функциональный АЦП работает сле- д,тош,им образом.

5 Режим нелинейного преобразования входного напряжения.

В данном режиме на входной шине 12 действует двоичный сигнал R О, а на шину 11 подано входное напряже- 0 ние и. Пусть на входной шине 13 действует сигнал О, означающий одно- . кратное преобразование. Непосредственно перед началом работы устройства подается сигнал Общий сброс,который устанавливает в исходное нулевое состояние реверсивный счетчик 3, буферный регистр 6, выходной суммирующий счетчик 7, триггер знака 8, а также управляемый делитель 31 час- 20 тоты и триггеры 15-17 (цепи подачи сигнала Общий сброс на фиг.1 и 2 не показаны).

Кратковременный импульс Пуск

15

проходит через элемент ИЛИ 19 и устанавливает в 1 триггер 15. Поскольку напряжение обратной связи U с выхода функционального ДАЛ 5 в момент начала преобразования равно нулю, то состояние компаратора 9 определяется соотношением . Если Uj(0, то выходной сигнал компаратора SGN 1, в противном случае SGN 0. По переднему фронту импульса с выхода триггера 15 (управляющий сигнал С01) осуществляется ввод состояния компаратора в триггер 8 знака, который представляет собой синхронизируемый по переднему фронту D-триг- гер (триггер-защелку), 1 с выхода триггера 15 открывает элемент И 22 с выхода которого (С02) поступают счетные импульсы на вход коммутатора 2 импульсов. Поскольку триггер 16 остается в нулевом состоянии, то его

выходной сигнал . Это значит, что счетные импульсы проходят через элемент 32 запрета и элемент ИЛИ 35 и поступают на суммирующий вход реверсивного счетчика 3, Эти же импульсы поступают на вход элемента И 36, входящего в состав блока 4 передачи импульсов. Поскольку на выходе элемента 37 импликации формируется 1, счетные импульсы проходят через элемент И 38 и поступают на выходной суммирующий счетчик 7.

Заполнение счетчиков 3 и 7 происходит до тех пор, пока напряжение обратной связи не уравновесит входное напряжение. Как только U - ос паратор 9 меняет свое состояние на противоположное. При этом детектор 14 фронтов вырабатывает сигнал, кото- рый, проходя через элемент lUM 20, устанавливает в О триггер 15. Нулевой сигнал этого триггера закрывает элемент И 22, поэтому подача счетных импульсов прекращается, В счетчиках 3 и 7 формируется код, связанный определенной нелинейной зависимостью с входным напряжением. В устройстве окончание процесса преобразования сопровождается формированием сигнала готовности (), С этой целью импульс с выхода детектора 14 фронтов проходит через элемент 28 запрета, а также элемент ИЛИ 21, после чего воздействует на вход установки в 1 триггера 17, Последний вырабатывает сигнал (выход С06 блока 1), который является признаком того, что возможно считывание в магистральные шины кода с выходных шин 10 счетчи- ка 7 и инверсного выхода триггера 8 знака. Кодировка знака напряжения

производится по известному правилу: положительному напряжению соответствует О, отрицательному - 1.

В режиме многократного нелинейного преобразования на входной шине 13 действует сигнал 1 и работа устройства протекает в такой последовательности.

После появления сигнала Пуск 1 включается в работу управляемый делитель 31 частоты, который уменьшает входную частоту непрерывной генерации таким образом, чтобы период следования импульсов с выхода делителя 31 бып не менее наибольшей длительности преобразования. После окончания первого цикла преобразования первый импульс с выхода делителя 31 проходит на выход С07 через дешифратор 30 сигнала Сброс, который устанавливает в О триггер 17 (при этом ГТ 0), подтверждает состояние триггера 16, формирует импульс на выходе СОВ элемента 27 запрета, который обнуляет реверсивный счетчик 3, а также обнуляет выходной суммирующий счетчик 7,

Сигнал Сброс поступает на вход элемента 25 задержки и через некоторую задержку, проходя элемент ИЛИ 19 устанавливает в 1 триггер 15, на

чиная тем самым второй цикл преобразования,, и так далее.

Выход из режима многократного нелинейного преобразования происходит при подаче кратковременного сигнала Стоп, который консервирует состояние делителя 3 и, проходя через элемент RHIi 20, устанавливает в О триггер 15, прекращая тем самым формирование счетных, импульсов на выходе С01 .

Режим работы устройства с фотомет р гческими датчиками информации.

В режиме однократного преобразования на входной шине I3 действует

О

а R 1. Работа устройства про

текает в две стадии. На первой стадии на шине 11 действует.напряжение начала отсчета (для примера

и 0) , Непосредственно -пбред запуском устройства формируется сигнал Общий сброс, действие которого описано Bbmie, Фактически первая стадия процесса преобразования начинается

при подаче сигнала Пуск. По перед- фронту импульса с выхода триггера 15 осуществляется опрос состояния компаратора 9 и запись этого состояния в триггер 8, Счетные импульсы

с выхода С02 через коммутатор импульсов 2 начинают поступать на суммирующий вход реверсивного счетчика 3, Поскольку сигнал с выхода CG4 равен О, на выходе логического элемента

37 формируется О, который закрывает элемент И 38, вследствие чего поступления импульсов в выходной сумми- руюшсий счетчик 7 не происходит.

По мере заполнения реверсивного счетчика 3 возрастает напряжегше UQ с выхода ЦАП 5, Когда UHO U , на выходе компаратора 9 вырабатывается нулевой сигнал, в результате чего детектор 14 фронтов выдает кратковременный положительный импульс, который, проходя через элемент ИЛИ 20, устанавливает в О триггер 15,прекращая поступление счетных импульсов; проходя через элемент запрета 29 на выход СОЗ, воздействует на вход разрешения записи -(вход Е) буферного регистра 6, вследствие чего выходной код реверсивного счетчика 3 записывается для хранения в буферный ре-, гистр 6; поступает на вход элемента 26 задержки, с выхода которого через открытый элемент И 23 воздействует на вход установки в 1 триггера 16,

который на своем выходе С04 вырабатывает сигнал S 1 окончания первой стадии преобразования.

Во второй стадии второго режима на шину 11 подают измеряемое напря- жение иjf (для примера Ux 0) , и включают устройство в работу путем подачи импульса по шине ПУСК, По переднему фронту импульса с выхода СО в триггер 8 знака записывается состоя- ние компаратора 9, определяемое соотношением напряжений И.х и 1 UHQ по следующему правилу: если U . , записывается 1, если U 11 , записывается О.

Счетные импульсы с выхода С02 поступают на вход коммутатора 2 импульсов и распределяется следующим образом: если выходной сигнал компаратора SGN 1, через элемент И 33 и элемент ИЛИ 35 (см.фиг.3) счетные импульсы проходят на сум14ирующий Вход реверсивного счетчика 3, в противном случае (SGN О) счетные импульсы поступают на вычитающий вход ревер- сивного счетчика 3.

Каждый импульс, поступивший в реверсивный счетчик, через блок 4 передачи импульсов записывается также в выходной суммирующий счетчик 7.

В общем случае с каждым поступившим в реверсивньш счетчик импульсом уменьшается рассогласование между напряжениями U и Ugj, . Когда компаратор 9 изменяет свое состояние на противоположное, на выходе детектора фронтов 4 формируется импуЛьс, который,проходя через элемент ИЛИ 20 сбрасывает в О триггер 15, вследствие чего закрывается элемент И 22; проходя через открытый элемент И 24, воздействует с выхода С05 на вход управления установкой кода (вход Е) реверсивного счетчика 3, вследствие чего код начала отсчета с выходов бу- ферного регистра 6 переписывается в реверсивный счетчик 3; проходя через элемент И 28, а также элемент ИЛИ 21, воздействует на вход установки в 1 триггера 17, который на .своем выходе С06 вырабатывает сигнал готовности к считыванию кодов с выходных шин 10 и инверсного выхода триггера знака 8. На этом однократное преобразование информационных сигналов фотометрического датчика заканчивается.

При многократном преобразовании работа устройства протекает в следующей последовательности. На первой стадии, преобразования формируется код начала отсчета аналогично формированию кода при однократ1 ом преобразовании сигналов фотометрических датчиков. После появления S 1 на выходе С04 блока на шину 11 подается измеряемое напряжение И, на шину 13 - сигнал 1, который является признаком многократного преобразования.При подаче сигнала Пуск вначале формируется знаковый разряд в триггере 8. Кроме того, включается в работу делитель 31 и дешифратор 30 сигнала Сброс, Последний формирует на выходе С07 сигнал, сбрасывающий в О триггер 17, на выходе С06 которого вырабатывается сигнал обнуляющий выходной суммирующий счетчик 7; проходя через элемент 25 задержки и элемент ШШ 19, устанавливающий в 1 триггер 15, начиная новый цикл преобразования, и т.д.

Выход из режима многократного преобразования производится при подаче кратковременного сигнала Стоп.

Работа и программирование функционального ЦАЛ.

Чтобы обеспечить требуемое функциональное соотношение выходного кода и входного напряжения, необходимо соответствующим образом настроить (запрограммировать) функциональньш ЦАП 5. Его основной частью является перепрограммируемьш блок 43 памяти, включающий в себя совокупность запоминающих ячеек, снабженных схемами адресации, стирания, записи и считывания информации. Регистры 39-41 установки кодов являются тумблерными, кнопочными и т.п.

Работа устройства основана на кусочно-линейной аппроксимации нелицейной функции с равномерным разбиением области определения функции.

ЦАП 5 имеет два режима: режим прогн раммирования (настройки) и рабочий режим, причем режим настройки всегда предшествует рабочему режиму. Основанием для настройки является таблица аппроксимации исходной функциональной зависимости, в которой для каждого j-ro интервала аппроксимации (, где п 1,2,3,...) указываются кодовые значения коэффициентов аппроксимации: начальной ординаты и углового коэффициента. Для адресации каждого интервала аппроксимации п

15

20

71260979

CTiipiJfHx разрядов реверсивного счетчика 3 соединяются с соответствующей группой входов группы 42 элементов ШШ. Остальные m младших разрядов реверсивного счетчика 3 подключают к 1ДИФРОВЫМ входам преобразовйтеля 46,

Непосредственно перед началом настройки осуществляется установка в О регистров 39-41 и реверсивного счетчика 3. Настройка осуществляется следующим образом. Управляющими сигналами по шине 48 управления перепрограммируемый блок 43 памяти переводится в режим записи кодов. Код адреса первой ячейки, записанный в регистре 39, проходя через группу элементов ИЛИ 42, воздействует на адресные входы блока памяти 43, На регистрах 40 и 41 установки кодов 40 и 41 устанавливают кодовые значения начальной ординаты и углового коэффициента аппроксимирующей прямой, которые после поачи исполнительного сигнапа записи по шине 48 записываются в первую ячейку. Затем-переходят к записи информаии во вторую ячейку блока амяти, для чего увеличивают а единицу адресный код в регистре 39 установки кода адеса, после чего аналогично изложеному записывают во вторую ячейку памяти коды начальной ординаты и углового коэффициента, относящиеся к второму интервалу аппроксимации, и т.д. о тех пор, пока в блок памяти не за- пишутся коды всех коэффициентов аппроксимации.

В рабочем режиме сигналом по щи- не 48 перепрограммируемый блок 43 памяти переводится в режим считывания, а регистры 39-41 обнуляются. При работе .реверсивный счетчик 3 заполняется счетными импульсами. Старшие разряды реверсивного счетчика указывают адрес ячейки блока памяти (через группу 42 элементов ИЛИ), в то время как мпадшие разряды кода преобразуются в пропорциональное напряжение, оспроизводящее приращение Л х аргуента (Оьдх ) . После считываия из блока памяти информации по заанному адресу код начальной ордина- ты воздействует на цифровые входы реобразователя 44, а код углового коэффихщента - на цифровые входы мно- жительного преобразователя 45.Таким образом, на выходе выходного сумматора 47 воспроизводится аппроксимируюая функция:

где ная аппр вале

цион ме т

jQ зова чить

I плот с фо ции, вани

30

40

воль прео стно

Фо

вой пара

2 шино вход цифр ходн равл пуль мент выхо нера щи ния

5 лени вани режи ны к счет дачи блок фрон втор мент

45 рета упра деши ный ност

50 режи ходо с вх прям та и

55 ки, перв та с

(fj (Лх) a j + bjjx.

где aj и bj - соответственно начальная ордината и угловой коэффициент аппроксимирующей прямой на j-м интервале аппроксимации.

Таким образом, предлагаемый функциональный АЦП может работать в режиме традиционного нелинейного преобразования, в режиме, позволяющем получить код относительной опт1гческой

плотности фотоматериалов при работе с фотометрическими датчиками информации, в режиме однократного преобразования, характерного для цифровых

вольтметров и в режиме многократного преобразования, типичного дпя совместной работы с ЭВМ.

Формула изобретения

0

0

1. Функциональный аналого-цифровой преобразователь, содержащий компаратор, соединенный первым входом с

шиной входного напряжения, а вторым входом - с выходом функционального цифроаналогового преобразователя, выходной суммирующий счетчик и блок управления, содержащий генератор импульсов, первый триггер и первый элемент И, входы которого подключены к выходу первого триггера и выходу генератора импульсов, отличающийся тем, что, с целью расширения области применения за счет вычис5 ления разности нелинейных преобразований в однократном и периодическом режимах, в него дополнительно введены коммутатор импульсов, реверсивный счетчик, буферный регистр, блок передачи импульсов и триггер знака, а блок управления содержит детектор фронтов, второй и третий триггеры, второй и третий элементы И, три элемента ШШ, три элемента зап-

5 рета, два элемента задержки, управляемый делитель частоты и дешифратор сигнала сброса, соединенный входами с входом признака кратности преобразователя, входом выбора

0 режима работы преобразователя и выходом второго триггера, а выходом - с входом обнуления третьего триггер, прямым входом первого элемента запрета и входом первого элемента задерз 5 ки, подключенного выходом к первому входу первого элемента ИЛИ, соединенного выходом с входом установки в 1 дер9

гера, л вторым вховходом запуска преобра- и первым управляющим управляемого делителя

подключенного информа- входом к выходу ге

11МПУЛЬСОВ;

а вторым управляющим входом - к входу останова преобразователя и первому входу втосоединен с выходом дешифратора сиг ла сброса, при этом реверсивный сч чик подключен установочным входом выходу буферного регистра, входом управления установкой кода - к вых ду второго элемента И, входом обну ления - к выходу первого элемента запрета, а выходом - к цифровому в ду функционального цифроаналоговог

рого элемента ИЛИ, соединенного выхо- преобразователя и информационному

30

дом с входом обнуления первого триггера, а вторым входом - с выходом детектора фронтов, первым входом второго элемента И, прямыми входами второго и третьего элементов запрета и j входом второго элемента задержки, выход которого подключен к первому входу третьего элемента И, соединенного вторым входом с входом выбора режима работы преобразователя и инверсными 20 входами первого и второго элементов запрета, а выходом - с входом установки в I второго триггера, подключенного входом обнуления к выходу первого элемента запрета, а выходом - к 25 инверсному входу третьего элемента запрета и второму входу второго элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, подключенного вторым входом к выходу второго элемента за прета; а выходом - к входу установки в 1 третьего триггера р выход которого является выходом сигнала готовности преобра зова- теля, причем вход детектора фронтов соединен с выходом компаратора и информационным входом триггера знака, подключенного прямым выходом к первому управляющему входу коммутатора им- ,. пульсов, инверсным выходом - к выходу знака преобразователя, а синхронизирующим входом - к выходу первого триггера, при этом коммутатор импульсов соединен информационным входом с выходом первого элемента И, вторым управляющим входом - с выходом второго триггера и первым управляющим входом блока передачи импульсов, первым выходом - с суммирующим входом реверсивного счетчика и первым сигнальным входом блока передачи импульсов, а .вторым выходом - с вьгчитаюпснм входом .реверсивного счетчика и вторым сигнальным входом блока передачи импуль- сов, подключенного вторым управляющим входом к входу выбора режима ра- 55 .боты преобразователя, а выходом - к счетному входу выходного суммирующего счетчика, вход обнуления которого

35

40

45

50

входу буферного регистра, вход раз шения записи кода которого соедине с выходом третьего элемента запрет

2.Преобразователь по п.1, о т личающийся тем, что функ циональный цифроаналоговый преобра зователь содержит регистр установк кода адреса, первый и второй регис ры установки кода числа, перепрогр мируемый блок памяти, три цифроана логовых преобразователя, выходной сумматор и группу элементов ИЛИ, п ключенных первыми входами к выхода разрядов регистра установки кода а реса, вторыми входами - к старшим разрядам цифрового входа функциона ного цифроаналогового преобразоват ля, а выходами - к адресным входам перепрограммируемого блока памяти, соединенного первой и второй групп ми входов записи кодов с выходами первого и второго регистров устано ки кода числа соответственно, вход ми разрешения записи и чтения - с ной управления работой блока памят а первой и второй группами выходов разрядов - с цифровыми входами пер го и второго цифроаналоговых преоб зователей соответственно, выходы к торых подключены к входам выходног сумматора, причем аналоговый вход второго цифроаналогового преобразо теля соединен с выходом третьего ц роаналогового преобразователя, под ключенного цифровым входом к младш разрядам цифрового входа функциона ного цифроаналогового преобразоват ля.

3.Преобразователь по п.1, о т личающийся тем, что бло передачи импульсов содержит элемен И, элемент импликации и элемент ИЛ входы которого являются первым и в рым информационными входами блока редачи импульсов, а выход соединен

с первым входом элемента И, выход торого является выходом блока пере

1260979

10

соединен с выходом дешифратора сигнала сброса, при этом реверсивный счетчик подключен установочным входом к выходу буферного регистра, входом управления установкой кода - к выходу второго элемента И, входом обнуления - к выходу первого элемента запрета, а выходом - к цифровому входу функционального цифроаналогового

преобразователя и информационному

0

j 20 25,. 5

5

0

5

0

входу буферного регистра, вход разрешения записи кода которого соединен с выходом третьего элемента запрета.

2.Преобразователь по п.1, о т - личающийся тем, что функциональный цифроаналоговый преобразователь содержит регистр установки кода адреса, первый и второй регистры установки кода числа, перепрограммируемый блок памяти, три цифроана- логовых преобразователя, выходной сумматор и группу элементов ИЛИ, подключенных первыми входами к выходам разрядов регистра установки кода адреса, вторыми входами - к старшим разрядам цифрового входа функционального цифроаналогового преобразователя, а выходами - к адресным входам перепрограммируемого блока памяти, соединенного первой и второй группами входов записи кодов с выходами первого и второго регистров установ- ки кода числа соответственно, входами разрешения записи и чтения - с шиной управления работой блока памяти, а первой и второй группами выходов разрядов - с цифровыми входами первого и второго цифроаналоговых преобразователей соответственно, выходы которых подключены к входам выходного сумматора, причем аналоговый вход второго цифроаналогового преобразователя соединен с выходом третьего цифроаналогового преобразователя, подключенного цифровым входом к младшим разрядам цифрового входа функционального цифроаналогового преобразователя.

3.Преобразователь по п.1, о т - личающийся тем, что блок передачи импульсов содержит элемент И, элемент импликации и элемент ИЛИ, входы которого являются первым и вторым информационными входами блока передачи импульсов, а выход соединен

с первым входом элемента И, выход которого является выходом блока переда-

11 .1260979-12

чи импульсов, а второГ вход подклю- ются первым и вторым управляющим вхо- чен к выходу элемента импликации,пря- даш блока передачи импульсов соот- мой и инверсный входы которого явля- -ветственно.

12

10

Фиг.1

мг. 3

Г

e

Редактор Л.Пчелинская

Составитель С.Казинов Техред М.Ходанич

Заказ 5234/51Тираж 671Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

I

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для измерения длительности импульсных сигналов | 1985 |

|

SU1272257A1 |

| Устройство для цифрового функционального преобразования | 1981 |

|

SU985792A1 |

| Цифровой измеритель пикового значения импульсных воздействий | 1984 |

|

SU1167734A1 |

| Нелинейный преобразователь | 1988 |

|

SU1674172A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1305852A1 |

| Устройство для определения автокорреляционной функции | 1984 |

|

SU1363254A1 |

| Преобразователь частоты в код | 1988 |

|

SU1607078A1 |

| Синхронный фильтр | 1988 |

|

SU1644366A1 |

Изобретение относится к области автоматики и вычислительной техники; Функциональный аналого-цифро- вой преобразователь содержит коммутатор штульсов, реверсивный счетчик, блок передачи импульсов, функциональный цифроаналоговый преобразователь, буферный регистр, выходной сз мирую- щий счетчик, триггер знака, компаратор и блок управления, содержащий детектор фронтов, триггеры, генератор импульсов, элементы И и ИЛИ,элементы запрета, элементы задержки,управляемый делитель частоты и дешифратор сигнала сброса. Расширение области применения достигается за счет возможности работы преобразователя в режимах нелинейного преобразования аргумента, формирования разности нелинейных преобразований аргумента, а также обеспечения однократного и периодических режимов работы. 2 э.п. ф-лы. 5 ил. р (Л

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ—ЦИФРА | 0 |

|

SU388361A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аналого-цифровой функциональный преобразователь | 1976 |

|

SU567203A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Ячейка каскадной коммутирующей среды | 1975 |

|

SU598067A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гитис Э.И., Пискулов Е.А | |||

| Аналого-цифровые преобразователи | |||

| - М.: Энергоиздат, 1981, с.255-257, рис.6.14. | |||

Авторы

Даты

1986-09-30—Публикация

1985-04-24—Подача