щий генератор 1, формирователь 2 эта

лонного ,интервала, блок 3 управлени измерительные каналы 4-Т,..-. ,4-п, шину 5 данных, блок 5 вычислений, запоминающее устройство 7, шину 8 выбора измерительного канала, распределител 9.

Выход задающего генератора 1 соединен с входом формирователя 2 и первыми входами измерительных каналов 4-i и бло.ка 3 управления. Выход фор- {мирователя 2 соединен с вторыми вход I ми бло.ка 3 управления и измеритель- ;НЫх каналов 4-i, Первый выход блока управления соединен с первым входом блока 6 вычислений, выход которого соединен с первым входом распределителя 9. Второй выход блока 3 управления соединен с. первымвходом запоминающего устройства 7 и с вторым входом распределителя 9, выход которого через шину 8 соединен с третьи ми входами измерительных каналов и вторым входом запоминающего, устрой ства 7. ВЬгходы измерительных каналов 4-1 и выход запоминающего устройства через шину 5 данных соединены с вторым входом блока 6 вычислений. Частоные датчики соединяются с третьими входами измерител: ных каналов 4-i.

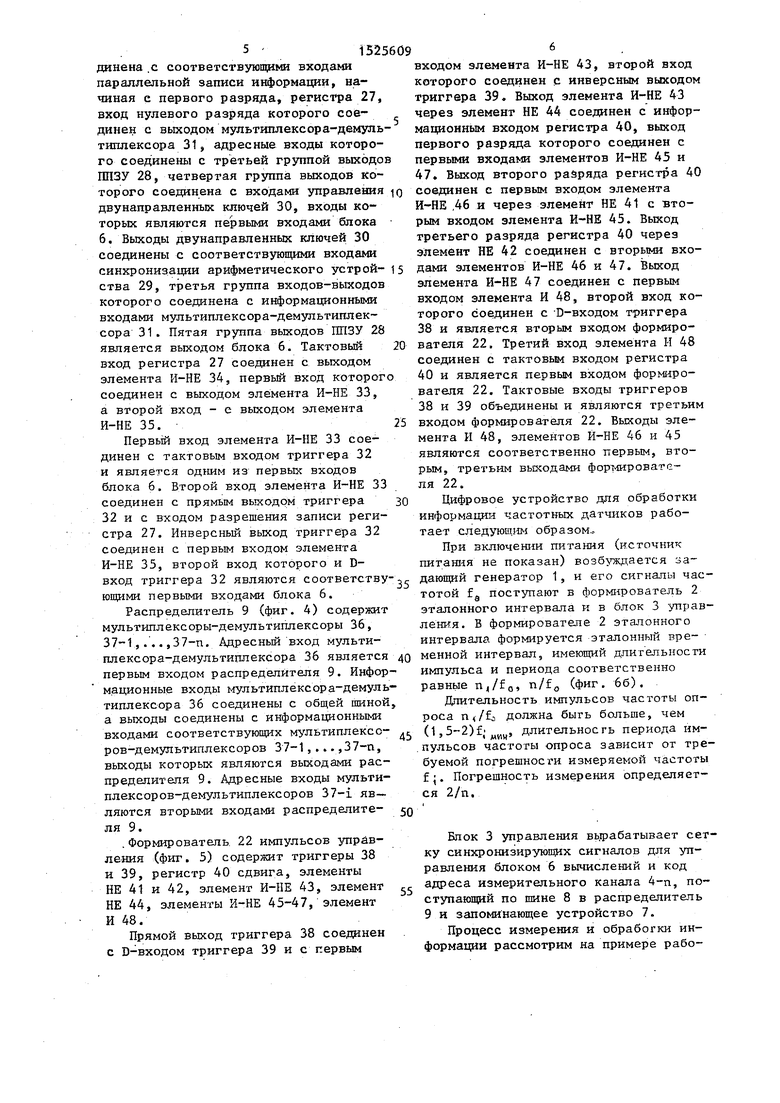

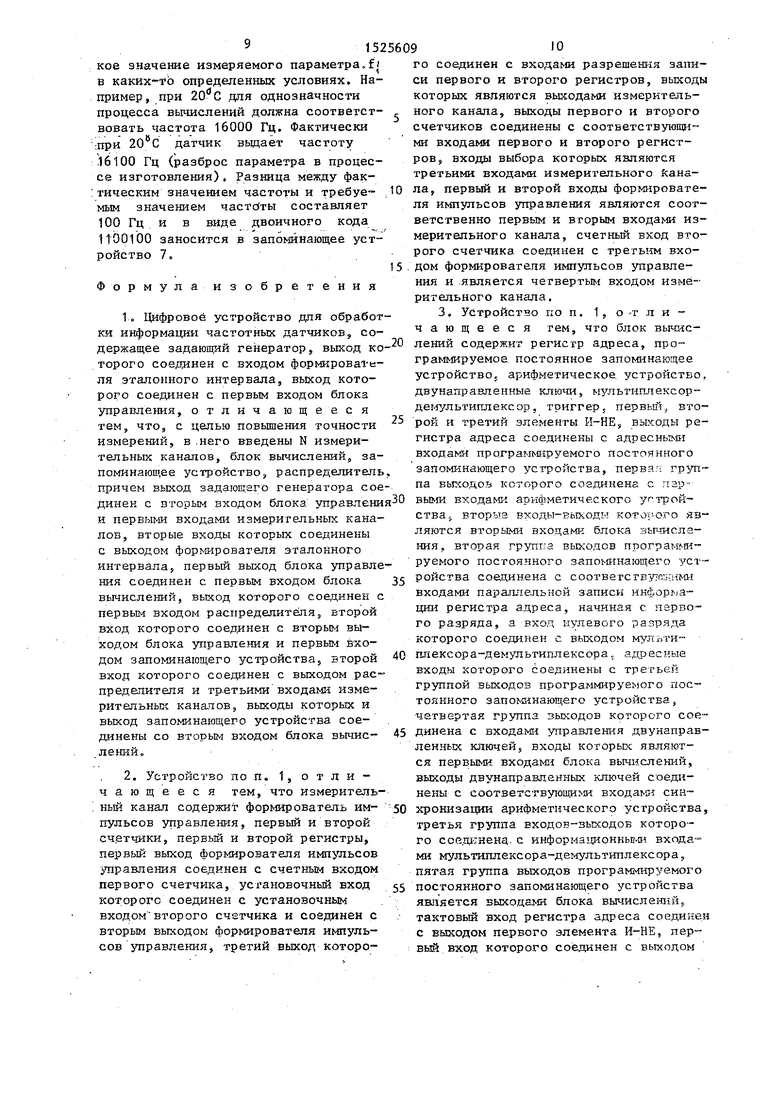

Бпок 3 управления (фиг. 2) содержит счетчик 10, элемент НЕ 11, счетчик 12 адреса, регистр 13 сдвига, элемент НЕ 14, регистр 13 сдвига, элемент ИЛИ 16, элементы НЕ 17-20, Выход первого разряда счетчика 10 является одним ив первых выходов блока 3. Выход последнего разряда счетчика 10 соединен с тактовым входом регистра 13 и через элемент НЕ 1,4, с

о ° счетчика 12.

5

5

Q

0

5

0

5

Измерительный канал 4-i (фиг. 1) содержит вход 21 формирователя 22 импульсов управления, счетчики 23 н. 24, регистры 25 и 26.

Первый выход формирователя 22 со.е- динен со .счетным входом счетчика 24, установочный вход которого соединен с установочным входом счетчика 23 и соединен с вторым выходом формирователя 22. Третий выход формирователя 22 соединен, с входами разрешения записи регистров 25 и 26, выходы которых являются выходами измерительного канала 4-i. Выходы счетчиков 23 и 24 соединены с входами соответственно регистров 25 и 26, входы выбора микросхем которых являются третьими входами измерительного канала 4-i.

Первый, второй входы формирователя 22 являются соответственно первым, вторым входами измерительного канала 4-i. Счетный вход счетчика 23 соединен с третьим входом формирователя 22 и является четвертым входом измерительного канала.

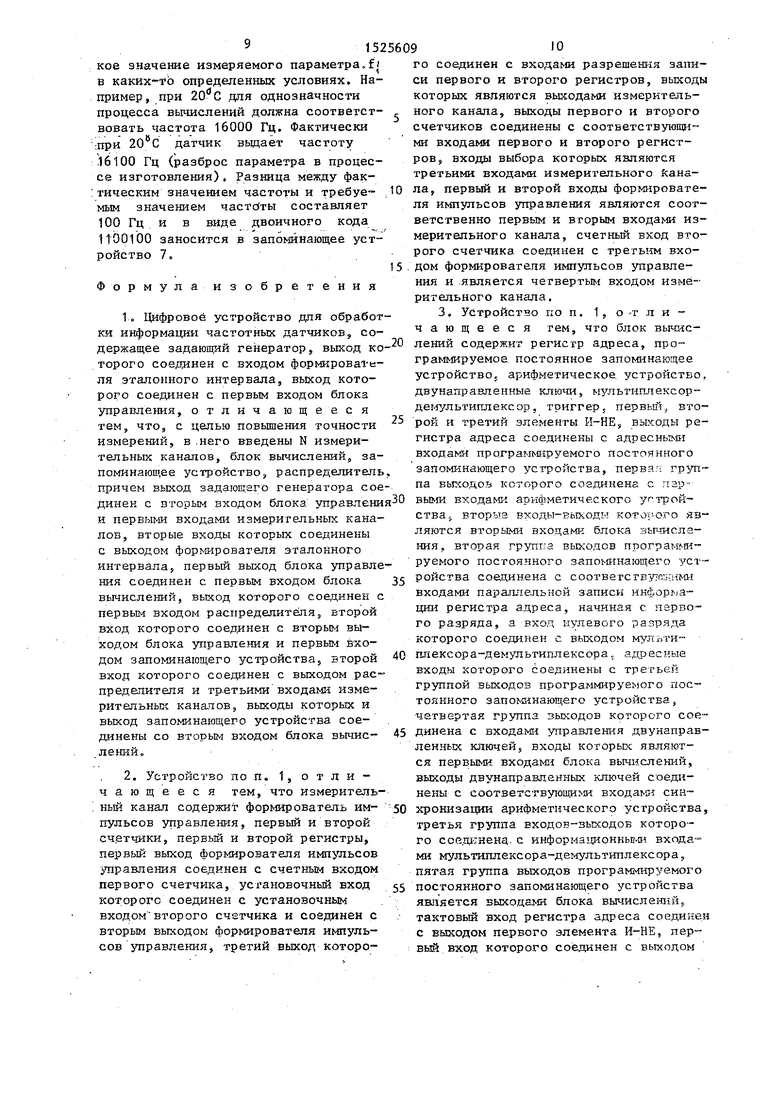

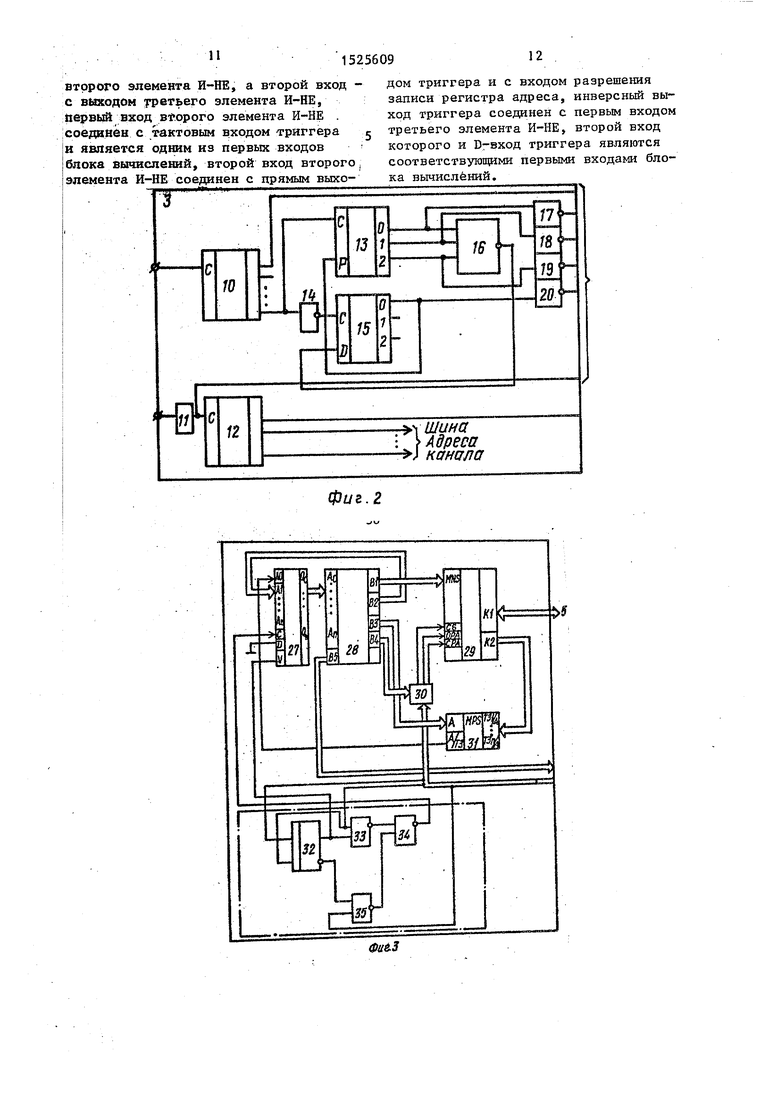

Блок 6 вычислений (фиг. 3) содержит регистр 27 адреса, программируемое постоянное запоминающее устройство (ППЗУ) 28, арифметическое устройство 29, двунаправленные ключи 30, мультиплексор-демультиплексор 31, триггер 32, элементы И-НЕ 33-35.

- ВЫХ.ОДЫ регистра 27 соединены с адресными входами ППЗУ 28, первая группа выходов которого соединена с первыми входами арифметического устройства 29, вторые входы-выходы которого являются вторыми входами блока 6, Вторая группа выходов ППЗУ 28 сое

5 -1525

динена .с соответствзпощими входами параллельной записи информации, начиная е первого разряда, регистра 27, вход нулевого разряда которого соединен с выходом мультиплексора-демуль- типлексора 31, адресные входы которого соединены с третьей группой выходов ППЗУ 28, четвертая группа выходов которого соединена с входами управления двунаправленных ключей 30, входы которых являются первыми входами блока 6. Выходы двунаправленных ключей 30 соединены с соответствующими входами синхронизации арифметического устрой- ства 29, третья группа входов-выходов которого соединена с информационными входами мультиплексора-демультиплек- сора 31. Пятая группа выходов ППЗУ 28 является вькодом блока 6. Тактовый вход регистра 27 соединен с выходом элемента И-НЕ 34, первый вход которого соединен с выходом элемента И-НЕ 33, а второй вход - е выходом элемента И-НЕ 35.

Первьй вход элемента И-НЕ 33 соединен с тактовым входом триггера 32 и является одним из первых входов блока 6. Второй вход элемента И-НЕ 33 соединен с прямьм вьзходо м триггера 32 и с входом разрешения записи регистра 27. Инверсный выход триггера 32 соединен с первым входом элемента И-НЕ 35, второй вход которого и D- вкод триггера 32 являются соответствующими первыми входами блока 6.

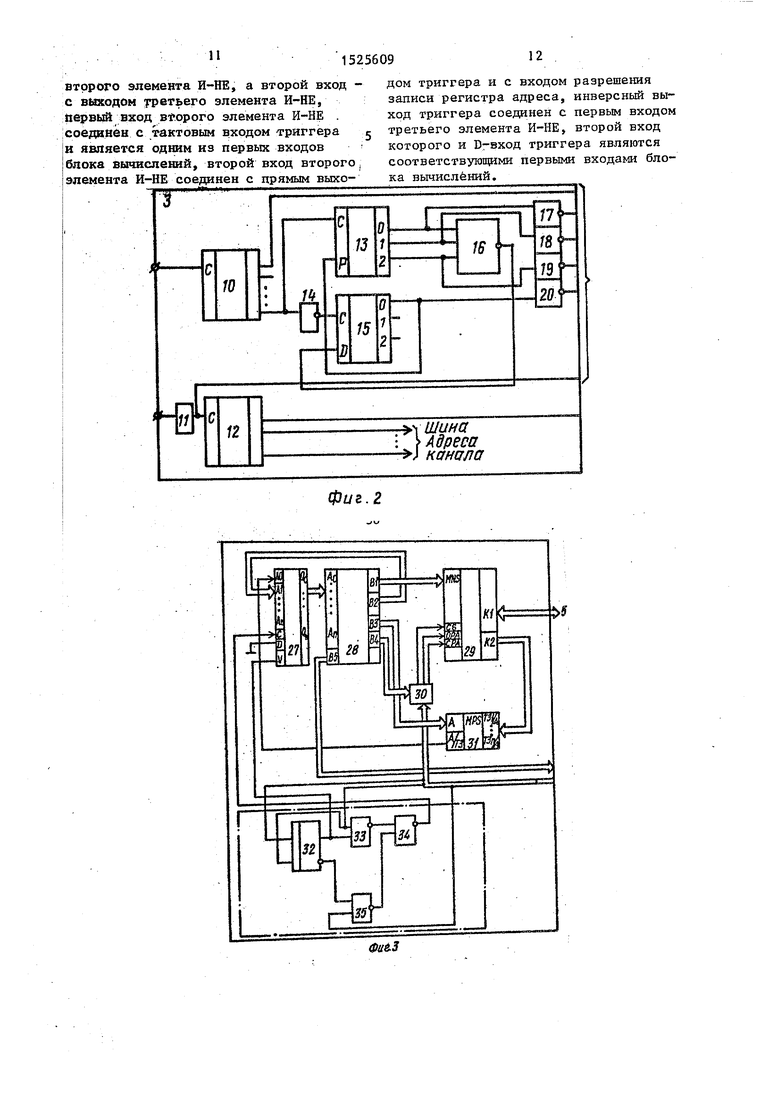

Распределитель 9 (фиг. 4) содержит мультиплексоры-демультиплексоры 36, 37-1,...,37-п. Адресный вход мульти- плексора-демультиплексора 36 является первым входом распределителя 9. Информационные входы мультиплексора-демуль- типлексора 36 соединены с общей шиной а выходы соединены с информационными входами соответствующих мультиплексо- ров-демультиплексоров 37-1,...,37-п, выходы которых являются выходами распределителя 9. Адресные входы мульти- плексоров-демультиплексоров 37-i являются вторыми входами распределите- ля 9.

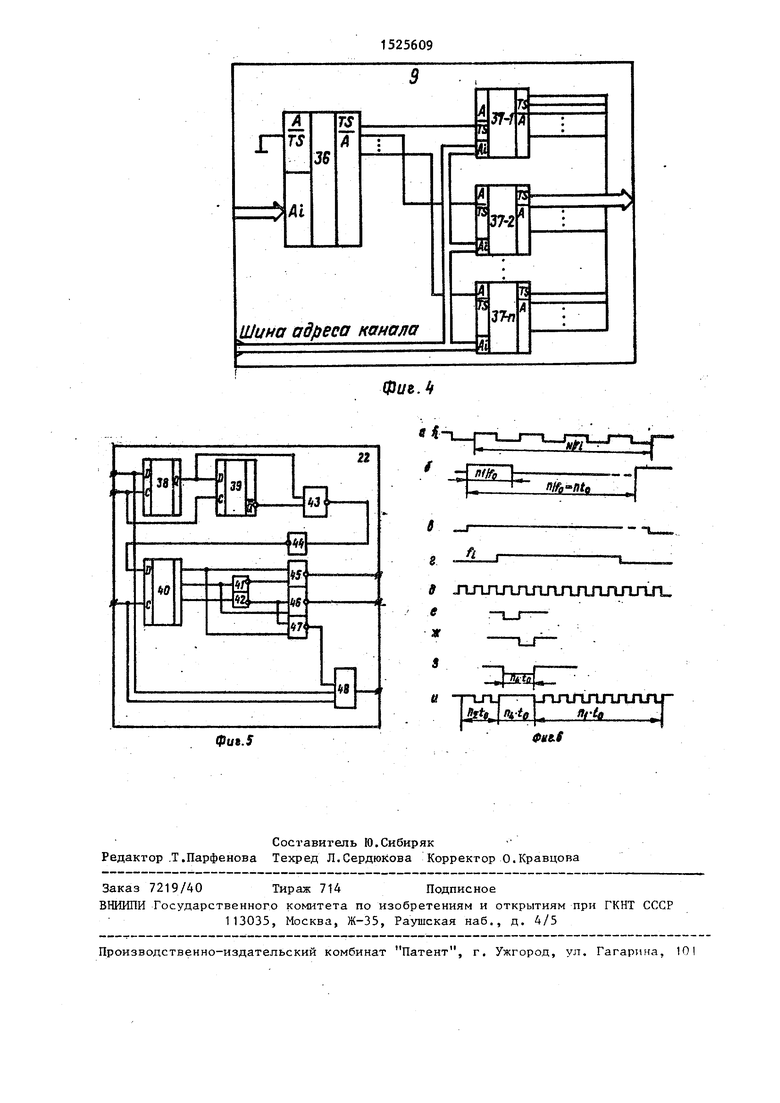

. Формирователь 22 импульсов управления (фиг. 5) содержит триггеры 38 и 39, регистр 40 сдвига, элементы НЕ 41 и 42, элемент И-НЕ 43, элемент НЕ 44, элементы И-НЕ 45-47, элемент И 48.

Прямой выход триггера 38 соеданен с D-входом триггера 39 и с первым

Q 5 0 5

О -

0 O

входом элемента И-НЕ 43, второй вход которого соединен с инверсным выходом триггера 39, Выход элемента И-НЕ 43 через элемент НЕ 44 соединен с информационным входом регистра 40, выход первого разряда которого соединен с первыми входами элементов И-НЕ 43 и 47. Выход второго разряда регистра 40 соединен с первым входом элемента И-НЕ ,46 и через элемент НЕ 41 с вторым входом элемента И-НЕ 45. Вькод третьего разряда регистра 40 через элемент НЕ 42 соединен с вторьми входами элементов И-НЕ 46 и 47. Выход элемента И-НЕ 47 соединен с первым входом элемента И 48, второй вход которого соединен с -В-входом триггера 38 и является вторым входом формирователя 22. Третий вход элемента И 48 соединен с тактовым входом регистра 40 и является первым входом формирователя 22. Тактовые входы триггеров 38 и 39 объединены и являются третьим входом формирователя 22. Выходы элемента И 48, элементов Й-НЕ 46 и 45 являются соответственно первым, вторым, третьим выходами фор -птровате- ля 22.

Цифровое устройство для обработки информации частотных датчиков работает следующим образом,При включении питания (источник питания не показан) возбуждается за- даюпщй генератор 1, и его сигналы частотой fg поступают в форми:рователь 2 эталонного интервала и в блок 3 управления. В формирователе 2 эталонного интервала формируется эталонный временной интервал, имеющий длительности импульса и периода соответственно равные Пд/fo, n/f (фиг. 6б).

Длительность импульсов частоты опроса nv/fj должна быгь больше, чем (1,5-2)f,, длительность периода импульсов частоты опроса зависит от требуемой погрешности измеряемой частоты f;. Погрешность измерения определяется 2/п.

Блок 3 управления вь,1рабатывает сетку синхронизирующих сигналов для управления блоком 6 вычислений и код адреса измерительного канала 4-п, по- ступакящй по шине 8 в распределитель 9 и запоминающее устройство 7.

Процесс измерения и обработки информации рассмотрим на примере работы одного из измерительных кйналов 4-п.

Во время действия импульса эталон кого временного интервапа5 поступающего в блок 3 управления, на нервьш вход блока б вычислений осуществля€:г ся за дание нулевого (начального) адреса (фиг. 3) и измерение приращения частоты fJ частотного датчика.

Измерение частоты датчика осуществляется следующим образом.

По фронту импульсов эталонного сигнала из измеряемого сигнала формируется одиночный импульс (фиг. 6 б; в, г), В свою очередь, по фронту измеряемого сигнала эталонных импульсов формируется сигнал записи информащШа сигнал установки, сигнал- блокировки (фиг. 6 е, ж, и).

По сигналу записи (третий выход формирователя 22) содержимое счетчиков 23 и 24 переписьшается соответственно в регистры 25 и 26; При этом в 25 регистр 25 записывается число импульсов измеряемой частоты f на ,интерва-.; ле n/f (,, а в регистр 26 число импуль- сов п + Пз - ., где п - число им пульсов частоты (, между фронтом изме-зо ряемой частоты и спадом импульсов эталонного интервала,- п - количество им- пульсов эталонной частоты f, во время которых происходит формирование

15256098

писи информации, прокожде ше сигналов

0

5

0

5 ; о

задающего генератора через элекент И-НЕ 35 запрещается; а через элемент 33 разрешается, прохождегше синхронизирующего сигнала смекы адреса в регистре 27. Начинается вьшолнение микропрограммы.

За время цикла измерений блок б вы-- числений последовательно обрабатывает информацию канодого измерительного канала 4-п. Алгори7 мы работы для каждо го канала одинаковые Цикл измерений подразделяется на одинаковые временные интервалы. Пауза интервала используется для нулевого адреса С приходом импульсного интервала начинается обработка информации. По нуплевому адресу на имке В1 ПИЗУ 28 устанавливается .микрокоманда начальной установки, на шине В2 - следующий адресэ на иине ВЗ - сигналы, разрешающие прохождение сигналов синхронизации на входы CSj ОРА, IPA арифметического устройства 295 осуществляется на чальная установка арифметического уст ройства 29. По окончанию синхросигнала IPA в регистр 27 записывается 0+1 адрес о Начинается вьшолнение следующей микрокоманды, например считывание информации из выходных регистров измерительных каналов 4-п.

Адрес считьтаемого регистра задается через распределитель 9 р:меющий

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения скорости перемещения | 1989 |

|

SU1732281A1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Устройство пункта управления системы телемеханики | 1986 |

|

SU1374265A1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И ЭКСПЕРТНАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2078324C1 |

| Устройство сбора дефектоскопической информации | 1985 |

|

SU1298719A1 |

| Устройство для измерения скорости движения | 1987 |

|

SU1476390A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168870C1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

Изобретение может быть использовано в информационно-измерительной технике. Цель изобретения - повышение точности измерений, что достигается введением запоминающего устройства 7, в которое заносятся калибровочные коды, учитывающие начальный разброс частот датчиков. Измерение частот датчиков осуществляется непрерывно измерительными каналами 4-N, данные из которых поступают в блок 6 вычислений, в котором вычисляются истинные значения частот датчиков с учетом начальных условий и нестабильности задающего генератора 1. Устройство также содержит формирователь 2 эталонных интервалов, блок 3 управления, шину 5 данных, шину 8 выбора измерительного канала, распределитель 9. 2 з.п. ф-лы, 6 ил.

импульсов записи и установки, п, - ко-, две координаты код адреса нзмефитель

личество импульсов эталонной частоты f между фронтом опорного интервала и фронтом измеряемого сигнала fj.

Далее осзпцествляется процесс обра- ;ботки. Во время импульса эталонного Q интервала происходит установка нулевого адреса в- блоке 6 вычислений.

Импульс временного интервала уточ- няется по фазе при помощи синхронного D-триггера 32 (фиг. 3) nto отношению к

фронту одного из синхронизирующих СИГ

налов, поступивших с первого входа блока/6. На вход регистра 27 поступает сигнал последовательной записи ий- формации, одновременно через элемент И-НЕ 35 разрешается прохождение сигнала задающего генератора на вход синхронизации регистра 27, где г

ного канала, код адреса регистра в измерительном канале. 3 результате оп роса регистров в арифметическое уст- ройство 29 заносятся значенз я N; (); ± ufp (), далее через пшну микрокоманд В1 заносятся постоянные значения- частот f

чисел (пп, + п)

о О , осуществляется вычт-хсг е ще

приращения частот f ,

NU

Д f : - .

- () + (п-1.,)+п

-си

где NJ - количество периодов измеряемого сигнала f, относительно эталонного интервала rt/f,., § начальная частота частотного датчика

FO;

Учет начальньЕ условий fl.f,-,;

через m - количество периодов частоты каждому измеряемому параметру осущеf д/ш на всех выходах записывается ствляется при. помощ запоминающего левая микрокоманда. По окончанию им-устройства 7. В результате первонапульса эталонного интервала регистрчальной настройки набирается двоичный

27 переходит в режим параллельной за- код числа, характеризующий фактичесного канала, код адреса регистра в измерительном канале. 3 результате опроса регистров в арифметическое уст- ройство 29 заносятся значенз я N; (); ± ufp (), далее через пшну микрокоманд В1 заносятся постоянные значения- частот f

п, + п)

о О , осуществляется вы

приращения частот f ,

NU

Д f : - .

- () + (п-1.,)+п

количество периодов измеряемого сигнала f, относительно эталонного интервала rt/f,., § начальная частота частотного датчика

Учет начальньЕ условий fl.f,-,;

кое значение измеряемого параметра,fi в каких-то определенных условиях. Например, при доя однозначности процесса вычислений должна соответствовать частота 16000 Гц. Фактически при датчик вьщает частоту 16100 Гц (разброс параметра в процессе изготовления). Разница между фак- :тическим значением частоты и требуе мым значением частоты составляет 100 Гц и в виде двоичного кода 1100100 заносится в запоминающее устройство 7 о

Формулаизобретения

1 Цифровое устройство дпя обработки информации частотных датчиков, со

держащее задающий генератор, выход ко торого соединен с входом формироваги- ля эталонного интервала, выход которого соединен с первым входом блока управления, отличающее с я

измерений, в .него введены N измерительных каналов, блок вычислений, запоминающее устройство, распределитель, причем выход задающего генератора соединен с вторым входом блока управления и первыми входами измерительных кана25

с выходом формирователя эталонного интервала, первый выход блока управления соединен с первым входом блока вычислений, выход которого соединен с первым входом распределителя, второй вход которого с вторым выходом блока управления и первым входом запоминающего устройства, второй вход которого соединен с выходом .рас пределителя и тр.етьими входами измерительных каналов, выходы которых и выход запоминающего устройства соединены со вторым входом блока вычислений.

1

го соединен с входами разрешен ьч записи первого и второго регистров, выходы которых являются выходами измеритеяь- , ного канала, выходы первого и второго счетчиков соединены с соответствующ -- ми входами первого и второго регистров, входы выбора которых являются третьими входами измерительного {сана10 ла, первый и второй входы формирователя импульсов управления являются соответственно первым и вторым входами измерительного канала, счетный вход второго счетчика соединен с третьим вхо15 дом формирователя импульсов управления и является четвертым входом измерительного канала.

3, Устройство по п. 1, о -т л и - чающееся тем, что блок вычис- 20 лений содержит регистр адреса, программируемое, постоянное запоминающее устройство, арифметическое, устройство, двунаправленные ключи, мультиплексор- деГ Г/льтигшексор, триггер, первьш, вто25 рой и третий элементы И-НЕ, выходы регистра адреса соединены с адреснь&и входами программируемого постоянного запоминающего устройства, первал группа выходов которого соединена с пзр- выми входам - арифметического устройства,; вторые входы-выходы котог-ого являются BTopbD-ffl входами блока .ле

руемого постоянного запоьшнающего устройства соединена с соответсгвутолгнмн входами параллельной записи ннфор)а- ции регистра адреса, начиная с лерво го разряда, а вход иулевого разряда которого соединен с выходом муяьти- гшексора-демультиплексора, адресные входы которого соединены с третьей группой выходов программируемого постоянного за.пом5 нающего устройства, четвертая группа зькодов которого соединена с входами управления двунаправленных ключей, входы которых являются первыми вxoдaмzi блока вычислений, выходы двунаправленных ключей соединены с соответствующими вxoдa s : син™

хронизации арифметического устройства, третья группа входов-выходов которого сое,Щ :нена. с информационныг-п входами мультиплексора-демультиплексора, пятая группа выходов программируемого

постоянного запоминающего устройства является выходами блока вычисленнй;. тактовый вход регистра адреса соединен с выходом первого элемента И-НЕ, первый вход которого соединен с выходом

второго элемента И-НЕ, а второй вход - с BtiQcoflOM третьего элемента И-НЕ, первый вход Bfoporo элемента И-НЕ . соеднйбв с тактовым входом триггера и является одним из первых входов блока вычислений, второй вход второго элемента И-НЕ соединен с прямым выхоJ

ю

lit

} -4

12

Фиг. г

дом триггера и с входом разрешения записи регистра адреса, инверсный выход триггера соединен с первым входом третьего элемента И-НЕ, второй вход которого и БГВХОД триггера являются соответствующими первыми входами блока вычислений.

13

16

IS

9

20

il/UW

: Адреса

J канала

Фи.5

ФиъЛ

Фие-б

Авторы

Даты

1989-11-30—Публикация

1987-10-02—Подача