Изобретение относится к области управления и регулирования, может быть использовано в системах числового программного управления исполнительными органами станков и является усовершенствованием известного устройства, описанного в а.с. СССР №. 1522155

Известно многокоординатное устройство для управления, содержащее импульсные датчики перемещений, блок данных, регистр номера ксординаты, коммутатор аналогового напряжения, цифроанапого- вый преобразователь, блок синхронизации, формирователь адреса, интерфейсный

го

блок, блок связи с импульсными датчиками перемещений, первый и второй блоки вычисления перемещений, блок оперативного управления, выходные усилители.

В известном устройстве отсутствует возможность работы многокоординатного устройства от фазовых датчиков.

Целью изобретения является расширение функциональных возможностей устройства путем обеспечения работы от фазовых датчиков.

Поставленная цель достигается тем, что в устройство введены фазовые датчики 14 перемещений и блок 15 связи с фазовыми датчиками перемещений, тактирующим входом подключенный к третьему выходу блока 1 синхронизации, входом начальной установки соединенный с выходом сброса блока 9 данных, а информационными входами соединенный с выходами соответствующих фазовых 14 датчиков перемещений, входы опорных сигналов блока 15 связи с фазовыми датчиками перемещений, адресные входы которого соединены поразрядно с выходами формирователя 2 адреса, информационные выходы блока 15 связи с фазовыми датчиками поразрядно соединены с информационными входами первого блока 5 вычисления перемещений, который входом управления соединен с выходом управлений интерфейсного блока 7.

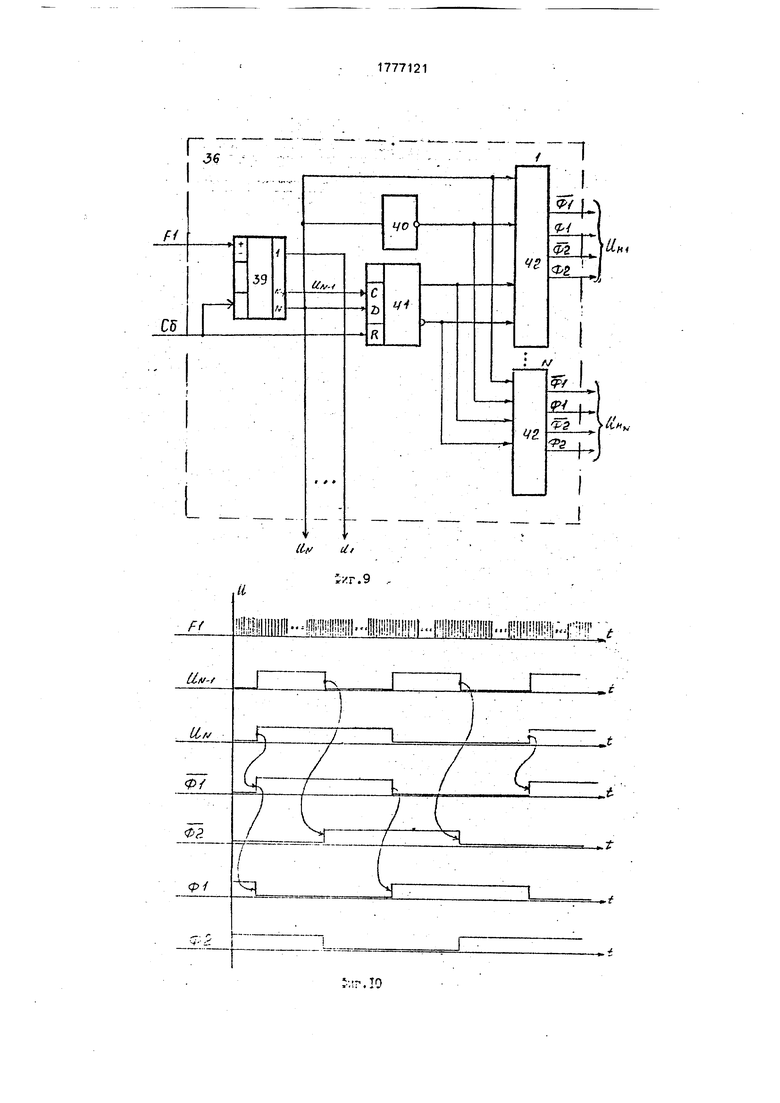

Блок 15 связи с фазовыми датчиками содержит формирователь 37 выходных сигналов фазовых датчиков, дешифратор 38 адреса и формирователь 36 опорных сигналов, содержащий опорный двоичный счетчик 39, элемент НЕ 40, D-триггер 41 и выходные усилители 42, опорный двоичный счетчик 39 формирователя опорных сигналов 36 счетным входом соединен с тактирующим входом формирователя 36 опорных сигналов, входом начальной установки формирователя опорных сигналов 36, а выходами - со вторыми выходами формирователя опорных сигналов, элемент НЕ 40 формирователя опорных сигналов 36 входом соединен с выходом старшего N-ro разряда опорного двоичного счетчика 39, D-триггер 41 формирователя опорных сигналов 36 С-входом подключен к выходу N-1 разряда опорного двоичного счегчика 39 формирователя опорных сигналов 36: D-входом к выходу старшего N-ro разряда опорного двоичного счетчика 39 формирователя опорных сигналов 36, R-входом начальной установки соединен с входом начальной установки формирователя опорных сигналов 36, выходные усилители 42 формирователя опорных СИГНЗЛОР 36, по количеству фазовых датчиков перемещений 14. первыми информационными входами соединены с выходом старшего N-ro разряда опорного двоичного счетчика 39 формирователя опорных сигналов 36, вторыми информационными входами соединены с выходом элемента НЕ 40 формирователя опорных сигналов 36, третьими информационными входами соединены с прямым выходом D-триггера 41 формирователя опорных сигналов 36, третьими ин0 формационными входами соединены с прямым выходом D-триггера 41 формирователя опорных сигналов 36, четвертыми информационными входами - с инверсным выходом D-триггера 41 формирователя

5 опорных сигналов 36, а выходы являются первыми выходами опорных сигналов формирователя 36 опорных сигналов, формиро- ватель выходных сигналов фазовых датчиков 37 содержит фильтры сигнала фа0 зового датчика 43, компараторы 44, буферный регистр 45. регистры данных 46, и преобразователь кодов 47, каждый информационный вход сигналов датчиков формирователя выходных сигналов фазовых

5 датчиков через последовательно соединенные фильтр 43 сигнала фазового датчика и компаратор 44 подключен к соответствующему информационному входу буферного регистра 45 формирователя выходных сиг0 налов фазовых датчиков 37, вход записи бу- ферного регистра 45 соединен с тактирующим входом формирователя выходных сигналов фазовых датчиков 37, каждый регистр данных 46 формирователя

5 выходных сигналов фазовых датчиков 37 информационными входами подключен пораз- рядно ко входам опорных сигналов формирователя выходных сигналов фазовых датчиков, входами записи каждый ре0 гистр данных 46 соединен с соответствующим информационным выходом буферного регистра 45 формирователя выходных сигналов фазовых датчиков 37. а входами выборки выходов каждый регистр

5 данных 46 подключен к соответствующему входу выборки каналов фазовых датчиков формирователя 37 выходных сигналов фазовых датчиков и к соответствующим входам старших разрядов преобразователя кодов

0 47 формирователя 37 выходных сигналов фазовых датчиков, входы младших разрядов которого соединены поразрядно с информационными выходами регистров данных 46 формирователя выходных сигналов фазо5 вых датчиков 37, информационными выходами преобразователь кодов 47 подключен к информационным выходам формирователя выходных сигналов фазовых датчиков 37, при этом формирователь опорных сигналов 36 тактирующим входом подключен к тактирующим входам блока связи 15 с фазовыми датчиками перемещений и формирователя 37 выходных сигналов фазовых датчиков, входом начальной установки соединен с входом начальной установки блока 15 связи с фазовыми датчиками перемещений, первыми выходами опорных сигналов - с выходами опорных сигналов блока 15 связи с фазовыми датчиками перемещений, формирователь 37 выходных сигналов фазовых датчиков информационными входами сигналов датчиков соединен с информационными входами блока 15, входами опорных сигналов поразрядно соединен со вторыми выходами опорных сигналов формирователя опорных сигналов 36, а информационными выходами поразрядно соединен с информационными выходами блока 15 связи с фазовыми датчиками перемещений, дешифратор адреса 38 входами адреса соединен поразрядно с адресными входами блока связи 15, а информационными выходами соединен с входами выборки каналов фазовых датчиков формирователя 37 выходных сигналов фазовых датчиков.

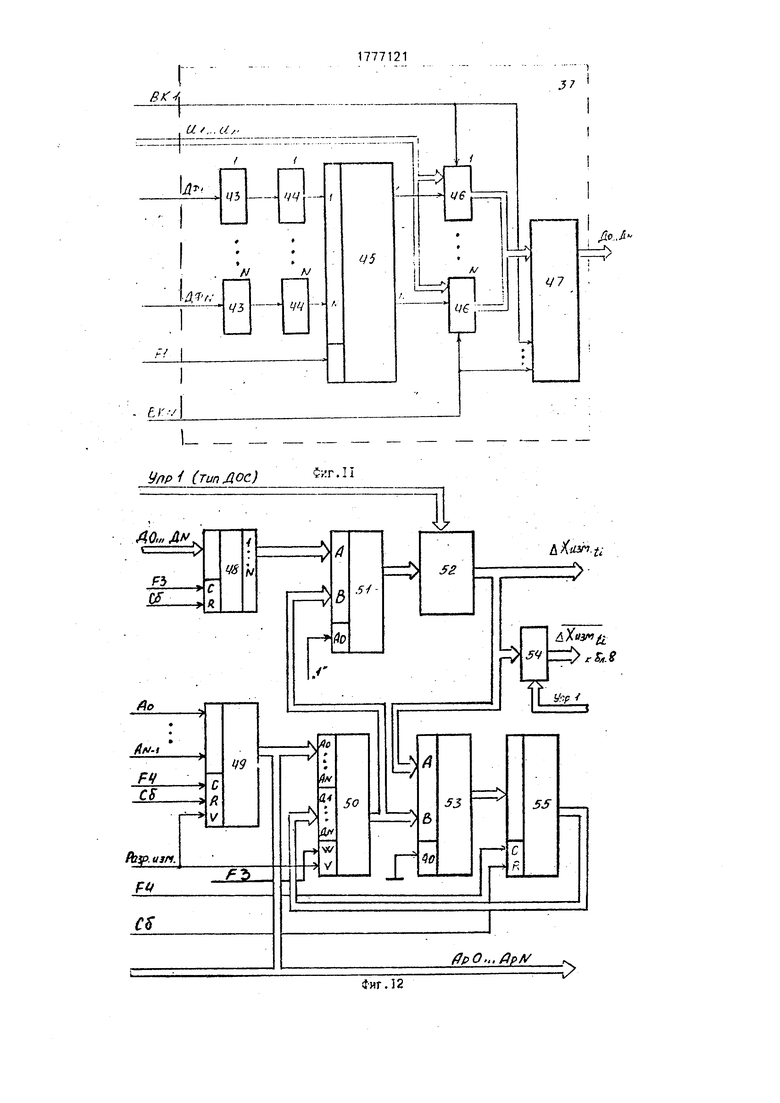

Первый блок вычисления перемещений 5 содержит регистр данных 48. регистр адреса 49, вычитаюший элемент 51, сумматор 53, преобразователь кодов 52, элемент оперативной памяти 50. буферный регистр 55 и элемент И-НЕ 54, регистр данных 48 информационными входами подключен соответственно к четвертому и пятому входам первого блока вычисления перемещений 5, С-входом - к первому входу первого блока вычислений перемещений 5. а группа выходов соединена с первой группой входов оы- читающего элемента 51, регистр адреса 49 группой информационных входов соединен с группой входов адреса первого блока вычисления перемещений, С-входом соединен с вторым входом первого блока вычислений 5 и С-входом буферного регистра, вход сброса которого соединен с входами сброса регистра данных 48, первого блока вычислителя перемещений 5 и регистра адреса 49, группа выходов которого подключена к группе адресных входов элемента оперативной памяти 50 и к группе адресных выходов первого блока вычисления перемещений, третий вход которого подключен к входу выборки выходов регистра адреса 49 и элемента оперативной памяти 50, группа выходов которого подключена к второй группе входов вычитающего элемента, вход переноса вычитающего элемента 51 соединен с шиной высокого логического уровня, преобразователь кодов 52 информационными входами поразрядно подключен к информационным выходам

вычитающего элемента 51 старшими разрядами адреса подключен к младшим разрядам входа управления первого блока вычисления перемещений, а входами - к первым информационным выходам первого блока 5 вычисления перемещений, к первой группе входов сумматора 53, к информационным входам элемента И-НЕ 54, выходы которого подключены ко вторым информа0 ционным выходам первого блока вычисления перемещений, а входы разрешения элемента И-НЕ 54 соединены со старшими разрядами входа управления первого блока вычисления перемещений 5, вторая группа

5 входов сумматора 53 подключена к группе информационных выходов элемента оперативной памяти 50, вход переноса - к шине низкого логического уровня, а выходы - к информационным входам буферного реги0 стра 55, выходы которого поразрядно соединены с информационными входами эле мента оперативной памяти 50, входом записи подключенного к первому входу первого блока вычисления перемещений,

5Интерфейсный блок 7 содержит приемник данных 62, два регистра 63, 64, дешифратор адреса 66, D-триггер 67, четыре элемента И 68, 69, 70, 73 элемент ИЛИ 71, блок формирования ответных сигналов 72,

0 элемент оперативной памяти 74 и сепектор адреса 65, информационные выходы которого соединены со входами первого регистра 64, выходы которого подключены к информационным входам дешифратора ад5 реса 66, соединенного выходом с первым входом первого элемента И 68, второй вход которого соединен с первым выходом блока формирования ответных сигналов 62 и с выходом оперативного управления интерфей0 сного блока 7, выход - D-входом D-триггера 67, вход которого соединен с первым информационным входом интерфейсного блока 7 и с первым входом блока формирования ответных сигналов 72 интерфейсного блока 7,

5 разрешающий выход которого соединен с инверсным выходом D-триггера 67, информационные входы второго регистра 63 соединены с первыми информационными выходами приемника 62 данных и с первы0 ми информационными входами селектора адреса 65, вторые информационные входы которого подключены ко вторым информационным выходам приемника данных 62, первая группа входов которого соединена с

5 информационными входами данных адреса интерфейсного блока 7, вход сброса которо го подключен к R-входу первого и второго регистров 64, 63, вход выборки выходов которого - со вторым входом блока формирования 72, третий вход которого подключен к

выходу элемента ИЛИ 71, первый вход которого подключен к первому оходу второго 70 элемента Пик первому разрешающему входу интерфейсного блока 7, второй разрешающий вход которого подключен к второму входу элемента ИЛИ 71, и к первой группе входов разрешения дешифратора адреса 66, второй вход которого соединен с выходом третьего элемента И 69 и с четвертым входом блока формирования ответных сиг- налов 72, пятый вход которого подключен к прямому выходу D-триггера G7 и к первому разрешающему выходу интерфейсного блока 7, к входу переноса второго регистра 63 выходы которого соединены с адресными выходами интерфейсного блока 7 и с адресными входами элемента оперативной памяти 74, вход записи/считывания которого соединен с выходом четвертого элемента И 73, первый информационный вход - с выхо- дом второго элемента И 70, второй и последующие входы поразрядно соединены с информационными выходами первого регистра 67, входы данных элемента оперативной памяти 74 поразрядно соединены со входами данных интерфейсного блока 7, выходы младших разрядов элемента оперативной памяти 74 соединены с младшими разрядами выхода управления интерфейсного блока 7, а выход старшего разряда - со старшим разрядов выхода управления интерфейсного блока, выход старшего разряда первого регистра 64 соединен со вторым входом второго элемента И 70, с первым входом третьего элемента И 69, второй вход которого соединен с С-входом первого 64 и второго 63 регистра и с входом синхронизации интерфейсного блока 7, выход второго элемента И 70 подключен к выходу координаты Y интерфейсного блока 7, второй вы- ход блока формирования ответных сигналов 72 подключен к второму разрешающему выходу интерфейсного блока 7, третий разрешающий выход которого соединен с третьим выходом блока формирования от- ветных сигналов 72, четвертый выход которого соединен с выходом ответных синхросигналов интерфейсного блока 7, а третий выход блока формирования ответных сигналов 72 соединен с входом управ- ленил приемника данных 7.

В результате анализа известных аналогичных решений установлено, что указанные отличительные признаки в аналогах отсутствуют, а их наличие в устройстве в совокупности обеспечивает достижение нового технического свойства, выражающегося в возможности работы устройства как с фазовыми, так и импульсными датчиками

перемещений благодаря параметрическому программированию каналов управления.

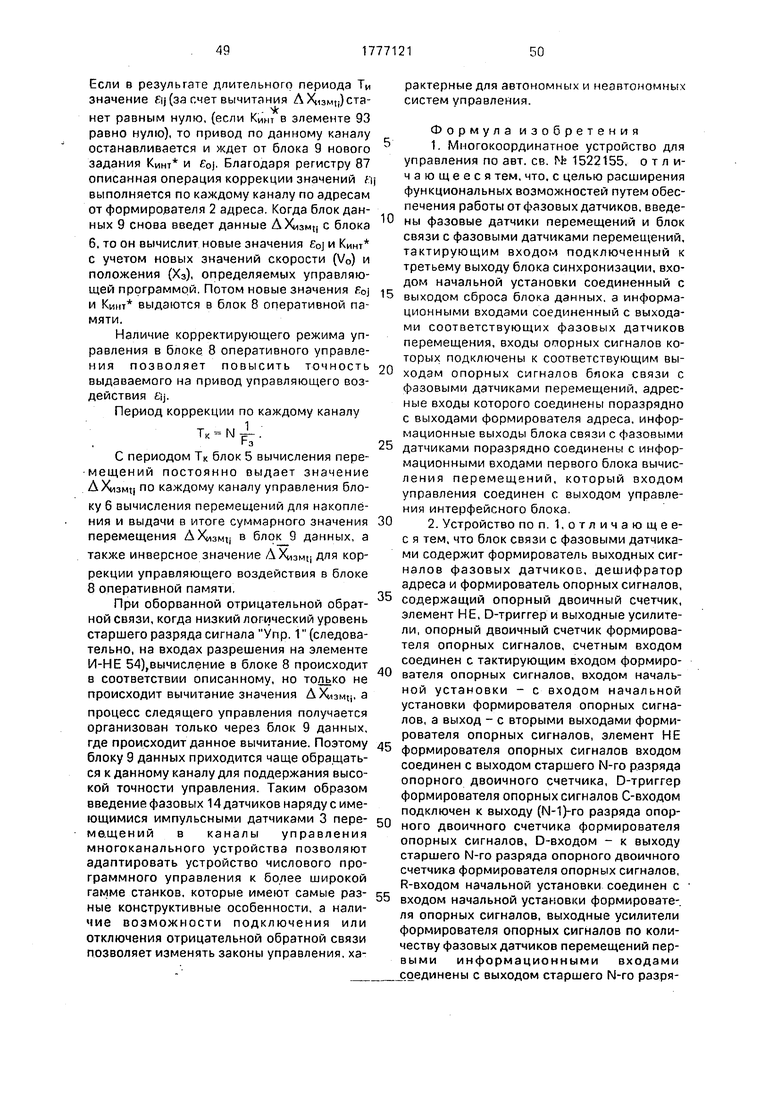

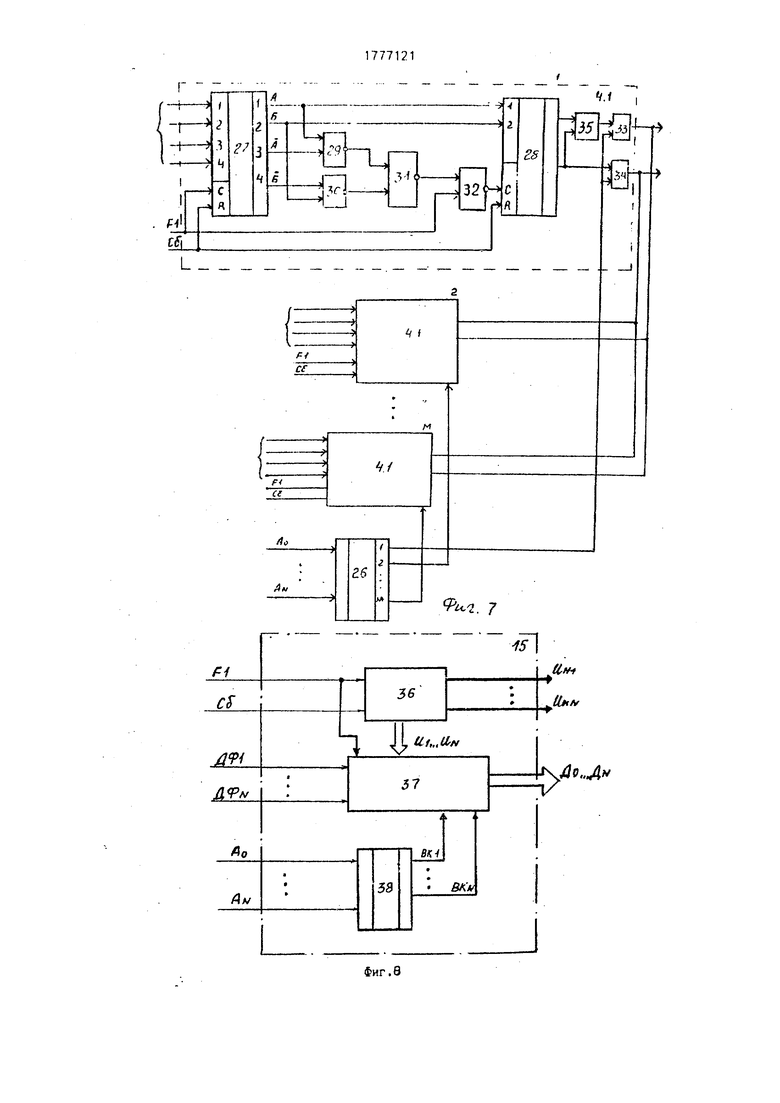

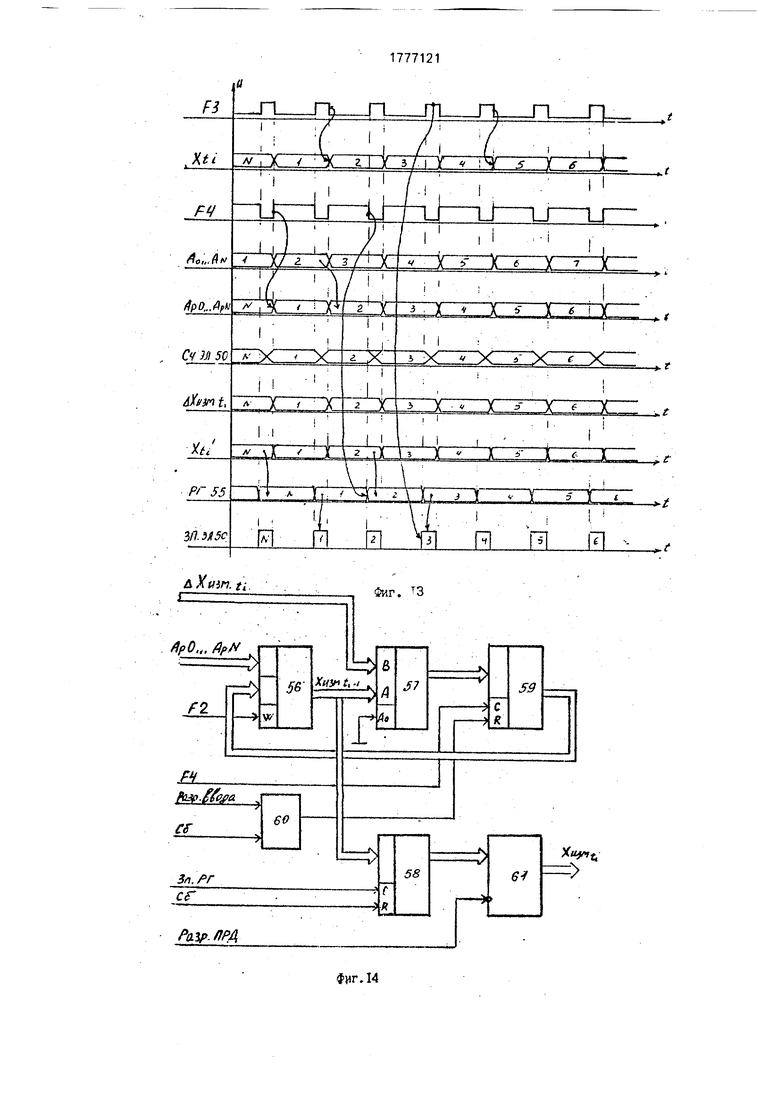

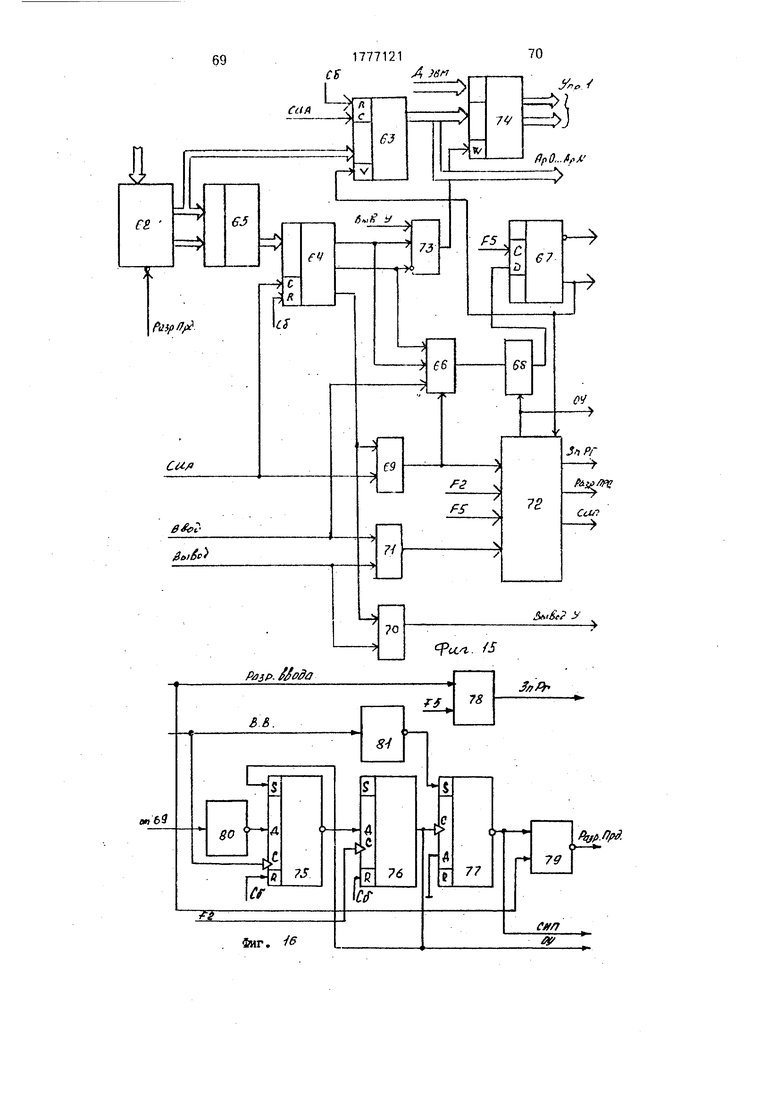

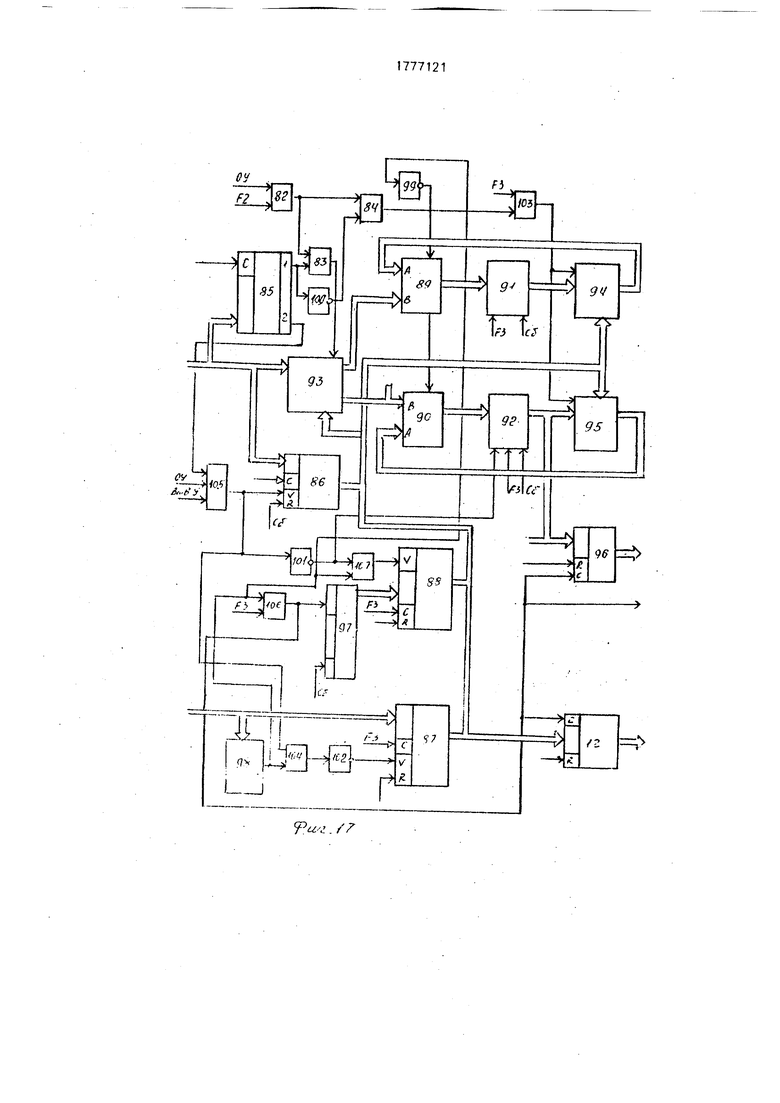

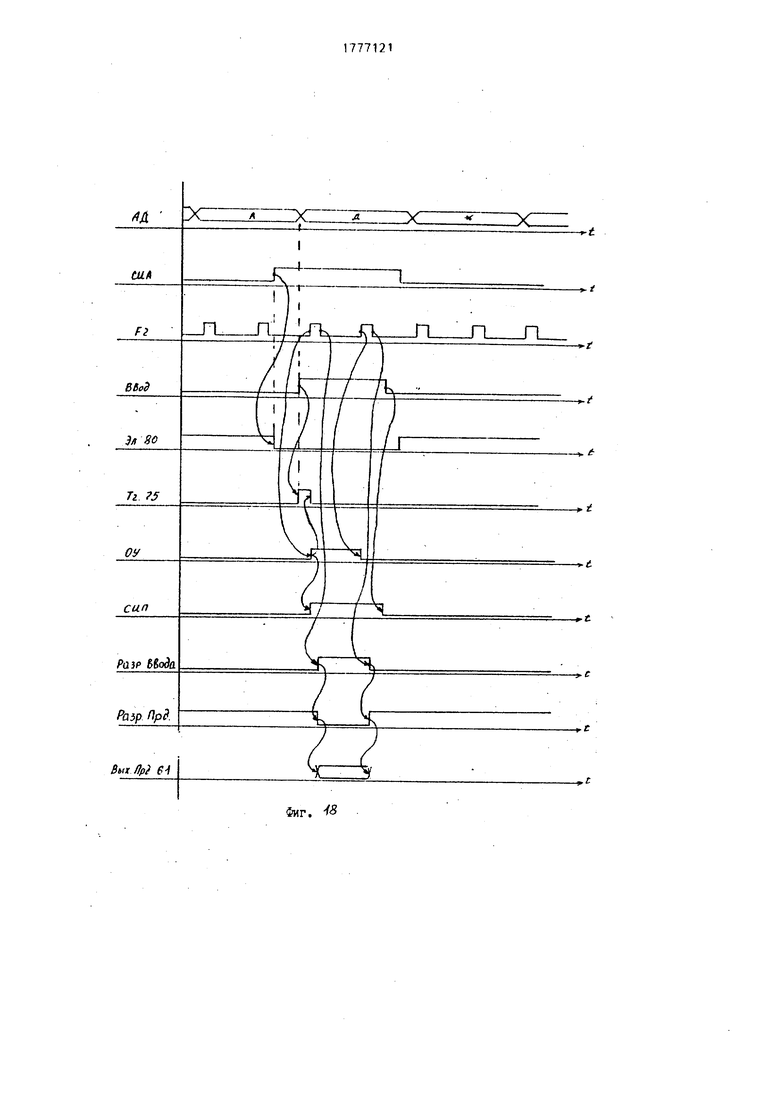

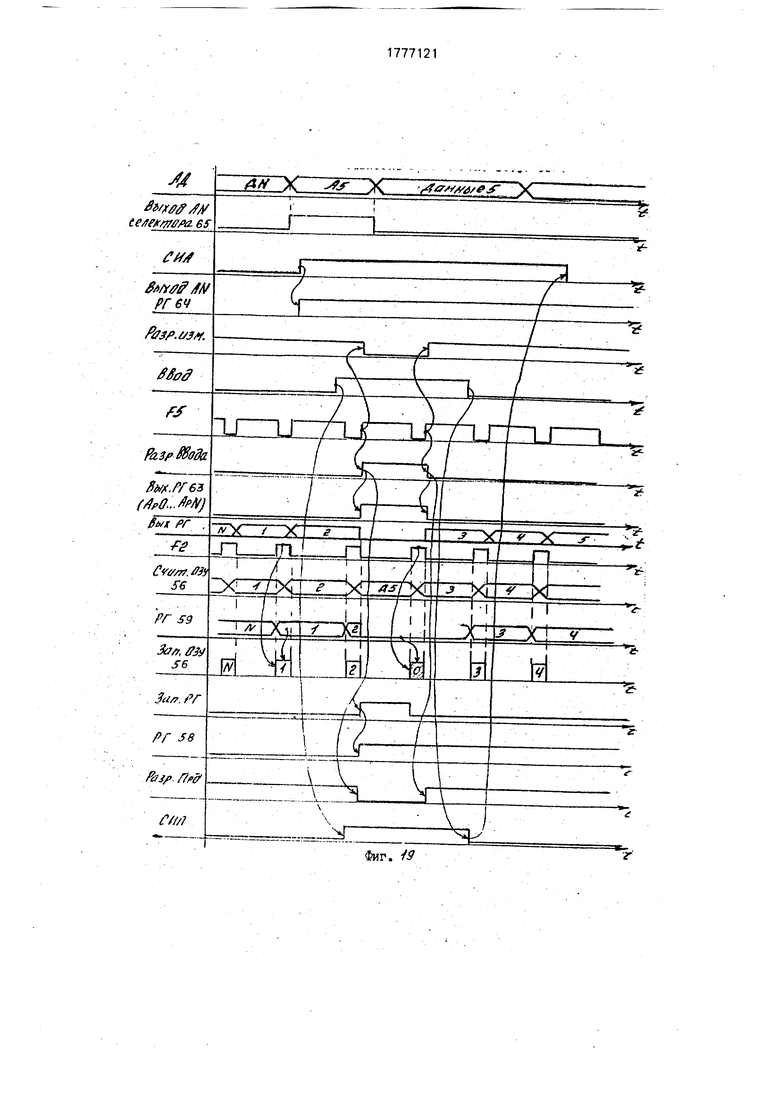

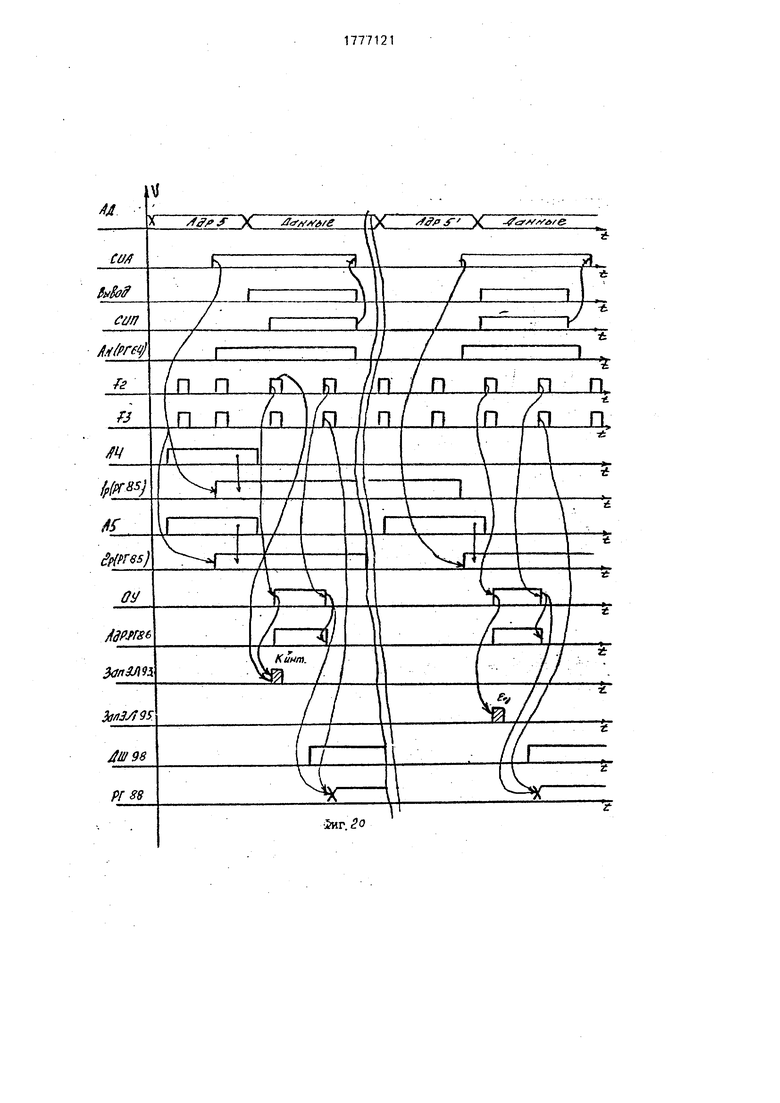

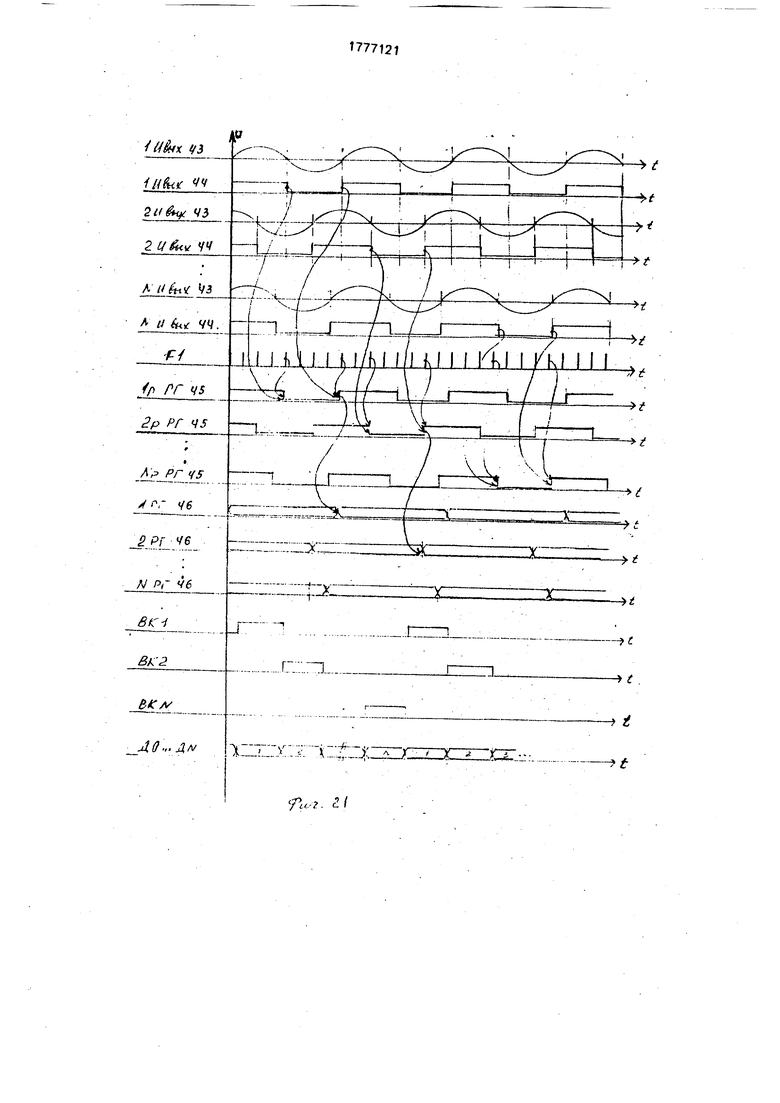

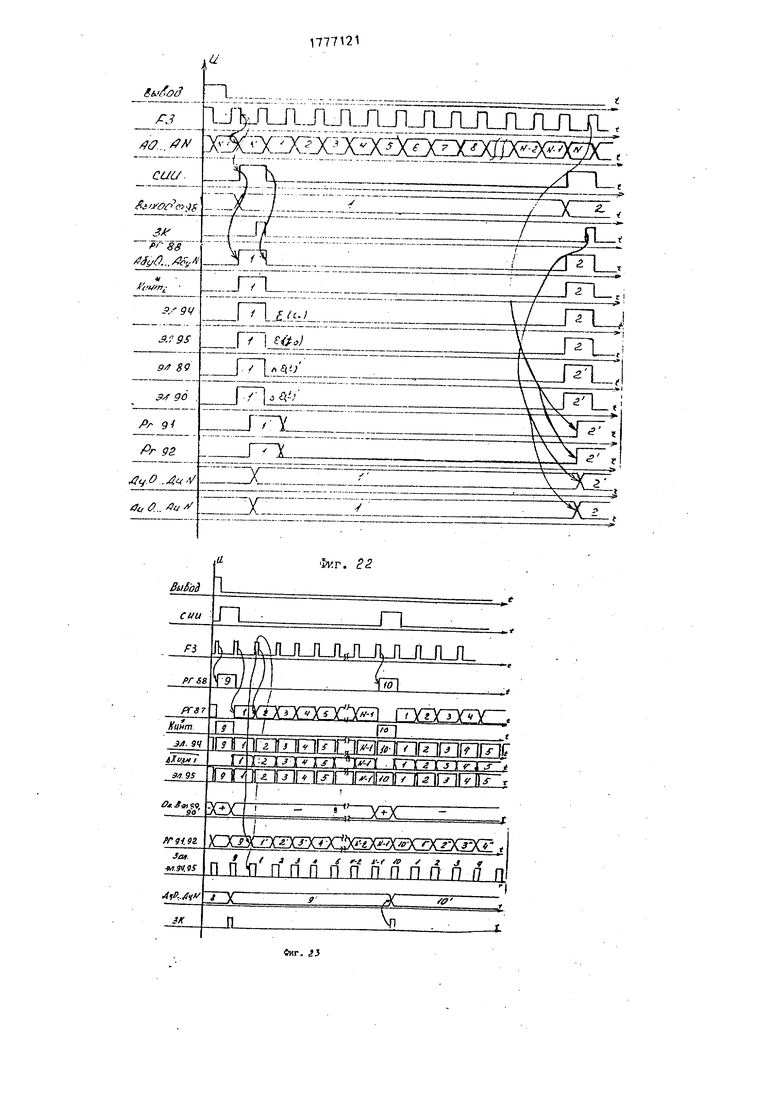

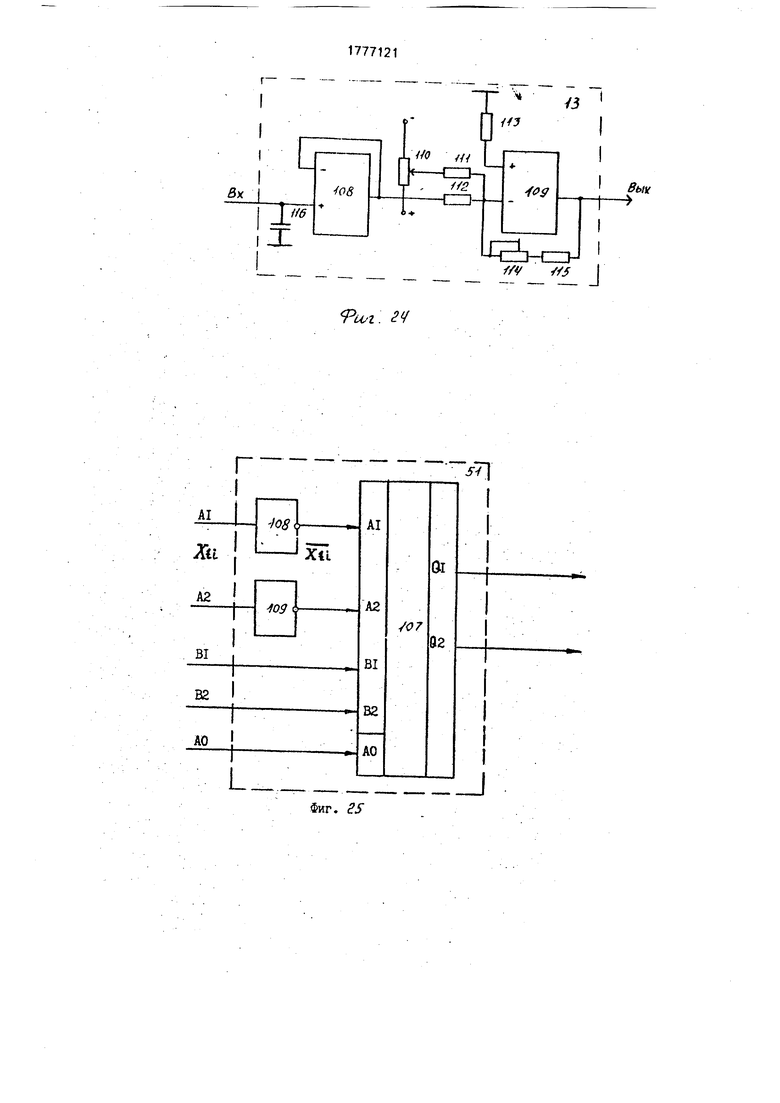

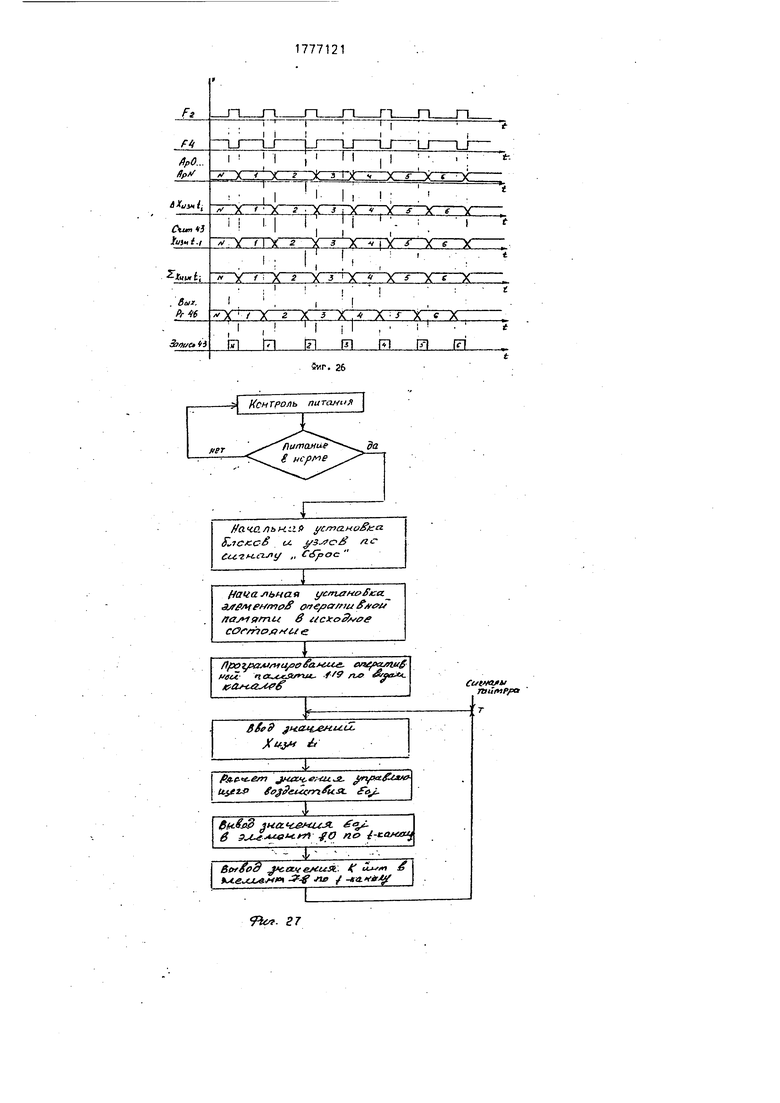

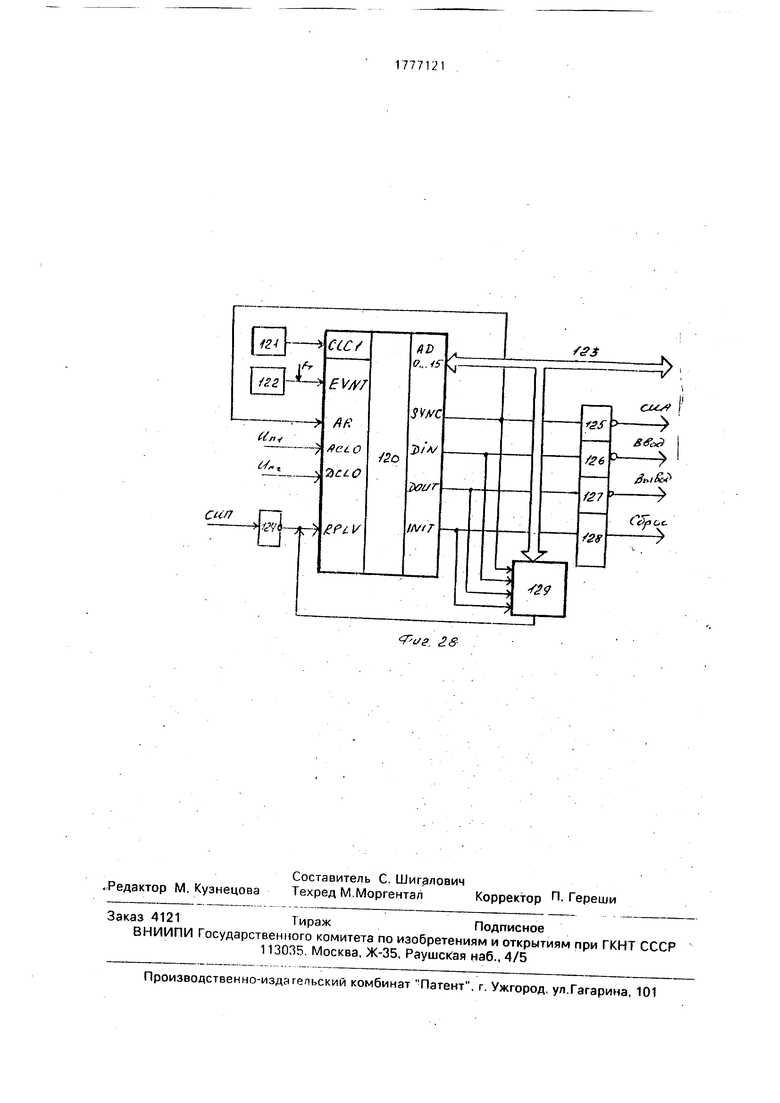

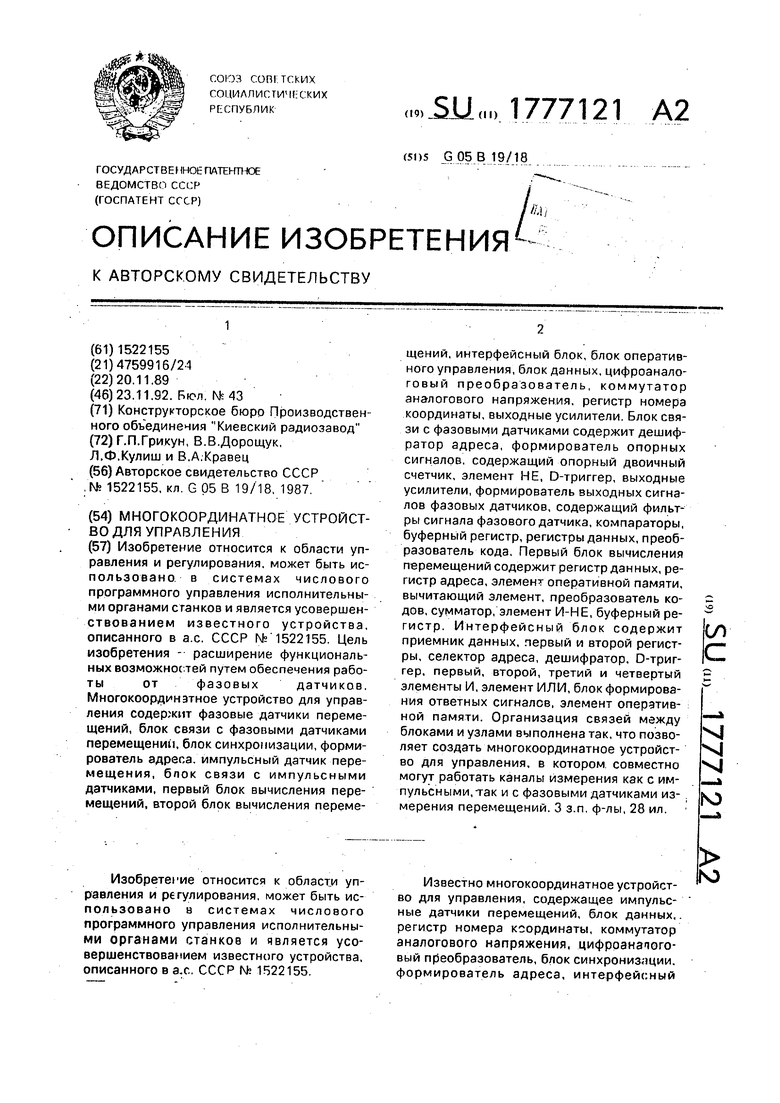

На фиг. 1 представлена блок-схема многокоординатного устройства для управления; на фиг. 2 - схема блока синхронизации, пример исполнения; на фиг. 3 - схема делителя частоты блока синхронизации, пример исполнения; на фиг. 4 - временные диаграммы работы блока синхронизации; на фиг. 5 схема формирования адреса, пример исполнения; на фиг. 6 - временные диаграммы формирования сигналов импульсного датчика перемещений; на фиг. 7 -схема блока связи с импульсными датчиками, пример исполнения; на фиг. 8 - схема блока связи с фазовыми датчиками; на фит. 9 - схема формирователя импульсов накачки, пример исполнения; на фиг. 10- временные диаграммы формирования импульсов накачки для фазовых датчиков перемещений; на фиг. 11 - схема-формирователя выходных сигналов фазового датчика, пример исполнения; на фиг. 12 - схема первого блока вычисления перемещений; на фиг, 13 приведены временные диаграммы работы первого блока вычисления перемещений; на фиг. 14 - схема второго блока вычисления перемещений, пример исполнения; на фиг. 15 - схема блока интерфейсного; на фиг. 16 - схема блока формирования ответных сигналов синхронизации, пример исполнения; на фиг. 17 - схема блока оперативного управления перемещениями, пример исполнения; на фиг. 18, фиг, 19 - временные диаграммы ввода данных; на фиг. 20- временные диаграммы вывода данных о значении величин коэффициентов интегрирования и начального управляющего воздействия в блок оперативного управления; на фиг. 21 - временные диаграммы формирования двоичного кода по сигналам фазовых датчиков; на фиг. 22 - временные диаграммы работы блока оперативного управления в режиме интерполяции; на фиг. 23 - временные диаграммы работы блока оперативного управления в режиме слежения за счет внутренней отрицательной связи по положению от датчиков за время между циклами интерполяции управляющего воздействия; на фиг. 24 - схема выходного усилителя с элементом аналоговой памяти, пример исполнения; на фиг. 25 - схема вычитающего элемента, пример исполнения; на фиг. 26 - временные диаграммы работы второго вычислителя перемещений; на фиг, 27 - алгоритм работы устройства; на фиг. 28-схема блока данных, пример исполнения.

Устройство содержит блок синхронизации 1. формирователь адреса 2, импульсный

датчик перемещения 3. блок 4 связи с импульсными датчиками, первый 5 и второй 6 блоки вычисления перемещений, интерфейсный блок 7, блок оперативного управления 8, блок данных 9. цифроаналоговый преобразователь 10, коммутатор аналогового напряжения 11, регистр номера координаты 12, выходные усилители 13.1...13.П, фазовый датчик перемещений 14, блок 15 связи с фазовыми датчиками перемещений.

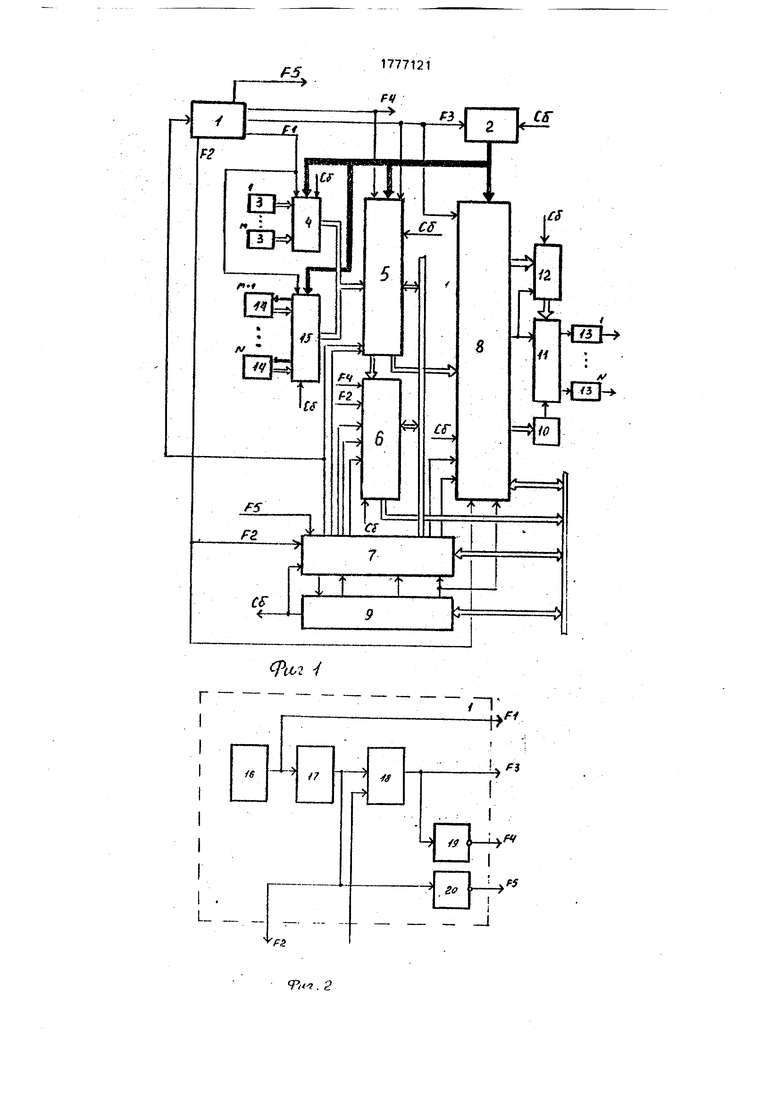

Блок 1 синхронизации (см. фиг. 2) образуют задающий генератор 16, делитель частоты 17, элемент И 18, элементы НЕ 19, 20.

Делитель частоты (см. фиг. 3) содержит двоичный счетчик 21, элемент И 22.

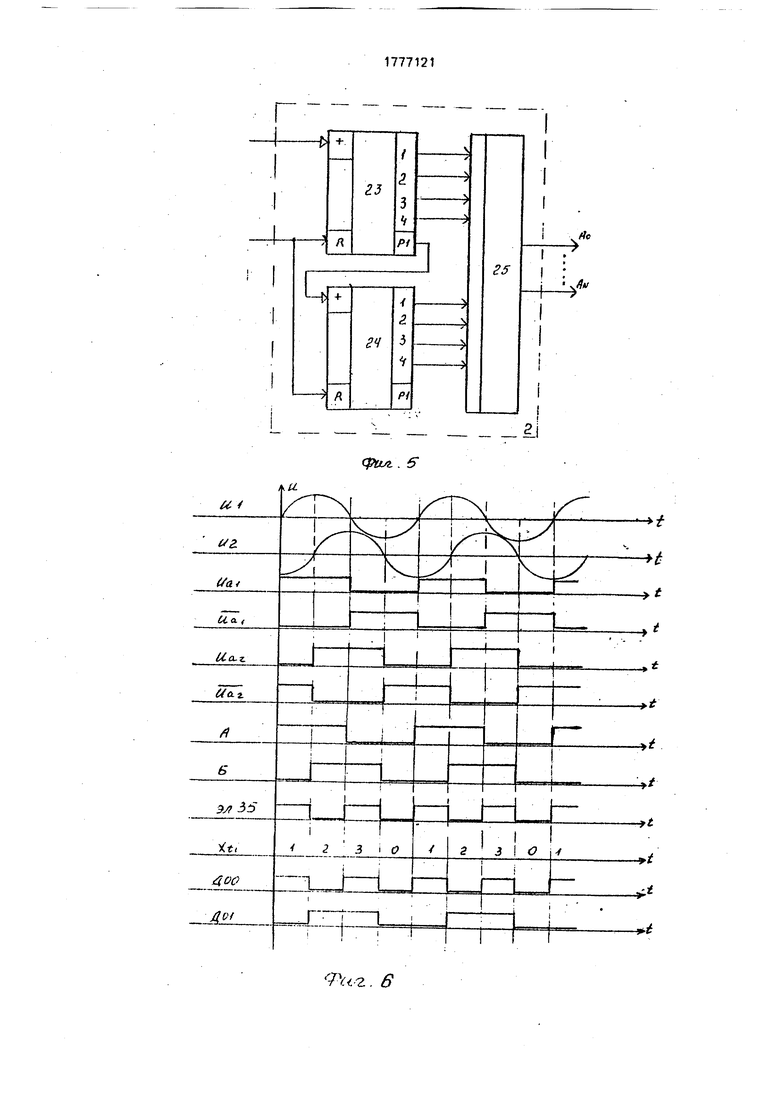

Формирователь 2 адреса (см. фиг. 5) содержит первый 23 и второй 24 двоичные счетчики, дешифратор 25.

Блок связи (см. фиг. 7) содержит дешифратор адреса 26. в каждом канале связи первый 27 и второй 28 регистры, элементы сравнения 29, 30, элемент ИЛИ-НЕ 31, первый 32, второй 33 и третий 34 элементы И, третий элемент сравнения 35.

Блок 15 связи с фазовыми датчиками перемещений (см. фиг. 8) содержит форми- рователь опорных сигналов 36, формирователь 37 выходных сигналов фазового датчика, дешифратор адреса 38.

Формирователь опорных сигналов 36 (см. фиг. 9) содержит опорный двоичный счетчик 39, элемент НЕ 40, D-триггер 41, выходные усилители 42 импульсов накачки.

Формирователь выходных сигналов фазового датчика 37 (см. фиг. 11) содержит фильтр 43 сигнала фазового датчика, компаратор 44, буферный регистр 45, регистр данных 46, преобразователь кодов 47.

Блок 5 (см. фиг. 12) содержит регистр данных 48, регистр адреса 49, элемент оперативной памяти 50, вычитающий элемент 51, преобразователь кодов 52, сумматор 53, элемент Й-НЕ 54, буферный регистр 55.

Блок 6 (см. фиг. 14) включает элемент оперативной памяти 56, сумматор 57, буферный регистр 58, регистр данных 59, элемент ИЛИ 60. передатчик данных 61.

Блок 7 (см. фиг. 15) содержит приемник данных 62, второй 63 и первый 64 регистры, селектор адреса 65, дешифратор 66, D-триггер 67, первый 68, третий 69 и второй 70 элементы И, элемент ИЛИ 71, блок формирования ответных сигналов 72, четвертый элемент И 73, элемент оперативной памяти 74.

Блок 72 формирования ответных сигналов (см. фиг. 16) содержит первый 75, второй 76, третий 77 D-триггеры, первый 78, второй 79 элементы И, первый 80, второй 81 элементы НЕ.

Блок оперативного управления 8 (см. фиг. 17) содержит первый 82, второй 83, третий 84 элементы И, первый 85, второй 86 регистры адреса, регистр 87 следящих коор- динат, регистр 88 адреса интерполяции, первый 89, второй 90 арифметические элементы (АЛУ), первый 91 и второй 92 регистры данных, первый 93, второй 94, третий 95 элементы оперативной памяти, регистр 96

данных управления приводом, счетчик 97 импульсов, дешифратор 98, первый 99, второй 100, третий 101, четвертый 102 элементы НЕ, первый 103, второй 104 элементы ИЛИ, первый 105, второй 106, третий 107

элементы И.

Выходные усилители 13.1...13.п(см.фиг. 24) содержат первый 108, второй 109 операционные усилители, первый 110, второй 111, третий 112, четвертый 113, пятый 114, шестой 115 резисторы, конденсатор 116.

Вычитающий элемент 51 (см. фиг, 25) содержит как пример исполнения сумматор 117, первый 118, второй 119 элементы НЕ. Пример исполнения блока 9 данных (см.

фиг. 28). Блок 9 содержит процессор 120, задающий генератор 121, таймер 122, канал связи 123, первый 124, второй 125, третий 126,четвертый 127 элементы НЕ, формирователь 128 сигнала Сброс, блок памяти

129 процессора.

Устройство работает следующим образом.

Блок 9 данных при включении питания многокоординатного устройства анализирует уровни напряжения на своих входах контроля питания. Если напряжение питания устройства в норме, то с выхода Сброс по шине Сброс распространяется сигнал высокого логического уровня. По этому сигналу в исходное состояние, при котором на информационных выходах - низкие логические уровни сигналов, устанавливаются счетчики 23, 24, 97, 39, регистры 12, 27, 28, 33, 34, 55, 58, 59, 63, 64, 86, 87, 88,91, 92, 96

и D-триггерры 75, 76 и 41.

После этого блок 9 данных производит запись нулевых логических уровней сигналов в ячейки элементов 56, 93, 94, 95 оперативной памяти следующим образом. На выходе блока 72 формирования ответных сигналов в исходном состоянии сигнал Разр. Прд. высокого логического уровня, потому что на входах элемента И-НЕ 79 - низкие логические уровни сигналов. Приемник данных 62 при наличии высокого логического уровня сигнала на входе (С) разрешения принимает двоичный многоразрядный код адреса, выставленного блоком 9. После установки адреса блок 9

выставляет сигнал синхронизации адреса (СИА) на свою шину СИА. Высокий логический уровень сигнала СИА свидетельствует о том, что адрес блока 9 данных выставлен на выходах приема (передачи адреса) данных. По положительному фронту сигнала СИА младшие разряды (например Ор...Зр) с информационных выходов приемника 62 запомнятся регистром 63. Одновременно селектор 65 по комбинации высоких и низких логических уровней сигналов старших разрядов (например, 6р...15р) с вторых информационных выходов приемника 62 определяет соответствие принадлежности адреса полю адресов многоканального устройства управления. Если адрес принадлежит этому полю, то на выходе AN селектора

65адреса появляется высокий логический уровень сигнала и одновременно разрешается прохождение транзитом дополнительных разрядов адреса (например, 4р и 5р) с первого выхода на соответствующие выходы АО, Ам-1 селектора 65. По положительному фронту сигнала СИА логические уровни сигналов с информационных выходов селектора 65 будут записаны в регистр 64. При наличии высокого логического уровня сигнала на информационном выходе AN регистра 64, а следовательно, высокий уровень сигнала на входе разрешения дешифратора

66адреса через элемент И 69 появляется высокий логический уровень сигнала, затем блок 9 выставляет сигнал Ввод с высоким логическим уровнем сигнала и убирает двоичный код адреса со своих информационных выходов, так как он уже расшифрован селектором 65 адреса и его логические уровни сигналов уже находятся в регистрах 63 и 64. Таким образом освобождаются выходы приема (передачи адреса) данных блока 9 для приема данных от передатчика 61. Наличие высокого логического.сигнала Ввод на первом входе разрешения дешифратора 66 адреса позволяет дешифратору 66 расшифровать дополнительные разряды АО,

, AN-I, примятые регистром 64 (например. 4ри 5р). При условии, что сигналы А0, Ам-1 низкого логического уровня, на выходе дешифратора 66 появляется сигнал высокого логического уровня, что свидетельствует о принадлежности выставленного блоком 9 адреса полю адресов элемента 56 оперативной памяти. Высокий логический уровень сигнала на выходе элемента И 78. возникший в результате поступления на его входы высоких логических уровней сигналов, инвертируется элементом НЕ 80. поступает на D-вход D-триггера 75. D-триггеры 75 и 76 находятся к этому моменту в исходном состоянии, при котором на их выходах - нулевые логические уровни сигналов. По положительному фронту импульса с выхода элемента ИЛИ 71, возникшего в результате установки сигнала Ввод, D-триггер 75 запоминает состояние нулевого логического уровня сигнала, присутствующего на его D- входе. В результате на инверсном выходе D-триггера 75 установлен высокий логический уровень сигнала.

0По положительному фронту импульса

частоты F2 на информационном выходе D- триггера 76 возникает также высокий логический уровень сигнала, по которому D-триггер 75 через S-вход устанавливает на

5 своем инверсном выходе нулевой логический уровень сигнала (фиг. 18). По следующему положительному фронту импульса частоты F2 на выходе D-триггера устанавливается низкий логический уровень сигнала.

0 в результате на выходе D-триггера 76 формируется импульс, по которому на выходе элемента И 68 устанавливается высокий логический уровень сигнала, Одновременно высокий логический уровень сигнала при5 сутстзует на D-входе D-триггера 67. По положительному фронту импульса частоты F5 на (прямом) первом выходе D-триггера 67 устанавливается высокий логический уровень сигнала Рззр. ввода, а на втором (ин0 версном) выходе - сигнал низкого логического уровня Разр. изм.. Высокий логический уровень сигнала Разр. ввода на входе выборки (V) регистра 63 разрешает выдачу двоичного кода числа, обозначаю5 щего адрес ячейки элемента оперативной памяти, относящейся к одному из каналов управления многоканального устройства управления (например, первого канала). Количество разрядов одного двоичного слова,

0 относящегося к одному адресу элемента 56 оперативной памяти, равно не менее 8, что соответствует одному байту передаваемой информации. С информационных выходов элемента 56 оперативной памяти данные

5 поступают через буферный регистр 58, передатчик 61 по каналу связи к входам передачи (приема данных) адреса (АД) блока 9 данных. Благодаря различным логическим уровням сигналов Разр. ввода и Разр.

0 изм. с выходов D-триггера 67 обеспечивается поочередная работа регистра 49 адресг и регистра 63 на входы адреса элемента 56 оперативной памяти. Таким образом, блок 9 посредством регистра 63 извлекает из ука5 занной ячейки элемента 56 оперативной памяти необходимые для реализации алгоритма работы устройства данные. Данные на выходе элемента 56 оперативной памяти - постоянные с момента выдачи адреса по отрицательному фронту частоты F2

до отрицательного фронта частоты F4. Сигнал частоты F5 имеет высокий логический уровень, Сигнал Разр. ввода с выхода D- триггера 67 также имеет высокий логический уровень. В результате на выходе элемента И 78 появляется сигнал Запись регистра (зап. Рг). По положительному фронту сигнала Зап. Рг данные с информационных выходов элемента 56 оперативной памяти Заносятся в буферный регистр 58. Одновременно сигнал Разр. ввода через элемент ИЛИ 60 по входу R устанавливает и удерживает на информационных выходах регистра 59 низкие логические уровни сигналов. Как только на входе W управления элемента 56 оперативной памяти установится высокий логический уровень сигнала частоты F2. нулевые логические уровни сигналов с выходов регистра 59 данных записываются в ячейку элемента 56 оперативной памяти вместо ранее находившейся информации. Таким образом, блок 9 данных, выполняя первоначальное считывание, очищает многоразрядную ячейку элемента 56 оперативной памяти, в которой накапливаются при вычислении перемещений данные по одному из каналов управления. Наличие высокого логического сигнала Ввод, а следовательно, высокого логического уровня сигнала на выходе элемента ИЛИ 71 позволяет через элемент НЕ 81 разблокировать D-триггер 77 по S-входу, из-за которого постоянно на его инверсном выходе удерживается сигнал нулевого логического уровня. Таким образом, по положительному фронту сигнала ОУ (фиг. 18) с выхода D-триггера 76-в D-триггер 77 записывается нулевой логический уровень сигнала с D-входа. В результате на инверсном выходе D-триггера 77 устанавливается высокий логический уровень ответного сигнала синхронизации (СИП), сигнализирующий блоку 9 данных о том. что информация на выходах передатчика стабильна. Наличие сигналов Разр. ввода и СИП на входах элемента И 79 вызывает появление сигнала Разр. Прд низкого логического уровня, по которому данные измерителя с буферного 58 регистра через передатчик 61 передаются на входы приема-передачи данных - адреса блока 9 данных и принимаются блоком 9 данных. Приняв сигнал СИП, блок 9 данных снимает высокие логические уровни сигналов со своих выходов Ввод и СИА и заканчивает обмен по данному адресу с одним из каналов измерителя (например, первым). Так как сигналы СИА и Ввод стали низкого логического уровня, то дешифратор 66 прекращает выдачу сигнала высокого логического уровня со своего информационного выхода. На выходе элемента И 68 также устанавливается низкий логический уровень сигнала из-за отсутствия высокого логического сигнала ОУ на входе, который по положительному фронту импульса частоты F5 запоминается D-триггером 67 (фиг. 19). В результате сигнал Разр. ввода становится низкого логического уровня, а сигнал Разр. изм. - высокого логического уровня и запрещается выдача регистру 63 двоичного кода (ApO...ApN) на адресные входы элементов 50 и 56 оперативной памяти, но разрешается выдача двоичного кода ApO...ApN на указанные элементы 50 и 56 оперативной

5 памяти регистру 49 адреса. Кроме того, по сигналу высокого логического уровня Разр. изм. разрешается выдача импульсов частоты F3 и F4. Из-за отсутствия высокого логического сигнала Ввод от блока 9 данных

0 D-триггер 77 по S-входу на своем инверсном выходе устанавливает сигнал низкого логического уровня благодаря наличию логической единицы на выходе элемента НЕ 81.Поэтому снимается высокий логический

5 уровень сигнала СИП. Так как логический уровень сигнала Разр. ввода стал низким, то снимается с выхода элемента И 78 высокий уровень сигнала Зап. Рг. Из-за высокого логического уровня сигнала Разр.

0 Прд. передатчик 61 прекращает выдачу данных в канал. На этом обмен блока 9 по вводу данных с ячеек элемента 56 оперативной памяти по адресу первого канала заканчивается, Блок 9 данных выставляет адрес

5 для приема данных в ячейки элемента 56 оперативной памяти, соответствующих второму каналу измерителя. Для этого блок 9 данных в младших разрядах адреса (Ор..,3р), передаваемого 16-разрядным двоичным ко0 дом, вместо двоичного кода нуля Оа (0000) выдает двоичный код 12 (0001), что соответствует адресу второго канала. Потом снова выставляет сигналы СИА, Ввод, принимает сигнал СИП и параллельно данные из

5 многоразрядной ячейки второго канала. В элементе 56 оперативной памяти теперь записаны логические уровни с выходов регистра 59 по адресу второго канала. Этот процесс - Ввод данных - блок 9 данных

0 повторяет по адресам ячеек всех каналов управления, реализованных в многоканальном устройстве, до тех пор пока не будут занесены нулевые логические уровни сигналов во все ячейки элемента 56 оперативной

5 памяти. После этого блок 9 данных в свой внутренний оперативный регистр процессо- ра записывает нулевые логические уровни сигналов, куда были приняты данные последнего канала многоканального устройст- вас ячеек элемента 56 оперативной памяти.

и заканчивает процесс установки ячеек элемента 56 оперативной памяти в исходное состояние. Блок 9 данных по этой же подпрограмме начальной установки продолжает установку в исходное состояние, при котором во всех ячейках осуществлена запись нулевых логических уровней сигналов элементов 93...95 оперативной памяти (фиг. 17) блока 8 оперативного управления. Для этого блок 9 выставляет на информационные входы приемника 62 многоразрядный двоичный код адреса (например 16-разрядный), Так как сигналы Разр. Прд. высокого логического уровня, как и в случае Ввод данных, то приемник 62 принимает многоразрядный двоичный код адреса со своих входов и транслирует младшие разряды (например, Ор...Зр) к информационтым входам регистра 63, сигналы дополнительных разрядов (например, 4р и 5р) - к первым информационным входам селектора 65 адреса и сигналы старших разрядов (например 6р...15р) - к вторым информационным входам селектора 65 адреса. После установки адреса блок 9 данных выставляет сигнал синхронизации адреса СИЛ. Высокий логический уровень сигнала С /1Асвидетельствует о том, что адрес блоком 9 данных выставлен в канал связи. По положительному фронту сигнала СНА младшие разряды (Ор...3р)с информационных выходов приемника 62 запоминается регистром 63, а также регистром 86. Селектор 65 аналогично описанной операции ввода данных от третьего вычислителя 6 расшифровывает старшие разряды адреса (6р. .15р) и выставляет на выходе AN высокий логический уровень сигнала, по которому через селектор 65 разрешается прохождение дополнительных разрядов (4р; 5р) соответственно на выходы АО, AN-I. Регистр 64 по положительному фронту сигнала СНА, передаваемому блоком 9 параллельно двоичному коду адреса, запоминает состояние логических уровней информационных входов, Для доступа блока к ячейкам элемента 93 оперативной памяти в такте выдачи адреса (А5 по фиг. 19) 4- и 5-й разряды должны быть установлены в I, Указанные разряды по сигналу СИЛ от блока 9 данных записываются в регистр 85. В результате на первом и втором выходах регистра 85 адреса присутствуют высокие логические уровни сигналов, свидетельствующие о том, что адресное поле младших разрядов адреса (Ор...р) относится к элементу 93 оперативной памяти. Высокий логический уровень сигнала на выходе AN регистра 64 разрешает появление высокого логического уровня сигнала на выходе элемента И 69. После выдачи сигнала СИА блок

9 снимает многоразрядный двоичный код адреса со своих выходов адреса-данных,который теперь уже запомнен регистром 64 и регистром 85, а самые младшие разряды

(Ор...3р) - регистром 86,, регистр 63 сигналом Вывод по входу V установлен в третье состояние. Блок 9 выставляет высокий логический уровень сигнала Вывод, по которому элементом ИЛИ 71, элементом НЕ 80,

0 D-триггерами 75 и 76 вырабатывается (как и в случае описанного процесса ввода данных измерителя) сигнал ОУ (фиг. 16) (опрос устройства) высокого логического уровня,а также элементом НЕ 81 и D-триггером 77

5 вырабатывается высокий логический уровень ответного сигнала СИП. Сигнал СИП, поступающий на вход приема ответного сигнала блока 9 данных, указывает теперь блоку 9 данных на готовность блока 8

0 оперативного управления принять данные в элемент 93 оперативной памяти. Наличие высоких логических сигналов на входах элемента И 105 вызывает появление на его выходе сигнала высокого логического уровня.

5 По этому сигналу выходы регистра 86 адреса (фиг. 20) подключаются R адресным входам элементе,.) 93...95 оперативной памяти. По двоичному коду адреса с выхода регистра 86 выбираются соответствующие ячейки

0 элементов 93...95. Блок 9 данных к этому моменту выставляет по шинам, ранее передавшим адрес, нулевые логические уровни данных, которые запоминаются ячейками элемента 93 оперативной памяти, так как

5 только на входе записи этого элемента присутствуетвысокий логический уровень сигнала с выхода элемента И 83 (фиг. 17). что было определено наличием единиц в дополнительных разрядах адреса

0 (4р, 5р), а следовательно на первом и втором информационных выходах регистра 85. Прием низких логических уровней сигналов данных и запись их в ячейки элементов 93 оперативной памяти соответствуют очище-.

5 нию (исходному состоянию) информации в ячейках указанным двоичным кодом адреса с выхода регистра 86 (например, по адресу первого канала управления). После передачи данных блок 9 данных снимает сигналы

0 Вывод, СИА со своих выходов. На выходах элемента И 70 и элемента ИЛИ 71 устанавливаются низкие логические уровни сигналов. В результате через элемент НЕ 81 на инверсном выходе D-триггера 77 по S-входу

5 устанавливается логический уровень сигнала, что соответствует снятию сигнала СИП. Низким логическим уровнем сигнала ОУ устанавливается логический уровень сигнала на выходе элемента И 105, который по входу выборки выходов (V) запрещает выдачу двоичного кода адреса с информационных выходов регистра 86 переводом их в третье состояние, при котором их выходное сопротивление велико. На этом цикл вывода данных в элемент 93 оперативной памяти по адресу одного из каналов многоканального устройства (например, первого) блок 9 заканчивает и вновь выставляет адрес, соответствующий элементу 93 оперативной памяти следующего (второго) канала управления. После этого блок 9 повторяет установку высоких логических уровней сигналов СИА, Вывод, далее ожидает, как и в предыдущем цикле, высокого логического сигна ла СИП и в итоге выдает низкие логические уровни сигналов данных, которые запоминаются ячейками, соответствующими в элементе 93 оперативной памяти адресу последующего (второго) канала управления. Далее блок 9 повторяет цикл нулевых логических уровней данных по адресам ячеек элемента 93 оперативной памяти последующих каналов, пока все ячейки элемента 93 оперативной памяти не окажутся заполненными низкими логическими уровнями сигналов, что соответствует установке элемента 93 оперативной памяти в исходное состояние. Блок 9 данных переходит к выводу нулевых логических уровней данных в элементы 94 и 95 оперативной памяти. Процесс вывода данных полностью совпадает с описанным для элемента 93 оперативной памяти и отличается только адресом, а точнее наличием нулевого логического разряда (4р) при высоком логическом уровне сигнала в старшем (5р) дополнительном разряде. В результате по такой комбинации логических сигналов дешифратор 71 адреса на своем выходе не выдает высокий логический уровень сигнала. Но эти логические уровни сигналов по сигналу СИА от блока 9 данных записываются в регистр 85 адреса. В результате на первом информационном выходе регистра 85 адреса устанавливается низкий логический уровень сигнала, а на втором информационном выходе - высокий логический уровень сигнала. В результате благодаря элементу НЕ 100 разрешается прохождение сигнала высокого логического уровня с выхода элемента И 82 через элемент И 84 вместо элемента И 83. Поэтому через элемент ИЛИ 104 высокий логический уровень сигнала на входах W элементов 94 и 95 разрешает запись данных с информационных выходов элементов 94 и 95 в ячейки, указываемые тем же вторым регистром 86 адреса, хранящим двоичный код адреса одного из каналов управления при выводе данных из блока 9 (например, первого канала, потом, при повторном выводе данных,

второго, третьего и до тех пор, пока не очистятся все ячейки элементов 94 и 95 оперативной памяти последующих каналов). Так как данные на информационные входы эле- мента 94 оперативной памяти непосредственно с блока 9 данных не поступают, то очищение ячеек этого элемента происходит благодаря наличию нулевых логических уровней сигналов в ячейках элемента 93

0 оперативной памяти, а также благодаря работе арифметических элементов 89 и 90 на вычитание из-за присутствия высокого логического уровня сигнала на выходе элемента НЕ 99. Тогда в ячейках элемента 94 опера5 тивной памяти, в которых сохранились высокие логические уровни, они будут скомпенсированы благодаря приходящему сигналу по этому же разряду данных с арифметического элемента с обратным знаком,

0 так как при вычитании двоичного кода на входах А из двоичного кода нуля на входах В получим число со знаком минус. Информационные выходы регистра 92 на время вывода данных из блока 9 отключены от

5 информационных входов элемента 95 оперативной памяти из-за наличия на входе выборки выходов (V) регистра 92 низкого логического уровня сигнала с выхода элемента НЕ 101, так как в это время на выходе

0 элемента И 105 должен быть высокий логический уровень сигнала. Таким образом, записью нулей в ячейки элементов 94 и 95 оперативной памяти блок 9 заканчивает выполнение подпрограммы установки много5 канального устройства в исходное состояние и переходит на программу управления перемещениями.

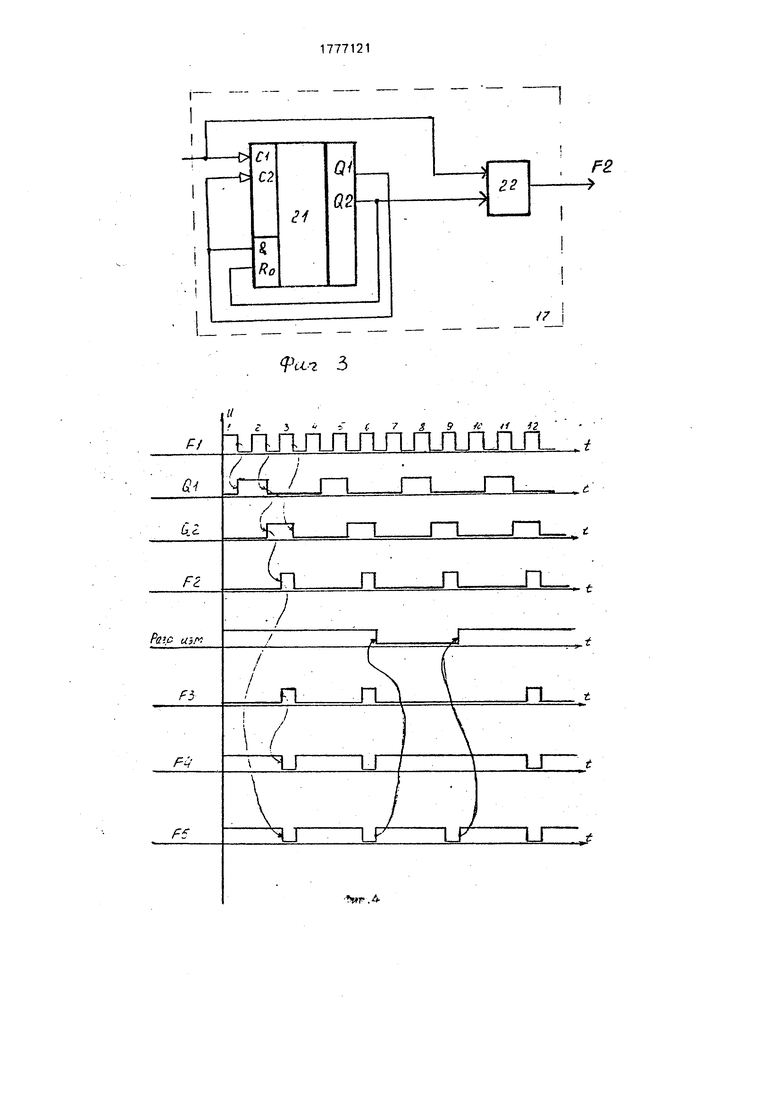

Прямоугольные импульсы частоты F1 с выхода задающего генератора 16 (фиг. 2)

0 поступают на вход делителя 17 частоты. Коэффициент деления делителя 17 частоты (фиг. 3) равен трем. В исходном состоянии уровни логических сигналов выходных разрядов Q1 и Q2 двоичного счетчика 21 нахо5 дятся в нулевом состоянии из-за наличия обратных связей с выходов счетчика 21 на его входы начальной установки. По каждому отрицательному фронту положительного импульса частоты F1 (фиг. 4) появляется низ0 кий или высокий уровень логического сигнала на выходе разряда Q1 счетчика 21. При изменении уровня логического сигнала на выходе Q2 двоичного счетчика 21 устанавливается высокий логический уровень сигнала

5 благодаря наличию связи с выхода Q1 на вход С2. По следующему (третьему) отрицательному фронту положительного импульса частоты F1 на выходе Q1 двоичного счетчика 21 должен установиться высокий логический уровень сигнала. Но наличие высокого

логического уровня сигнала на выходах 02 и Q1 двоичного счетчика 21 позволяет через его входы начальной установки установить снова на выходах Q1 и Q2 низкие логические уровни сигнала. Далее процесс повторяется. В результате на выходах Q1 и Q2 счетчика 21 будут две последовательности импульсов. При наличии высоких логических уровней сигналов одновременно на выходе Q2 двоичного счетчика 21 и на выходе задающего генератора 16 на выходе элемента И 22 появляется высокий логический .уровень сигнала, а пропадание одного из сигналов - низкий логический уровень. Так как этот процесс периодически повторяется, то на выходе элемента И 22 формируется последовательность прямоугольных импульсов с частотой F2, которая по частоте в три раза ниже последовательности импульсов частоты F1. Высокий логический уровень сигнала Разр. изм на втором входе элемента И 18, который присутствует всегда, когда блок 9 не выводит данных о перемещении с элемента 56 оперативной памяти третьего вычислителя 6, разрешает прохождение импульсных сигналов частоты F2 с первого входа элемента И 18 на его выход. Импульсные сигналы на выходе элемента И 18 (последовательность импульсов частоты F3) всегда равны частоте импульсов F2, за исключением того, что могут прерываться на время отсутствия высокого логического уровня сигнала Разр. изм. Последовательность импульсов частоты F5 получена путем инверсии логических уровней сигнала частоты F2 элементом НЕ 20.

Прямоугольные импульсы частоты F3 поступают на вход формирователя 2 адреса (фиг. 5). В исходном состоянии, при котором на информационных выходах - низкие логические уровни сигналов, а на выходе Р1 (по- ложительного переноса) - высокий логический уровень сигнала, двоичные счетчики 23 и 24 устанавливаются по сигналу Сброс от блока 9 данных.

По каждом/ отрицательному фронту положительного импульса частоты F3 на выходе 1 двоичного счетчика 23 появляются высокие или низкие уровни логического сигнала. По каждому отрицательному фронту положительного импульса на выходе 1 появляются высокие или низкие уровни логического сигнала на выходе 2 двоичного счетчика 23. По каждому отрицательному фронту положительного импульса на выходе 3 появляются высокие или низкие уровни логического сигнала на выходе 4 двоичного счетчика 23. В момент, когда на всех выходах двоичного счетчика 23 устанавливаются высокие логические уровни по отрицательному фронту импульса частоты F3, на выходе положительного переноса (Р1) двоичного счетчика 23 появляется низкий

логический уровень сигнала. По следующему положительному фронту импульса частоты F3 на всех информационных выходах двоичного 23 счетчика устанавливаются низкие логические уровни логического сиг0 нала, а на выходе положительного переноса (Р1) - высокий логический уровень. По каждому отрицательному фронту импульса с выхода положительного переноса (Р1) счетчика 23 двоичный счетчика 24 на выходе

5 1 формирует высокий или низкий логический уровень логического сигнала. По каждому отрицательному фронту импульса с выхода 1 двоичного счетчика 24 на выходе 2 формируется высокий или низкий логи0 ческий уровень. Далее по отрицательному фронту импульса с выхода 2 появляются высокие или низкие логические уровни сигнала на выходе 3 двоичного счетчика 24. По отрицательному фронту импульса с выхо5 да 3 устанавливаются высокие или низкие логические уровни на выходе двоичного счетчика. После прохождения 256 импульсов частоты F3 на счетный вход двоичного счетчика 23 на информационных выходах

0 двоичных счетчиков 23 и 24 устанавливаются высокие логические уровни. Таким образом получаем на информационных выходах двоичных счетчиков 256 комбинаций высоких или низких логических уровней сигна5 лов. Дешифратор 25 (дешифратор, генератор кодов каналов управления) представляет собой элемент программируемого запоминающего устройства, преобразующего уровни логических сигналов с выходов

0 двоичных счетчиков 23 и 24 в двоичные коды адресов каналов управления. Двоичный код числа О соответствует адресу первого канала управления, двоичный код числа 1 соответствует адресу второго канала управ5 ления и так до полного количества каналов (N-1) (например, 11-1) многоканального устройства управления и плюс один последующий дополнительный двоичный код числа N например, 11 для реализации режима

0 интерполяции в блоке 8 оперативного управления. Разрядность двоичного кода с выхода программируемой логической матрицы выбирается в соответствии с разрядностью двоичного кода числа N (например, 11),

5 используемого для реализации режима интерполяции. При малом количестве каналов управления,когда разрядность входного кода на дешифраторе 25 намного больше разрядностивыходногокода, программирование необходимо выполнить

так, чтобы последующие (избыточные) комбинации входных сигналов повторно последовательно выставляли на выходах двоичные коды чисел, соответствующие адресам каналов управления, пока не будут полностью использованы все 256 комбинаций сигналов с информационных выходов двоичных счетчиков 23 и 24.

Каналы управления, требующие более частого появления адреса по отношению к остальным каналам управления при их последовательном появлении на выходе дешифратора 25, программируются не последовательно, а периодически повторяются внутри полного цикла изменения двоичных кодов чисел на выходе дешифратора 25, что соответствует более частому выставлению адреса канала управления. Количество разрядов двоичного числа на выходе дешифратора 25 должно всегда соответствовать количеству информационных входов регистра 63 и регистра 93 устройства управления для совместимости адресов, выставляемых с дешифратора 25 и выдаваемых блоком 9 по каналам управления. Количество разрядов двоичного числа на выходе дешифратора 25 должно всегда соответствовать количеству информационных входов регистра-63 и регистра 93 устройства управления для совместимости адресов, выставляемых с дешифратора 25 и выдаваемых блоком 9 по каналам управления.

Датчик 3 представляет собой фотоэлектрический измерительный преобразователь. Конструктивно осветитель, конденсатор, индикаторный растр, измерительная растровая решетка, четыре фотоприемника расположены так, что при перемещении измерительной растровой решетки, кинематически связанной с перемещаемым узлом станка, на выходах фотоприемников происходит изменение электрических сигналов во времени, что позволяет осуществлять автоматический подсчет прошедших муаровых полос. Фотоприемники, в свою очередь, конструктивно расположены так, что при перемещении измерительной растровой решетки в одном направлении первый сигнал Ui, создаваемый первой парой фотоприемников, опережает на четверть периода второй сигнал U2, создаваемый второй парой фотоприемников, а при перемещении в противоположном направлении второй сигнал Ur опережает первый сигнал Ui на четверть периода. Поэтому знак фазового сдвига сигналами Ui и U2 с выходов фотоприемников характеризует направление измеряемого - перемещения. Плавно

изменяющиеся (фиг. 6) сигналы Ui и Ua с выходов соответственно первой и второй пар фотоприемников усиливаются и преобразуются в прямоугольные сигналы каждый

своим усилителем-формирователем, находящимся внутри датчика 3.

В результате на выходах усилителей- формирователей получаем прямоугольные импульсы (фиг. 6) Uai и U32. Каждый высокий

или низкий логический уровень импульсной последовательности U31 или Ua2 соответствует перемещению измерительной растровой решетки датчика на один шаг. Так как датчик 3 располагается всегда непосредст5 венно на станке, а устройство числового программного управления, обрабатывающее сигналы Uai и Ua2 датчика на расстоянии 10 м и более, то с целью повышения помехоустойчивости передачи сигналов па0 раллельно сигналам Uai и Ua2 формируются дополнительно контрольные сигналы Uai и Ua2, имеющие инверсное значение логических уровней по отношению к основным сигналам Ua1 И Ua2

5 Для этого сигналы Uai и Ua2 пропускают каждый через свой логический элемент НЕ, находящийся в датчике, и полученные сигналы Uai и Ua2 выдаются параллельно с сигналами Uai и иа2 на вьосоды датчика.

0Сигналы U31- Ua2, U31, Ua2 датчика 3 принимаются каналами связи блока 4 связи. В исходное (фиг. 7) состояние, при котором на выходах - нулевые логические уровни, регистры 27 и 28 каждого канала связи устанав5 ливаются по сигналу Сброс при включении питания устройства. По приходу импульса положительной полярности частоты F1 с выхода блока 1 синхронизации зна- чения логических уровней .сигналов Uai, Ua2.

0 uai, Ua2 запоминаются четырехразрядным регистром 27. В результате на информационных выходах регистра 27 устанавливаются логические уровни сигналов, соответствующие логическим уровням сиг5 налов на информационных входах. Сигнал А с первого информационного выхода регистра 27 сравнивается элементом 29 сравнения со своим дополнительным инверсным сигналом А, который был принят через третий

0 информационный вход и находится на третьем информационном выходе этого регистра. Аналогично происходит сравнение сигнала Б с второго выхода регистра 27 со своим дополнительным инверсным сигна5 лом Б элементом 30 сравнения. Если сигналы на информационных входах элементов 29 и 30 сравнения различных логических уровней, то на их выходах присутствуют низкие логические уровни сигналов, что смг- нализирует о правильном приеме сигналов

Ual и Ua2 от датчика 3. При совпадении логических уровней сигналов на входах одного из элементов 29 и 30 сравнения на его выходе устанавливается сигнал высокого логического уровня из-за инверсного выхода. Наличие высокого логического уровня на выходе элемента 29 сравнения сигнализирует о существовании помехи по сигналу Uai, передаваемому с датчика, и его ложное значение учитывать не следует. Поэтому элемент ИЛИ-НЕ 31 анализирует состояние логических уровней сигналов на своих входах. Если на обоих входах элемента ИЛИ- НЕ 31 сигналы низкого логического уровня, то на его выходе устанавливается сигнал высокого логического уровня, который разрешает прохождение положительного импульса частоты F1 через элемент И 32 на вход записи (С) регистра 28. Только после этого регистр 28 запоминает логические уровни сигналов А и Б, находящиеся на его информационных входах.

Появление высокого логического уровня сигнала на выходе одного из элементов 29 и 30 сравнения вызывает появление нулевого логического уровня сигнала на выходе элемента ИЛИ-НЕ 31, что запрещает прохождение положительного импульса частоты F1 через элемент И 32 на вход записи с регистра 28. Для обеспечения многократной проверки сигналов Uai и Ua2, достоверной записи их в регистр 28 каждого канала необходимо, чтобы F1 F3. Это соотношение задается делителем 17 частоты блока 1 синхронизации. Частота импульсов F3 блока синхронизации должна, в свою очередь, быть выбрана из условия

F3 .датч Мд,

где Гмакс.датч - частота выходных (Uai, Ua2) сигналов датчика при максимальной скорости движения перемещаемого объекта на станке;

Ыд - максимальное количество каналов управления (датчиков) в многоканальном устройстве.

Логические уровни сиг налов на выходах второго 28 регистра канала связи, представляющие код Грея, несущий информацию о положении подвижного органа датчика 3 данного каиала, преобразуются третьим 35 элементом сравнения исключающим ИЛИ в обычный двоичный код. Следует обратить внимание что элемент 35 исключающий ИЛИ в отличие от устройства по основному изобретению установлен в каналы связи 4.1 блока связи 4. Необходимость в преобразовании кода Грея в обычный двоичный код вызвана неудобством дальнейших вычислений с этим кодом. Кроме того, как показано ниже, имея возможность получить

данные о перемещении датчика 3 на выходе блока связи 4 в обычном двоичном коде, получаем новую возможность - подключить к информационным входам первого 5 вычислителя перемещений блок 15 связи с фазовыми датчиками перемещений - фазовый 14 датчик перемещения, наряду с имеющимся уже в устройстве импульсным 3 датчиком перемещений. Рассмотрим процесс

преобразования кода Грея в двоичный код на примере одного (например, первого из датчиков 3) (фиг. 6). Благодаря элементу 35 сравнения, который при различных уровнях сигналов на входах выдает на своем выходе

высокий логический уровень сигнала, а при совпадающих уровнях - низкий, легко получить двоичный код числа о положении датчика по коду Грея, несущий ту же информацию. В результате на новых информационных входах элементов И 33 и 34 появляется двоичный код Xti положения датчика с периодом, равным периоду последовательности импульсов F1.

Дешифратор 26 расшифровывает двоичные коды адреса координаты, приходящие с выходов формирователя 2 адреса. Если но входе дешифратора 26 находится не дополнительный код, предназначенный для реализации режима интерполяции в блоке 8

оперативного управления, то на одном из выходов дешифратора, подключенного к вторым входам элементов И 33 и 34 одного из каналов связи 4.1, появляется высокий логический уровень сигнала, соответствующий входному двоичному коду адреса канала управления. Например, если на входе дешифратора 26 двоичный код числа 02, что соответствует адресу первого канала управления, то на первом выходе дешифратора 26 присутствует высокий логический уровень сигнала. Таким образом, через элементы И 33 и 34 разрешается прохождение высоких логических уровней сигналов с их информационных входов. В результате на

первом и втором выходах первого канала связи устанавливается комбинация высоких или низких логических уровней сигналов ДОО и Д01, соответствующая обычному двоичному коду и обозначающая число о положении датчика первого канала в данный момент считывания.

Кроме того, сигналы о перемещении подвижных органов станка (фиг. 1) по каналам от М+1 до N вырабатываются фазовыми 14

датчиками перемещений. Датчик 14 представляет собой синусно-косинусный вращающийся трансформатор. На статоре и роторе намотаны не менее чем по две обмотки, сдвинутые в пространстве на 90°.

На статорные обмотки подаются две последовательности импульсов Ф1 и Ф2 от блока 15 связи с фазовыми датчиками перемещений, Благодаря первым гармоникам импульсных сигналов Ф1 и Ф2 в роторных обмотках индицируется ЭДС, имеющая такую же частоту, как и частота опорных сигналов Ф1 и Ф2, но сдвинутая по фазе относительно первых гармоник опорного напряжения на угол, который определяется углом поворота ротора датчика 14. Так как ротор датчика кинематически связан с перемещаемым узлом станка, то датчик 14 осуществляет измерительные преобразования перемещения в фазовый угол синусоидальных колебаний первой гармоники сигнала на выходе датчика. Но так как на датчик 14 подаются импульсные сигналы, то при разложении в ряд Фурье будут также присутствовать кроме первых гармоник и высшие нечетные гармоники. В результате этого на выходе датчика 14 будет сигнал не синусоидальный, а более сложной формы из-за присутствия дополнительно в датчике магнитных полей образующихся от последующих гармоник импульсных сигналов Ф1 и Ф2, Для обеспечения фазовых датчиков 14 перемещения опорными сигналами накачки и принятия сигналов о перемещении служит блок 15 связи с фазовыми датчиками перемещений (фиг. 8).

Формирователь 36 импульсов накзчки блока 15 связи с фазовыми датчиками перемещений вырабатывает последовательность импульсов Ф1 и Ф2 и инверсные им значения импульсов Ф1, Ф2. Четыремпосле- довательности импульсов Ф1, Ф2, Ф1, Ф2 условно на фиг. 8 обозначены Ин1 (опорное напряжение). Схема формирователя 36 импульсов накачки представлена на фиг. 9. При поступлении импульсов последовательности F1 на счетный вход опорного двоичного счетчика 39 на его информационных выходах устанавливаются высокие или низкие логические уровни сигналов.

В исходное состояние, когда на всех информационных выходах низкие логические уровни сигналов, двоичный счетчик 39 устанавливается сигналом Сброс. С информационного выхода старшего разряда логические сигналы поступают на первые входы выходных 42 усилителей, а через элемент НЕ 40 - на вторые информационные входы выходных 42 усилителей импульсов. С помощью D-триггера 41 логические сигналы с выхода старшего разряда тактируются по С-входу-импульсами предыдущего разряда (UN-I). В результате на третьем и четвертом выходах усилителей 42 импульсов будут находится импульсы Ф2, Ф2 сдвинутые по

0

5

0

5

0

5

0

5

0

5

отношению к импульсам Ф1, Ф1 на первом и втором входах этого же усилителя на 90° (фиг. 10). Усиленные по мощности последовательности импульсов Ф1, Ф1, Ф2, Ф2 усилителем 42 поступают на статорные обмотки (вращающегося трансформатора) фазового 14 датчика перемещений в качестве опорных. Причем последовательности поступают в начало первой обмотки, а Ф1 в конец этой же обмотки и аналогично - Ф2 и Ф2 на вторую обмотку датчика 14.

Выходные сигналы о перемещении якоря каждого датчика 14 поступают на один из одноименных номеру фазового датчика 14 перемещений входов ДФ1...ДФМ формирователя 37 выходных сигналов фазового датчика (фиг. 8). Так как сигнал, снимаемый с якорной обмотки фазового датчика 14 пере- мещений,имеет сложную форму, из-за присутствия множества гармоник, полученных от импульсных сигналов (Ф1, Ф2) накачки и их инверсных значений (Ф1, Ф2), подаваемых, как указывалось выше, на статорные обмотки, то для выделения первой гармоники (как наиболее информативной для измерения) из сигнала якорной обмотки служит фильтр 43 сигнала фазового датчика, установленный на каждом входе ДФ1...ДФМ (фиг. 11). Примером построения такого фильтра является фильтр, состоящий из двух последовательно соединенных звеньев, каждое из которых является фильтром нижних частот второго порядка, передаточная характеристика с парой комплексно сопряженных полюсов

H(

Но 0)0

S i + а й)0 + о)0 где S - комплексная частота;

Но - коэффициент усиления;

со0 - собственная круговая частота фильтра;

а - относительный коэффициент затухания.

Для установления оптимальной ширины полосы пропускания сигналов первой гармоники, обеспечивающей неискаженную передачу сигнала первой гармоники с выхода датчика на компаратор, и из двух звеньев, первое и второе звено настроены на пропускание частот, близких (одно выше, другое ниже) к частоте опорных импульсов Ф1, Ф2.

С информационного выхода фильтра 43 сигналов фазового датчика сигнал первой гармоники поступает на информационный вход компаратора 44. Если синусоидальный сигнал первой гармоники с выхода фильтра 43 ниже нуля, то компаратор 44 на своем информационном выходе устанавливает

сигнал логического нуля. Если синусоидальный сигнал первой гармоники с. выхода фильтра 43 выше нуля, го компаратор 44 на своем информационном выходе устанавливает сигнал высокого логического уровня. В результате на информационных входах (1 ...N) третьего 45 буферного регистра будут устанавливаться высокие или низкие логические уровни сигналов, которые получены от компаратора 44 каждого канала. По каждому положительному фронту импульса F1 (фиг. 21) значения логических сигналов на информационных входах третьего буферного 45 регистра будут запоминаться этим же регистром. В результате на информационных выходах третьего 45 буферного регистра будут появляться также высокие или низкие логические уровни логических сигналов, принятые с одноименного по номеру входа этого же регистра. По переднему фронту появляющегося положительного импульса на одном из выходов (например, первом) происходит запись двоичного кода UI...UN в соответствующий номеру регистр данных 46. Так как на выходах буферного регистра 45 положительные фронты положительных импульсов будут появляться (из- за перемещения роторов датчиков) в различное время, то в каждом из регистров 46 будут записаны различные числа,соответ- ствующие двоичному коду Ui. .UN от опорного счетчика 39.

Так как вал (ротор) каждого датчика 14 вращается, то следовател но по отношению к опорным импульсам будет смещаться фаза первой гармоники сигнала, полученного на выходе фильтра 43, а следовательно раньше или позднее будет появляться (с каждым F1) передний фронт положительного импульса, который также будет синхронно смещаться. Следовательно, в один и тот же регистр 46 постоянно будет записываться двоичный код числа величина которого пропорциональна перемещению фазы относительно импульсов накачки Ф1 и Ф2. Дешифратор адреса 38 настроен так, что дешифрует область адресов А0 . AM от формирователя адреса 2,не занятую дешифратором адреса 26. В результате на выходе дешифратора 38 будут последовательно появляться высокие логические уровни сигналов BK1...BKN При установлении последовательно высоких логических уровней сигналов ВК1 AKN регистры данных 46 с первого по N поочередно открывают свои информационные выходы, которые в исходном состоянии находятся в третьем состоянии. Данные с выходов регистра данных 46 поступают на входы младших разрядов адреса преобразопателя кодов 47 На входы

0

5

0

5

0

5

0

5

0

5

старших разрядов адреса преобразователя кодов 47 поступают поразрядно сигналы ВК1 .BKN. Преобразователь кодов 47 представляет собой программируемую логическую матрицу, запрограммированную таким образом, что при поступлении кодов двоичных чисел,пропорциональных смещению фазы из регистра данных 46, на информационных выходах преобразователя кодов 47 появлялись скорректированные коды (ДО. .ДМ) двоичных чисел с учетом погрешности фильтрации фильтра 43 и измерения датчика 14. Сигналы ВК1 BKN указывают преобразователю кодов 47 в какой области находятся скорректированные двоичные коды, относящиеся к одному из N фазовых датчиков 14 и его фильтру 43, который установлен в каждом канале ДФ1. ДФМ Скорректированные данные ДО ..ДЫ в сопровождении адреса поступают на входы данных первого 5 блока вычисления перемещений Первый блок 5 вычисления перемещений принимает данные отдатчиков 3 и 14 и обрабатывает следующим образом

В исходном состоянии, при котором на выходах - низкие логические уровни сигналов, регистр 48 данных, регистр 49 адреса, буферный регистр установлены блоком 9 донных по сигналу Сброс. Так как адрес канала управления в формирователе 2 адреса формируется по отрицательному фронту импульса частоты F3 и управление записью по С-входу в регистр 48 (фиг. 12) также происходит по импульсу частоты F3, то данные ДОО, Д01 с выходов блока 4 связи 4 при двоичном коде числа 02 на входах дешифратора 26 (адрес первого канала управления перемещениями) записываются в этот регистр По положительному фронту положительного импульса частоты F4 двоичный код адреса первого канала управления запоминается регистром 49 адреса, после чегэ на выходах формирователя 2 адреса появляется двоичный код адреса второго канала 12. С этого момента блок 5 вычисления перемещений производит вычисление перемещения измерительной растровой решетки датчика 3, кинематически связанной с перемещаемым объектом первого канала, за время между предыдущим и настоящим положениями датчика 3 в моменты записч двоичного кода (в отличие от основного изобретения), где перемещения датчика были выражены кодом Грея в регистр 48 данных (точнее за период записи адреса, например, первого канала в регистр 49 адреса). Если будет выставлен адрес канала (например, пятого), к которому подключен фазовый датчик 14 перемещений, то блок 5 вычисления

перемещений производит вычисление поворота якоря датчика 14, кинематически связанного с перемещаемым объектом пятого канала, за время между предыдущим и настоящим положениями якоря датчика 14 в моменты записи двоичного кода в регистр 48 данных (точнее за период записи адреса, например, пятого канала в регистр 49 адреса).

Положение датчика (ДОО, Д01 для им- пульсного датчика 3 и ДОО.,.ДМ для фазового датчика 14 перемещений), записываемые ;в регистр 48 данные выражены для обоих видов датчиков 3 и 14 в виде многоразрядного двоичного кода. Однако следует обра- тить внимание на то, что для передачи перемещений импульсного 3 датчика достаточно двух разрядов, что обеспечивает им преимущество в простоте передачи данных. Для фазовых датчиков, чем больше разряд- ность двоичного кода, тем точнее будут отслежены перемещения фазы фазового датчика-14. Это обстоятельство ставит (по удобству реализации) фазовые датчики на второе место, но следует также обратить внимание, что фазовые датчики являются более помехоустойчивыми чем импульсные.

8результате (фиг. 13) на информационных входах А вычитающего элемента 51 будет установлен многоразрядный двоичный код Xti положения подвижного органа импульсного 3 или фазового 14 датчика в зависимости от выбранного номера канала, соответствующего адресу, записанному в регистр 49.

При наличии высокого логического уровня сигнала Разр. изм на входе выборки выходов регистра 49 адреса с его информационных выходов по внутреннему каналу ApO...ApN на адресных входах элемента 50 оперативной памяти устанавливается адрес первого канала. По этому адресу из ячеек элемента 50 оперативной памяти извлекается двоичный код положения датчика в предыдущем цикле вычислений. Так как на входе (V) выборки выходов элемента 50 оперативной памяти - высокий логический уровень сигнала, то при наличии низкого логического уровня сигнала по входу записи-считывания (W) двоичный код числа о положении датчика в предыдущем цикле вычислений передается на многоразрядный вход В вычитающего элемента 51 с информационных выходов элемента 50. Блок 5 устроен таким образом, что несмотря на то. что элемент 50 оперативной памяти не установлен от блока

9данных в исходное состояние, на выходе преобразователя 52 кодов ложный код заменяется двоичным кодом числа О, что в итоге устраняет помеху в ячейках элемента

50оперативной памяти. Рассмотрим работу блока 5 вычисления перемещений по определению пути перемещения датчика за период появления адреса одного и того же канала (например, первого) на информационных выходах регистра 49 адреса. Вычисление выполняется путем вычитания двоичных кодов чисел предыдущего и настоящего положений датчика. Процесс вычитания заключается в сложении с дополнительным кодом одного из слагаемых. При наличии кодов на входах вычитающего элемента 51 выполняется операция вычитания путем сложения кода числа на входах В с дополнительным кодом числа на входах А согласно выражению

-AX 3MtieX(t.i)iJ-Xt| + Pi, где X(t-i) - двоичный код положений 1-го датчика, принятый в предыдущем цикле по i-й координате;

„Хц двоичный код положений 1-го датчика в данный момент времени по i-й координате;

ДХизмц величина перемещения подвижного органа датчика;

Pi - единица переноса.

В результате на выходах вычитающего элемента 51 получают двухразрядный код величины перемещения конкретного датчика 3 за период появления адреса его канала на выходах регистра 49 адреса. Так как частота импульсов F3 с блока 1 синхронизации не ниже величины 4рмакс.датч Мд, то значение - Д Хизм ti на выходе вычитающего элемента

51не достигает значения больше единицы даже при максимальной скорости движения подвижного органа станка, кинематически связанного с измерительной растровой решеткой датчика 3 для каналов с импульсными датчиками (как указывалось выше,для передачи данных в каналах с импульсными датчиками и вычисления перемещений первым 5 вычислителем достаточно двухразрядного двоичного кода). Для фазовых 14 датчиков величина перемещения фазы достигает десятков единиц, а следовательно выражается многоразрядным ДОО...ДМ кодом. Поэтому преобразователь 52 кодов, предназначенный для оценки результата - ДХизмц и изменения его знака,дополни- тельно управляется сигналом Упр. 1 от блока 9 данных через интерфейсный блок 7. При низком логическом уровне младшего разряда сигнала Упр. 1 от элемента оперативной памяти 74 выбирается в программируемой логической матрице (ПЛМ) преобразователя 52 кодов зона адресов, относящихся к каналам с импульсными 3 дат уиками. При высоком логическом уровне в

младшем разряде сигнала Упр. 1 выбирается в преобразователе кодов 52 зона адресов, относящаяся к каналам с фазовыми 14 датчиками. Данные о сигналах Упр. 1 по каждому каналу (адресу) записаны в элементе оперативной памяти 74. Если значение ЛХизм tj вканзлесимпульснымдатчиком по

абсолютной величине меньше или равно единице на выходах преобразователя 52 кодов, то преобразователь 52 кодов выставляет значение ДХизм иа своих информационных выходах со знаком плюс, Если значение ДХизмц по абсолютной величине больше единицы на входах преобразователя 52, то на его выходах будет установлено число ноль в двоичной форме. Для каналов с фазовыми датчиками проверка результата не производится, но происходит изменение знака многоразрядного кода результата ДХиэкн, С выхода преобразователя кодов 52 двоичный код величины ДХиэмц поступает на сумматор 57 второго 6 вычислителя перемещений, где происходит суммирование и накопление в элементе 56 оперативной памяти значений о перемещении подвижных органов каждого датчика (импульсного 3 или фазового 14) в отдельности за множество циклов опроса. Инверсное значение ДХпмц после элемента И-НЕ 54

используется блоком 8 оперативного управления для организации отрицательной обратной связи в режиме следящего управления при отсутствии задания от блока данных 9 на перемещение объекта. Двоичный код числа ДХмзм (B отличие от основного изобретения) на выходе элемента И-НЕ 54 появляется только в том случае, когда на выходе старшего разряда элемента оперативной памяти 74 установлен высокий логический уровень сигнала Упр. 1.

Кроме того, значение Д Хцзм t,. прошедшее проверку в преобразователе 52 кодов, используется сумматором 53 для вычисления достоверного положения (Xt,) контролируемого в данный момент одного из датчиков 3 или 14. Сумматор складывает значение ДХизмц с двоичным кодом, который хранится в оперативной памяти 50. Длительность сигнала Сброс выбирается из соотношения

Тсб К -1- ,

Гз

где Тсб длительность сигнала Сброс от блока данных;

К - суммарный коэффициент деления двоичных счетчиков 23 и 24 формирователя 2 адреса;

Рз - частота импульсов блока 1 синхронизации.

Длительность сигнала Сброс формируется в блоке 9 элементом НЕ 19.

Из-за большой длительности сигнала

Сброс с блока 9 на информационных выходах буферного регистра 55 устанавливаются и удерживаются низкие логические уровни, которые по адресам с выхода реги0 стра адреса 49 последовательно записываются в ячейки элемента 50 оперативной памяти. По окончании сигнала Сброс значения Хц с выхода сумматора запоминаются регистром 55 и записываются как достовер5 ные значения кода положения контролируемого датчика в ячейки элемента 50 оперативной памяти. Каждому адресу в элементе 50 оперативной памяти соответствует многоразрядная (в отличие от двухразряд0 ной в основном изобретении) ячейка памяти, чем обеспечивается унификация блока 5 вычислений для работы как с импульсными 3 датчиками перемещений, так и с фазовыми 14 датчиками перемещений. Значение

5 кода положения датчика (3 или 14) Хц на выходе сумматора 53 по отрицательному фронту импульса частоты F4 запоминается буферным регистром 55. Так как адрес (например, первого канала), удерживается на

0 входах адреса элемента 50 оперативной памяти (фиг. 13), то по высокому логическому уровню импульса частоты F3 данные о положении датчика с информационных выходов буферного регистра 55 записываются в

5 ячейку элемента 50 оперативной памяти по адресу первого канала управления. Далее по положительному фронту импульса частоты F4 с выхода формирователя 2 адреса записывается двоичный код адреса второго

0 (или шестого, если был пятый для фазового датчика) канала управления, а по отрицательному фронту F3 - данные (ДОО...Д01 для импульсного датчика 3 или ДОО..,ДМ для фазового 14 датчика перемещения) с блока

5 связи (4 или 15) в зависимости от адреса. По этому же отрицательному фронту импульса частоты F3 на формирователе 2 адреса появляется адрес следующего канала (например, третьего).

0 Дешифратор 26 блока 4 связи опознает свой адрес, расшмфровует, и по одному из своих выходов, например третьему,уста- навливает высокий логический уровень сигнала и разрешает выдачу данных ДОО, Д01

5 о положении датчика уже третьему каналу на вход регистра 48 данных блока 5 вычисления перемещений. Блок 5 вычисления перемещений повторяет процесс вычисления перемещения по датчику 3 второго канала, аналогично третьего, четвертого и последующих каналов с импульсными 3 датчиками. Далее дешифратор 38 адреса блока 15 связи с фазовыми датчиками перемещений обозначает свой адрес, расшмфровует и по одному из своих выходов (например, шестому) устанавливает высокий логический уровень сигнала ВК и разрешает выдачу данных ДОО...ДМ о положении датчика 14 шестому каналу на вход регистра 48 данных блока 5 вычисления перемещений. Блок 5 вычисле- ния перемещений повторяет процесс вычисления перемещения по пятому каналу, аналогично шестому и последующих каналов с фазовыми датчиками, реализованных в многоканальном устройстве управления, и вновь возвращается к первому каналу с импульсным датчиком, начиная второй, третий и последующие циклы вычислений. При установлении низкого логического уровня сигнала Разр. изм| от интерфейсного блока 7 прекращается поступление импульсов частоты F3 и F4 (фиг. 4) от блока 1 синхронизации на формирователь 2 адреса и блок 5. Таким образом, каналы связи 4.1 блока 4 связи дешифратором 26 не переключаются. Одновременно дешифратор 38 прекращает выдачу сигналов ВК на регистр 46 данных. Запись данных (ДОО, Д01 от импульсных датчиков и ДОО...ДЫ от фазовых датчиков) в регистр 48 данных не происходит, запись адреса в регистр 49 адреса не происходит, выходы регистра 49 адреса по входу (V) выборки выходов и информационные выходы элемента 50 оперативной памяти по входу (V) выборки выходов переводятся в третье состояние, при котором их сопротивление бесконечно велико. Таким образом, вычисления в блоке 5 и в блоке 6 прекращаются. При установлении обратно блоком 7 сигнала Разр. изм. высокого логического уров- ня блоки 5 и 6 вычисления перемещений продолжают свою работу с места прерывания вычислений, так как адрес с выходов формирователя 2 адреса также остался неизменным из-за отсутствия импульсов час- тоты F3. Параллельно блоку 5, блок 6 вычисления перемещений производит накопление значений АХиэмц с выхода преобразователя 52 кодов в ячейках элемента 56 оперативной памяти синхронно по адре- сам, выставляемым регистром 49 адреса. Для этого блок 6 выполняет следующие операции. Двоичный код числа ДХизмц о перемещении с выходов преобразователя 52 кодов последовательно от каждого датчика в сопровождении адреса ApO...ApN передается на входы В сумматора 57 (фиг. 14). При низком логическом уровне сигнала частоты F2 на входе (W)управления записью-считыванием элемента 56 оперативной памяти по адресу на его адресных входах устанавливается на входах А сумматора содержимое ячеек. Так как в исходном состоянии в ячейках элемента 56 оперативной памяти записаны нулевые логические уровни сигналов, то на входах А сумматора 57 устанавливается двоичный код числа ноль.

В результате сложения двоичного кода числа ДХизмц с двоичным кодом ноля на выходе сумматора 57 появляется двоичный код числа АХЙзмц- По отрицательному фронту импульса частоты F4 двоичный код числа ДХ,змг| записывается в регистр 59

данных. По ближайшему высокому логическому уровню сигнала частоты F2 двоичный код числа АХизм t| с информационных выходов регистра 59 данных записывается в ячейки элемента 56 оперативной памяти по адресу, присутствующему на адресных входах этого же элемента оперативной памяти. Синхронно с импульсом частоты F2 по отрицательному фронту импульса частоты F3 в регистр 48 записываются уже данные следующего (например, второго) канала управления и по положительному фронту импульса частоты F4 -адрес второго канала в регистр 49, так как на выходе формирователя 2 адреса по предыдущему отрицательному фронту импульса частоты F3 был установлен адрес второго канала. Следовательно, блок 5 вычисляет значение АХизмц Для второго канала. Так как адрес второго канала присутствует также на адресных входах элемента 56 оперативной памяти, то блок 6 вычисления перемещений производит вычисления по второму каналу аналогично первому. В ячейках по адресу второго канала элемента 59 оперативной памяти находятся нулевые логические уровни сигналов, которые были записаны во время установки элемента 56 оперативной памяти в исходное состояние. Поэтому сумматор складывает двоичный код числа AXiaMti на входах В с двоичным кодом нуля, установленного на входах А. В результате, как и для первого канала, значение ДХизмц запоминается в

регистре 59 по отрицательному фронту импульса частоты F4 и после этого по положительному уровню сигнала частоты F2 двоичный код числа ДХомц запоминается элементом 56 памяти по адресу второго канала. Аналогично выполняются вычисления для третьего, четвертого и последующих каналов, реализованных в многоканальном ус- тройстве, и начинаются повторно вычисления по первому каналу, По адресу первого канала из ячеек элемента 56 на входах А сумматора 57 устанавливается двоичный код числа ДХ1змц , которое было записано при первом цикле вычислений, а на входах В сумматора 57 присутствует двоичный код числа АХизм ц с выходов преобразователя 52 кодов блока 5 вычисления перемещений. В результате на выходе сумматора 57 получаем двоичный код суммы двух чисел. Двоичный код суммы двух чисел, полученный в результате сложения и несущий информацию о перемещении подвижного органа датчика (измерительной решетки для датчика 3 и якоря для датчика 14) за предыдущий и настоящий циклы измерений, по отрицательному фронту импульса частоты F4 запоминается регистром 59. По высокому логическому уровню сигнала частоты F2 двоичный код суммы с регист- ра 59 записывается в ячейки 56 элемента оперативной памяти по адресу первого канала. Аналогично происходит второй цикл вычислений по адресу второго, третьего, четвертого и последующих каналов. После этого второй вычислитель начинает третий цикл вычислений с адреса первого канала. На третьем цикле вычислений складывается двоичный код суммы двух чисел, записанный в ячейки элемента 56 оперативной памяти на втором цикле вычислений и выставленный при низком уровне сигнала частоты F2 на входы А сумматора, с двоичным кодом числа с выходов преобразователя 52 кодов, присутствующим на входах В сумматора 57. В результате сложения на выходах сумматора 57 получаем двоичный код суммы двух чисел, несущий информацию о перемещении подвижного органа датчика (измерительной растровой решетки для импульсных 3 датчиков и якоря для фазовых 14 датчиков) за три цикла измерения по первому каналу, потом по второму, третьему и последующим каналам. Таким образом, в ячейках элемента 56 оперативной памяти накапливается информация о перемещении подвижного органа каждого датчика,кинематически связанного с подвижным органом станка,в отдельности за множество циклов измерений. Цикл блоком 6 прерывается только на время считывания данных, накопленных за множество циклов в ячейках элемента 56 оперативной памяти блоком 9 данных, при выполнении операции Ввод данных вычислителя перемещений, которую блок 9 данных также выполняет при работе по программе управления приводами после выполнения программы начальной установки устройства в исходное состояние следующим образом.

Пуск программы управления приводами осуществляется от (таймера) внутреннего генератора блоком 9 при прерывании обработки программы от внешних устройств, которые могут быть подключены к блоку 9 (фиг. 28). Тактовый генератор должен обеспечить на входе тактового сигнала (CLCI) микросхемы процессора 120 прямоугольные импульсы частотой 10 МГц. На входе прерывания

по таймеру (EVNT) импульсные сигналы должны быть периодом больше периода повторения программы управления приводами (fT

1 у), 16 входов - выходов (АДО...АД15) совмещены по адресным и данным системной магистрали. Использование одних и тех же выводов для передачи адресов и данных достигается разделением во времени. Для обеспечения такого разделения во времени

при передаче адреса с выхода SYNC микросхемы процессора 120 (примером исполнения которого может послужить микросхема КМ1801ВМ2) выдается сигнал синхронизации адреса (СИА), а при передаче или приеме данных - соответственно сигнал Вывод с выхода или Ввод с выхода Д1Ы микросхемы процессора 120. С вывода 1N1T микросхемы процессора 120 выдается сигнал Сброс при высоком логическом

уровне сигнала на входе ACLO. Поэтому достаточно задавать соответствующую (равную Тс) длительность сигнала Оп2 при включении источника питания многоканального устройства управления. С целью упрощения источника питания Оп2 формирователь длительности сигнала Сброс 128 выполнен отдельно, как показано на фиг. 28. Присутствие низкого логического уровня сигнала на входе RPLV

микросхемы процессора 120 указывает, что внешнее устройство приняло или выдало данные на входы АДО...АД15 микросхемы. Начальная область блока 129 памяти с адресами 0...376 (в восьмеричном коде) зарезервирована под вектора прерываний. В этой области находится вектор ЮОв, который является пусковым адресом для программы управления приводами. При переводе на входе EVNT микросхемы процессора 120

сигнала с высокого логического уровня на