сд

ГС

ел

ас

Изобретение относится к радиотехнике и может быть использовано в составе приемников амплитудно-модулированных сигналов..

Цель изобретения - повышение помехозащищенности по отношению к узкополосным помехам.

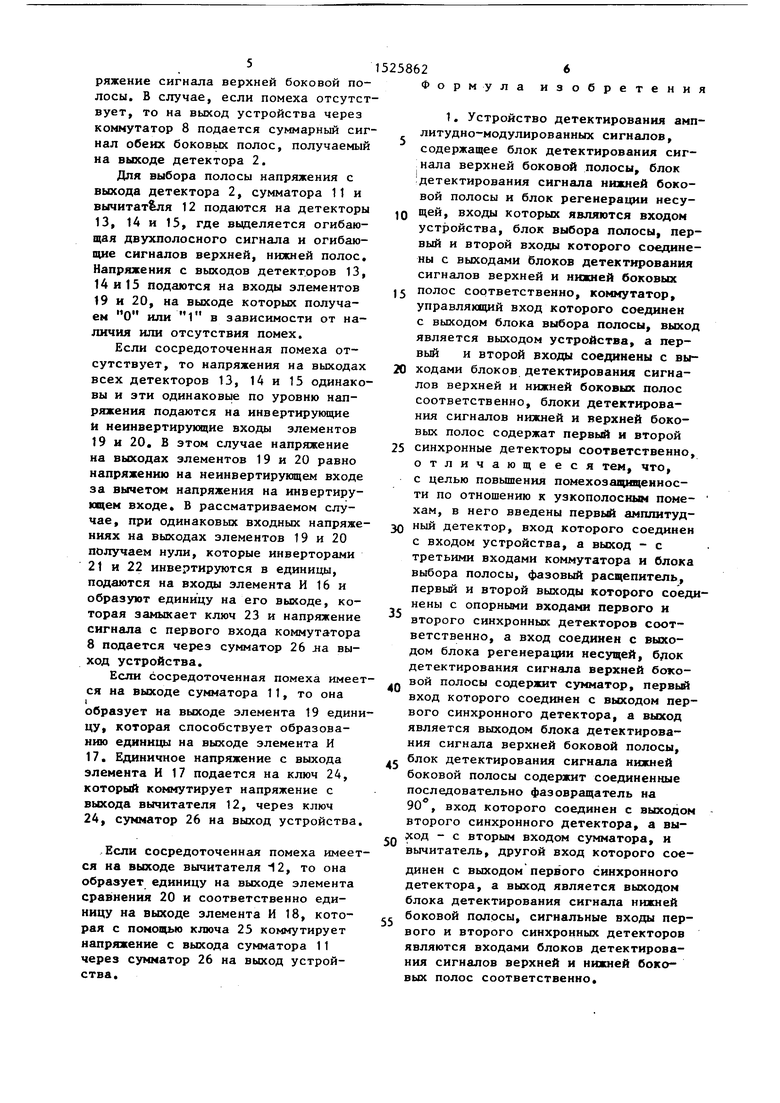

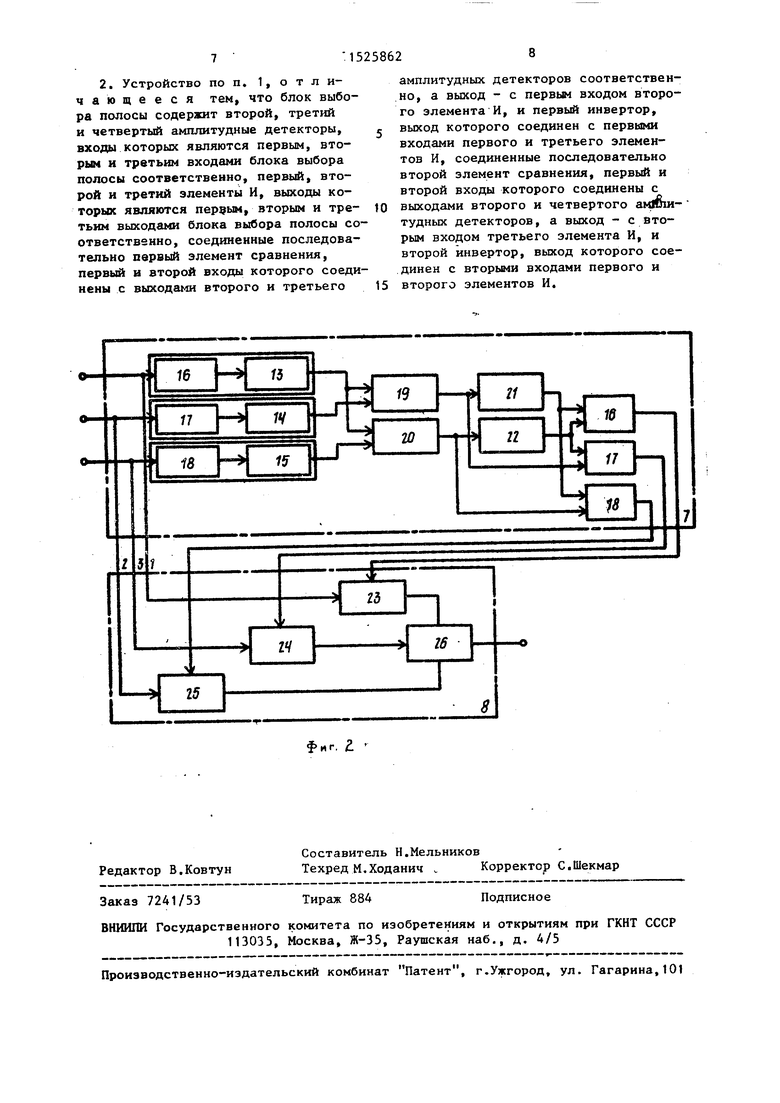

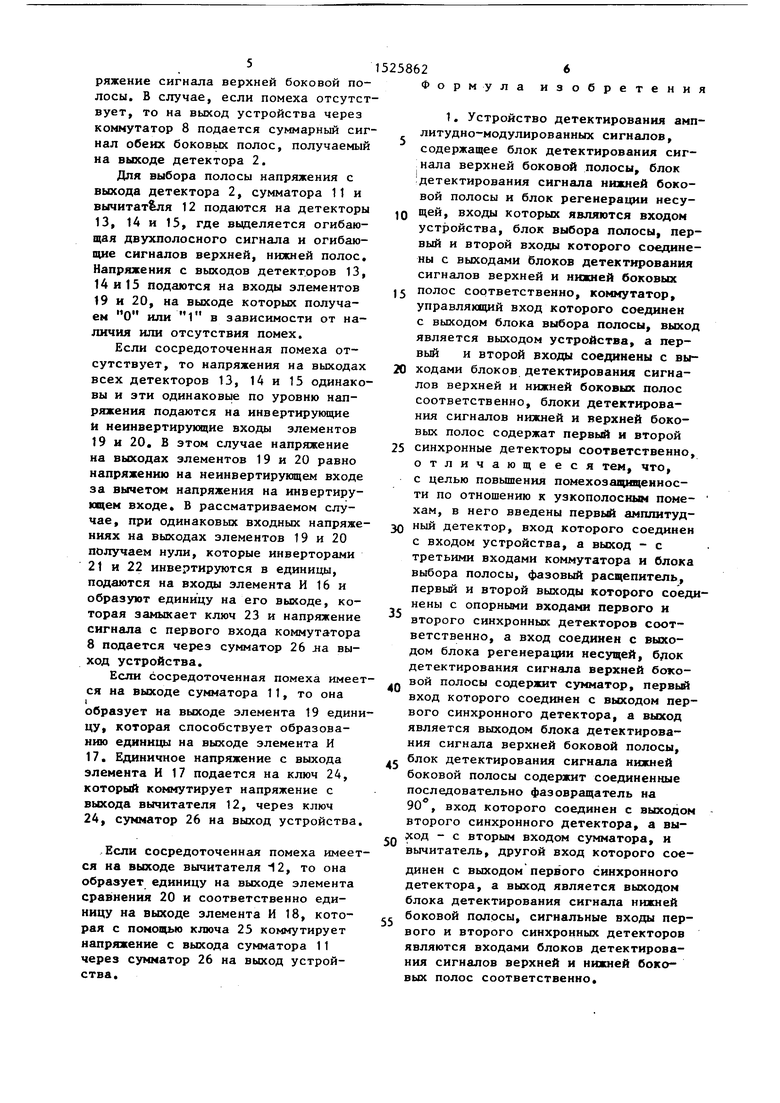

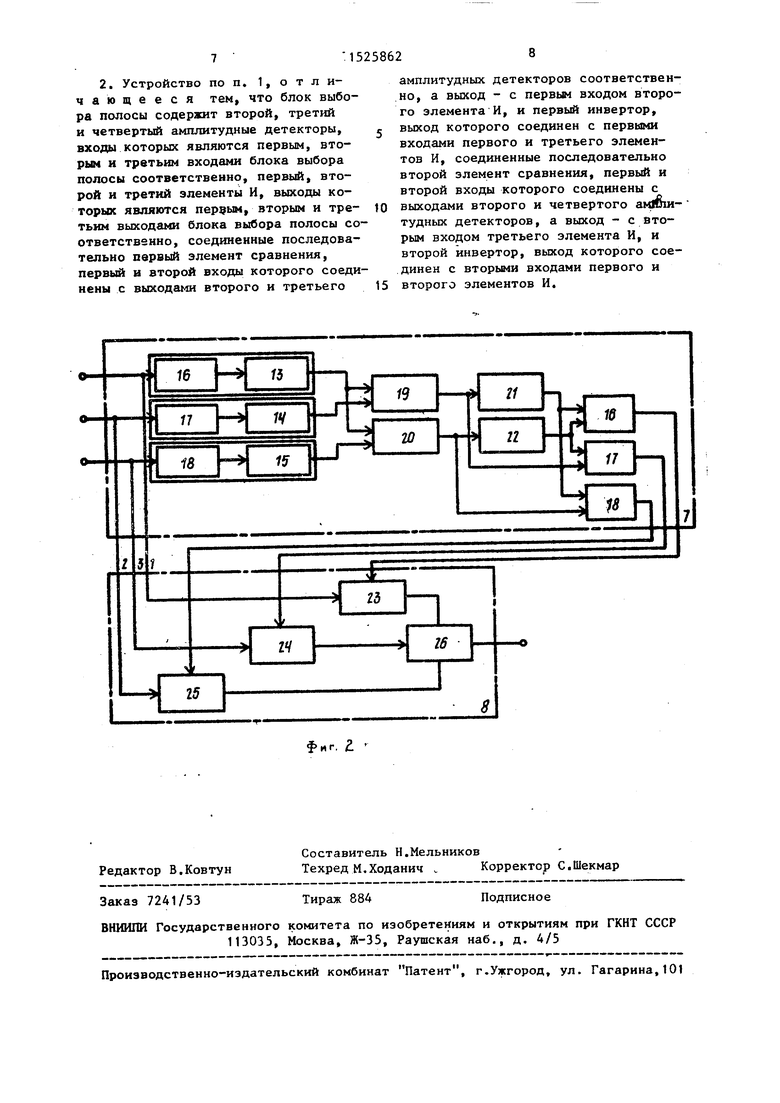

На фиг. 1 представлена структурная электрическая схема устройства детектирования амшштудно-модулиро- ванных сигналов; на фиг. 2 - структурные электрические схемы блока выбора полосы и коммутатора.

Устройство детектирования ампли- тудно-модулированных сигналов содержит блок 1 детектирования сигнала верхней боковой полосы, первый амплитудный детектор 2, первый синхрон- .ный детектор 3, второй синхронный детектор А, блок 5 регенерации несущей, блок 6 детектирования сигналов нижней боковой полосы, блок 7 выбора полосы, коммутатор 8, фазовый расщепитель 9, фазовращатель на УО 10, сумматор 11, вычитатель 12.

Блок 7 выбора полосы содержит второй, третий и четвертый амплитудные детекторы 13, 14 и 15, первый, второй и третий элементы И 16, 17, 1 первый и второй элементы 19 и 20 сравнения, первый и второй инверторы 21 и 22.

Ko Jyтaтop 8 содержит первый, второй и третий ключи 23, 24 и 25 и второй сумматор 26,

Устройство работав следующим образом.

При отсутствии помех напряжение сигнала на входе устройства, которое можно представить в виде

Ug, U,coswet + - U,cos(wo +

Л)1 + 2 U cobCu +аЛ,1, (1)

поступает на детектор 2, первый и второй синхронные детекторы 3 и 4 и на блок 3. В выражении (1) приняты следующие обозначения: U - амплиту- да несущей частоты на выходе устрой- CTBa j Wo несущая частота (круговая); ffij и т„ - коэффициенты модуляции соответственно верхней и нижней боковых полос (обычно га т); ft Jig и лЛ.н полосы низкочастотных модулирующих частот, соответственно верхней и нижней боковых полос (обычно Л-П. ЛЛ(, ),

Блок 5 из суммарного принятого колебания (1) выделяет первое слагаемое и на основе его регенерирует напряжение вида

Uy Ыд+1/ )t, (2)

где Ч - некоторый фазовый сдвиг. Это колебание поступает на вход фазового расщепителя 9 и на его синфазном и квадратурном выходах получим напряжения

Uc Wot 1 и Ui8inii;et 3

которые поступают на первый и второй синхронные детекторы 3 и 4.

На выходе первого синхронного детектора 3 получим

(3)

те

Шн

Uj - U.U cosft/J t + - X

(4)

X СОЬДЛ С .

На выходе второго синхронного детектора 4 имеем

и -4 U,U,8in,t 3 и,и X X sina л. с .(5)

Далее, напряжение (5) подается на фазовращатель 10 на 90, выходное наряжение которого можно записать в виде

и,о 4 и,и,соадл.,1 - ,и х ;с соалл с .(6)

Напряжения (4) и (6) подаются на входы вычитателя 12 и сумматора 11. Напряжение на выходе сумматора 11 можно записать в виде

5 «

Л

U,,UjCoeftA t,(7)

а на выходе вычитателя 12

- з - О- ,UjCosaJljt

(8)

Как видно из выражения (7) и (8), на выходе сумматора 11 блока 1 мы получаем только верхнюю боковую полосу принимаемого сигнала, а на выходе вычитателя 12 блока Ь только нижнюю боковую полосу принимаемого сигнала.

Таким образом, если помехой поражена верхняя боковая полоса принимаемого сигнала, блоком 7 на выход устройства через коммутатор 8 коммутируется напряжение сигнала нижней боковой полосы, Есяи поражена нижняя боковая полоса, то коммутируется напряжение сигнала верхней боковой полосы. В случае, если помеха отсутствует, то на выход устройства через коммутатор 8 подается суммарный сигнал обеих боковых полос, получаемый на выходе детектора 2.

Для выбора полосы напряжения с выхода детектора 2, сумматора 11 и вычитат ля 12 подаются на детекторы 13, 14 и 15, где вьщеляется огибающая двухполосного сигнала и огибаю- пще сигналов верхней, нижней полос. Напряжения с выходов детекторов 13, 14 и 15 подаются на входы элементов 19 и 20, на выходе которых получаем О или 1 в зависимости от наличия или отсутствия помех.

Если сосредоточенная помеха отсутствует, то напряжения на выходах всех детекторов 13, 14 и 15 одинаковы и эти одинаковые по уровню напряжения подаются на инвертирующие И неинвертирукяцие входы элементов 19 и 20. В этом случае напряжение на выходах элементов 19 и 20 равно напряжению на неинвертирующем входе за вычетом напряжения на инвертирующем входе, В рассматриваемом случае, при одинаковых входных напряжениях на выходах элементов 19 и 20 получаем нули, которые инверторами 21 и 22 инвертируются в единицы, подаются на входы элемента И 16 и образуют единицу на его выходе, которая замыкает ключ 23 и напряжение сигнала с первого входа коммутатора 8 подается череэ сумматор 26 ма выход устройства.

Если сосредоточенная помеха имеется на выходе сумматора 11, то она

образует на выходе элемента 19 единицу, которая способствует образованию единицы на выходе элемента И 17. Единичное напряжение с выхода элемента И 17 подается на ключ 24, который коммутирует напряжение с выхода вычитателя 12, через ключ 24, сумматор 26 на выход устройства.

Если сосредоточенная помеха имеется на выходе вычитателя 12, то она образует единицу на выходе элемента сравнения 20 и соответственно единицу на выходе элемента И 18, которая с помощью ключа 25 коммутирует напряжение с выхода сумматора 11 через сумматор 26 на выход устройства.

ормула

6

3 о

бретения

0

5

1. Устройство детектирования амп- литудно-модулированных сигналов, содержащее блок детектирования сигнала верхней боковой полосы, блок детектирования сигнала нижней боковой полосы и блок регенерации несущей, входы которых являются входом устройства, блок выбора полосы, первый и второй входы которого соединены с выходами блоков детектирования сигналов верхней и нижней боковых полос соответственно, коммутатор, управлямощй вход которого соединен с выходом блока выбора полосы, выход является выходом устройства, а первый и второй входы соединены с вы0 ходами блоков детектирования сигналов верхней и нижней боковых полос соответственно, блоки детектирования сигналов нижней и верхней боко- вьк полос содержат первый и второй

5 синхронные детекторы соответственно, отличающееся тем, что, с целью повышения помехозащшценнос- ти по отношению к узкополосным поме- хам, в него введены первый амшштуд0 ный детектор, вход которого соединен с входом устройства, а выход - с третьими входами коммутатора и блока выбора полосы, фазовый расщепитель, первый и второй выходы которого соединены с опорными входами первого и второго синхронных детекторов соответственно, а вход соединен с выходом блока регенерации несущей, детектирования сигнала верхней боковой полосы содержит сумматор, первый вход которого соединен с выходом первого синхронного детектора, а выход является выходом блока детектирования сигнала верхней боковой полосы, блок детектирования сигнала нижней боковой полосы содержит соединенные последовательно фазовращатель на

о

5

0

5

90

, вход которого соединен с выходом

второго синхронного детектора, а выход - с вторым входом сумматора, и вычитатель, другой вход которого соединен с выходом первого синхронного детектора, а выход является выходом блока детектирования сигнала нижней боковой полосы, сигнальные входы первого и второго синхронных детекторов являются входами блоков детектирования сигналов верхней и нижней боковых полос соответственно.

2. Устройство по п. 1, отличающееся тем, что блок выбора полосы содержит второй, третий и четвертый амплитудные детекторы, входы которых являются первым, вторым и третьим входами блока выбора полосы соответственно, первый, второй и третий элементы И, выходы которых являются первым, вторым и третьим выходами блока выбора полосы соответственно, соединенные последовательно первый элемент сравнения, первый и второй входы которого соединены с выходами второго и третьего

амплитудных детекторов соответственно, а выход - с первым входом второго элемента И, и первый инвертор, выход которого соединен с первыми входами первого и третьего элементов И, соединенные последовательно второй элемент сравнения, первый и второй входы которого соединены с выходами второго и четвертого акйбш- тудных детекторов, а выход - с вторым входом третьего элемента И, и второй инвертор, выход которого соединен с вторыми входами первого и второго элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство компенсации помех | 1986 |

|

SU1363488A2 |

| Устройство компенсации помехи | 1981 |

|

SU1083370A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ ДЛЯ ПРИЕМНИКОВ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2001 |

|

RU2205503C2 |

| РАДИОЛИНИЯ СВЯЗИ С ПОВТОРНЫМ ИСПОЛЬЗОВАНИЕМ ЧАСТОТЫ | 2002 |

|

RU2233030C2 |

| УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ ДВУХ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ С ПЕРЕКРЫВАЮЩИМИСЯ СПЕКТРАМИ | 1991 |

|

RU2065666C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ СТРУКТУРНЫХ ПОМЕХ | 2001 |

|

RU2209512C2 |

| Устройство подавления импульсных помех при приеме телевизионных сигналов в системах связи с частотной модуляцией | 1982 |

|

SU1075447A1 |

| Устройство слежения за информационной дорожкой оптического носителя информации | 1990 |

|

SU1777172A1 |

| СПОСОБ КОРРЕЛЯЦИОННОЙ ОБРАБОТКИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2000 |

|

RU2185658C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ШИРОКОПОЛОСНЫХ СИГНАЛОВ ПРИ РАЗНЕСЕННОМ ПРИЕМЕ | 1999 |

|

RU2168272C2 |

Изобретение относится к радиотехнике. Цель изобретения - повышение помехозащищенности по отношению к узкополосным помехам. Устройство содержит блок детектирования 1 сигнала верхней боковой полосы, состоящей из синхронного детектора 3 и сумматора 11, амплитудный детектор 2, блок регенерации 5 несущей, блок детектирования 6 сигнала нижней боковой полосы, состоящий из синхронного детектора 4, фазовращателя 10 на 90° и вычитателя 12, блок выбора 7 полосы, коммутатор 8 и фазовый расщепитель 9. Если помехой поражена верхняя (нижняя) боковая полоса принимаемого сигнала, то блоком выбора 7 на выход устройства через коммутатор 8 коммутируется напряжение сигнала нижней (верхней) боковой полосы. Если помеха отсутствует , то на выход устройства через коммутатор 8 подается суммарный сигнал обеих боковых полос, получаемый на выходе детектора 2. Устройство по п. 2 ф-лы отличается выполнением блока выбора 7. 1 з.п. ф-лы, 2 ил.

. 2.

| Fumeno I., Inone М | |||

| А Sideband Selective receiver. | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Устройство для контактной стыковой сварки оплавлением | 1988 |

|

SU1593834A1 |

Авторы

Даты

1989-11-30—Публикация

1988-01-11—Подача