блока управления, шестой выход которого соединен с управляющим входом блока регистра числа, при этом первые входы корректирующих компараторов соединены с выходом ключа, а вторые входы через опорные фазовращатели соединены с выходом генератора опорного напряжения.

2. Преобразователь по п. 1, о т личающийся тем, что блок управления выполнен на счетчике, дешифраторе, щести триггерах, шести элементах ИЛИ, генераторе импульсов, выход которого соединен с первым входом счетчика, второй вход которого соединен с прямым выходом первого триггера, третий вход - с выходом первого элемента ИЛИ, а выход - с входом дешифратора, первый выход которого соединен с .входом установки второго триггера и входом Сброс третьего триггера, второй и третий выходы - соответственно с входами установки четвертого и пятого триггеров, четвертый выход - с первым ВХОДОМ второго элемента ИЛИ, пятый

выход - с входом установки usecToro триггера, шестой выход - с первыми входами соответственно первого, третьего, четвертого, пятого и шестого элементов ИЛИ, вторые входы всех элементов ИЛИ объединены и соединены с шиной Сброс и входом Сброс первого триггера, причем информационный и тактовый входы первого, второго, третьего, четвертого и пятого триггеров объединены и соединены с общей шиной, прямые выходы второго, третьего, четвертого, пятого и шестого триггеров и инверсный выход второго триггера соединены соответственно с вторым, третьим, четвертым, первым, шестым и пятым вькодами блока управления а входы Сброс второго, четвертого, пятого и Щестого триггеров соединены с выходами соответственно второго, пятого, шестого и третьего элементов ИЛИ, выход четвертого элемента ИЛИ соединен с входом установки третьего триггера, вход установки первого триггера соединен с шиной Пуск.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1985 |

|

SU1297225A1 |

| Адаптивный аналого-цифровой преобразователь | 1986 |

|

SU1311028A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Адаптивное кодирующее устройство | 1983 |

|

SU1166308A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности (его варианты) | 1983 |

|

SU1144189A1 |

| Аналого-цифровой преобразователь с автокоррекцией погрешности | 1983 |

|

SU1091337A1 |

| Преобразователь угла поворота вала в код | 1980 |

|

SU942089A1 |

| Устройство для автоматического измерения погрешности фазовращателя | 1985 |

|

SU1295515A1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1095393A1 |

| Устройство для автоматического измерения погрешностей фазовращателя | 1985 |

|

SU1292179A1 |

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий генератор опорного напряжения, два блока фазовых компараторов,, два шифратора, блок регистра числа, дешифратор, два блока компенсирующего тока, фазовращатель смещения, ключ, блок управления, фазовращатель, первый вход которого соединен с входной шиной, второй вход через первый блок компенсирующего тока соединен с входом второго блока компенсирующего тока и выходом дешифратора, вход которого соединен с первой выходной шиной, третий вход фазовращателя соединен с выходом второго блока компенсирующего тока, четвертый вход - с выходом генератора опорного напряжения, первым входом первого блока фазовых компараторов и входом фазовращателя смещения, а выход с вторым входом первого блока фазовыу компараторов и первым входом ключа, второй вход которого соединен с первым вьгходом блока управления, а выход - с. первым входом второго блока фазовых комч;г1 аторов, второй пход KOTOpoi o соединен с выходом фазовращателя смещения, а выход через последовательно соединенные первый шифратор, блок регистра числа соединен с второй выходной шиной,, выход первого блока фазовых компараторов соединен с входом второго шифратора, отлич а ющий с я тем, что, с целью повышения точности преобразования, в него введены два корректирующих компаратора, два опорных фазовращстеля, три злёмента И, два формирователя импульсов, реверсивный счетчик, выход которого соединен с входом дешифратора, .а первый информационный вход - с выходом второго шифратора,, управляющий вход которого.сое(Л динен с вторым выходом блока управления третий и четвертый выходы которого соединены соответственно с первым и вторым управляющими входами реверсивного счетчика,третий и четвертый управляющие входы которого через первый и второй формирователи :д импульсов соединены соответственно за с выходами первого и второго элементов И, первый вход первого элемента И fC. соединен с первым входом третьего jl эо элемента И и прямым выходом первого корректирующего компаратора; инве:р1сный выход которого соединен с первьм входом второго элемента И, причем второй вход первого элемента И соединен с прямым выходом -второго корректирующего компаратора, инверсный выход которого соединен с вторыми входами второго и третьего элементов И, выход последнего из которых соединен с первым управляющим входом первого шифратора, второй управляющий вход которого соединен с пятыи выходом

.- ...1 , . ,

Изобретение относится к измерительной и вычислительной технике.

Известен аналого-цифровой преобразователь, содержащий (для одного канала) рабочее фазовращающее устройствр, две ступени преобразования (грубую и точную), каждая из которых состоит из последовательно включенных блока пороговых элементов (фазовых компараторов) , дешифратора и бло Kci регистра числа, блок компенсирующего тока, генератор опорного напряжения, блок управления ОЗНедостатком данного преобразоватёдя является большая погрешность преобразования, обусловленная нестабильностью порогов срабатывания фазовых компараторов в грубой и точной ступенях преобразования при воздействии различного рода дестабилизирующих факторов (при изменении окружающей температуры, питающих напряжений, воздействии помех).

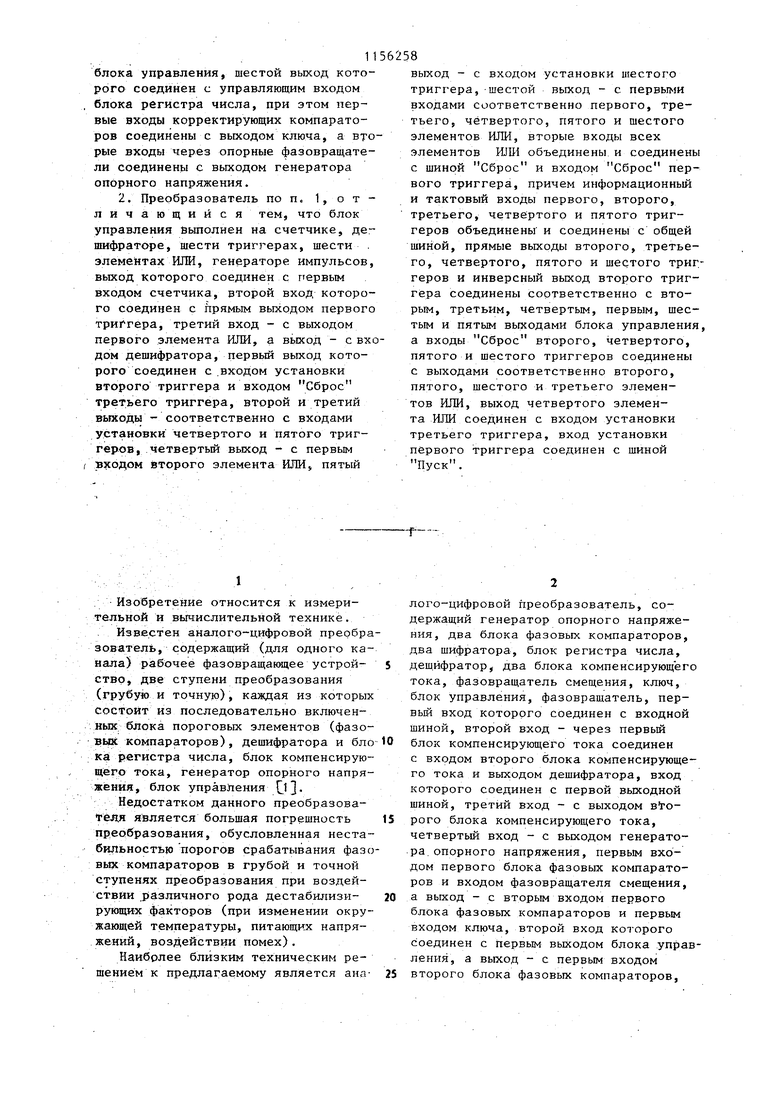

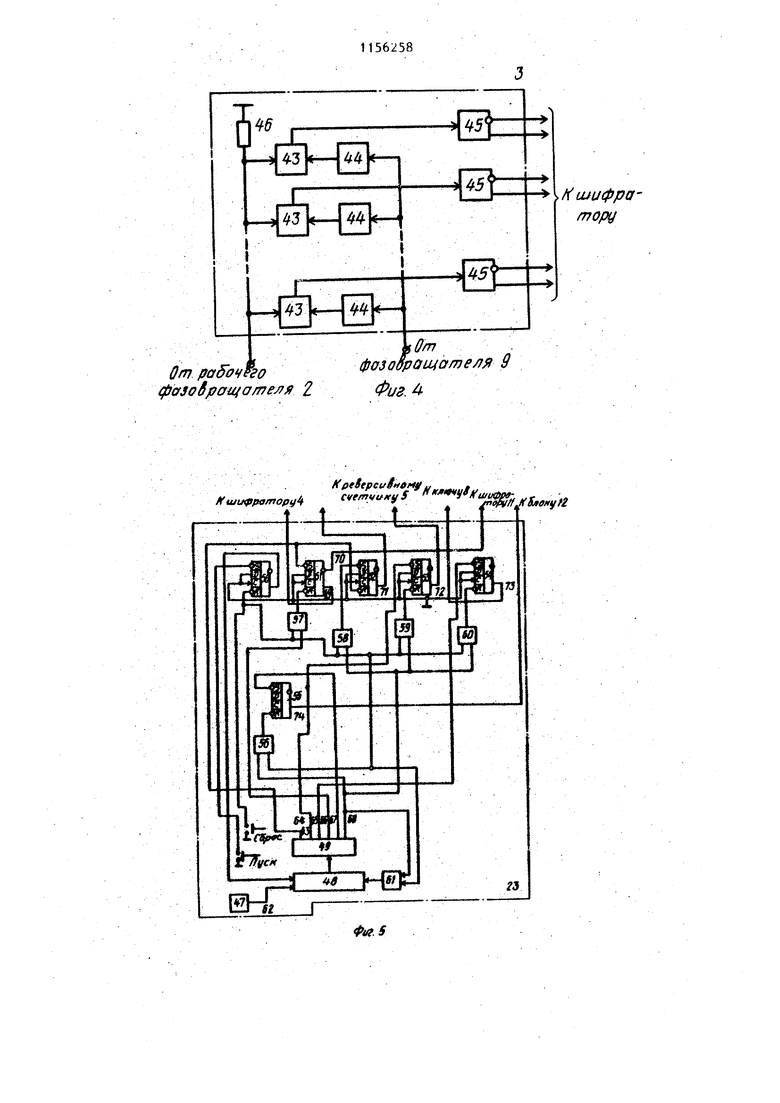

Наиболее близким техническим решением к предлагаемому является аналого-цифровой преобразователь, содержащий генератор опорного напряжения, два блока фазовых компараторов, два шифратора, блок регистра числа, дешифратор, два блока компенсирующег тока, фазовращатель смещения, ключ, блок управления, фазовращатель, первый вход которого соединен с входной шиной, второй вход - через первый блок компенсирующего тока соединен с входом второго блока компенсирующего тока и выходом дешифратора, вход которого соединен с первой выходной шиной, третий вход - с выходом вгорого блока компенсирующего тока, четвертый вход - с выходом генератора, опорного напряжения, первым входом первого блока фазовых компараторов и входом фазовращателя смещения, а выход - с вторым входом первого блока фазовых компараторов и первым входом ключа, второй вход которого соединен с первьм выходом блока упраления, а выход - с первым входом второго блока фазовых компараторов. второй вход которого соединен ходом фазовращателя смещения, а через последовательно соедине ные первый шифратор и первый блок регистра числа соединен с второй вы ходной шиной, причем выход первого блока фазовых компараторов через последовательно соединенные второй шифратор и второй блок регистра чис соединен с входом дешифратора . Недостатком этого преобразовател является низкая точность преобразов ния из-за влияния дестабилизирующих факторов. Цель изобретения - повьшение точ ноети преобразования. Указанная цель достигается тем, что в аналого-цифровой преобразователь, содержащий генератор опорного напряжения, два блока фазовых компараторов, два шифратора, блок регистра числа. Дешифратор, два блокакомпенсирукицего тока, фазовращатель сме щения, ключ, блок управления, фазовращатель, первьй вход которого соединен с .входной шиной, второй вход через первый блок компенсирующего то ка соединен с входом второго блока компенсирующего тока и выходом дешифратора,, вход которого соединен с пе вой выходной шиной, третий вход фазе вращателя соединен с выходом второго блока компенсирующего тока, четверты вход - с выходом генератора опорного напряжения, первым входом первого блока фазовых компараторов и входом фазовращателя смещения, а вых.од с вторым входом первого блока фазовых компараторов и первым входом клю ча, второй вход которого соединен с первым выходом блока управления, а выход - с первым входом второго блока фазовых компараторов, второй вход которого соединен с выходом фазовращателя смещения, а выход через последовательно соединенные первый шифратор, блок регистра числа соединен с второй выходной шиной, выход первого блока фазовых компараторов соединен с входом второго шифратора, введены два корректирующих компарато ра, два опорных фазовращателя, три элемента И, два формирователя импуль сов, реверсивный счетчик, выход кото рого соединен с входом дешифратора, а первый информационньш вход - с выходом второго шифратора, управляющий вход которого соединен с вторым выходом блока управления, третий и четвертый выходы которого соединены соответственно с первым и вторым управляющими входами реверсивного счетчика, третий и четвертый управляющие входы которого через первый и второй формирователи импульсов соединены соответственно с выходами первого и второго элементов И, первый вход первого элемента И соединён с первьп- входом третьего элемента И и прямым выходом первого корректирующего компаратора, инверсный выход которого соединен с первым входом второго элемента И, причем второй вход первого элемента И соединен с прямым выходом второго корректирующего компаратора, инверсный выход которого соединен с вторыми входами второго и третьего элементов И, выход .последнего из которых соединен с первым управляющим входом первого шифратора, второй управляющий вход которого соединен с пятым выходом блока управления, шестой выход которого соединен с управляющим входом блока регистра числа, при этом первые -входы корректирую11и1х компараторов соединены с выходом ключа, а вторые входы через опорные фазовращатели соединены с выходом генератора опорного напряжения. Кроме того, блок управления выполнен на счетчике, дешифраторе, шести триггерах, шести элементах ИЛИ, генераторе импульсов, выход которого соединен с первым входом счетчика, второй вход которого соединен с прямым выходом первого триггера, третий вход - с выходом первого элемента ИЛИ, а вькод - с входом дешифратора, первый выход которого соединен с входом установки второго триггера и входом Сброс третьего триггера, второй и третий выходы - соответственно с входами установки четвертого и пятого триггеров, четвертый выход с первым входом второго элемента ИШ, пятый выход - с входом установки шестого триггера, шестой выход с первыми входами соответственно первого, третьего, четвертого, пятого и шестого элементов ИЛИ, .вторые входы всех элементов ИЛИ объединены и соединены с шиной Сброс и входом Сброс первого триггера, причем информационный и тактовь входы первого второго, третьего, четвертого и пятого триггеров объединены и соединены с общей шиной, прямые выходы второго, третьего, четвертого, пятого и шестого триггеров и инверсный выход второго триггера соединены соответственно с вторым, третьим, четвертым, первым, шестым и пятым выходами блока управления, а входы Сброс второго, четвертого, пятого и шестого триггеров соединены с выходами соответственно второго, пятого, шестого и третьего элементов ИЛИ, выход четвертого элемента ИЛИ соединен с входом установки третьего триггера, вход установки первого триггера соединен с шиной Пуск. На, фиг. 1 изображена структурная электрическая схема преобразователя; на фиг, 2 - временные диаграммы работы преобразователя; на фиг. 3 - струк турная электрическая схема рабочего фазовращателя; на фиг. 4 - сТрукту-рная электрическая схема Злока фазовых компараторов; на фиг.- 5 - структурная электрическая схема блока управления на фиг. 6 - временная диаграмма рабо ты блока управления; на фиг. 7 структурная электрическая схема корректирующего компаратора; на фиг. 8 структурная электрическая схема формирователя импульсов; на фиг. 9 структурная электринеская схема блока компенсирукнцего тока. Преобразователь (фиг. 1) содержит последовательно соединенные генератор 1 опорного напряжения, фазовраща тель 2, блок 3 фазовых компараторов, шифра:тор 4, реверсивный счетчик 5, дешифратор 6, блок 7 компенсирующего тока, ключ 8, последовательно соединенные фазовращатель 9 смещения, блок 10 фазовых компараторов, шифратор 11, блок 12 регистра числа, блок 13 компенсирукмцего тока, формирователи 14 и 15 импульсов, выходы которых соединены с входами счетчика 5 соответственно, элементы И 16 18, корректирующие компараторы 19 и 2Q, инверсные выходы которых соеди нены с входами элемента И 18, опорны фазовращатели 21 и 22, входы которых объединены и подключены к входу фазо вращателя 9, а также содержит блок 23 управления. Корректирующий компаратор 19 имеет прямой 24 и инверсный 25 вьсходы, корректирующий компаратор 20 имеет прямой 26 и инверсньй 27 выходы, элементы И 16 18 имеют вьЕсоды 28 - 30, а формирователи 14 и 15 - выходы 31 и 32. 11 84 На временной диаграмме (фиг. 2) обозначено: напряжения на выходах Z4 32 корректирующих компараторов 19 и 20, элементов И 16 - 18, формирователей 14 и 15. Логические состояния указанных блоков обозначены: сх и 5 - (0,1) логические состояния на выходах 24 и 25, b и Л - на выходах 26 и 27, F «Ъ , F аЪ , .- на выходах 28 - 30. Рабочий фазовращатель 2 (фиг. 3) выполнен на резисторах 33 35, ферромагнитных сердечниках 36 и 37, на которых нанесены рабочие обмотки 38 и 39, управляющая 40 и компенсирующие и 42 обмотки. Блок 3 фазовых компараторов (фиг. 4) выполнен на фазовых компараторах 43, опорных фазовращателях 44, 45, резисторе 46. Триггерах Блок 23 управления (фиг. 5) выполнен на генераторе 47 импульсов, счетчике 48, дешифраторе 49, триггерах 50 - 55, элементах ИЛИ 56 - 61. Генератор 47 имеет выход 62, дешифратор 49 имеет выходы 63 - 68, триггер 51 имеет прямой выход 69, инверсный выход 70, триггеры 52-54 имеют соответственно выходы 71-74. Корректируниций компаратор 19 или 20 (фиг; 7) может быть вьтолнен на коадтЕараторе 75 напряжений,например микросхема 521 СА2, инверторе 76. Формирователь 14 или 15 импульсов (фиг. 8) может быть выполнен на диоде 77, конденсаторе 78, элементах И-НЕ 79 и 80. Источник тока в блоке 7 или 13 компенсирующего тока (фиг. 9) выполнен на транзисторах 8t - 84 и резисторах 85 и 86. В качестве генератора 1 опорного напряжения может быть использован любой генератор гармонических колебаний со стабилизацией амплитуды и частоты его выходного напряжения и с симметричным выходом. . Шифраторы 4 и 11 быть выполнены на основе интегральных микросхем, например 155-й серии. В качестве рев эрсивного счетчика 5 может быть использован реверсивный двоичный счетчик, в котором имеется возможность предварительного занесения информации (например К155 ИЕ7) . Дешифратор 6 может быть выполнен на основе интегральных микросхем, например 155-й серии. Блок 12 регистра числа может быт выполнен на основе триггеров 155-й серии., ншример К155 ТМ2, К155 ТМ7. Элементы И 16 - 18 могут быть выполнены на интегральных микросхемах 155-й серии, например К155 ЛАЗ. i В качестве ключа 8 могут быть использованы мйкросхемь К 143 КТ1, КТ681, КТ682 и др. Преобразователь работает следующим образом. В первом такте при помопщ грубой ступени преобразования происходит определение .w старших разрядов цифрового кода: сигнал с выхода фазовращателя 2 с фазовым сдвигом f , пропордиональньм величине преобразу мого сигнала 3, поступает на первы вход блока 3, В: эависйиостй от вели чины , Ь в блоке 3 срабатывает определенное количество фазовых компара торов, после чего при помощи шифратора 4 происходит формирование двоичного кода « старших разрядов и занесение их в реверсивный счетчик 5. В зависимости от кода получе ных старших разрядов дешифратор 6 или включает, один из блоков-(7 или 13 или выключает оба блока 7 или 13. Если входной сигнал J удовлетворяет соотношению , то включается блок 13, ток которого JK. , складываясь с преобразуемым током Л (сложение .происходит в рабочем фазовращателе 2), образует эквивалентный входной сигнал D , ко торый должен удовлетворять соотношению ,- хт/2+:7хт/2. Если входной сигнал 3- удовлетворяет соотношению -3x1X1/2+ J х + то включается блок 7, ток которого Лх вычитается из входного тока J(вычитание происходит в рабо чем фазовращателе 2); в результате на вход преобразователя воздействуе эквивалентный входной сигнал Лэ2 который должен удовлетворять соотно шению т/2,,./2-../2 Если же входной сигнал Jjf удовле воряет соотношению / Л,,0,/2,/2 то блоки 7 и t3 вьшлючены, поскольку фазовые компараторы в блоке 10 настроены относительно значения ,„/ (середины диапазона изменения преобразуемых сигналов), а включение любого из блоков 7 или 13 осуществ2588ляется для того, чтобы эквивалентный входной сигнал, воздействующий на точную ступень в течение второгс такта преобразования, удовлетворял соотношению (1). Первый корректирукиций компаратор 19 настроен на фазовый сдвиг, соответствующий току хт/2 (середина диапазона изменения преобразуемых сигналов). Состояние его прямого выхода обозначают через «. Настройка второго корректирукнцего компаратора 20 превышает настройку корректи рующего компаратора 19 на величину -хт/ , равную дискретности блока 3. Состояние прямого выхода компаратора 20 обозначают через Ъ. Если уровни срабатывания фазовых компараторов в блоке 3 грубой ступени преобразования не изменились относительно своих номинальных значений, то в течение второго такта преобразования кодируется фазовый сдвиг, которьй соответствует току, удовлетв.оряющему соотношению (1). При этом корректирующий компаратор 19 срабатывает (а 1), а кoppeктиpyюп ий компаратор 20 не срабатывает (). Вследствие этого на выходе элемента И 16 появляется сигнал F аЪ, позволяющий шифратору 11 сформировать двоичный код h-т младших разрядов (п общее количество разрядов преобразователя) . Одновременно на выходах элементов И 17 и 18 будут запрещающие сигналы (у эовень логического нуля) соответственно вследствие чего показания реверсивного счетчика 5 остаются без изменения, поскольку на выходах формирователей 14 (Ф2). и 15 (Ф) отсутствуют импульсы (фиг. 2). Перед началом преобразования оба корректируюш Их компаратора находятся в нулевом состоянии (), что достигается подачей на их вторые входы опорных сигналов с выходов опорных фазовращателей 21 и 22 и подключением первых входов корректирующих компараторов 19 и 20 через резистор 35 на общую шину (резистор 35 находится в блоке 3). Если под влиянием дестабилизирующих факторов уровни срабатьшания фазовых компараторов fi блоке 3 и шифраторе 11 смещаются, например, вверх от своих номинальных значений, то код m старших разрядов, полученньй в течение первого такта преобразования, оказывается меньшим, чем при отсутствии дестабилизирующих факторов. Вследствие этого компенсирующий ток JK вьфабатываемый блоком 7, также уменьшается, а эквивалентный входной ток Зэ , воздействующий на вход преобразователя в течение второго такта преобразования и равный разности 3j - 3, , увеличивается, что приводит к срабатыванию корректи рующего компаратора 20, поэтому , (фиг. 2S) . При этом сигнал на выходе 28 элемента И 16, равный , запрещает шифратору 11 формирование двоичного кода п-т младших разрядов, а комбинация выходных сигналов (на выходе элемента И 17) и (на выходе 30 элемента И 18) создает на выходе 3 формирователя 14 импульс, которьй, поступая на счетный, вход Сложение реверсивного счетчика 5, увеличивает его показания на 1, так что эквивалентный ток Dg, вызывающий фазовый сдвиг выходного напряжения рабочего Фазовращателя 2, подлежащий кодированию в течение второго такта преоб разования, находится в интервале в пределах которого настроены фазовые компарат ры в шифраторе 11. Аналогично можно показать, что при смещении уровней срабатывания фазовых компараторов в блоке 3 и ши фраторе 11 в сторону уменьшения отн сительно их номинальной настройки, эквивалентный ток Эд, равный рази воздействующий на ности Jj(-J вход преобразЬвателя в течение втор го такта преобразования, меньше половины диапазона изменения преобразуемых сигналов. Поэтому с( (ни один из корректирующих компараторов не срабатывает, вследствие че fo на выходе элемента И 18 появляет ся положительный перепад Гз-5Ъ 1, что вызьгаает появление импульса на выходе 32 формирователя 15) фиг. 2i. Это приводит к уменьшению на единицу показаний реверсивного счетчика 5. В результате эквивалент ный ток; ;Jj, воздействующий на вход преобразователя и вызьгоающий фазовы сдвиг выходного напряжения рабочего фазовращателя 2,.подлежащий кодиров нию в течение второго такта, находи ся в нужном интерв.але J /2iJj 3. + кт/2, В пределах которого произв дена настройка фазовых компараторов в шифраторе 11, Режим счета реверсивного счетчика 5 при проведении коррекции обеспечивается подачей импульсов соответствующей полярности на счетные входы + или -. При этом на втором счетном входе в это время должен быть уровень логической 1. Все это обеспечивается введением в состав преобразователя формирователей 14 и 15. Блоки 7 и 13 компенсирующего тока состоят из наборов источников тока. Блок 7 компенсирующего тока содержит m-i., г источников тока (.т - количество двоичных разрядов выходного кода, определяемых в течение первого такта преобразования), величины токов которых образуют арифметическую прогрессию. Например, для в блоке 7 необходимо иметь четьфе источника тока с выходными токами, образующими ряд -о 2Do,, Источник тока (фиг. 9) состоит из генератора тока (транзисторы 81 и 82) и переключателя тока .(транзисторы 83 и 84) . Величина тока определяется питающими на пряжениями F. , F и -резисторами 85 и 86. В зависимости от напряжения, подаваемого на базу транзистора 84 (с выхода д-шифратора 6), ток проходит через транзисторы 84 (источник включен) или 83 (источник выключен) . Блок 13 компенсирующего тока отличается от блока 7 тем, что в своем составе он имеет на один источник тока меньше. Если полярность тока источников в бпоках 7 и 13 одинакова, то компенсирующие обмотки фазовращателя 2, в котором подключены выходы блоков 7 и 13, должны быть намотаны в противоположных направлениях. Рабочий фазовращатель 2 (фиг. 3) состоит из трех резисторов 33 - 35 и реактивного Х сопротивления, включенных по Мостовой схеме. В диагональ АВ подается опорное напряжение с выхода генератора 1. С диагонали СД снимается напряжение, сдвинутое на величину . 4g, относительно входного по закону R - сопротивление резистора 35. В качестве реактивного сопротивления Хр используется управляемая индуктивность, выполненная по схеме простейшего магнитного усилителя: и11562 два ферромагнитных сердечника 36 и 37 с нанесенными на каждом из них рабочими обмотками 38 и 39, включенными встречно. -Управляющая 40 и компенсирующие 41 и 42 обмотки нанесены 5 на оба сердечника вместе. Опорные фазовращатели 21 и 22 отличаются от фазовращателя 2 отсутствием управляющей и компенсирующих обмоток. Их перестройка осуществляется изменением, величины резистора 35 при этом изменяется отношение /Х , а значит и величины фазовых сдвигов их входных напряжений. Фазовращатель 9 смещения отличается от опорных фазовращателей 21 и 22 тем, что имеет симметричный выход (точка Д не заземляется (фиг.З) Структурная схема блока 3 фазовых компараторов (фиг. 4) включает фазовые компараторы 43 (например К521СА2) опорные фазовращатели 44, триггеры 45 для запоминания состояний фазовых компараторов. В зависимости от величины 1/, в блоке 3 (фиг. 4) срабатывает определенное количество компараторов 43, в результате чего в триггерах 45 зафиксируется унитарный код, пропорциональный величине V. Количество компараторов в блоке 3 равно , где m - количество двоичных разрядов выходного кода, определяемых грубой ступенью преобразования. Блок 10 фазовых компараторов точной ступени преобразования отличается от блока 3 лишь величиной настройки фазовых компараторов. В блоке 23 управления применены микросхемы 155-й серии. При нажатии кнопки Пуск начинается подсчет импульсов генератора 47 счетчиком 48 (фиг. 5). Дешифратор 49 выделяет из этой серии 1,3,7,8,9 и 10-й импуль сы на выходах 63 - 68. Первый импульс

устанавливает в 1 триггер 51, фор- Торов, двух опорных фазовра1цателей,

мируя сигнал разрешения на шифратор 4трех элементов И, двух формирователей

и в О - триггер 52, переводя ревер-и реверсивного счетчика, включенных

сивный счетчик 5 из режима хранениясоответствующим образом, повышает

в режнм записи. После записи старшихточность аналого-цифрового преобразоразрядов кода (с выхода шифратора 4) вания. 58 , 12 в реверсивный счетчик 5 третий импульс устанавливает в 1 триггер 53, переводя реверсивный счетчик 5 из режима записи в режим хранения, после чего начинается процесс компенсации сдвига фазы выхбдного напряжения фазовращателя 2. К моменту прихода 7-го импульса на вход счетчика 48 процесс компенсации завершается. Седьмой импульс устанавливается .в 1 триггер 54 ключ 8 открывается, что обеспечивает поступление выходного напряжения фазовращателя 2 с фазовым сдвигом V, пропорциональным току Э , на вход точной ступени преобразования (блок 10, шифратор 11, блок 12). Интервал времени между 7 и 8-ым импульсами, поступакяцими на вход счетчика 48, вьщелен для коррекции результата, полученного в течение первого такта преобразования: в зависимости от состояния корректируюЩих компараторов 19 и 21 показания реверсивного счетчика 5 увеличиваются, уменьшаются или остаются без изменения. Восьмой импульс устанавливает О триггер 51, формируя сигнал разрешения на шифратор Т1 точной ступени преобразования. Девятый импульс устанавливает в 1 триггер 55, в результате чего двоичный код с выхода шифратора 11 (младшие разряды выходного кода) заносится в блок 12. Десятый импульс обеспечивает начальную установку триггеров .50-55, реверсивного счетчика 5 и счетчика 48, а также блока 12, подготавливая преобразователь к следукицему циклу преобразования. Таким образом, введение в преобразователь двух корректирующих компараЪжодФи8. 1

f8

а 2

Ol

, %

-t

5 л

26

(8

271

28 if,

A.

fz

i

t

f , r-

30

1 f if- b i-32 Фз

f 2 д)(од H 5лонд7 Нблог у/

1156258

1,1

-Y

25

o -if

h

27 iB

-Jf Y t

t

29if2

t

3/1SPf

i t

i

. bun,

.

Фиг.З / генератору / f 6ло)(д

От paSof фауодрощоше ZФиг.

KptStpcvttttHjf .f,

tf tuutfpa/noftg

cte/nvuKuS Sffa/tfiafK&MiMyfZ

I i И i И И И 11 И И i И

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальный преобразователь сигналов от термопар и термометров сопротивления | |||

| Приборы и системы управления, 1972, № 8,-с | |||

| Приспособление с иглой для прочистки кухонь типа "Примус" | 1923 |

|

SU40A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU588631A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-05-15—Публикация

1983-04-08—Подача