Изобретение относится к измерительной технике, а именно к устройствам автоматического контроля параметров интегральных стабилизаторов напряжения.

Цель изобретения - повышение точности контроля и быстродействия за счет возможности преобразования малых приращений выходного информативного параметра в форму, удобную для измерения.

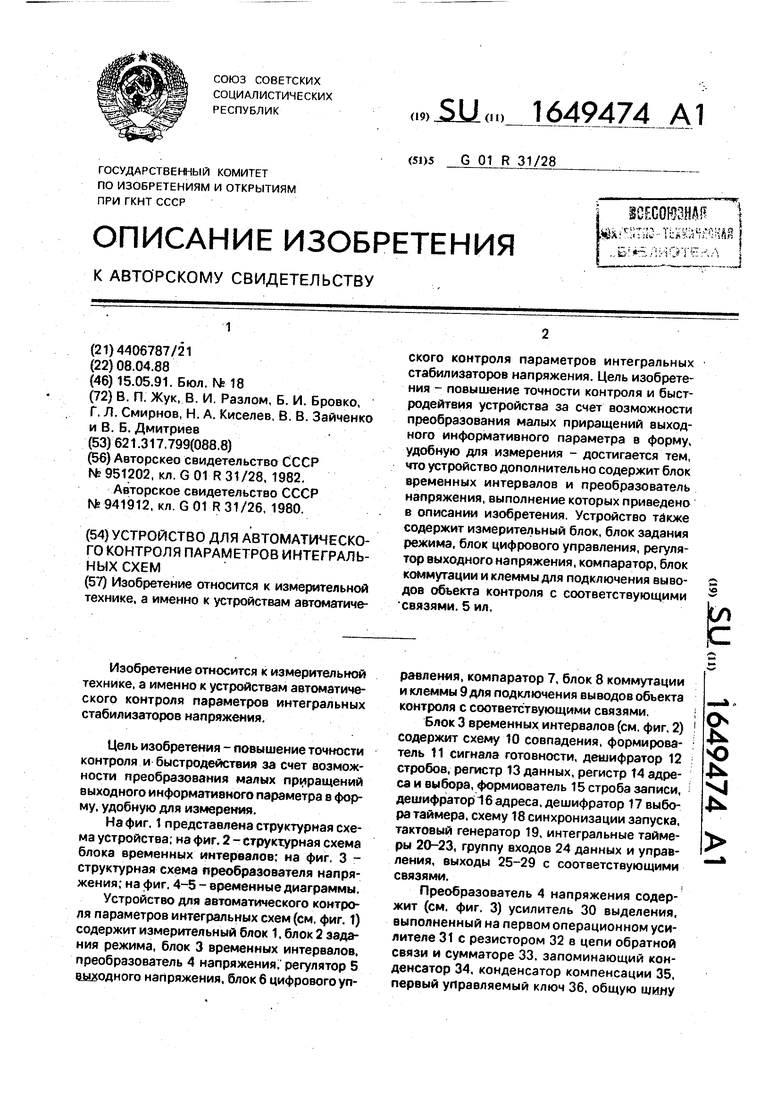

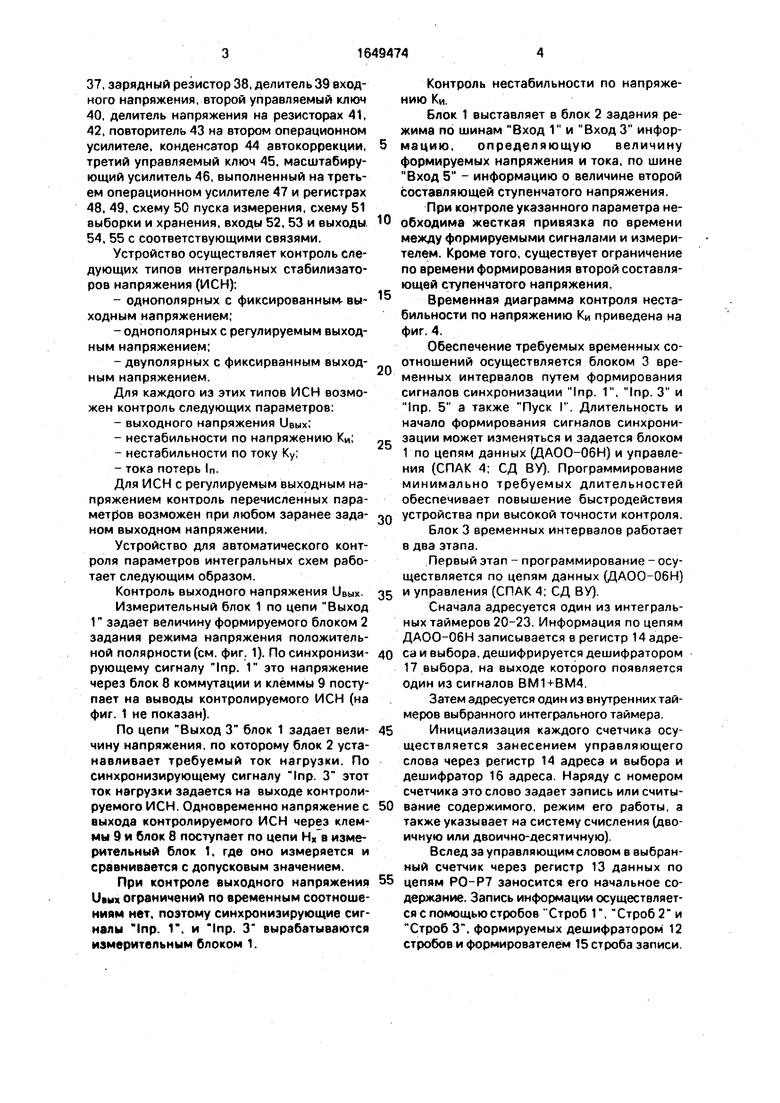

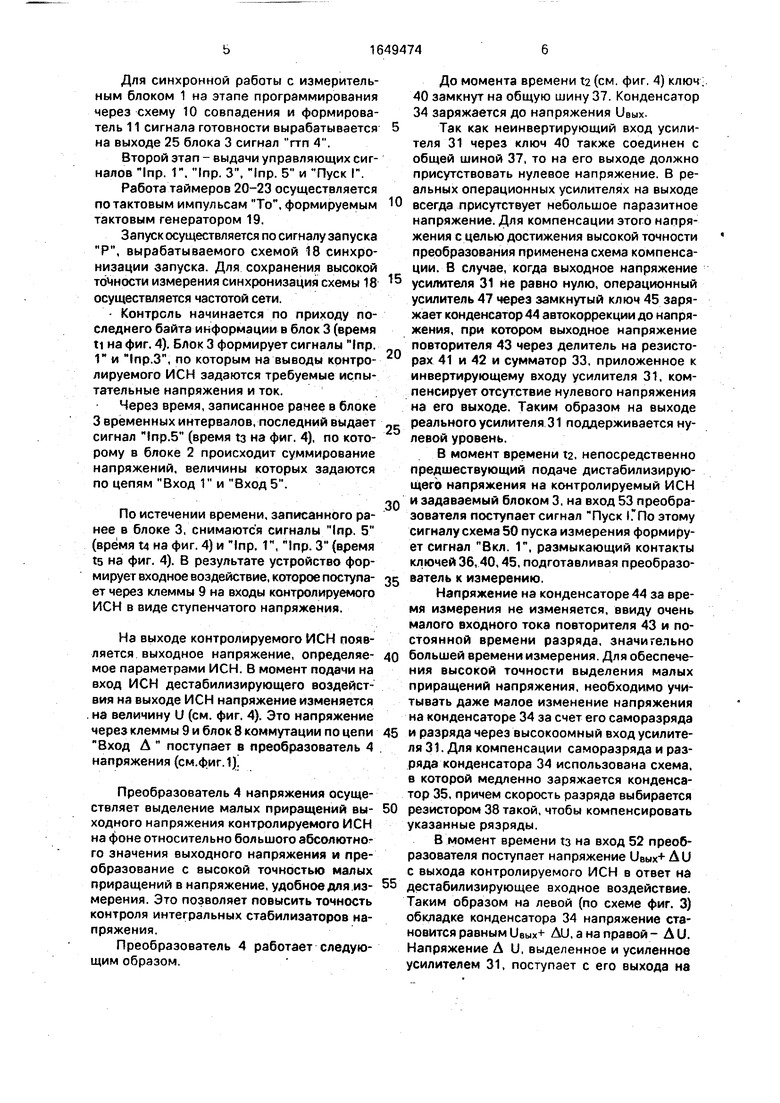

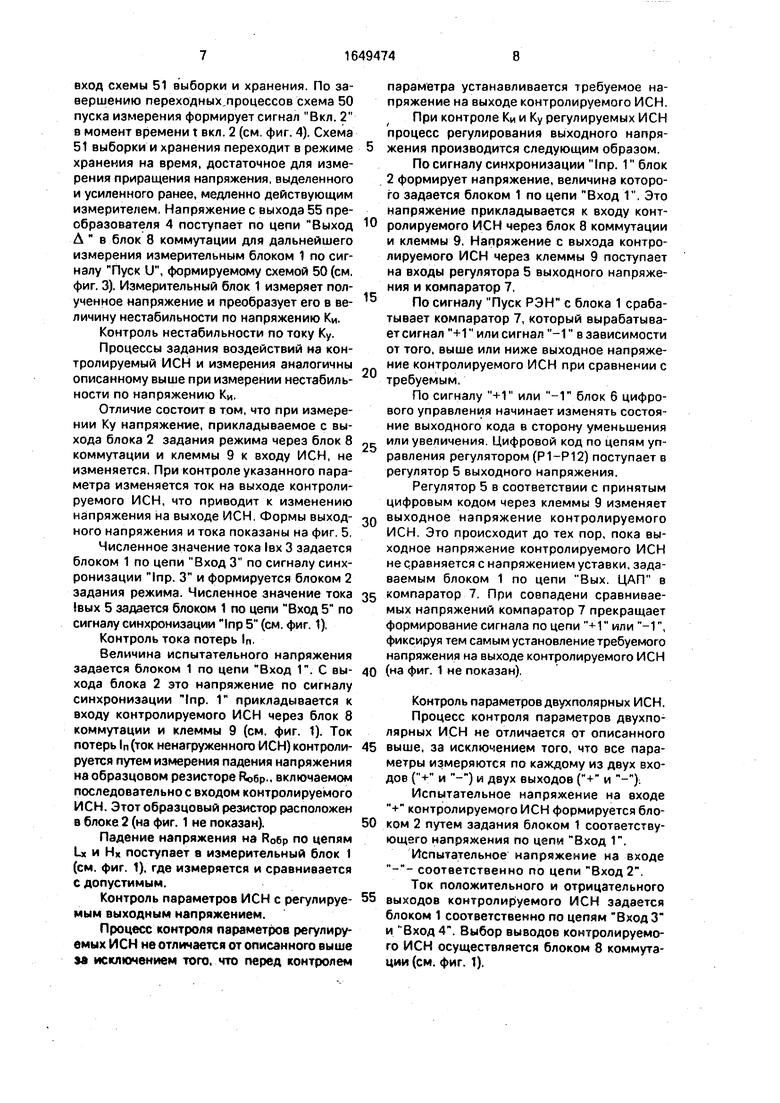

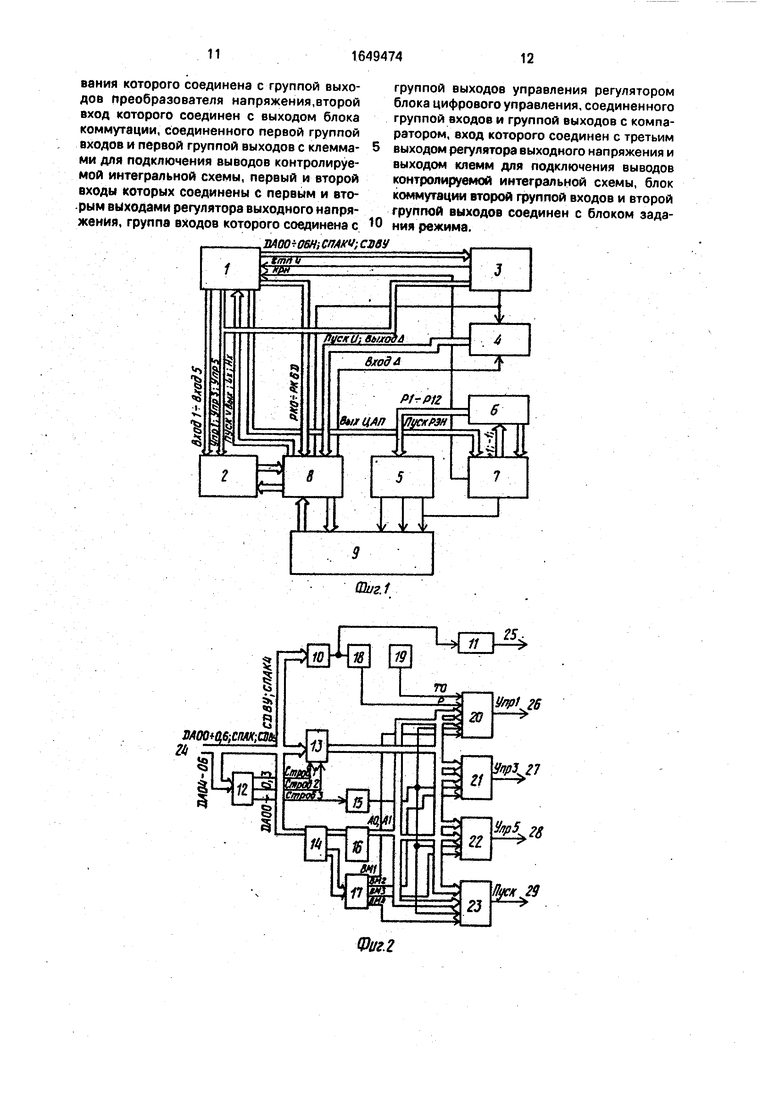

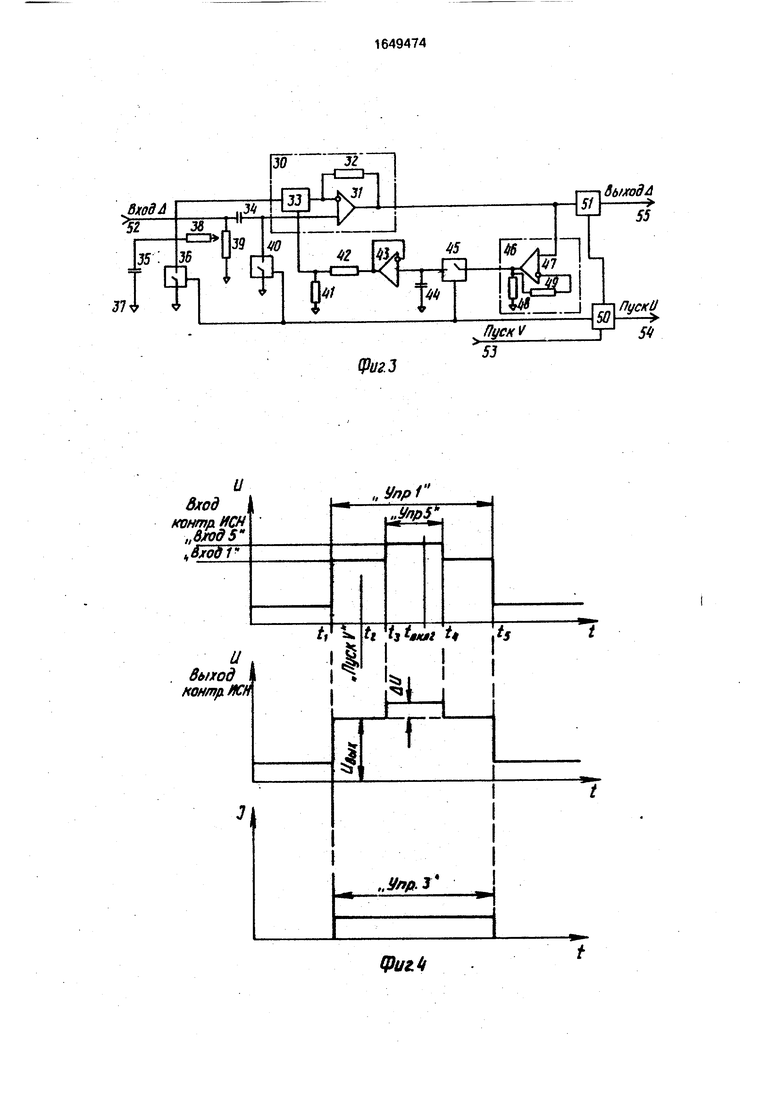

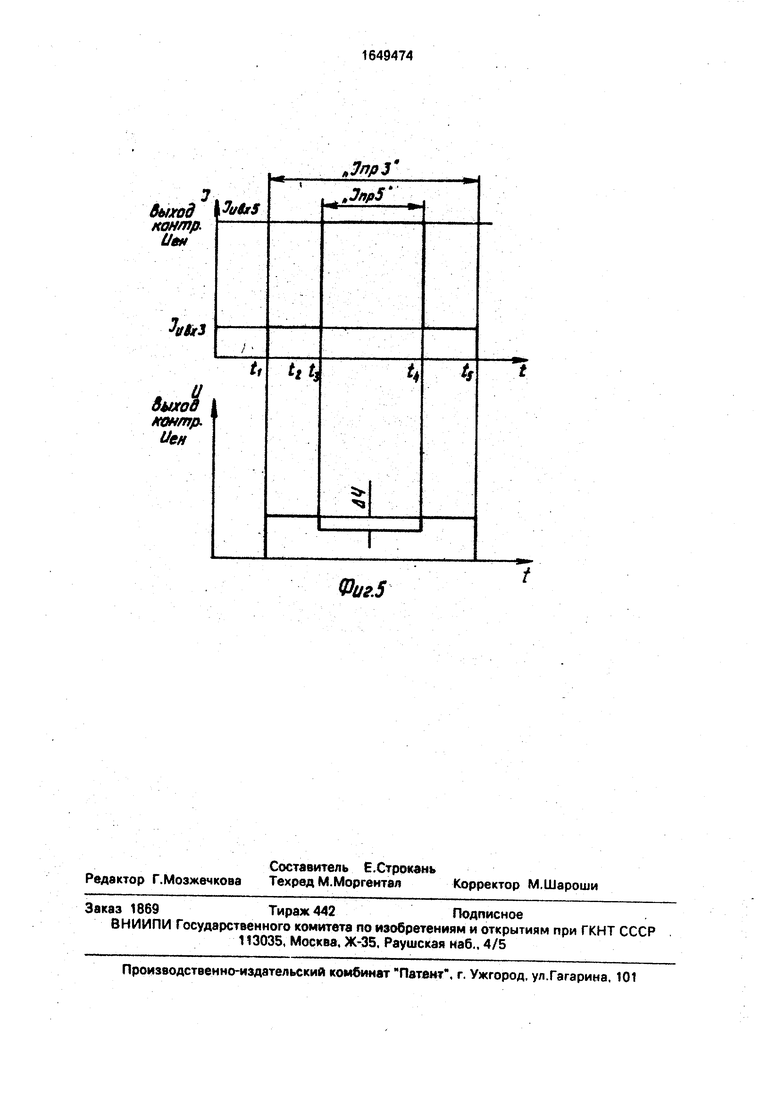

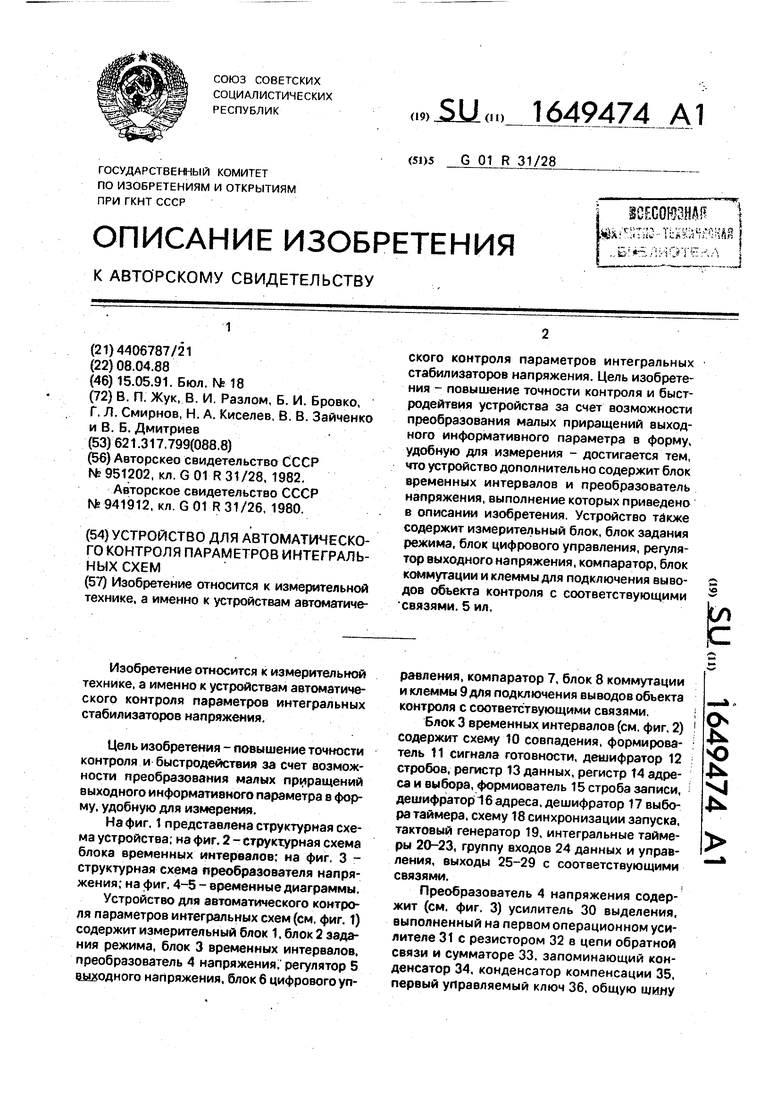

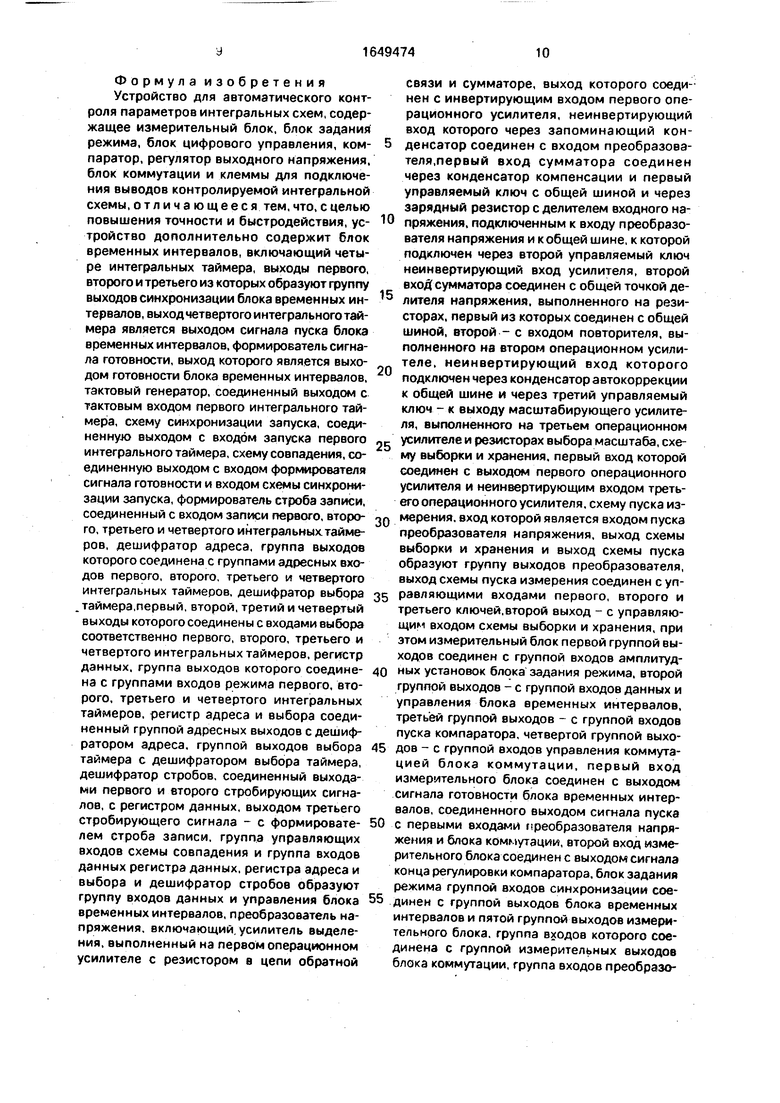

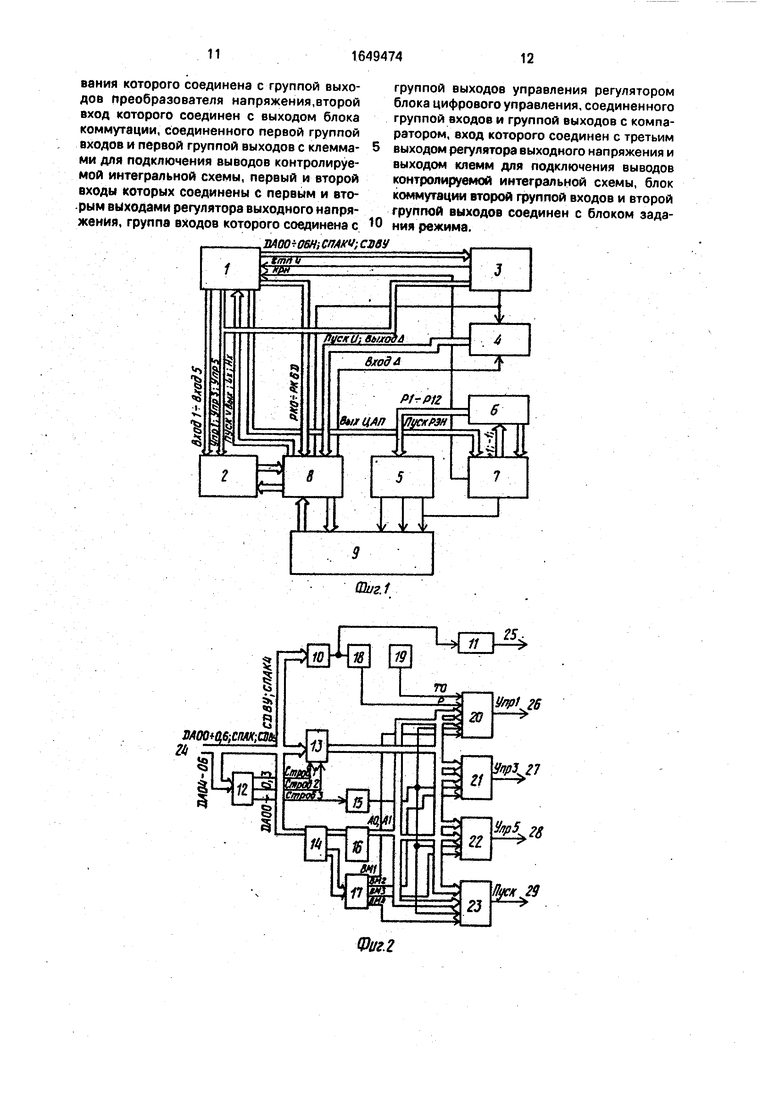

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - структурная схема блока временных интервалов: на фиг. 3 - структурная схема преобразователя напряжения; на фиг. 4-5 - временные диаграммы.

Устройство для автоматического контроля параметров интегральных схем (см. фиг. 1) содержит измерительный блок 1, блок 2 задания режима, блок 3 временных интервалов, преобразователь 4 напряжения,1 регулятор 5 выходного напряжения, блок 6 цифрового управления, компаратор 7, блок 8 коммутации и клеммы 9 для подключения выводов объекта контроля с соответствующими связями,

Блок 3 временных интервалов (см. фиг. 2) содержит схему 10 совпадения, формирователь 11 сигнала готовности, дешифратор 12 стробов, регистр 13 данных, регистр 14 адреса и выбора, формиователь 15 строба записи, дешифратор 16 адреса, дешифратор 17 выбора таймера, схему 18 синхронизации запуска, тактовый генератор 19, интегральные таймеры 20-23, группу входов 24 данных и управления, выходы с соответствующими связями.

Преобразователь 4 напряжения содержит (см. фиг. 3) усилитель 30 выделения, выполненный на первом операционном усилителе 31с резистором 32 в цепи обратной связи и сумматоре 33, запоминающий конденсатор 34. конденсатор компенсации 35, первый управляемый ключ 36, общую щияу

Os Јь

ю

ГЬь

2

37, зарядный резистор 38, делитель 39 входного напряжения, второй управляемый ключ 40, делитель напряжения на резисторах 41, 42, повторитель 43 на втором операционном усилителе, конденсатор 44 автокоррекции, третий управляемый ключ 45. масштабирующий усилитель 46, выполненный на третьем операционном усилителе 47 и регистрах 48, 49, схему 50 пуска измерения, схему 51 выборки и хранения, входы 52, 53 и выходы 54, 55 с соответствующими связями.

Устройство осуществляет контроль следующих типов интегральных стабилизаторов напряжения (ИСН):

-однополярных с фиксированным- выходным напряжением;

-однополярных с регулируемым выходным напряжением;

-двуполярных с фиксирванным выходным напряжением.

Для каждого из этих типов ИСН возможен контроль следующих параметров:

-выходного напряжения Увых;

-нестабильности по напряжению Ки;

-нестабильности по току Ку;

-тока потерь In.

Для ИСН с регулируемым выходным напряжением контроль перечисленных параметров возможен при любом заранее зада- ном выходном напряжении.

Устройство для автоматического контроля параметров интегральных схем работает следующим образом.

Контроль выходного напряжения иВых.

Измерительный блок 1 по цепи Выход 1 задает величину формируемого блоком 2 задания режима напряжения положительной полярности (см. фиг. 1). По синхронизирующему сигналу 1пр. 1 это напряжение через блок 8 коммутации и клеммы 9 поступает на выводы контролируемого ИСН (на фиг. 1 не показан).

По цепи Выход 3я блок 1 задает величину напряжения, по которому блок 2 устанавливает требуемый ток нагрузки. По синхронизирующему сигналу tnp. 3 этот ток нагрузки задается на выходе контролируемого ИСН. Одновременно напряжение с выхода контролируемого ИСН через клеммы 9 и блок 8 поступает по цепи Нх в измерительный блок 1. где оно измеряется и сравнивается с допусковым значением.

При контроле выходного напряжения ограничений по временным соотношениям нет, поэтому синхронизирующие сигналы Inp. 1, и Inp. 3 вырабатываются измерительным блоком 1.

Контроль нестабильности по напряжению Ки.

Блок 1 выставляет в блок 2 задания режима по шинам Вход 1 и Вход 3 инфор- мацию, определяющую величину формируемых напряжения и тока, по шине Вход 5 - информацию о величине второй составляющей ступенчатого напряжения.

При контроле указанного параметра не- обходима жесткая привязка по времени между формируемыми сигналами и измерителем. Кроме того, существует ограничение по времени формирования второй составляющей ступенчатого напряжения.

Временная диаграмма контроля неста

бильности по напряжению Ки приведена на фиг. 4.

Обеспечение требуемых временных соотношений осуществляется блоком 3 временных интервалов путем формирования сигналов синхронизации Inp. 1, Inp. 3 и Inp. 5 а также Пуск I. Длительность и начало формирования сигналов синхрониэации может изменяться и задается блоком 1 по цепям данных (ДАОО-06Н) и управления (СПАК 4; СД ВУ). Программирование минимально требуемых длительностей обеспечивает повышение быстродействия

устройства при высокой точности контроля. Блок 3 временных интервалов работает в два этапа.

Первый этап - программирование - осуществляется по цепям данных (ДАОО-06Н)

и управления (СПАК 4; СД ВУ).

Сначала адресуется один из интегральных таймеров 20-23. Информация по цепям ДАОО-06Н записывается в регистр 14 адреса и выбора, дешифрируется дешифратором 17 выбора, на выходе которого появляется один из сигналов ВМ1+ВМ4.

Затем адресуется один из внутренних таймеров выбранного интегрального таймера.

Инициализация каждого счетчика осуществляется занесением управляющего слова через регистр 14 адреса и выбора и дешифратор 16 адреса. Наряду с номером счетчика это слово задает запись или считывание содержимого, режим его работы, а также указывает на систему счисления (двоичную или двоично-десятичную).

Вслед за управляющим словом в выбранный счетчик через регистр 13 данных по

цепям РО-Р7 заносится его начальное содержание. Запись информации осуществляется с помощью стробов Строб Г,Строб2 и Строб 3. формируемых дешифратором 12 стробов и формирователем 15 строба записи

Для синхронной работы с измерительным блоком 1 на этапе программирования через схему 10 совпадения и формирователь 11 сигнала готовности вырабатывается на выходе 25 блока 3 сигнал пгп 4.

Второй этап - выдачи управляющих сигналов Inp. 1, Inp. 3. Inp. 5 и Пуск Г.

Работа таймеров 20-23 осуществляется по тактовым импульсам То, формируемым тактовым генератором 19.

Запуск осуществляется по сигналу запуска Р, вырабатываемого схемой 18 синхронизации запуска. Для сохранения высокой точности измерения синхронизация схемы 18 осуществляется частотой сети.

Контроль начинается по приходу последнего байта информации в блок 3 (время ti на фиг. 4). Блок 3 формирует сигналы (пр. 1 и 1пр.З, по которым на выводы контролируемого ИСН задаются требуемые испытательные напряжения и ток.

Через время, записанное ранее в блоке 3 временных интервалов, последний выдает сигнал 1пр.5 (время тз на фиг. 4), по которому в блоке 2 происходит суммирование напряжений, величины которых задаются по цепям Вход 1 и Вход 5.

По истечении времени, записанного ранее в блоке 3, снимаются сигналы Inp. 5 (время t4 на фиг. 4) и Inp. Г, 1пр. 3 (время ts на фиг. 4). В результате устройство фор- мируег входное воздействие, которое поступа- ет через клеммы 9 на входы контролируемого ИСН в виде ступенчатого напряжения.

На выходе контролируемого ИСН появляется выходное напряжение, определяв- мое параметрами ИСН. В момент подачи на вход ИСН дестабилизирующего воздействия на выходе ИСН напряжение изменяется на величину U (см. фиг. 4). Это напряжение через клеммы 9 и блок 8 коммутации по цепи Вход Л поступает в преобразователь 4 напряжения (см.фиг.1).

Преобразователь 4 напряжения осуществляет выделение малых приращений вы- ходного напряжения контролируемого ИСН на фоне относительно большого абсолютного значения выходного напряжения и преобразование с высокой точностью малых приращений в напряжение, удобное для из- мерения. Это позволяет повысить точность контроля интегральных стабилизаторов напряжения.

Преобразователь 4 работает следующим образом.

0

0

с

0

5

0 5

0 5

До момента времени ta (см. фиг, 4) ключ. 40 замкнут на общую шину 37. Конденсатор 34 заряжается до напряжения 1)Вых.

Так как неинвертирующий вход усилителя 31 через ключ 40 также соединен с общей шиной 37, то на его выходе должно присутствовать нулевое напряжение. В реальных операционных усилителях на выходе всегда присутствует небольшое паразитное напряжение. Для компенсации этого напряжения с целью достижения высокой точности преобразования применена схема компенсации. В случае, когда выходное напряжение усилителя 31 не равно нулю, операционный усилитель 47 через замкнутый ключ 45 заряжает конденсатор 44 автокоррекции до напряжения, при котором выходное напряжение повторителя 43 через делитель на резисторах 41 и 42 и сумматор 33, приложенное к инвертирующему входу усилителя 31. компенсирует отсутствие нулевого напряжения на его выходе. Таким образом на выходе реального усилителя 31 поддерживается нулевой уровень.

В момент времени ta, непосредственно предшествующий подаче дистабилизирую- щего напряжения на контролируемый ИСН и задаваемый блоком 3, на вход 53 преобразователя поступает сигнал Пуск 1.По этому сигналу схема 50 пуска измерения формирует сигнал Вкл. 1, размыкающий контакты ключей 36,40,45, подготавливая преобразователь к измерению.

Напряжение на конденсаторе 44 за время измерения не изменяется, ввиду очень малого входного тока повторителя 43 и постоянной времени разряда, значительно большей времени измерения. Для обеспечения высокой точности выделения малых приращений напряжения, необходимо учитывать даже малое изменение напряжения на конденсаторе 34 за счет его саморазряда и разряда через высокоомный вход усилителя 31. Для компенсации саморазряда и разряда конденсатора 34 использована схема, в которой медленно заряжается конденсатор 35, причем скорость разряда выбирается резистором 38 такой, чтобы компенсировать указанные рязряды.

В момент времени ta на вход 52 преобразователя поступает напряжение 11вых+ AU с выхода контролируемого ИСН в ответ на дестабилизирующее входное воздействие. Таким образом на левой (по схеме фиг. 3) обкладке конденсатора 34 напряжение становится равнымивых+ Аи. а на правой- AU. Напряжение A U, выделенное и усиленное усилителем 31, поступает с его выхода на

вход схемы 51 выборки и хранения. По завершению переходных„процессов схема 50 пуска измерения формирует сигнал Вкл. 2 в момент времени t вкл. 2 (см. фиг. 4). Схема 51 выборки и хранения переходит в режиме хранения на время, достаточное для измерения приращения напряжения, выделенного и усиленного ранее, медленно действующим измерителем. Напряжение с выхода 55 преобразователя 4 поступает по цепи Выход Д в блок 8 коммутации для дальнейшего измерения измерительным блоком 1 по сигналу Пуск U, формируемому схемой 50 (см, фиг. 3). Измерительный блок 1 измеряет полученное напряжение и преобразует его в величину нестабильности по напряжению Ки. Контроль нестабильности по току Ку. Процессы задания воздействий на контролируемый ИСН и измерения аналогичны описанному выше при измерении нестабильности по напряжению Ки.

Отличие состоит в том, что при измерении Ку напряжение, прикладываемое с выхода блока 2 задания режима через блок 8 коммутации и клеммы 9 к входу ИСН, не изменяется. При контроле указанного параметра изменяется ток на выходе контролируемого ИСН, что приводит к изменению напряжения на выходе ИСН. Формы выходного напряжения и тока показаны на фиг. 5, Численное значение тока (вх 3 задается блоком 1 по цепи Вход 3 по сигналу синхронизации Inp. 3 и формируется блоком 2 задания режима. Численное значение тока вых 5 задается блоком 1 по цепи Вход 5 по сигналу синхронизации 1пр 5 (см. фиг. 1), Контроль тока потерь п. Величина испытательного напряжения задается блоком 1 по цепи Вход Г. С выхода блока 2 это напряжение по сигналу синхронизации Чпр. 1 прикладывается к входу контролируемого ИСН через блок 8 коммутации и клеммы 9 (см. фиг. 1). Ток потерь 1П (ток ненафуженного ИСН) контролируется путем измерения падения напряжения на образцовом резисторе Rc6p. включаемом последовательно с входом контролируемого ИСН. Этот образцовый резистор расположен в блоке 2 (на фиг. 1 не показан).

Падение напряжения на Нобр по цепям U и Нх поступает в измерительный блок 1 (см. фиг. 1). где измеряется и сравнивается с допустимым.

Контроль параметров ИСН с регулируемым выходным напряжением.

Процесс контроля параметров регулируемых ИСН не отличается от описанного выше м исключением того, что перед контролем

параметра устанавливается требуемое напряжение на выходе контролируемого ИСН. При контроле Ки и Ку регулируемых ИСН процесс регулирования выходного напряжения производится следующим образом.

По сигналу синхронизации Inp. 1 блок 2 формирует напряжение, величина которого задается блоком 1 по цепи Вход 1, Это напряжение прикладывается к входу контролируемого ИСН через блок 8 коммутации и клеммы 9. Напряжение с выхода контролируемого ИСН через клеммы 9 поступает на входы регулятора 5 выходного напряжения и компаратор 7.

По сигналу Пуск РЭН с блока 1 сраба

тывает компаратор 7, который вырабатывает сигнал сигнал -1 в зависимости от того, выше или ниже выходное напряжение контролируемого ИСН при сравнении с требуемым.

По сигналу +1 или -1 блок 6 цифрового управления начинает изменять состояние выходного кода в сторону уменьшения

или увеличения. Цифровой код по цепям управления регулятором (Р1-Р12) поступает в регулятор 5 выходного напряжения.

Регулятор 5 в соответствии с принятым цифровым кодом через клеммы 9 изменяет

выходное напряжение контролируемого ИСН. Это происходит до тех пор, пока выходное напряжение контролируемого ИСН не сравняется с напряжением уставки, задаваемым блоком 1 по цепи Вых. ЦАП в

компаратор 7. При совпадени сравниваемых напряжений компаратор 7 прекращает формирование сигнала по цепи +1 или -1, фиксируя тем самым установление требуемого напряжения на выходе контролируемого ИСН

(на Фиг- 1 не показан).

Контроль параметров двухполярных ИСН,

Процесс контроля параметров двухполярных ИСН не отличается от описанного выше, за исключением того, что все параметры измеряются по каждому из двух входов и -) и двух выходов (+ и -).

Испытательное напряжение на входе + контролируемого ИСН формируется бло- ком 2 путем задания блоком 1 соответствующего напряжения по цепи Вход 1.

Испытательное напряжение на входе соответственно по цепи Вход 2.

Ток положительного и отрицательного выходов контролируемого ИСН задается блоком 1 соответственно по цепям Вход 3 и Вход 4. Выбор выводов контролируемого ИСН осуществляется блоком 8 коммутации (см. фиг. 1).

Формула изобретения Устройство для автоматического контроля параметров интегральных схем, содержащее измерительный блок, блок задания режима, блок цифрового управления, компаратор, регулятор выходного напряжения, блок коммутации и клеммы для подключения выводов контролируемой интегральной схемы, отличающееся тем, что, с целью повышения точности и быстродействия, устройство дополнительно содержит блок временных интервалов, включающий четыре интегральных таймера, выходы первого, второго и третьего из которых образуют группу выходов синхронизации блока временных интервалов, выход четвертого интегрального таймера является выходом сигнала пуска блока временных интервалов, формирователь сигнала готовности, выход которого является выходом готовности блока временных интервалов, тактовый генератор, соединенный выходом с тактовым входом первого интегрального таймера, схему синхронизации запуска, соединенную выходом с входом запуска первого интегрального таймера, схему совпадения, соединенную выходом с входом формирователя сигнала готовности и входом схемы синхронизации запуска, формирователь строба записи, соединенный с входом записи первого, второго, третьего и четвертого интегральных таймеров, дешифратор адреса, группа выходов которого соединена с группами адресных входов первого, второго, третьего и четвертого интегральных таймеров, дешифратор выбора . таймера.первый, второй, третий и четвертый выходы которого соединены с входами выбора соответственно первого, второго, третьего и четвертого интегральных таймеров, регистр данных, группа выходов которого соединена с группами входов режима первого, второго, третьего и четвертого интегральных таймеров, регистр адреса и выбора соединенный группой адресных выходов с дешифратором адреса, группой выходов выбора таймера с дешифратором выбора таймера, дешифратор стробов, соединенный выходами первого и второго стробирующих сигналов, с регистром данных, выходом третьего стробирующего сигнала - с формирователем строба записи, группа управляющих входов схемы совпадения и группа входов данных регистра данных, регистра адреса и выбора и дешифратор стробов образуют группу входов данных и управления блока временных интервалов, преобразователь напряжения, включающий усилитель выделения, выполненный на первом операционном усилителе с резистором в цепи обратной

связи и сумматоре, выход которого соединен с инвертирующим входом первого операционного усилителя, неинвертирующий вход которого через запоминающий конденсатор соединен с входом преобразователя,первый вход сумматора соединен через конденсатор компенсации и первый управляемый ключ с общей шиной и через зарядный резистор с делителем входного напряжения, подключенным к входу преобразователя напряжения и к общей шине, к которой подключен через второй управляемый ключ неинвертирующий вход усилителя, второй вхоД сумматора соединен с общей точкой де

лителя напряжения, выполненного на рези

сторах, первый из которых соединен с общей шиной, второй - с входом повторителя, выполненного на втором операционном усилителе, неинвертирующий вход которого подключен через конденсатор автокоррекции к общей шине и через третий управляемый ключ - к выходу масштабирующего усилителя, выполненного на третьем операционном

усилителе и резисторах выбора масштаба, схему выборки и хранения, первый вход которой соединен с выходом первого операционного усилителя и неинвертирующим входом третьего операционного усилителя, схему пуска мзмерения, вход которой является входом пуска преобразователя напряжения, выход схемы выборки и хранения и выход схемы пуска образуют группу выходов преобразователя, выход схемы пуска измерения соединен с управляющими входами первого, второго и третьего ключей.второй выход - с управляющим входом схемы выборки и хранения, при этом измерительный блок первой группой выходов соединен с группой входов амплитудных установок блока задания режима, второй группой выходов - с группой входов данных и управления блока временных интервалов, третьей группой выходов - с группой входов пуска компаратора, четвертой группой выходов - с группой входов управления коммутацией блока коммутации, первый вход измерительного блока соединен с выходом сигнала готовности блока временных интервалов, соединенного выходом сигнала пуска

с первыми входами преобразователя напряжения и блока коммутации, второй вход измерительного блока соединен с выходом сигнала конца регулировки компаратора, блок задания режима группой входов синхронизации соедимен с группой выходов блока временных интервалов и пятой группой выходов измерительного блока, группа входов которого соединена с группой измерительных выходов блока коммутации, группа входов преобразоввния которого соединена с группой выходов преобразователя напряжения,второй вход которого соединен с выходом блока коммутации, соединенного первой группой входов и первой группой выходов с клеммами для подключения выводов контролируемой интегральной схемы, первый и второй входы которых соединены с первым и вторым выходами регулятора выходного напряжения, группа входов которого соединена с

0

группой выходов управления регулятором блока цифрового управления, соединенного группой входов и группой выходов с компаратором, вход которого соединен с третьим выходом регулятора выходного напряжения и выходом клемм для подключения выводов контролируемой интегральной схемы, блок коммутации второй группой входов и второй группой выходов соединен с блоком задания режима.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| Устройство для контроля параметров электронных блоков | 1987 |

|

SU1471156A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| СПОСОБ ЭЛЕКТРОЕМКОСТНОЙ ВЛАГОМЕТРИИ ВОДОНЕФТЯНЫХ ЭМУЛЬСИЙ В ПОТОКЕ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2383885C1 |

| Многопостовое устройство для контроля параметров электронных схем | 1983 |

|

SU1108374A1 |

| Устройство для автоматического контроля интегральных схем | 1986 |

|

SU1401418A2 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для контроля суточных графиков электрических нагрузок | 1986 |

|

SU1336036A1 |

| Устройство для автоматизированного контроля источников питания | 1986 |

|

SU1366978A1 |

Изобретение относится к измерительной технике, а именно к устройствам автоматического контроля параметров интегральных стабилизаторов напряжения. Цель изобретения - повышение точности контроля и быст- родейтвия устройства за счет возможности преобразования малых приращений выходного информативного параметра в форму, удобную для измерения - достигается тем, что устройство дополнительно содержит блок временных интервалов и преобразователь напряжения, выполнение которых приведено в описании изобретения. Устройство тёкже содержит измерительный блок, блок задания режима, блок цифрового управления, регулятор выходного напряжения, компаратор, блок коммутации и к леммы для подключения выводов объекта контроля с соответствующими связями. 5 ил. W Ё

t&

№РЫ7

Ш4

29

f

2w3

Фиг.5

| Устройство для контроля параметров полупроводникового стабилизатора напряжения | 1980 |

|

SU951202A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения параметров линейных интегральных стабилизаторов напряжения | 1980 |

|

SU941912A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-15—Публикация

1988-04-08—Подача