#9 ггел

00 Јъ 4Ь 00 СП

Изобретение относится к электротехнике, в частности к цифровым регуляторам трехфазного напряжения, и может найти применение в цепях питания радиотехнических устройств с повышенными требованиями к качеству выходного напряжения, а также в различных технологических установках с из- мененяемым по требуемому закону выходными параметрами.

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности стабилизации трехфазного напряжения при минимальных аппаратных затратах.

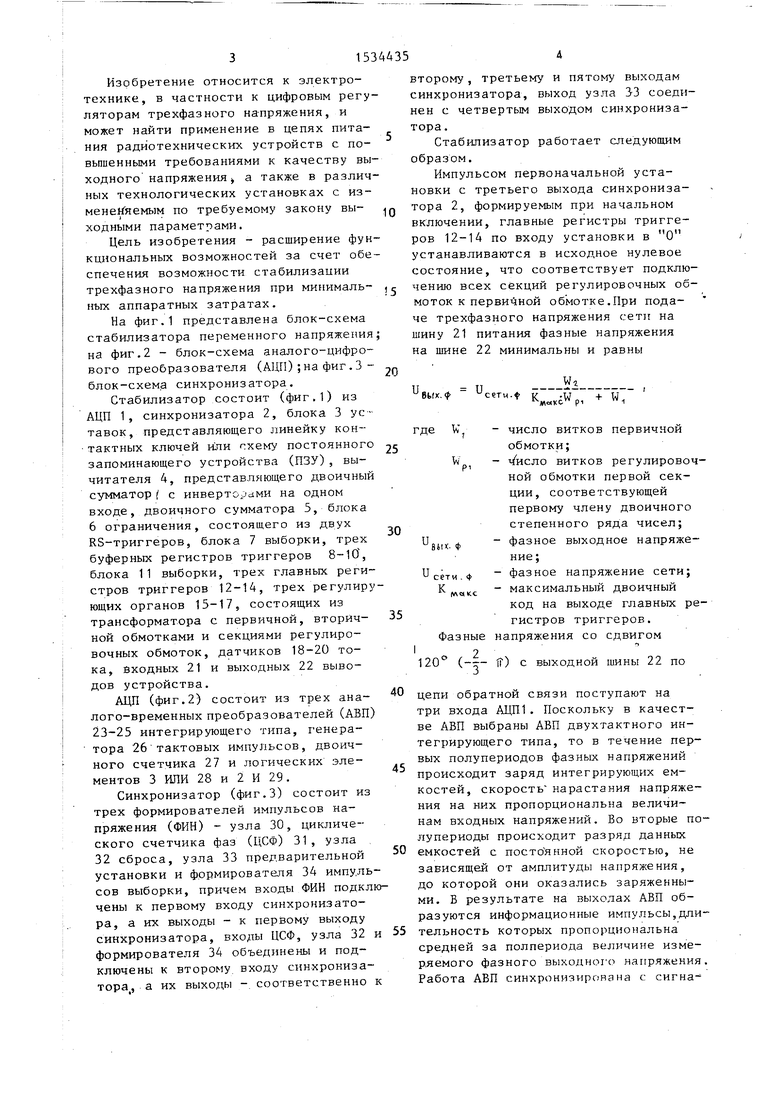

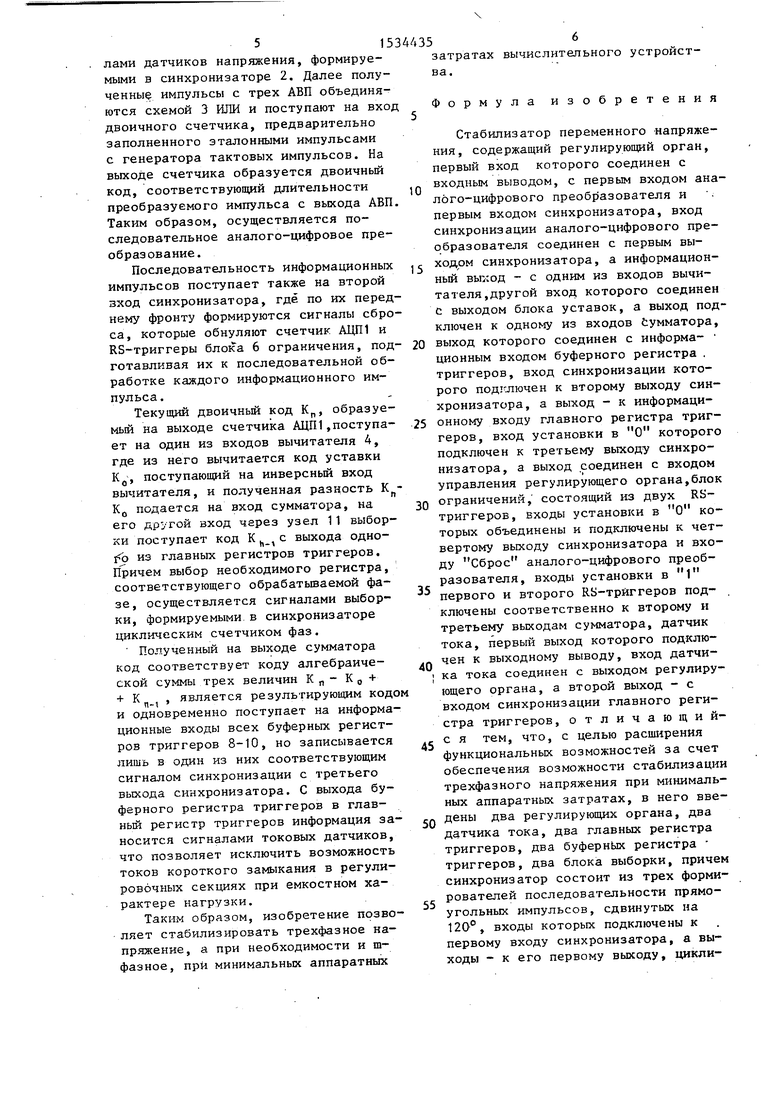

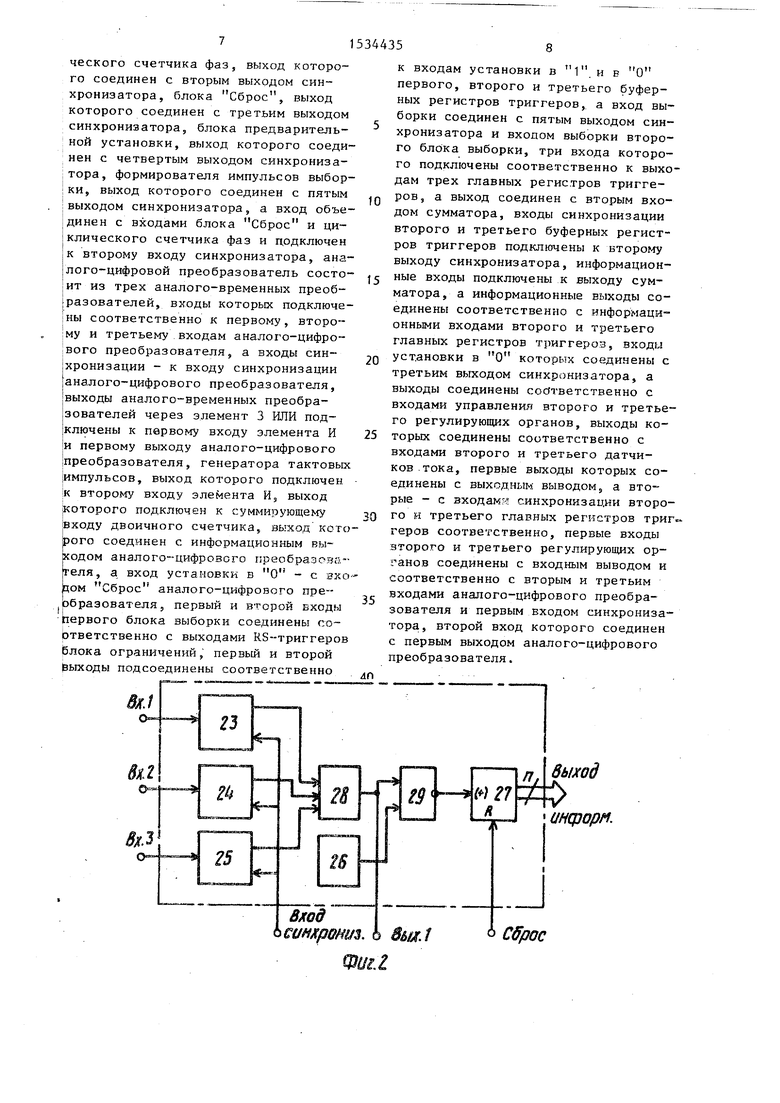

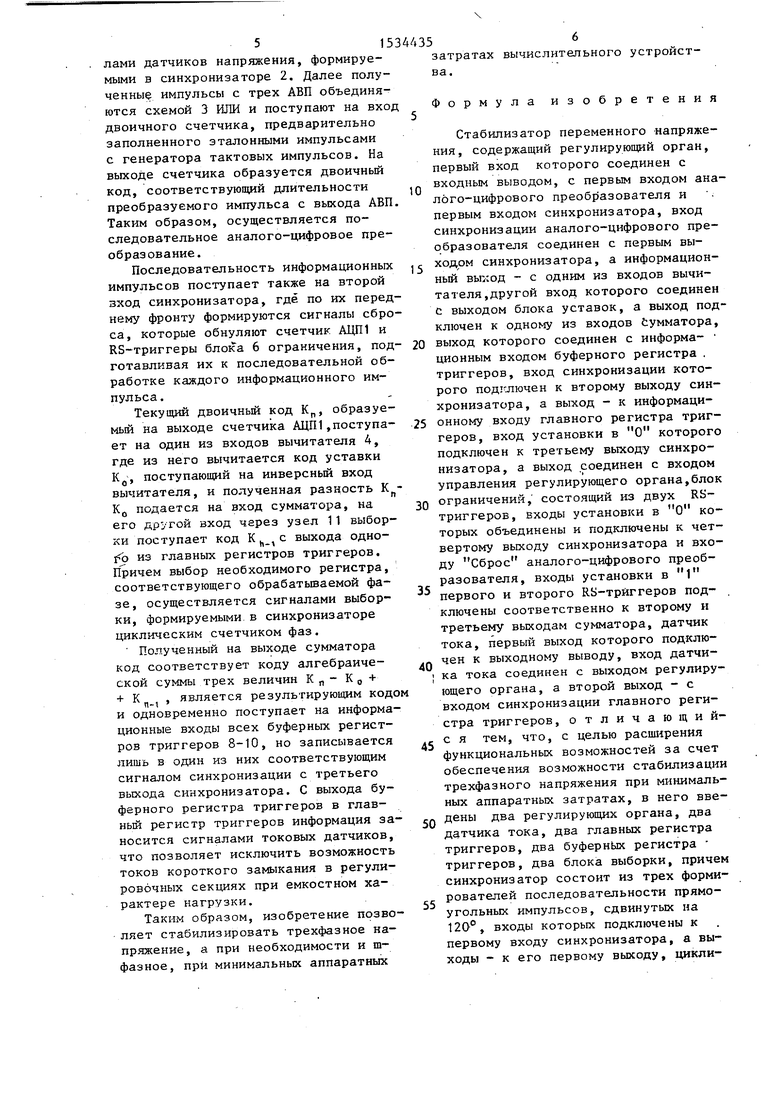

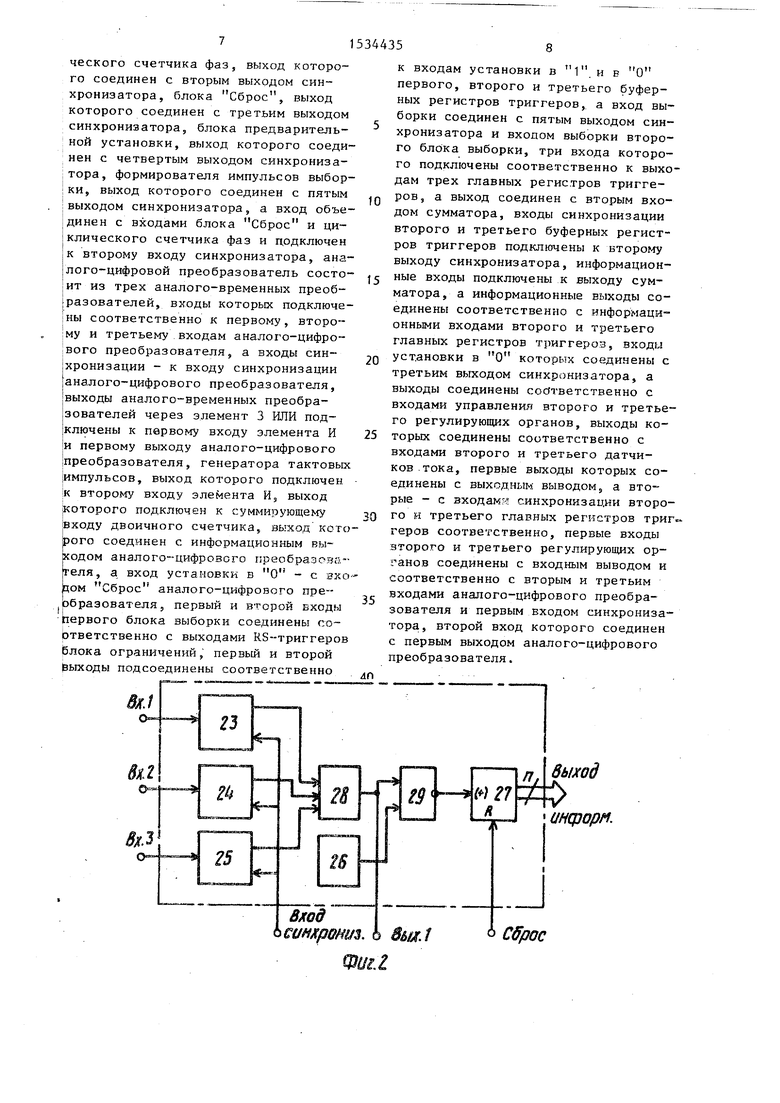

На фиг.1 представлена блок-схема стабилизатора переменного напряжения на фиг.2 - блок-схема аналого-цифрового преобразователя (АЦП);на фиг. 3 - блок-схема синхронизатора.

Стабилизатор состоит (фиг.1) из АЦП 1, синхронизатора 2, блока 3 уставок, представляющего линейку контактных ключей или гхему постоянного запоминающего устройства (ПЗУ), вы- читателя 4, представпяющего двоичный сумматор/ с инверторами на одном входе, двоичного сумматора 5, блока 6 ограничения, состоящего из двух RS-триггеров, блока 7 выборки, трех буферных регистров триггеров 8-10, блока 11 выборки, трех главных регистров триггеров 12-14, трех регулирующих органов 15-17, состоящих из трансформатора с первичной, вторичной обмотками и секциями регулировочных обмоток, датчиков 18-20 тока, входных 21 и выходных 22 выводов устройства.

АЦП (фиг.2) состоит из трех ана- лого-временных преобразователей (АВП) 23-25 интегрирующего типа, генератора 26 тактовых импульсов, двоичного счетчика 27 и логических элементов 3 ИЛИ 28 и 2 И 29.

Синхронизатор (фиг.З) состоит из трех формирователей импульсов напряжения (ФИН) - узла 30, циклического счетчика фаз (ЦСФ) 31, узла 32 сброса, узла 33 предварительной установки и формирователя 34 импульсов выборки, причем входы ФИН подключены к первому входу синхронизатора, а их выходы - к первому выходу синхронизатора, входы ЦСФ, узла 32 и формирователя 34 объединены и подключены к второму входу синхронизатора, а их выходы - соответственно к

5

второму, третьему и пятому выходам синхронизатора, выход узла 33 соединен с четвертым выходом синхронизатора.

Стабилизатор работает следующим образом.

Импульсом первоначальной установки с третьего выхода синхронизатора 2, формируемым при начальном включении, главные регистры триггеров 12-14 по входу установки в О устанавливаются в исходное нулевое состояние, что соответствует подключению всех секций регулировочных обмоток к первичной обмотке.При подаче трехфазного напряжения гети на шину 21 питания фазные напряжения на шине 22 минимальны и равны

20

п ттW

ивых исети. к -W + W

моисс 4 PIw 1

5

0

5

0

5

0

5

где W

v

P

BUX Ф

сети Ф К „„„.

-число витков первичной обмотки;

-ч исло витков регулировочной обмотки первой секции, соответствующей первому члену двоичного степенного ряда чисел;

-фазное выходное напряжение ;

-фазное напряжение сети;

-максимальный двоичный код на выходе главных регистров триггеров.

Фазные напряжения со сдвигом

о 2 120° (-о- f) с выходной шины 22 по

цепи обратной связи поступают на три входа АЦП1. Поскольку в качестве АВП выбраны АВП двухтактного интегрирующего типа, то в течение первых полупериодов фазных напряжений происходит заряд интегрирующих емкостей, скорость нарастания напряжения на них пропорциональна величинам входных напряжений. Во вторые полупериоды происходит разряд данных емкостей с постоянной скоростью, не зависящей от амплитуды напряжения, до которой они оказались заряженными. В результате на выходах АВП образуются информационные импульсы,длительность которых пропорциональна средней за полпериода величине измеряемого фазного выходного напряжения. Работа АВП синхронизирована с сигналами датчиков напряжения, формируемыми в синхронизаторе 2. Далее полученные импульсы с трех АВП объединяются схемой 3 ИЛИ и поступают на вхо двоичного счетчика, предварительно заполненного эталонными импульсами с генератора тактовых импульсов. На выходе счетчика образуется двоичный код, соответствующий длительности преобразуемого импульса с выхода АВП Таким образом, осуществляется последовательное аналого-цифровое преобразование.

Последовательность информационных импульсов поступает также на второй вход синхронизатора, где по их переднему фронту формируются сигналы сброса, которые обнуляют счетчик А1Щ1 и RS-триггеры блока 6 ограничения, подготавливая их к последовательной обработке каждого информационного импульса.

Текущий двоичньй код Кп, образуемый на выходе счетчика АЦП1,поступает на один из входов вычитателя 4, где из него вычитается код уставки К0, поступающий на инверсный вход вычитателя, и полученная разность К - К0 подается на вход сумматора, на его другой вход через узел 11 выборки поступает код Кh с выхода одно- из главных регистров триггеров. Причем выбор необходимого регистра, соответствующего обрабатываемой фазе, осуществляется сигналами выборки, формируемыми в синхронизаторе циклическим счетчиком фаз.

Полученный на выходе сумматора код соответствует коду алгебраической суммы трех величин К п- К 0 + + К , является результирующим кодом и одновременно поступает на информационные входы всех буферных регистров триггеров 8-10, но записывается лишь в один из них соответствующим сигналом синхронизации с третьего выхода синхронизатора. С выхода буферного регистра триггеров в главный регистр триггеров информация заносится сигналами токовых датчиков, что позволяет исключить возможность токов короткого замыкания в регулировочных секциях при емкостном характере нагрузки.

Таким образом, изобретение позволяет стабилизировать трехфазное напряжение, а при необходимости и т- фазное, при минимальных аппаратных

0

5

0

5

0

5

0

5

0

5

затратах вычислительного устройства.

Формула изобретения

Стабилизатор переменного напряжения, содержащий регулирующий орган, первый вход которого соединен с входным выводом, с первым входом аналого-цифрового преобразователя и первым входом синхронизатора, вход синхронизации аналого-цифрового преобразователя соединен с первым выходом синхронизатора, а информационный вы;;од - с одним из входов вычитателя, другой вход которого соединен с выходом блока уставок, а выход подключен к одному из входов сумматора, выход которого соединен с информа- ционным входом буферного регистра . триггеров, вход синхронизации которого подключен к второму выходу синхронизатора, а выход - к информационному входу главного регистра триггеров, вход установки в О которого подключен к третьему выходу синхронизатора, а выход соединен с входом управления регулирующего органа,блок ограничений, состоящий из двух RS- триггеров, входы установки в О которых объединены и подключены к четвертому выходу синхронизатора и входу Сброс аналого-цифрового преобразователя, входы установки в 1 первого и второго RS-триггеров подключены соответственно к второму и третьему выходам сумматора, датчик тока, первый выход которого подключен к выходному выводу, вход датчика тока соединен с выходом регулирующего органа, а второй выход - с входом синхронизации главного регистра триггеров, отличают и й- с я тем, что, с целью расширения функциональных возможностей за счет обеспечения возможности стабилизации трехфазного напряжения при минимальных аппаратных затратах, в него введены два регулирующих органа, два датчика тока, два главных регистра триггеров, два буферных регистра - триггеров, два блока выборки, причем синхронизатор состоит из трех формирователей последовательности прямоугольных импульсов, сдвинутых на 120°, входы которых подключены к первому входу синхронизатора, а выходы - к его первому выходу, циклического счетчика фаз, выход которого соединен с вторым выходом синхронизатора, блока Сброс, выход которого соединен с третьим выходом синхронизатора, блока предварительной установки, выход которого соединен с четвертым выходом синхронизатора, формирователя импульсов выборки, выход которого соединен с пятым выходом синхронизатора, а вход объединен с входами блока Сброс и циклического счетчика фаз и додключен к второму входу синхронизатора, аналого-цифровой преобразователь состоит из трех аналого-временных преобразователей, входы которых подключены соответственно к первому, второму и третьему входам аналого-цифрового преобразователя, а входы синхронизации - к входу синхронизации аналого-цифрового преобразователя, выходы аналого-временных преобра- зователей через элемент 3 ИЛИ подключены к первому входу элемента И IH первому выходу аналого-цифрового преобразователя, генератора тактовых импульсов, выход которого подключен к второму входу элемента Иэ выход которого подключен к суммирующему 1Входу двоичного счетчика, выход которого соединен с информационным выходом аналого-цифрового преобразит- геля, а вход установки в 0м - с входом Сброс1 аналого-цифрового преобразователя, первый и второй БХОДЫ Ьервого блока выборки соединены соответственно с выходами RS-триггеров блока ограничений, первый и второй |зыходы подсоединены соответственно

Вход Ьеинхрвнш. Ь Выл.1

0

5

0

5

0

5

к входам установки в 1 и р О первого, второго и третьего буферных регистров триггеров, а вход выборки соединен с пятым выходом синхронизатора и входом выборки второго блока выборки, три входа которого подключены соответственно к выходам трех главных регистров триггеров, а выход соединен с вторым входом сумматора, входы синхронизации второго и третьего буферных регистров триггеров подключены к второму выходу синхронизатора, информационные входы подключены к выходу сумматора, а информационные выходы соединены соответственно с информационными входами второго и третьего главных регистров триггеров, входи установки в О которых соединены с третьим выходом синхронизатора, а выходы соединены соответственно с входами управления второго и третьего регулирующих органов, выходы которых соединены соответственно с входами второго и третьего датчиков тока, первые выходы которых соединены с выходным выводом,, а вторые - с входам- синхронизации второго и третьего главных регистров триг. геров соответственно, первые входы зторого и третьего регулирующих органов соединены с входным выводом и соответственно с вторым и третьим входами аналого-цифрового преобразователя и первым входом синхронизатора, второй вход которого соединен с первым выходом аналого-цифрового преобразователя.

выход

инфорн.

Фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Стабилизатор переменного напряжения | 1985 |

|

SU1334117A1 |

| Стабилизатор переменного напряжения | 1983 |

|

SU1092476A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ СО СЖАТИЕМ | 1984 |

|

SU1177836A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1989 |

|

SU1691880A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Устройство для ввода информации | 1982 |

|

SU1070537A1 |

| Устройство для передачи информации с защитой от ошибок | 1989 |

|

SU1669080A1 |

| Спироанализатор | 1986 |

|

SU1391621A1 |

| РАДИОЛОКАТОР-ИНТРОСКОП | 1994 |

|

RU2096767C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

Изобретение относится к вторичным источникам питания радиоаппаратуры. Целью изобретения является расширение функциональных возможностей путем обеспечения стабилизации трехфазного напряжения при минимальных аппаратных затратах. Цель достигается за счет введения в устройство двух регулирующих органов 16 и 17, двух буферных регистров триггеров 9 и 10, двух главных регистров триггеров 13 и 14, двух датчиков 19 и 20 тока. При этом уменьшение аппаратных затрат достигается введением двух блоков 7 и 11 выборки и выполнения аналого-цифрового преобразователя 1 на трех аналого-временных преобразователях, генераторе тактовых импульсов, двоичном счетчике и логических элементах ИЛИ и И. В результате такого выполнения схемы на выходе сумматора 5 появляется код, поступающий на информационные входы всех буферных регистров триггеров 8, 9 и 10, но записывается лишь один из них соответствующим сигналом синхронизации с третьего выхода синхронизатора 2. 3 ил.

| Стабилизатор переменного напряжения | 1983 |

|

SU1092476A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Стабилизатор переменного напряжения | 1985 |

|

SU1334117A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1990-01-07—Публикация

1987-04-20—Подача