Изобретение относится к преобразованию информации и может найти применение в информационно-измеритель- ньпс системах, гибридных вычислительных комплексах, системах автоматического управления.

Целью изобретения является повышение точности.

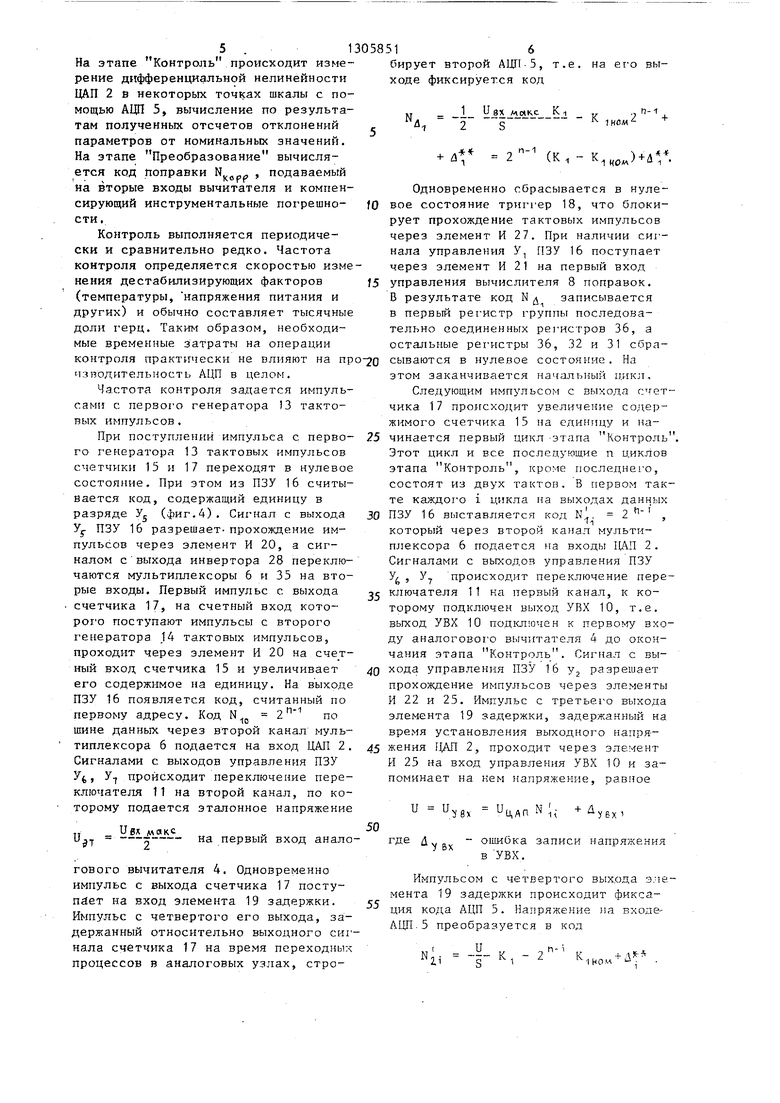

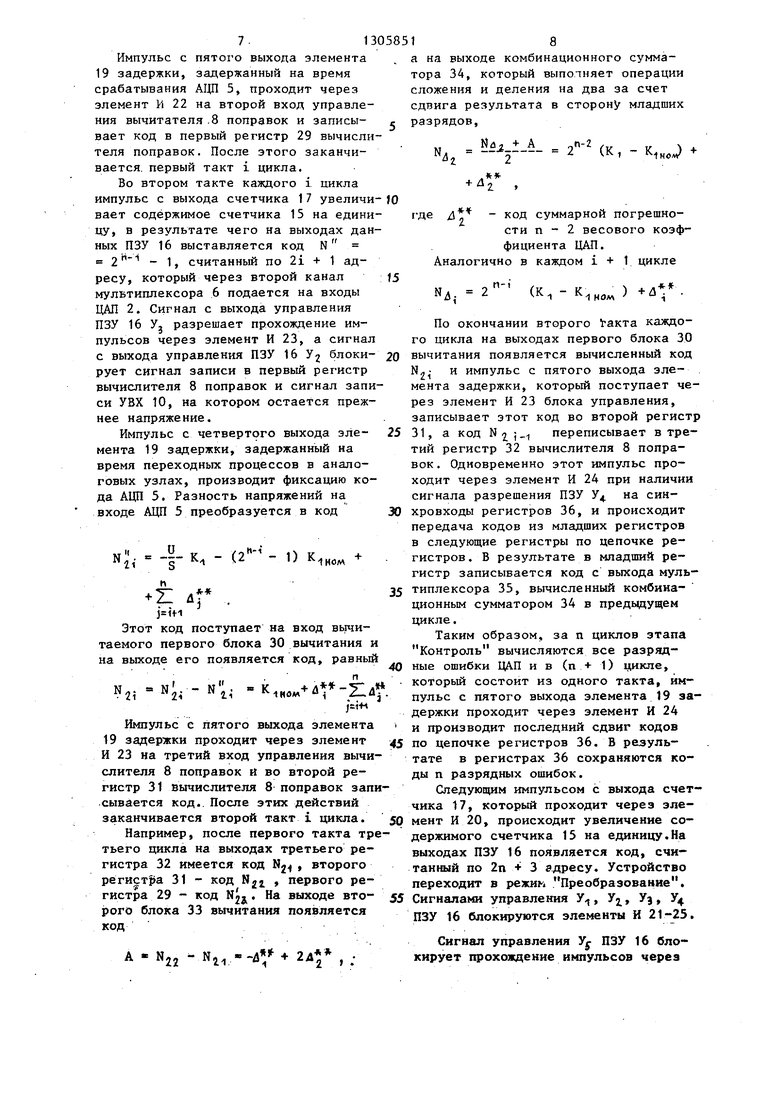

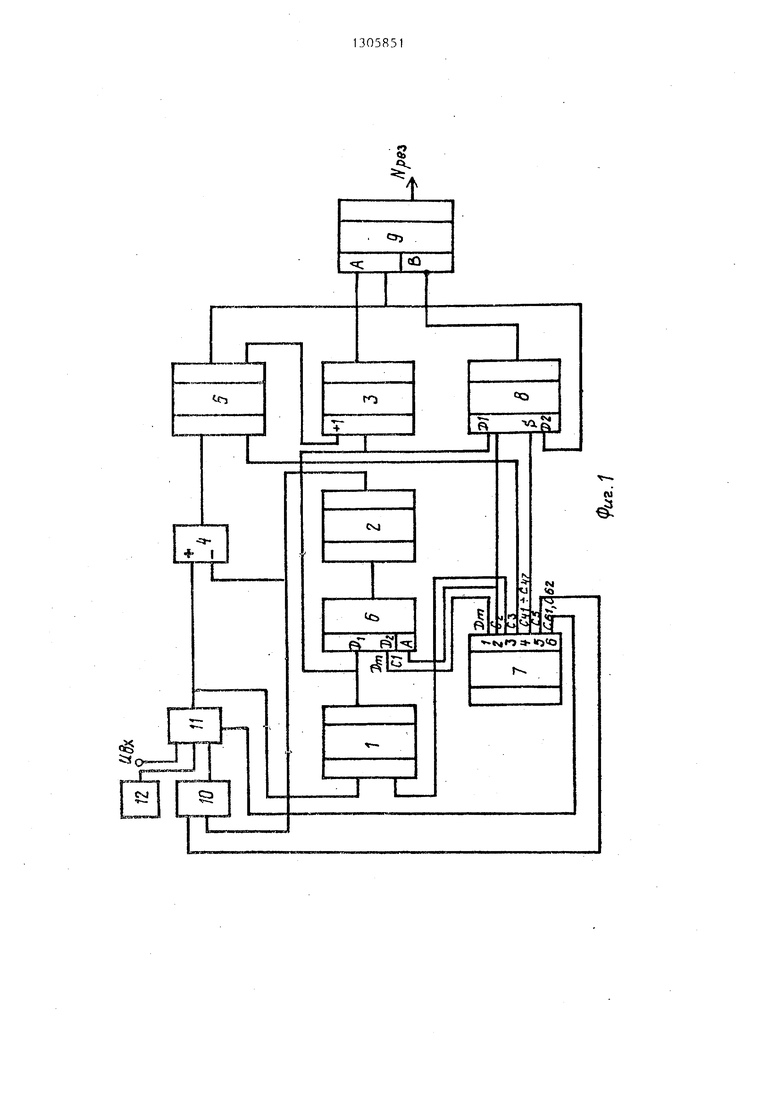

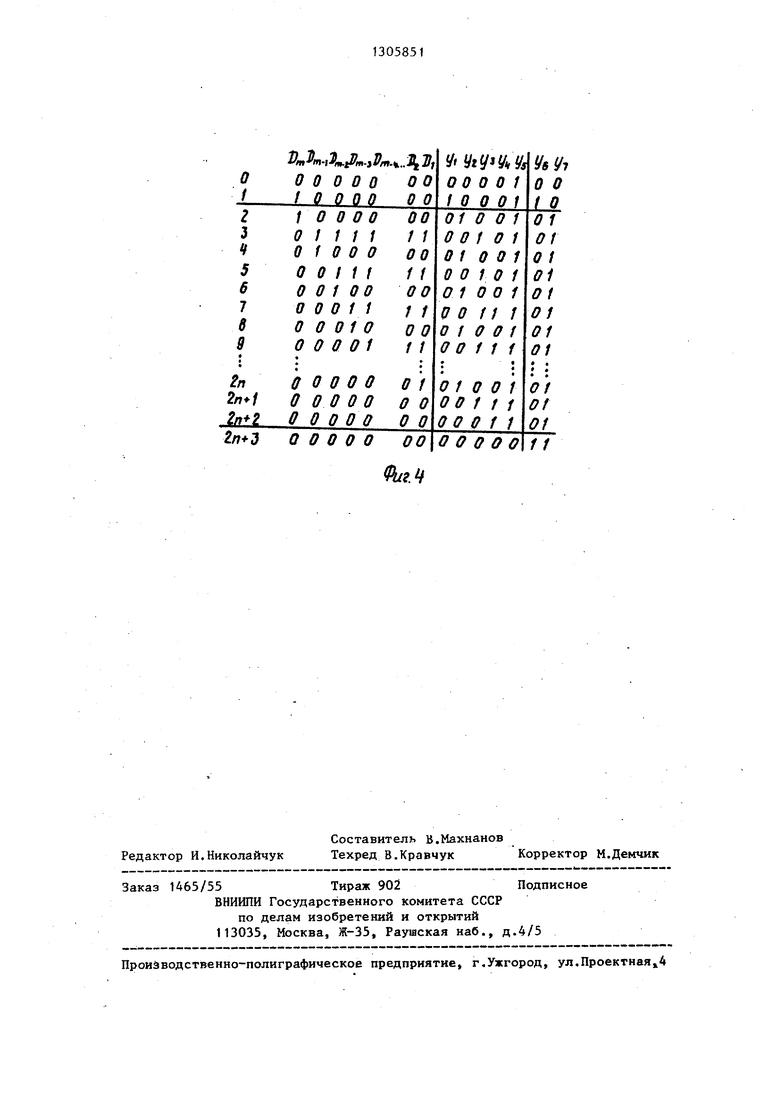

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - вариант реализации блока управления; на фиг.З - вариант реализации вычислителя поправок; на фиг.4 - таблица кодов,записанных в ПЗУ для реализации функций управления.

Устройство содержит первый аналого-цифровой преобразователь (А1Щ) 1 , например, параллельного типа, циф- роаналоговый преобразователь (ЦАП) 2, цифровой сумматор 3, аналог овый вычитатель 4, второй АЦП 5, мультиплексор 6, блок 7 управления, вычислитель 8 поправок, цифровой вычитатель 9, устройство 10 выборки и хранения (УВХ) , пе реключатель 11, источник 12 эталонного напряжения.

Блок 7 управления (фиг,2) содержит первый 13 и второй 14 генераторы тактовых импульсов, распределитель импульсов, реализованный на счетчике 15, постоянном запоминающем устройстве (ПЗУ) 16, счетчике (делителе частоты) 17, триггере 18, элементе 19 задержки, восьми элементах И 20-27 и одном инверторе 28.

В разрядах, являющихся выходами данных, по нулевому, 2п + 1, 2п + 2 и 2п + 3 адресам ПЗУ записаны нулевые коды, где п - разрядность ЦАП 2, В первом адресе двоичный код числа 2 . По каждому 21 адресу, где 1 i i i п, записан двоичный код числа 2 , а по адресам 21 + 1 - двоичные коды чисел 2 - 1.

Разряд, являющийся выходом У , содержит единицу по первому адресу и нули в остальных. Разряд, являющийся выходом У , содержит единицу в адресах 21, где 1 i i ;i п, и нули в остальных, а разряд, являющийся выходом УЗ, содержит единицу во всех ад- ресах 21 + 1 и нули в остальных. Разряд У4 содержит единицу по адресам 21 + 1 и 2п + 2, где 3 6 i jfen, а в -остальных - нули. Разряд У содержит нуль по адресу 2п + 3 и единицу во всех остальных. Разряд У содержит единицу по адресам 1 и 2п + 3, а в

рстальных - нули, -разряд У - единицу во всех адресах, кроме нулевого и первого.

Вычислитель 8 поправок (фиг.З)

содержит первый рег истр 29, первый блок 30 вычитания, второй 31 и третий 32 регистры, второй блок 33 вычитания, комбинационный сумматор 34, мультиплексор 35, группу последовательно соединенных регистров 36, элемент ИЛИ 37, регистр 38 сдвига, элемент И 39 и накапливающий сумматор 40.

Устройство работает в двух режимах: Контроль и Преобразование.

В начальном цикле Контроль происходит измерение масштаба преобразования с помощью аналого-цифрового преобразователя и запись полученного кода в регистр хранения вычислителя поправок,

В следую1дие п + 1 циклы производится вычисление п разрядных ошибок и запоминание их в регистрах вычислителя поправок. На этапе Преобразование происходит преобразование входного

напряжения, формирование кода поправки по значению кода АЦП 1 и вычисление выходного кода,

После любого стробирующего импульса на управляющем входе первого АЦП

1 фиксируется код

oti 2

n-i

и . с +й

лип 1

где с

2 /Ц

d - разрядная цифра;

НУ ,.«„Г номинальная крутизна

Л /ЛО1чС

АЦП;

п - число разрядов выходного кода; и - напряжение на выходе

переключателя 11; Лдцп - погрешность. Напряжение на выходе ЦАП при этом авно

ЦАП

1.0, (а.

ИА

50

S-N, , 1 1

номинальная крутизна ЦАП; идеальное значение веса i-ro разряда ЦАП; погрешность весового коэффициента i-ro разряда ЦАП.

313058514

На выходе вычитателя формируется читателя, число, представленное кодом; напряжениена первых входах вычитателя, равно

АЦП2 1 - %лп 2 1

п .

- Kj(S-N, + Zlot, 4; )

к,(и - N, S) + (К, - кр X

X S

1 d.,-2 - KjHoC.d:,

irfi t

где К и К, - коэффициенты передачи вычитателя по инвертирующему и неинвертирующему входам соответственно, причем для правильной работы устройства следует принять

S К,

а номинальное значение должно быть равно целой степени двойки, например

KIHCM - 2

п-1

где п - число разрядов АЦП 5.

Обозначив суммарную ошибку,обусловленную влиянием неидеальности задания а. и неравенством коэффициентов передачи вычитателя по разным входам, как

д (К - К) S-2 - К,д. ,

запишем

и

К.(и - N S) +51ot,dV

А,П,

Код на выходе АЦП 1 равен

NI nAng- ЛЦП

Пусть с 1/S (при других соотношениях получаются аналогичные результаты, если соответствующим образом изменить К).Тогда

N, K,(U/S-N,)

Код, поступающий на первые входы вычитателя 9, состоит из двух групп п-1 разрядов с выходов второго АЦП 5, являющихся младшими разрядами ко- да и кода суммы выходного кода первого АЦП 1 и старшего разряда второго АЩ1 5. Учитывая позиции этих групп в разрядной сетке кода на входах.выNBUM, 1ио. -N, р

нс. N, ..л,

iC. с

- Ь

Аи,П5

С учетом того, что К -(ном + 4к , где Дц - инструментальная ошибка задания К, получаем

«выч, K.N, + (К,„,-ьЛк, ) I - - (К,. N, + 21 - +

, U-KjjjOM , . и . + AUn, - ЛК, с

25

Ео.

1S1

где

j

«

5

0

Г -.) -- -is-- Так как ЛдцПс превышает единицы с младшего разряда кода Nj и соответственно Ng,,, а Ng - 2 , где обычно п равно 6 или 8, то относительная погрешность, вносимая ,nt 3 результат преобразова- НИН, пренебрежимо мала и в дальнейшем ti АЦП5 пренебрегаем. Д дцп j также не влияет на результат преобразования, если только величина Лдид S Kj не превышает допустимого диапазона входных сигналов АЦП 5.

Таким образом, если переключатель 11 коммутирует На вход первого АЦП J входной сигнал U , код на первом входе вычитателя 9 представляет число, отличающееся от идеального значения на величину, зависящую от этого кода1 и инструментальных погрешностей устройства, т.е. ошибок задания коэффициентов К, К и aj. Для компенсации этих погрешностей на вторых входах вычитатг.ля 9 должен форьш- роваться код, равный

и

§

N

Корр

и м -S- J

Uf

«

i

Работа АЦП подразделяется на два этапа - Контроль и Преобразование.

5 .13058

На этапе Контроль происходит измерение дифференциальной нелинейности ЦАП 2 в некоторых точках шкалы с помощью АЦП 5, вычисление по результатам полученных отсчетов отклонений , параметров от номинальных значений. На этапе Преобразование вычисляется код поправки N.,

, подаваемый

корр

на вторые входы вычитателя и компенсирующий инструментальные погрешно- сти.

Контроль выполняется периодически и сравнительно редко. Частота контроля определяется скоростью изменения дестабилизирующих факторов (температуры, напряжения питания и других) и обычно составляет тысячные доли 1 ерц. Таким образом, необходимые временные затраты на операции контроля практически не влияют на пр нзподительность АЦП в .

Частота контроля задается импульсами с первого генератора )3 тактовых импульсов.

При поступлений импульса с перво- го генератора 13 тактовых импульсов счетчики 15 и 17 переходят в нулевое состояние. При этом из ПЗУ 16 считывается код, содержащий единицу в разряде У (фиг.4). Сигнал с выхода Yj- ПЗУ 16 разрешает-прохождение импульсов через элемент И 20, а сигналом с выхода инвертора 28 переключаются мультиплексоры 6 и 35 на вторые входы. Первый импульс с выхода счетчика 17, на счетный вход кото- рог о поступают импульсы с второго генератора 14 тактовых импульсов, проходит через элемент И 20 на счетный вход счетчика 15 и увеличивает его содержимое на единицу. На выходе ПЗУ 16 появляется код, считанный по первому адресу. Код N 2 по шине данных через второй канал мультиплексора 6 подается на вход ЦАП 2 Сигналами с выходов управления ПЗУ У(,, У происходит переключение переключателя 11 на второй канал, по которому подается эталонное напряжение

и

5Т

Bf. макс

на первый вход аналогового вычитателя 4. Одновременно импульс с выхода счетчика 17 поступает на вход элемента 19 задержки. Импульс с четвертого его выхода, задержанный относительно выходного сигнала счетчика 17 на время переходных процессов в аналоговых узлах, стро516

бирует второй АЦГ1-5, ходе фиксируется код

,., 1 USXMWKC

N. - --- -

+ й.

2 (К 1 - К)+(

Одновременно сбрасывается в нулевое состояние триггер 18, что блокирует прохождение тактовых импульсов через элемент И 27. При наличии сигнала управления У, ПЗУ 16 поступает через элемент И 21 на первый вход управления вычислителя 8 поправок. В результате код N записывается в первьй регистр группы последовательно соединенных регистров 36, а остальные регистры 36, 32 и 31 сбрасываются в нулевое состояние. На этом заканчивается начггльный цикл.

Следующим импульсом с выхода счетчика 17 про1гсходит увеличение содержимого счетчика 15 на единицу и начинается первый цикл этапа Контроль. Этот цикл и все последующие п циклов этапа Контроль, кроме последнего, состоят из двух тактов. В первом такте каждо1 о i цикла на выходах данных ПЗУ 16 выставляется код N. 2 , который через второй канал мультиплексора 6 подается на входы ИДИ 2. Сигналами с выходов управления ПЗУ У, У происходит переключение переключателя 11 на первый канал, к которому подключен выход УВХ 10, т.е. выход УВХ 10 подключен к пepвo ry входу аналогового вычитателя 4 до окончания этапа Контроль. Сигнал с выхода управления ПЗУ 16 у разрешает прохождение импульсов через элементы И 22 и 25. Импульс с третьего выхода элемента 19 задержки, задержанный на время установления выходного напряжения ЦАП 2, проходит через эле -1ент И 25 на вход управления УВХ 10 и запоминает на кем напряжение, равное

N;- + Дуб,,

где Д.. . - ошибка записи напряжения в УВХ.

Импульсом с четвертого выхода элемента 19 задержки происходит фиксация кода АЦП 5. Напряжение на входе- АЦП. 5 преобразуется в код

N. - К, - K,,,,,i .

ii

Импульс с пятого выхода элемента 19 задержки, задержанный на время срабатывания А1ДП 5, проходит через элемент И 22 на второй вход управления вычитателя .8 поправок и записы- , вает код в первый регистр 29 вычислителя поправок. После этого заканчивается, первый такт i цикла.

Во втором такте каждого i цикла импульс с выхода счетчика 17 увеличи-JO вает содержимое счетчика 15 на единицу, в результате чего на выходах данных ПЗУ 16 выставляется код N - 1, считанный по 21 + 1 адресу, который через второй канал f5 мультиплексора 6 подается на входы ЦАП 2. Сигнал с выхода управления ПЗУ 16 У, разрешает прохождение импульсов через элемент И 23, а сигнал с выхода управления ПЗУ 16 У2 блоки- 20 рует сигнал записи в первый регистр вычислителя 8 поправок и сигнал записи УВХ 10, на котором остается прежнее напряжение.

Импульс с четвертого выхода элемента 19 задержки, задержанный на время переходных процессов в аналоговых узлах, производит фиксацию кода АЦП 5. Разность напряжений на входе АЦП 5 преобразуется в код

а на выходе комбинационного сумматора 34, который выполняет операции сложения и деления на два за счет сдвига результата в сторону младших разрядов.

Nd, А

(К, - К,„,

fUt

г-де Л

+ Л

f

код суммарной погрешности п - 2 весового коэффициента ЦАП. Аналогично в каждом i + 1 цикле

N. (К, - К,„,„ ) -fd

По окончании второго акта каждого цикла на выходах первого блока 30 вычитания появляется вычисленный код N2,- и импульс с пятого выхода зле25

N

ii

-У- к

S

- - О

h

z:

it

ч

Этот код поступает на вход вь1чи- таемого первого блока 30 вычитания и на выходе его появляется код, равный

N

2i

N . - N

2i

li

мента задержки, который поступает через элемент И 23 блока управления, записывает этот код во второй регистр 31, а код , переписывает в третий регистр 32 вычислителя 8 поправок. Одновременно этот импульс проходит через элемент И 24 при наличии сигнала разрешения ПЗУ Уд. на син30 хровходы регистров 36, и происходит передача кодов из младших регистров в следующие регистры по цепочке ре- 1ном гистров. В результате в младший регистр записывается код с выхода муль35 типлексора 35, вычисленный комбинационным сумматором 34 в предьвдущем цикле.

Таким образом, за п циклов этапа Контроль вычисляются все разряд40 ные ошибки ЦАП и в (п + 1) цикле, который состоит из одного такта, импульс с пятого выхода элемента 19 задержки проходит через элемент И 24 и производит последний сдвиг кодов

V

Чиом i - i

jti-M

Импульс с пятого выхода элемента

19 задержки проходит через элемент 45 по цепочке регистров 36. В резуль- И 23 на третий вход управления вычи- тате в регистрах 36 сохраняются ко- слителя 8 поправок и во второй ре- ды п разрядных ошибок, гистр 31 вычислителя 8 поправок записывается код.. После этих действий

Следующим импульсом с выхода счетчика 17, который проходит через элезаканчивается второй такт i цикла. 50

Например, после первого такта третьего цикла на выходах третьего регистра 32 имеется код N2 , второго регистра 31 - код . первого регистра 29 - код Njj. На выходе вто рого блока 33 вычитания появляется код

Следующим импульсом с выхода счетчика 17, который проходит через элемент И 20, происходит увеличение содержимого счетчика 15 на единицу.На выходах ПЗУ 16 появляется код, считанный по 2п + 3 адресу. Устройство переходит в режик Преобразование.

На выходе вто- 55 Сигналами управления У, У,, УЗ , У4

ПЗУ 16 блокируются элементы И 21-25.

- N

11

+

2Л

а на выходе комбинационного сумматора 34, который выполняет операции сложения и деления на два за счет сдвига результата в сторону младших разрядов.

Nd, А

(К, - К,„,

fUt

+ Л

г-де Л

f

код суммарной погрешности п - 2 весового коэффициента ЦАП. Аналогично в каждом i + 1 цикле

N. (К, - К,„,„ ) -fd

По окончании второго акта каждого цикла на выходах первого блока 30 вычитания появляется вычисленный код N2,- и импульс с пятого выхода злемента задержки, который поступает через элемент И 23 блока управления, записывает этот код во второй регистр 31, а код , переписывает в третий регистр 32 вычислителя 8 поправок. Одновременно этот импульс проходит через элемент И 24 при наличии сигнала разрешения ПЗУ Уд. на синпо цепочке регистров 36. В резуль- тате в регистрах 36 сохраняются ко- ды п разрядных ошибок,

Следующим импульсом с выхода счетчика 17, который проходит через элеСигнал управления Уу ПЗУ 16 блокирует прохождение импульсов через

элемент И 20, и сигналом с выхода инвертора 28 переключаются мультиплексоры 6 и 35 на первые каналы и разрешается прохождение импульсов через элемент И 26. Сигналами с выходов управления Уд,, ПЗУ 16 происходит переключение переключателя 11 на вход устройства. Устройство остается в режиме Преобразование .до прихода очередного импульса с генератора 1 тактовых импульсов. За это время выполняется последовательность преобразований входного сигнала с высокой частотой, задаваемой генератором тактовых импульсов и ограниченнойj Одновременно этот импульс фиксирует

сверху . практически только динамическими параметрами 2.

Импульсом с первого выхода элемента 19 задержки, задержанным на время подключения входного напряжения, фик сируется код в первом АЦП 1. После г рубого преобразования АЦП импульсом с второго выхода элемента 19 задержки, который проходит через элемент. И 26, записывается код АЦП 1 в регистр 38 сдвига вычислителя 8 поправок, обнуляется накапливающий сумматор 40 и устанавливается в единичное состояние триггер 18. Сигнал с прямого выхода триггера 18 разрешает прохождение импульсов генератора 14 тактовых импульсов на шестой вход управления вычислителя 8 поправок. Если в старшем разряде регистра 38 сдвига логическая единица, то к содержимому накапливающего сумматора 40 прибавляется соответствующая разрядная ошибка, одновременно происходит передача содержимых регистров 36 в цепочке рег истров и сдвиг кода -в сторону старшего разряда на регистре 38 сдвига, и на входе накапливающего сумматора 40 выставляется очередная разрядная ошибка. Этот процес повторяется п тактов генератора 14 тактового импульса..

В резу.пьт ате на выходе накапливающего сумматора 40 формируется код поправки

h

-L, I lt

N

di

У

(К, - К,„„,)

,

. При частоте генератора 14 такто-- вых импульсов, 15 мГц (что вполне допустимо при реализации вычислителя 8 поправок на стандартных микросх«

5110

мах транзисторно-транзисторной логики) вычисление занимает 500 - 600 МКС, что меньше времени переходных процессов в серийных ЦАП. Таким

образом, вычисление совпадает по времени с формированием отсчета младших разрядов на втором АЦП 5 и не приводит к снижению быстродействия в режиме Преобразование.

После п такта импульс с четвертого выхода элемента 19 задержки сбрасывает в нулевое состояние триггер 18, который блокирует прохождение импульсов через элемент. И 27.

код в. АЦП 5. После кодирования младшие разряды АЦП 5 поступают на младшие разряды первого входа цифрового вычитателя ., а при наличии единицы в старшем разряде происходит инкремент кода старших разрядов, полученных при грубом преобразовании, на цифровом сумматоре 3. Выходной код цифрового сумматора 3 подается на старшие разряды цифрового вычитателя 9, а на вычитающий вход цифрового вычитателя подается код поправки N, .

В результате на выходе цифрового вычитателя 9 получается результирующий код

1Н01Л

У|1к

-ь N,

- N

корр

л НОИ

(f- - N,) (К,

К. 1 ном

Таким образом, происходит полная компенсация погрешностей, обусловленных н еидеальностью коэффициента пе- редачи Kj и весовых коэффициентов ЦАП, а также ослабление влияния погрешности, вызванной неидеальностью

коэффициента передачи К, в 2 раз, где п - число.разрядов АЦП 1.

С приходом следующего импульса со счетчика ,

г

17 описанный цикл Преобразование повторяется. После появления очередного импульса с генератора тактовых импульсов работа устройства повторяется.

изоб

р е т е н и я

1. Параллельно-последовательный аналого-цифровой преобразователь, содержащий первый аналого-цифровой преобразователь, выход которого соединен с первым входом цифрового сумматора, второй вход которого соединен с выходом старшего разряда второго аналого-цифрового преобразователя, вход которого подключен к выходу аналогового вычитателя, первый вход которого объединен с.информационным входом первого аналого-цифрового преобразователя, а второй вход соединен с выходом цифроаналогового преобразователя, отличающийся тем, что, с целью повышения точности, в него введены источник эталонного напряжения, устройство выборки и хранения, переключатель, мультиплексор, вычислитель поправок, цифровой Бычитатель и блок управления, инфор- мационный выход которого соединен с первым ир1формационным входом мультиплексора, второй информационный вход которого соединен с выходом первого анало1 о-цифрового преобразователя и объединен с первым информационным входом вычислителя поправок, выход подключен к входу цифроаналогового преобразователя, адресный вход объединен с первым управляющим входом вычислителя поправок и подключен к первому управляющему выходу блока управления, второй управляющий выход которого соединен с входом синхронизации первого аналого-цифрового преобразователя, третий управляющий выход - с входом синхронизации второго аналого-цифрового преобразователя, выход младших разрядов которого соединен с вторым информационным входом вычислителя поправок и подключен к входам первой группы входов цифрового вычитателя, входы старших разрядов которого подключены к

выходам цифрового сумматора соответ- 40 мационный вход которого объединен с ственно, а вторая группа входов цифрового вычитате.ття подключена к выходу вычислителя поправок, управляющие входы которого с второго по седьмой

соединены с соответствующими управля- 45 адресный вход является пятым ющими вькодами с четвертого по девятый блока управления, десятый управляющий выход которого подключен к управляющему входу устройства выборки и хра 1ения, одиннадцатый управляющий выход - к управляющему входу переключателя, первый информационный вход которого соединен с выходом устройства выборки и хранения, второй информационный вход - с выходом источ- з гистров и является первым управляю- ника эталонного напряжения, третий щим входом вычислителя, второй вход информационный вход является шиной . синхронизации объединен с входами син- преобразуемого сигнала, а выход под- хронизации остальных регистров груп- ключен к информационному входу пер- пы последовательно соединенных-реинформационным входом накапливающего сумматора и соединен с выходом последнего регистра группы последовательно соединенных регистров, а

управляющим входом вычислителя, второй информационный вход первого из группы последовательно соединенных регистров соединен с выходом муль- 50 типлексора, первый вход синхронизации объединен с входами сброса всех остальных регистров группы последовательно соединенных регистров, с входами сброса второго и третьего ре0

5

0

5

0

5

вого аналого-цифрового преобразователя, причем выход цифрового вычитателя является выходной шиной устройства, а информационный вход устройства выборки и хранения соединен с выходом цифроаналогового преобразователя.

2. Преобразователь по п.1, отличающийся тем, что вычислитель поправок выполнен на трёх регистрах, двух блоках вычитания, комбинационном и накапливающем сумматорах, мультиплексоре, регистре сдвига, элементах И и ИЛИ, группе последовательно соединенных регистров, первый информационный вход первого из которых объединен с первым входом первого блока вычитания и информационным входом первого регистра и является вторым управляющим входом вычислителя, выход соединен с вторым

ВХОДОМ первого блока вычитания, выход которого соединен с информационным входом второго регистра, выход которого соединен с информационным входом третьего регистра и первым входом второго блока вычитания, входы синхронизации второго и третьего регистров объединены и являются третьим управляющим входом вычислителя, второй вход второго блока вычитания соединен с выходом третьего регистра, а выход - с первым входом комбинационного сумматора, второй вход которого подключен к вр 1ходу первого регистра группы последовательно соединенных регистров, а выход си- единен с первым информационным входом мультиплексора, второй инфорационный вход которого объединен с

адресный вход является пятым гистров и является первым управляю- щим входом вычислителя, второй вход синхронизации объединен с входами син- хронизации остальных регистров груп- пы последовательно соединенных-ренформационным входом накапливающего сумматора и соединен с выходом поседнего регистра группы последовательно соединенных регистров, а

управляющим входом вычислителя, второй информационный вход первого из группы последовательно соединенных регистров соединен с выходом муль- типлексора, первый вход синхронизации объединен с входами сброса всех остальных регистров группы последовательно соединенных регистров, с входами сброса второго и третьего регистров и подключен к выходу элемента ИЛИ, первый вход которого является четвертым управляющим входом вычислителя, второй вход объединен с первым входом элемента И и первым входом синхронизации регистра сдвига и является шестым управляющим входом вычислителя, вход управления записью параллельного кода регистра сдвига объединен с входом сброса накаплива- ющего сумматора и является седьмым управляющим входом вычислителя, информационный вход является первым информационным входом вычислителя, а выход старшего разряда соединен с вторым входом элемента И, выход которого подключен к входу синхронизации накапливающего сумматора, выход которого является выходом вычислителя.

3. Преобразователь по п.1, о т - личающийся тем, что блок управления выполнен на двух счетчиках, элементе задержки, восьми эле ментах И, постоянном запоминающем устройстве, инверторе,триггере, двух генераторах тактовых импульсов, выход первого из которых соединен с входами сброса первого и второго счетчиков, выход второго генератора тактовых импульсов соединен с входом синхронизации первого счетчика, выход переполнения которого подключен к входу элемента задержки и первому входу первого элемента И, выход ко-, торого соединен с входом синхронизации второго счетчика, выход которого подключен к адресному входу постоян20 ка, второй выход элемента задержки является вторым управляющим выходо блока, третий выход соединен с вто входом шестого элемента И, выход к торого соединен с входом установки триггера и является восьмым управл щим выходом блока, четвертый выход элемента задержки соединен с первы входом седьмого элемента И, второй вход которого подключен к второму

30 управляющему выходу .постоянного за поминающего устройства, а выход яв ляется девятым управляющим выходом блока, пятый выход элемента задерж ки соединен с входом сброса тригге

35 ра и является третьим управляющим ходом блока, выход триггера соедин с первым входом восьмого элемента второй вход которого подключен к в ходу второго генератора тактовых и

.25

ного запоминающего устройства, управ-40 пульсов, а выход является десятым ляющие выходы которого с первого по управляющим выходом блока.

четвертый соединены с первыми входами соответствующих элементов И с второго по пятый, вторые входы которых объединены и подключены к первому выходу элемента задержки, а выходы являются соответственно четвертым, пятым, шестым и седьмым управляющими выходами блока, пятый управляющий выход постоянного запоминающего устрой510 ства соединен с вторым входом первого элемента И, через инвертор подключен к первому входу шестого элемента И и является первым управляющим выходом блока, шестой .управлянлций выход

5 постоянного запоминающего устройства является одиннадцатым управляющим выходом блока, информационный выход постоянного запоминающего устройства является информационным выходом бло20 ка, второй выход элемента задержки является вторым управляющим выходом блока, третий выход соединен с вторым входом шестого элемента И, выход которого соединен с входом установки триггера и является восьмым управляющим выходом блока, четвертый выход элемента задержки соединен с первым входом седьмого элемента И, второй вход которого подключен к второму

30 управляющему выходу .постоянного запоминающего устройства, а выход является девятым управляющим выходом блока, пятый выход элемента задержки соединен с входом сброса тригге-35 ра и является третьим управляющим выходом блока, выход триггера соединен с первым входом восьмого элемента И, второй вход которого подключен к выходу второго генератора тактовых им25

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1427564A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1398093A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Устройство контроля аналого-цифровых преобразователей | 1988 |

|

SU1711327A1 |

| Устройство для измерения отношения сигнала к помехе в телевизионном канале | 1985 |

|

SU1292206A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1984 |

|

SU1290521A1 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

Изобретение касается преобразования информации и может найти применение в информационно-измерительных системах, гибридных вычислительных комплексах, системах автоматического управления. Цель изобретения - повышение точности. Существенным отличием предлагаемого преобразователя от известньк является применение цифровой коррекции результатов преобразования по резальтатам контрольных измерений, реализуемых за счет введения в преобразователь, состоящий из аналого-цифровых преобразователей, цифроаналогового преобразователя, цифрового сумматора, аналогового вы- читателя, дополнительных блоков мультиплексора, блока управления, вычислителя поправок, цифрового вычитате- ля, устройства выборки и хранения, , переключателя-, источника эталонного напряжения, что обеспечивает существенное (в десять и более раз) повышение точности при его работе в широком температурном диапазоне. 2 з.п. .ф-лы, 4 ил. с fi (Л с со о 01 00 ся

Авторы

Даты

1987-04-23—Публикация

1985-05-17—Подача