| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство циклового фазирования для волоконно-оптических систем передачи информации | 1988 |

|

SU1552392A1 |

| Устройство приема информации волоконно-оптической линии связи | 1990 |

|

SU1753605A1 |

| Устройство для приема биимпульсных сигналов | 1989 |

|

SU1596477A1 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Устройство для формирования биимпульсных сигналов | 1989 |

|

SU1741267A1 |

| Устройство для формирования биимпульсных сигналов | 1988 |

|

SU1598197A1 |

| Устройство для приема биимпульсных сигналов | 1988 |

|

SU1598191A1 |

| Устройство для передачи данных по волоконно-оптическим линиям связи | 1989 |

|

SU1698994A2 |

| Устройство цикловой синхронизации | 1983 |

|

SU1332551A1 |

| Устройство для формирования биимпульсных сигналов | 1989 |

|

SU1601767A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Устройство циклового фазирования содержит регистр 1 сдвига, эл-т ИСКЛЮЧАЮЩЕЕ ИЛИ 2, г-р 3 импульсов, D-триггеры 4-6, эл-ты И 7-9, эл-т ИЛИ 10, мультиплексор 11, счетчик 12 импульсов и дешифратор 13. Для обеспечения надежной передачи данных в начале (конце) каждого сообщения передается фазирующая кодовая комбинация (метка), обеспечивающая на приемном конце выделение границ передаваемых сообщений (цикловую синхронизацию). Цель достигается за счет обеспечения формирования метки. При этом для однозначного выделения метки из состава передаваемых данных используется метод нарушения структуры линейного кода. 2 ил.

Фиг. f

-1 сЭ

Изобретение относится к электросвязи и может использоваться в волоконно-оптических системах передачи информации для циклового фазирования.

Цель изобретения - повышение помехоустойчивости .

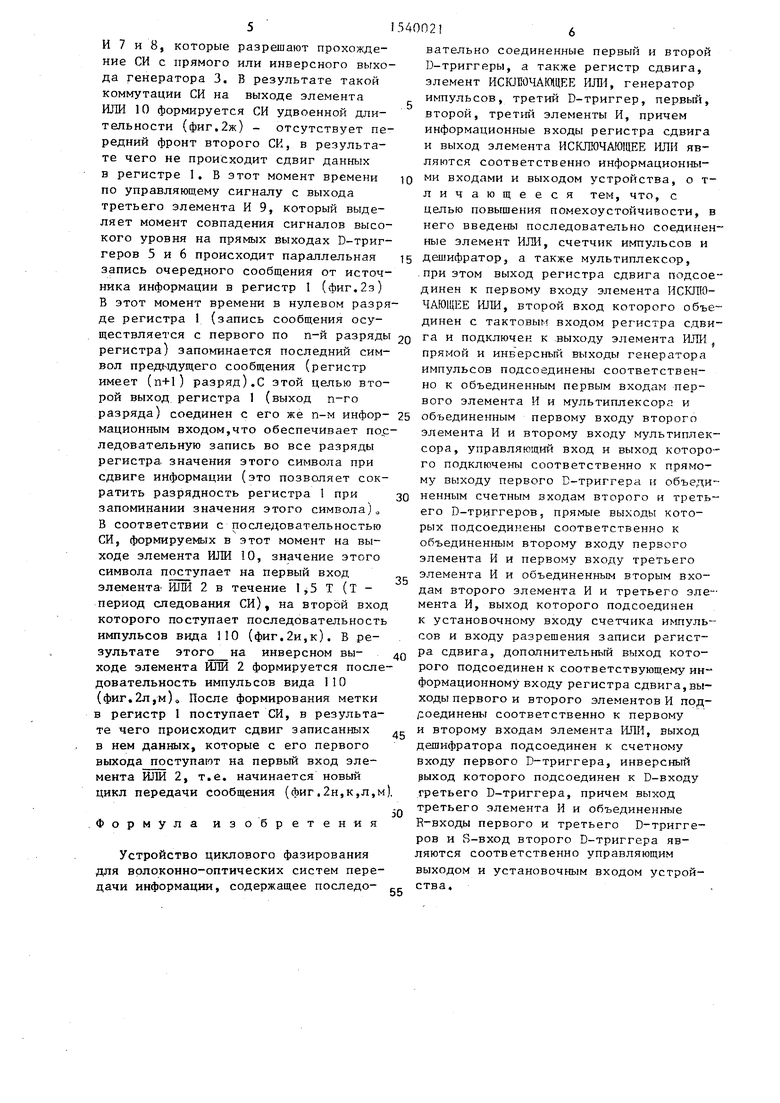

На фиг. 1 представлена структурная электрическая схема устройства циклового фазирования для волоконно- оптических систем передачи информации; на фиг.2 - временные диаграммы сигналов, поясняющие работу устройства циклового фазирования для волокон- jно-оптических систем передачи инфор- мации.

Устройство циклового фазирования для волоконно-оптических систем передачи информации содержит регистр 1 сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (ИЛИ) 2, генератор 3 импульсов, первый 4, второй 5 и третий 6 D-тригге- ров, первьй 7, второй 8 и третий 9 элементы И, элемент ИЛИ 10, мультиплексор 11, счетчик 12 импульсов и дешифратор 13.

Устройство циклового фазирования волоконно-оптических систем передачи информации работает следующим обра

По сигналу с выхода третьего элемента И 9 (фиг02з), поступающего в источник информации и регистр 1, происходит запись передаваемого сообщения параллельным кодом (форматом) в регистр 1. Сообщение состоит из п символов. Для преобразования параллельного кода в последовательный, удобный для передачи информации по каналу связи, осуществляется последо- нательный сдвиг записанных в регистре 1 данных, которые с его первого выхода поступают на первый вход элемента ИЛИ 2, на второй вход которого поступают синхронизирующие импульсы (СИ), представляющие собой последовательности импульсов типа меандр (фиг. 2а,б). В результате выполнения элементом ИЛИ 2 логической операции ИСКЛЮЧАЮЩЕЕ ИЛИ на его инверсном выходе формируются данные, представленные в биимпульсном виде (коде Манчестера). Этот код выбран в качестве линейного 1и обеспечивает оптимальные условия функционирования приемопередающих устройств(фиг.2л,м),

Для обеспечения надежной передачи данных в начале (в конце) каждого сообщения передается фазирующая кодо

c

Q

0

д

5

5

вая комбинация (метка), обеспечивающая на приемном конце выделение границ передаваемых сообщений (цикловую синхронизацию).

Для однозначного выделения метки из состава передаваемых данных используется метод нарушения структуры ли- 1нейного кода. В биимпульсном сигнале обязательным является наличие смены значений импульсов посредине би- импульсного интервала (фиг.2м). Структура метки содержит в биимпульсном интервале два одноименных импульса 1-1 (0-0), в результате чего этот переход отсутствует (фиг.2л,м) Для исключения возможности следования подряд более двух одноименных символов, значение этой пары импульсов выбирается одноименным значению двоичного символа, являющегося последним в передаваемом ранее сообщении, а значение третьего импульса метки - противоположным первым двум.

Формирование метки осуществляется следующим образом.

Счетчик 12 осуществляет подсчет числа передаваемых символов (подсчет СИ). После передачи n-го символа сообщения, по (п+1)СИ от начала сообщения, на выходе дешифратора 13 формируется управляющий импульс, который устанавливает первый D-триггер 4 в нулевое состояние (фиг.2в,г, at - задержка переключения). Дешифратор 13 выделяет (п+1) состояние счетчика 12, после сброса которого в нулевое состояние сигналом с выхода третьего элемента И 9 (фиг.2з,к,л,м) вначале осуществляется передача одного бита метки. По сигналу с инверсного выхода первого D-триггера 4 осуществляется установка в единичное состояние третьего D-триггера 6 и переключение мультиплексора 11, на выход которого теперь проходят СИ с инверсного выхода генератора 3 (фиг.2е,д). По следующему СИ с выхода мультиплексора 11 осуществляется установка в нулевое состояние второго D-триггера 5 (фиг.4ж).

Установка в единичное состояние D-триггера 5 и 6 по передним фронтам управляющих импульсов осуществляется асинхронно, а их установка в нулевое состояние - синхронно (по СИ).

Сигналами высокого уровня с прямых выходов D-триггеров 5 и 6 осуществляется управление работой элементов

И 7 и 8,

ние СИ с

да генератора 3.

коммутации СИ на

которые разрешают прохожде- прямого или инверсного выхо- В результате такой

выходе элемента ИЛИ 10 формируется СИ удвоенной длительности (фиг,2ж) - отсутствует передний фронт второго СИ, в результате чего не происходит сдвиг данных в регистре 1. В этот момент времени по управляющему сигналу с выхода третьего элемента И 9, который выделяет момент совпадения сигналов высокого уровня на прямых выходах D-триг- геров 5 и 6 происходит параллельная запись очередного сообщения от источника информации в регистр 1 (фиг.2з) В этот момент времени в нулевом разряде регистра 1 (запись сообщения осуществляется с первого по n-й разряды 2о га и подключен к выходу элемента ИЛИ регистра) запоминается последний символ предыдущего сообщения (регистр имеет (п+1) разряд).С этой целью второй выход регистра 1 (выход п-го разряда) соединен с его же n-м инфор- 25 объединенным первому входу второго

прямой и инверсный выходы генератора импульсов подсоединены соответственно к объединенным первым входам первого элемента И и мультиплексора и

мационным входом,что обеспечивает пое ледовательную запись во все разряды регистра значения этого символа при сдвиге информации (это позволяет сократить разрядность регистра 1 при запоминании значения этого символа) В соответствии с последовательностью СИ, формируемых в этот момент на выходе элемента ИЛИ 10, значение этого символа поступает на первый вход элемента- ИЛИ 2 в течение 1,5 Т (Т - период следования СИ), на второй вход которого поступает последовательность импульсов вида 110 (фиг.2и,к), В результате этогона инверсном выходе элемента ИЛИ 2 формируется последовательность импульсов вида ПО (фиг.2л,м)„ После формирования метки в регистр 1 поступает СИ, в результате чего происходит сдвиг записанных в нем данных, которые с его первого выхода поступают на первый вход эле- начинается новый

мента ИЛИ 2, т.е.

цикл передачи сообщения (фиг . 2н,к,л,м

Формула изобретения

Устройство циклового фазирования для волоконно-оптических систем пере

дачи информации, содержащее последо- 55

вательно соединенные первый и второй D-триггеры, а также регистр сдвига, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, генератор импульсов, третий D-триггер, первый, второй, третий элементы И, причем информационные входы регистра сдвига и выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются соответственно информационными входами и выходом устройства, о т- личающееся тем, что, с целью повышения помехоустойчивости, в него введены последовательно соединенные элемент ИЛИ, счетчик импульсов и

5 дешифратор, а также мультиплексор,

при этом выход регистра сдвига подсоединен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого объе динен с тактовым входом регистра сдвига и подключен к выходу элемента ИЛИ объединенным первому входу второго

прямой и инверсный выходы генератора импульсов подсоединены соответственно к объединенным первым входам первого элемента И и мультиплексора и

30

35

5

элемента И и второму входу мультиплексора, управляющий вход и выход которого подключены соответственно к прямому выходу первого D-триггера и объединенным счетным входам второго и третьего D-триггеров, прямые выходы которых подсоединены соответственно к объединенным второму входу первого элемента И и первому входу третьего элемента И и объединенным вторым входам второго элемента И и третьего элемента И, выход которого подсоединен к установочному входу счетчика импульсов и входу разрешения записи регистра сдвига, дополнительный выход которого подсоединен к соответствующему информационному входу регистра сдвига,выходы первого и второго элементов И под- роединены соответственно к первому .5 и второму входам элемента ИЛИ, выход дешифратора подсоединен к счетному входу первого D-триггера, инверсный рыход которого подсоединен к D-входу третьего D-триггера, причем выход третьего элемента И и объединенные R-входы первого и третьего D-триггеров и S-вход второго D-триггера являются соответственно управляющим

выходом и установочным входом устройства.

0

0

jgm..n

.СП

s

e ж

t-L

. Г1 ГП

жюввя™

A tf

±ti

. .

fl&W8. 2

СП-E Lf-1, J

)

яt

Ii JT f -.- .™3,

Авторы

Даты

1990-01-30—Публикация

1988-03-18—Подача