(21)4420233/24-09

(22)19.05.88

(46) 23.03.90.Бнш. № 1 1 (72) А.П.Орлов, А.И.Беляцкий, И.А.Шилов и А.И.Федоров

(53)621.394.662 (088,8)

(56)Авторское свидетельство СССР № 1019656, кл. Н 04 L 17/16, 1981.

Патент США V 4276656, кл. Н 04 В 9/00, 1982.

(54)УСТРОЙСТВО ЦИКЛОВОГО ФАЗИРОВАНИЯ ДЛЯ ВОЛОКОННО-ОПТИЧЕСКИХ СИСТЕМ ПЕРЕДАЧИ инфop {лции

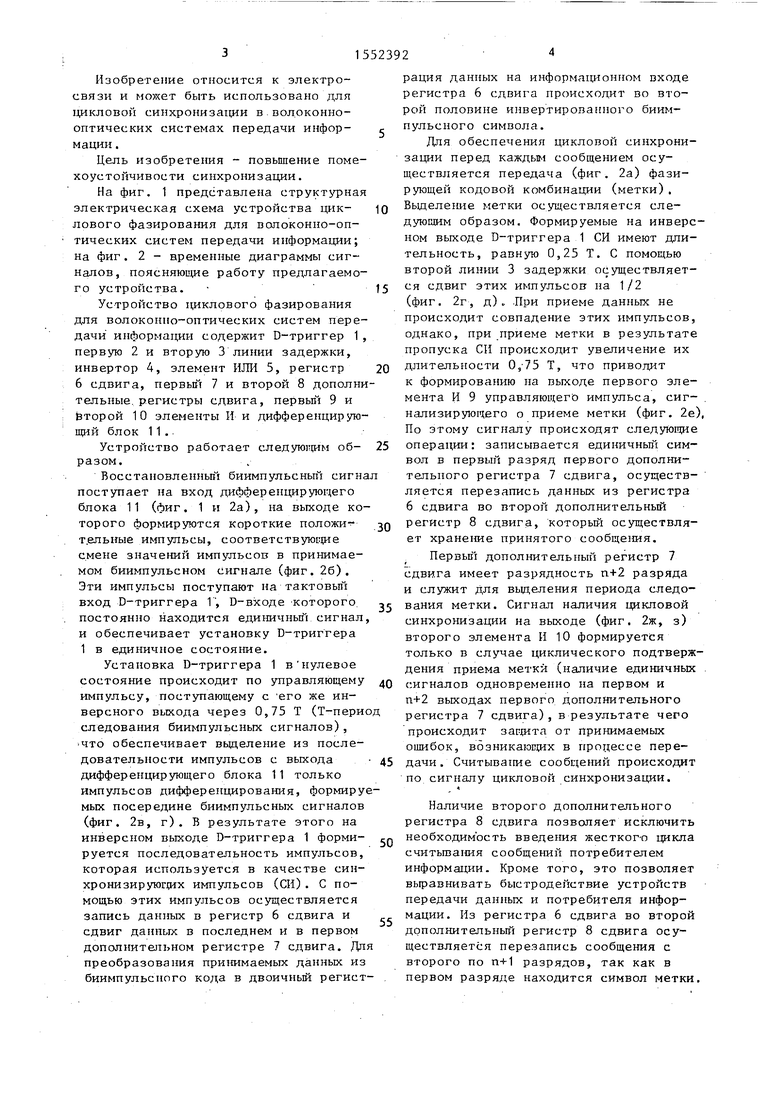

(57)Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости синхронизации. Устр-во содержит D-триггер 1, линии задержки 2 и 3, инвертор 4, эл-т

ИЛИ 5, регистры 6-8 сдвига, эл-ты И 9 и 10 и дифференцирующий блок 11.

Считывание сообщений происходит по сигналу цикловой синхронизации. Для обеспечения цикловой синхронизации перед каждым сообщением осуществляется передача фазирующей кодовой комбинации, т.е. выделенной метки. Регистр 7 служит для выделения периода следования метки, а регистр 8 позволяет исключить необходимость введения жесткого цикла считывания сообщений потребителем информации. Значение импульсов в метке выбирается противоположным значению последнего импульса предыдущего сообщения. Структура метки выбирается таким образом, чтобы следующий после метки импульс дифференцирования выделялся посередине биим- пульсного сигнала, что исключает возможность срыва работы системы синхронизации. 2 ил.

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство циклового фазирования для волоконно-оптических систем передачи информации | 1988 |

|

SU1540021A1 |

| Устройство для приема биимпульсных сигналов | 1988 |

|

SU1598191A1 |

| Устройство приема информации волоконно-оптической линии связи | 1990 |

|

SU1753605A1 |

| Устройство для приема биимпульсных сигналов | 1989 |

|

SU1596477A1 |

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Устройство цикловой синхронизации | 1987 |

|

SU1515382A2 |

| Устройство цикловой синхронизации | 1983 |

|

SU1332551A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ БИИМПУЛЬСНОГО СИГНАЛА | 1992 |

|

RU2048706C1 |

| Устройство для формирования биимпульсного сигнала | 1989 |

|

SU1637000A1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости синхронизации. Устройство содержит Д-триггер 1, линии задержки 2 и 3, инвертор 4, эл-т ИЛИ 5, регистры 6 - 8 сдвига, эл-ты И 9 и 10 и дифференцирующий блок 11. Считывание сообщений происходит по сигналу цикловой синхронизации. Для обеспечения цикловой синхронизации перед каждым сообщением осуществляется передача фазирующей кодовой комбинации, т.е. выделенной метки. Регистр 7 служит для выделения периода следования метки, а регистр 8 позволяет исключить необходимость введения жесткого цикла считывания сообщений потребителем информации. Значение импульсов в метке выбирается противоположным значению последнего импульса предыдущего сообщения. Структура метки выбирается таким образом, чтобы следующий после метки импульс дифференцирования выделялся посередине биимпульсного сигнала, что исключает возможность срыва работы системы синхронизации. 2 ил.

11-1

СП

ел

ND

СО

фие.1

Изобретение относится к электросвязи и может быть использовано для цикловой синхронизации в волоконно- оптических системах передачи инфор- мации.

Цель изобретения - повышение помехоустойчивости синхронизации.

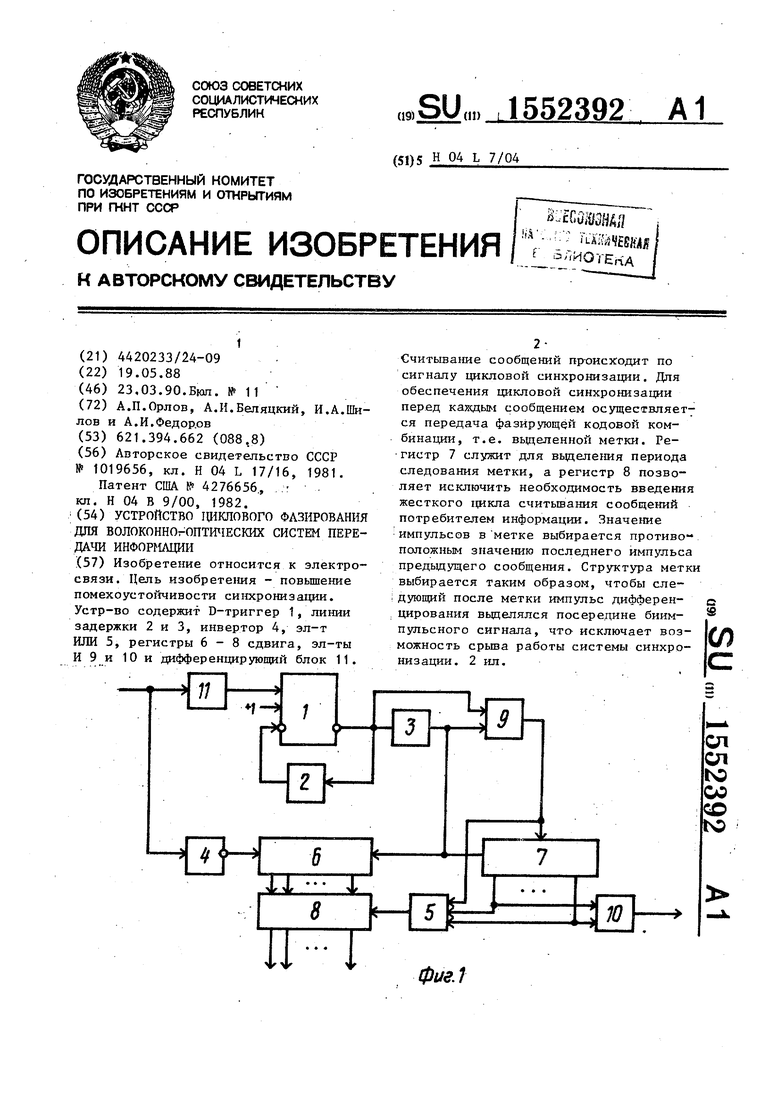

На фиг. 1 представлена структурная электрическая схема устройства цик- левого фазирования для волоконно-оптических систем передачи информации; на фиг. 2 - временные диаграммы сигналов, поясняющие работу предлагаемого устройства.

Устройство циклового фазирования для волоконно-оптических систем передачи информации содержит D-триггер 1, первую 2 и вторую 3 линии задержки, инвертор 4, элемент ИЛИ 5, регистр

6 сдвига, первый 7 и второй 8 дополнительные регистры сдвига, первый 9 и Второй 10 элементы И и дифференцирующий блок 11.

Устройство работает следующим об- р а з ом.

Восстановленный биимпульсный сигна поступает на вход дифференцирующего блока 11 (фиг. 1 и 2а), на выходе которого формируются короткие положи- тельные импульсы, соответствующие смене значений импульсов в принимаемом биимпульсном сигнале (фиг. 26). Эти импульсы поступают на тактовый вход D-триггера 1, U-входе которого постоянно находится единичный сигнал, и обеспечивает установку D-триггера 1 в единичное состояние.

Установка D-триггера 1 в нулевое состояние происходит по управляющему импульсу, поступающему с его же инверсного выхода через 0,75 Т (Т-перио следования биимпульсных сигналов) , что обеспечивает выделение из последовательности импульсов с выхода дифференцирующего блока 11 только импульсов дифференцирования, формируемых посередине биимпульсньгх сигналов (фиг. 2в, г). В результате этого на инверсном выходе D-триггера 1 форми- руется последовательность импульсов, которая используется в качестве синхронизирующих импульсов (СИ). С помощью этих импульсов осуществляется запись данных в регистр 6 сдвига и сдвиг данных в последнем и в первом дополнительном регистре 7 сдвига. Для преобразования принимаемых данных из биимпульсного кода в двоичный регистрация данных на информационном входе регистра 6 сдвига происходит во второй половине инвертированного биимпульсного символа.

Для обеспечения цикловой синхронизации перед каждым сообщением осуществляется передача (фиг. 2а) фазирующей кодовой комбинации (метки). Выделение метки осуществляется следующим образом. Формируемые на инверсном выходе D-триггера 1 СИ имеют длительность, равную 0,25 Т. С помощью второй линии 3 задержки осуществляется сдвиг этих импульсоп на 1/2 (фиг. 2г, д). При приеме данных не происходит совпадение этих импульсов, однако, при приеме метки в результате пропуска СИ происходит увеличение их длительности 0,75 Т, что приводит к формированию на выходе первого элемента И 9 управляющего импульса, сигнализирующего о приеме метки (фиг. 2е) По этому сигналу происходят следующие операции: записывается единичный символ в первый разряд первого дополнительного регистра 7 сдвига, осуществляется перезапись данных из регистра 6 сдвига во второй дополнительный регистр 8 сдвига, который осуществляет хранение принятого сообщетя.

Первый дополнительный регистр 7 сдвига имеет разрядность п+2 разряда и служит для выделения периода следования метки. Сигнал наличия цикловой синхронизации на выходе (фиг. 2ж, з) второго элемента И 10 формируется только в случае циклического подтверждения приема метки (наличие единичных сигналов одновременно на первом и п+2 выходах первого дополнительного регистра 7 сдвига), в результате чего происходит защита от принимаемых ошибок, возникающих в процессе передачи. Считывание сообщений происходит

по сигналу цикловой синхронизации,

Наличие второго дополнительного регистра 8 сдвига позволяет исключить необходим ость введения жесткого цикла считывания сообщений потребителем информации. Кроме того, это позволяет выравнивать быстродействие устройств передачи данных и потребителя информации. Из регистра 6 сдвига во второй дополнительный регистр 8 сдвига осуществляется перезапись сообщения с второго по п+1 разрядов, так как в первом разряде находится символ метки.

Значение импульсов в метке выбирается противоположным значению последнего импульса предыдущего сообщения. Структура метки выбирается так, что следующий после метки импульс дифференцирования выделяется посередине биимпульсного сигнала, что исключает возможность срыва работы системы синхронизации .

Формула изобретения

информационному входу первого дополни тельного регистра сдвига и через элемент ИЛИ - к тактовому входу второго дополнительного регистра сдвига,первый и второ выходы первого дополнительного регистра сдвига подсоединены к соответствующим входам элемента ИЛИ и соответствующим входам второго элемента И, выходы регистра сдвига

Устройство циклового фазирования для волоконно-оптических систем пере- 15 дачи информации, содержащее последовательно соединенные D-триггер и первую линию задержки, выход которой подсоединен к входу установки нулевого состояния D-триггера, последова- 20 подсоединены к соответствующим инфор- тельно соединенные инвертор и регистр мационным входам второго дополнитель- сдвига, а также вторую линию задержки, первый и второй элементы И и элемент ИЛИ, отличающееся тем, что, с целью повышения помехоустойчивости синхронизации, введены дифференцирующий блок, первый и второй дополнительные регистры сдвига, при

ного регистра сдппга, а вход дьфферен цирующего блока подключен к входу инвертора, причем вход дифференцирую- 25 щего блока, выход второго элемента И и выходы второго дополнительного регистра сдвига являются соответственно входами, выходом синхросигнала и информационными выходами устройства,

этом выход дифференцирующего блока

подсоединен к тактовому входу D-триг- гера, инверсный выход которого подсоединен непосредственно к первому входу первого элемента И и через вторую линию задержки к объединенным тактовым входам регистра сдвига и первого дополнительного регистра сдвига и второму входу первого элемента И, выход ко- торого подключен непосредственно к

информационному входу первого дополнительного регистра сдвига и через элемент ИЛИ - к тактовому входу второго дополнительного регистра сдвига,первый и второй выходы первого дополнительного регистра сдвига подсоединены к соответствующим входам элемента ИЛИ и соответствующим входам второго элемента И, выходы регистра сдвига

5 0 подсоединены к соответствующим инфор- мационным входам второго дополнитель-

подсоединены к соответствующим инфор- мационным входам второго дополнитель-

ного регистра сдппга, а вход дьфферен- цирующего блока подключен к входу инвертора, причем вход дифференцирую- щего блока, выход второго элемента И и выходы второго дополнительного регистра сдвига являются соответственно входами, выходом синхросигнала и информационными выходами устройства,

Авторы

Даты

1990-03-23—Публикация

1988-05-19—Подача