Изобретение относится к технике связи и может быть использовано в системах передачи данных, использующих самосинхринизирующиеся коды, в частности в волоконно-оптических линиях связи.

Целью изобретени является уменьшение времени фазирования при одновременном снижении вероятности ошибки.

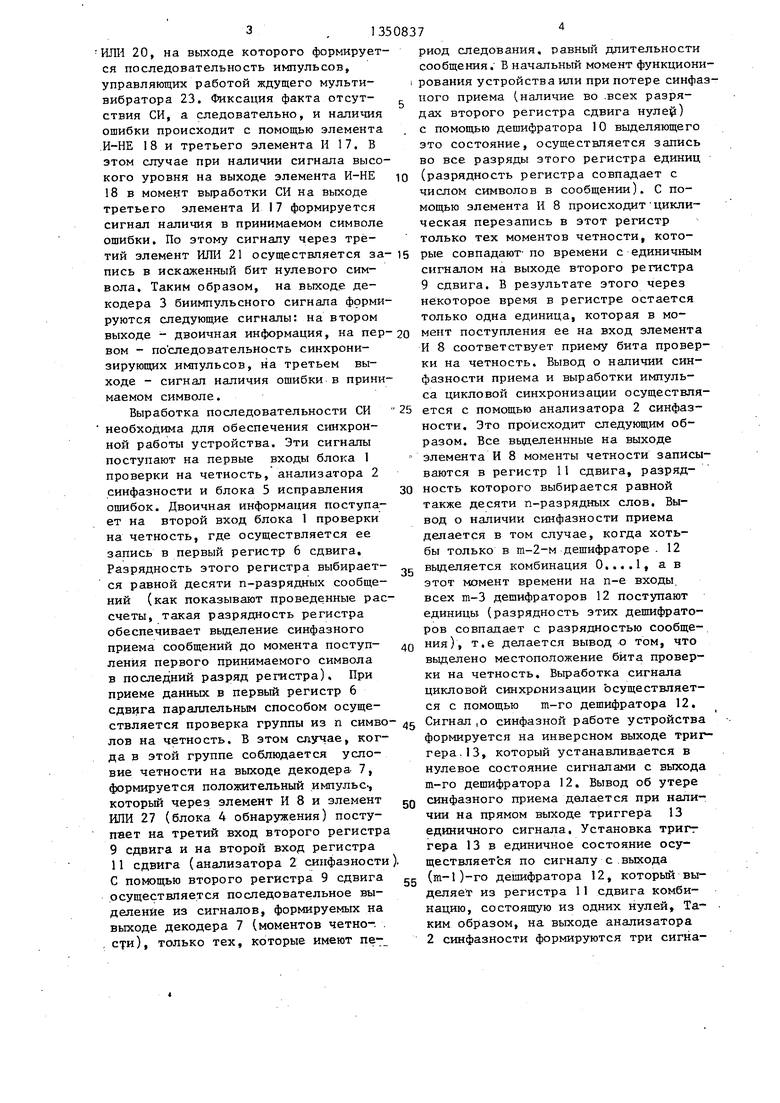

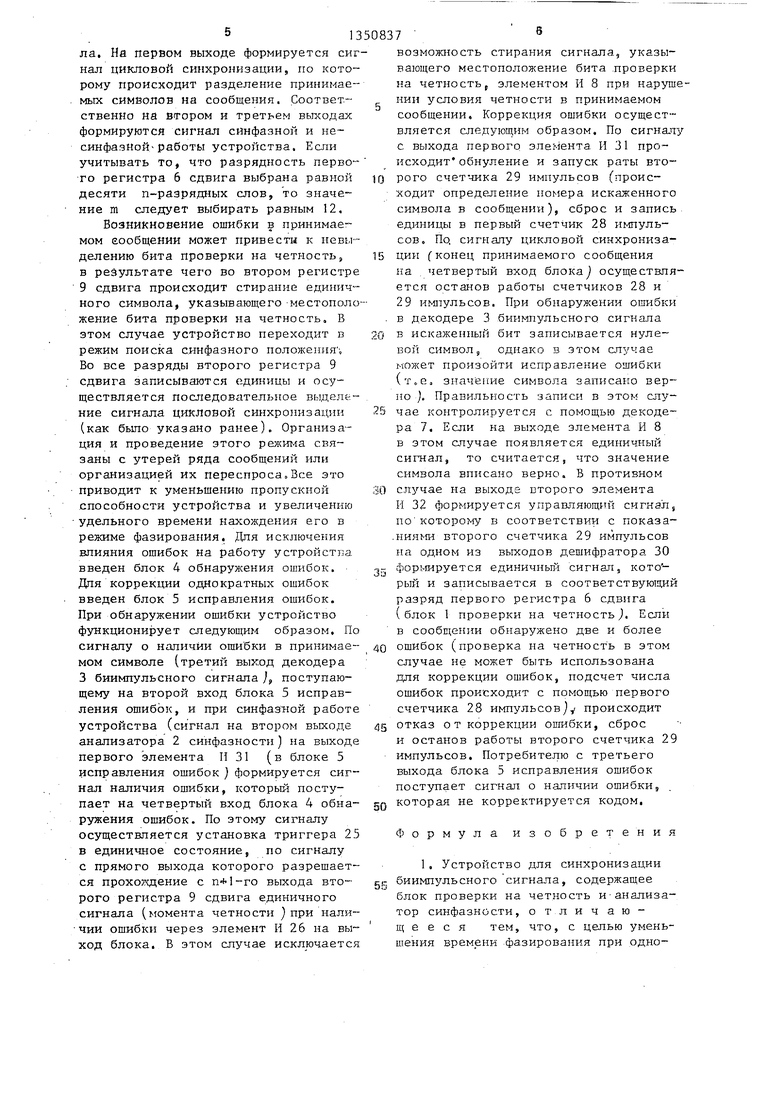

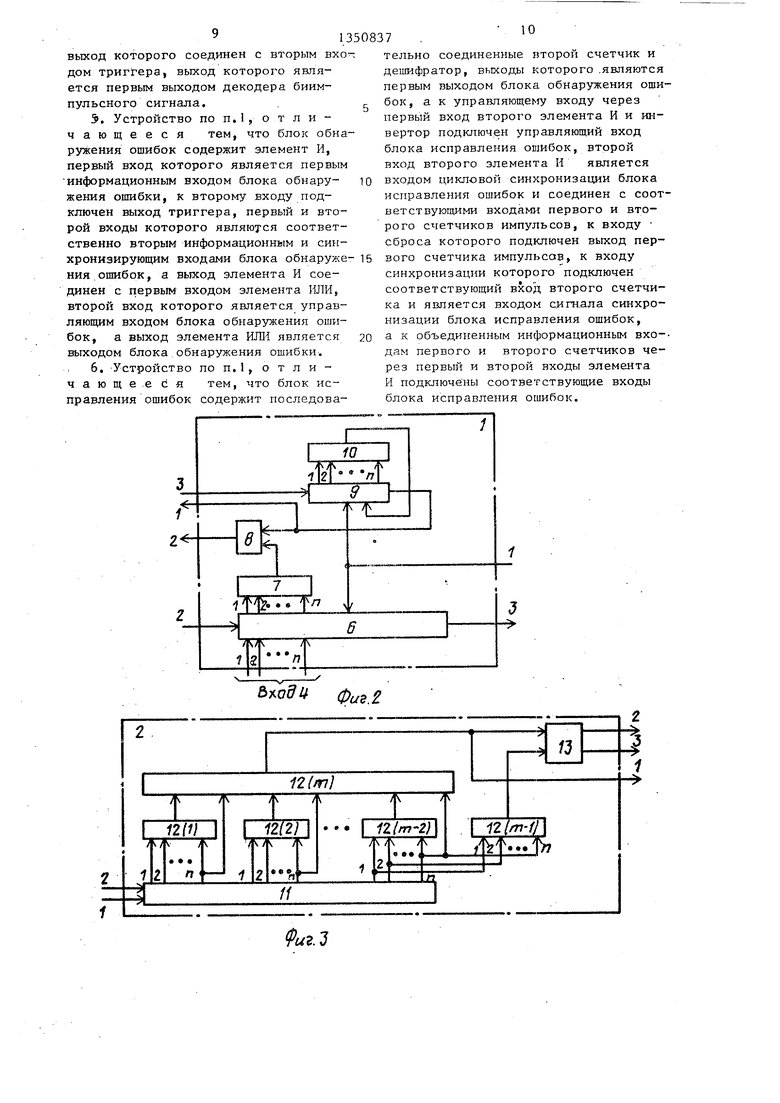

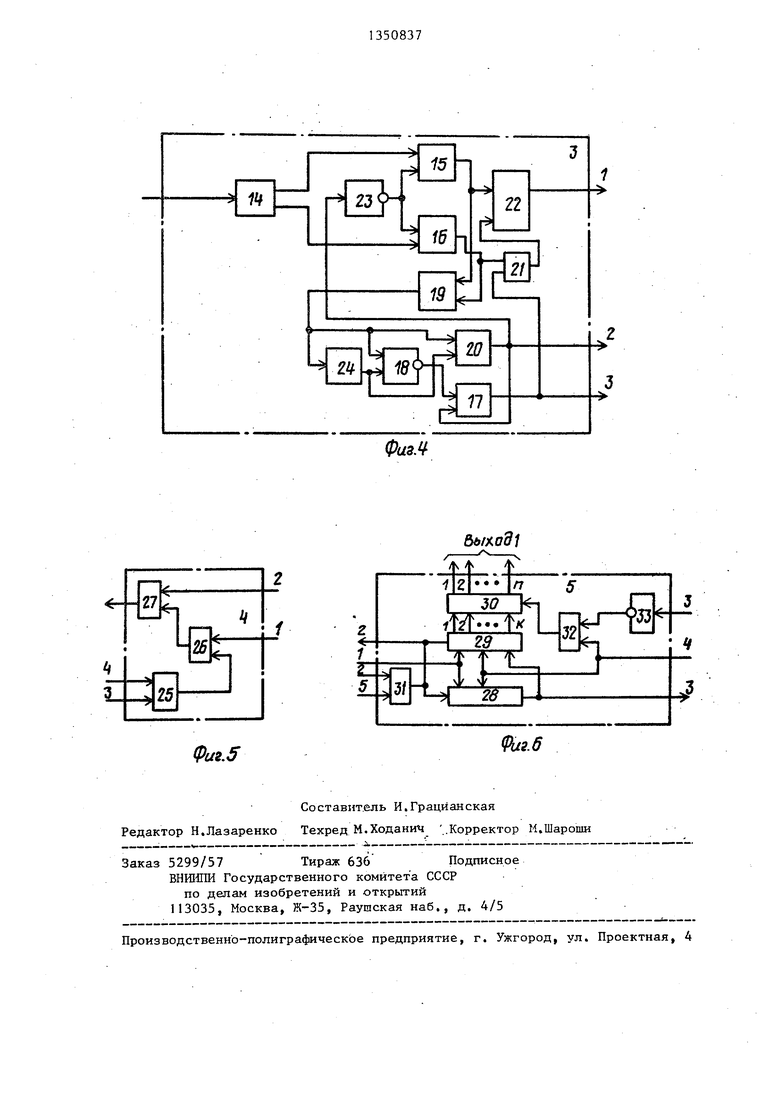

На фиг.1 представлена структурная электрическая схема устро/1ства для синхронизации биимпульсного ;игнапа; на фиг.2 - структурная электрическая схема блока проверки на четность: на фиг.З - структурная электрическая схема анализатора синфазности; на фиг.4 - схема декодера биимпульсного сигнала; на фиг.З - блок обнару-жения ошибки; на фиг.6 - блок исправления

ошибок.

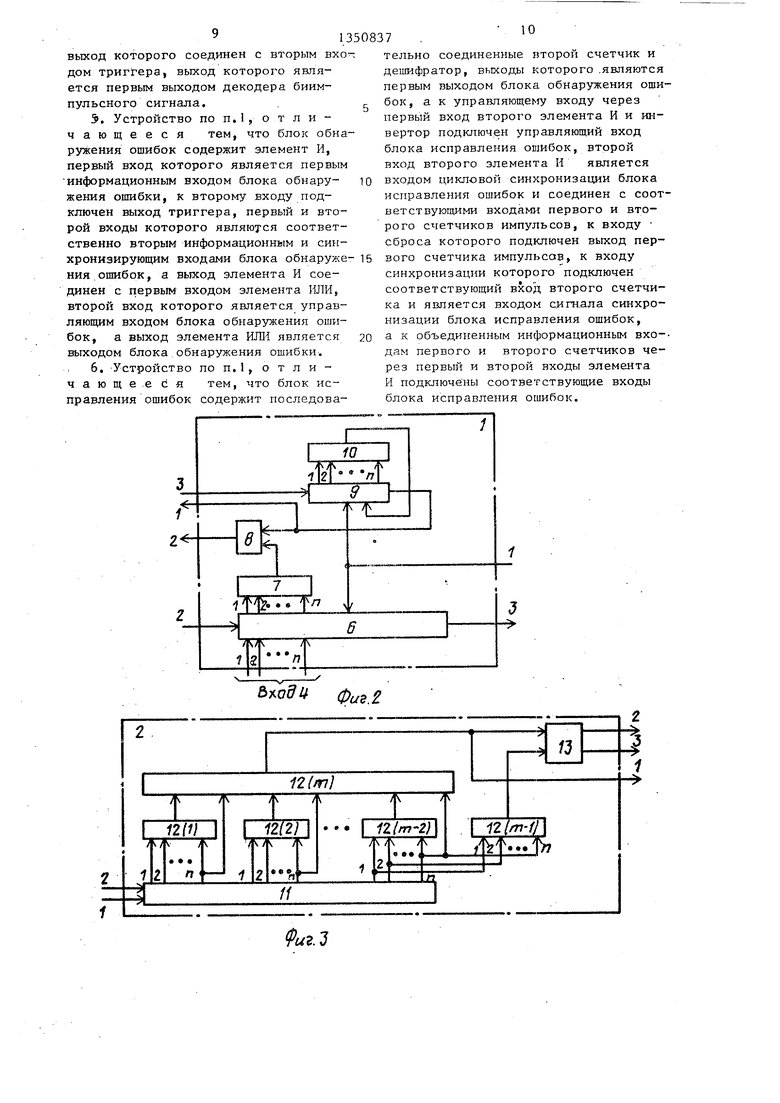

Устройство синхронизации биимпульсного сигнала содержит блок 1 Проверки на четность, анализатор 2 синфазности, декодер 3 биимпульсного сигнала, блок 4 обнаружения ошибок и блок 5 исправления ошибок.

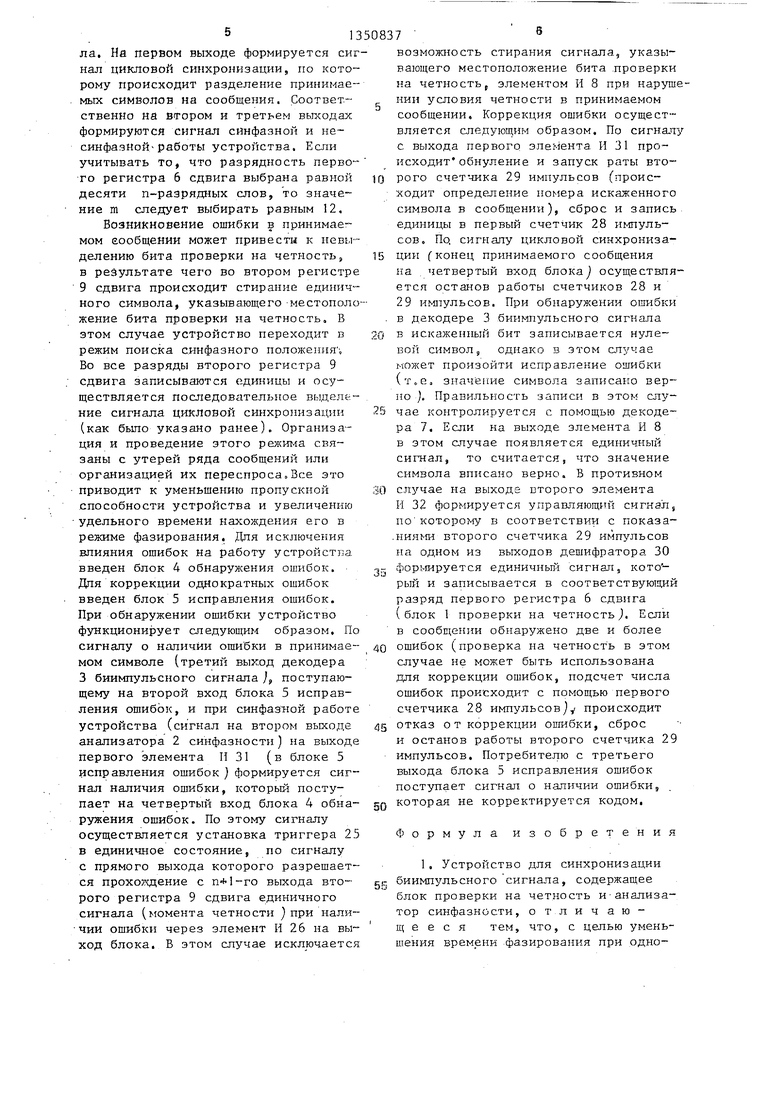

Блок 1 проверки на четность (фиг.2) содержит первый-регистр 6 сдвига, декодер 7, элемент И 8, второй регистр 9 сдвига и дешифратор 10

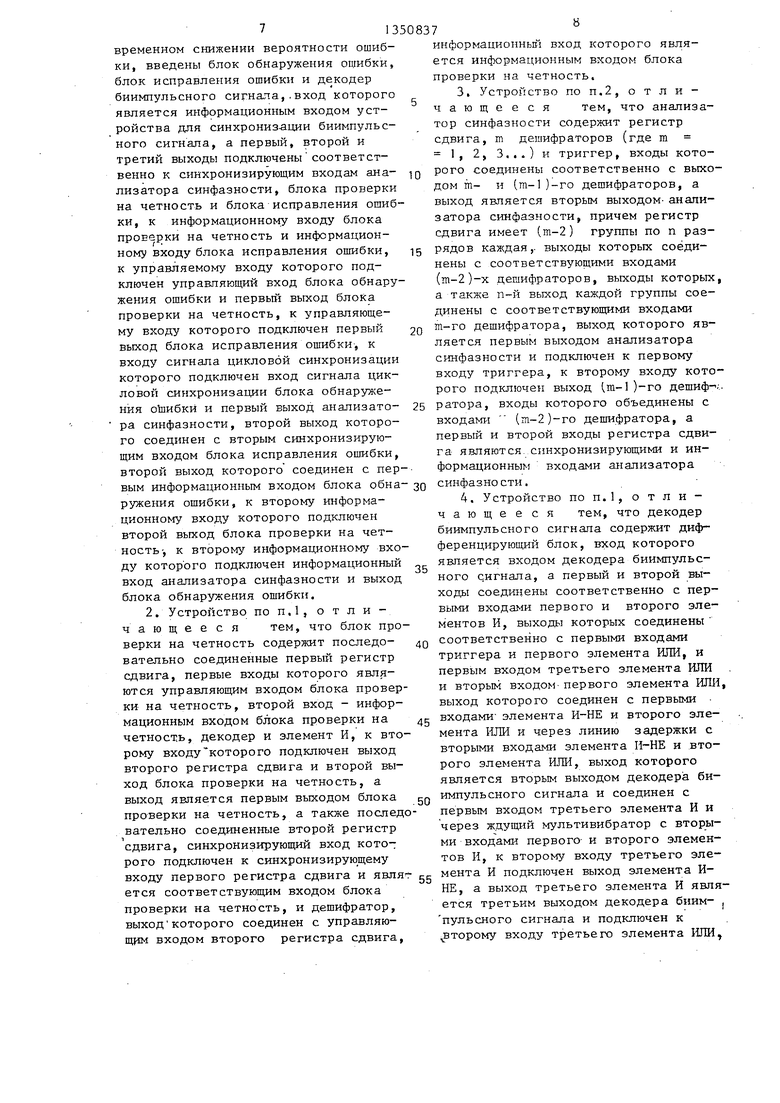

Анализатор 2 синфазности (фиг.З) содержит регистр 11 сдвига, m дешифраторов 12 (где m 1,2,..,) и триггер 13,

Декодер 3 биимпульсного сигнала (фиг.4) содержит дифференцирующий блок 14, три элемента И 15-17, элемент И-НЕ 18, три элемента ИЛИ Г9-21 триггер 22, ждущий мультивибратор 23 и линию 24 задержки.

Блок 4 обнаружения ошибок( фиг. 5) содержит триггер 25, элемент И 26 и элемент ИЛИ 2 7.

Блок-5 исправления ошибок (фиг,6) содержит два счетчика 28 и 29 импульсов, дешифратор 30, два элемента И 31 и 32 и инвертор 33.

Устройство работает следующим образом.

Передаваемые данные, представленные в биимпульсном коде, поступают на вход декодера 3 биимпульсного сигнала, С помощью дифференцирующего блока 14 осуществляется дифференцирование фронтов принимаемых посылок. На первом выходе этого блока формируются импульсы положительной поляр5

ности, соответствующие отрицательным импульсам дифференцирования, а на втором выходе - положительным импуль сам дифференцирования. Для выработки синхронизирующих импульсов (си) из . принимаем151х данных используется свойство биимпульсного сигнала - наличие обязательного перехода в значениях

0 импульсов по середине битового интервала. Исключение непериодических импульсов дифференцирования, формируемых в начале или в конце биимпульсного сигнала, осуществляется с по5 мощью первого 15 и второго 16 элементов И и ждущего мультивибратора 23, на инверсном выходе которого формируется сигнал, запрещающий прохождение через первый 15 и второй 16

0 элементы И импульсов дифференцирования, имеющих период следования, меньший тактовой частоты. Для нормальной работы декодера в этом случае необходимо, чтобы в начале передаваемых данных следовал нулевой символ, В этом случае запуск ждущего мультивибратора 23 осуществляется по импульсу дифференцирования, находящемуся в середине битового интервала.

0 В противном случае нормальная работа декодера будет восстановлена только после смены значений символов в принимаемых данных. Выдбшение двоичной информации осуществляется с помощью

5 триггера 22. При этом используется свойство биимпульсного сигнала - наличие отрицательного импульса дифференцирования в середине битового интервала для приема единичного сим0 вола и положительного импульса при приеме нулевого символа. С этой целью первыр выход дифференцирующего блока 14 черех первьш элемент И 15 соединен с входом установки триггера 22 в единичное состояние, а второй выход дифференцирующего блока 14 через второй элемент И 16 - с входом установки его в нулевое состояние. Искажение принимаемых посылок вызы- .

0 вает невыделение СИ и тем самым приводит к нарушению работы декодера. Исключение влияния ошибок на работу декодера обеспечивается путем вставки СИ из предыдущего такта. Для этих

g целей используется линия 24 задержки, которая обеспечивает задержку СИ, формируемого в предыдущем такте, на период следования СИ, Вставка СИ происходит с помощью второго элемента

5

ся последовательность импульсов, управляющих работой ждущего мультивибратора 23, Фиксация факта отсутствия СИ, а следовательно, и наличия ошибки происходит с помощью элемента И-НЕ 18 и третьего элемента И 17, В этом случае при наличии сигнала высокого уровня на выходе элемента И-НЕ 18 в момент вьфаботки СИ на выходе третьего элемента И 17 формируется сигнал наличия в принимаемом символе ошибки. По этому сигналу через трёсообщения,- В начальный момент функциони I рования устройства или при потере синфаз

J- ного приема (наличие во .всех разрядах второго регистра сдвига нулец) с помощью дешифратора 10 выделяющего это состояние, осуществляется запись во все разряды этого регистра единиц

10 (разрядность регистра совпадает с числом символов в сообщении), С помощью элемента И 8 происходит циклическая перезапись в этот регистр

только тех моментов четности, кото- тий элемент ИЛИ 21 осуществляется за- 15 рые совпадают- по времени с единичным пись в искаженный бит нулевого сим- сигналом на выходе второго регистра вола. Таким образом, на выходе де- 9 сдвига, В результате этого через

кодера 3 биимпульсного сигнала формируются следующие сигналы: на втором

выходе - двоичная информация, на пер-20 мент поступления ее на вход элемента

вом - последовательность синхронизирующих импульсов, на третьем выходе - сигнал наличия ошибки в принимаемом символе.

Выработка последовательности СИ необходима для обеспечения синхронной работы устройства. Эти сигналы поступают на первые входы блока 1 проверки на четность, анализатора 2 синфазности и блока 5 исправления ошибок. Двоичная информация поступает на второй вход блока 1 проверки на четность, где осуществляется ее запись в первый регистр 6 сдвига.

Разрядность этого регистра выбирает- g вьщеляется комбинация 0,,,,1, а в ся равной десяти п-разрядных сообще- этот момент времени на п-е входы. НИИ (как показывают проведенные рас- всех т-3 дешифраторов 12 поступают счеты, такая разрядность регистра обеспечивает выделение синфазного приема сообщений до момента поступления первого принимаемого символа

в последний разряд регистра). При приеме данных в первый регистр 6 сдвига параллельным способом осущеединицы (разрядность этих дешифрато ров совпадает с разрядностью сообще 40 ния), т,е делается вывод о том, чт вьщелено местоположение бита прове ки на четность. Выработка сигнала цикловой синхронизации осуществляе ся с помощью т-го дешифратора 12

ствляется проверка группы из п симво- Сигнал ,0 синфазной работе устройства

лов на четность, В этом случае, когда в этой группе соблюдается условие четности на выходе декодера- 7, формируется положительный импульс-, который через элемент И 8 и элемент ИЛИ 27 (блока А обнаружения) поступает на третий вход второго регистра 9 сдвига и на второй вход регистра 11 сдвига (анализатора 2 синфазности). С помощью второго регистра 9 сдвига осуществляется последовательное выделение из сигналов, формируемых на выходе декодера 7 (моментов четно- . сти), только тех, которые имеют пе50

формируется на инверсном выходе триггера. 13, который устанавливается в нулевое состояние сигналами с выхода т-го дешифратора 12, Вывод об утере синфазного приема делается при наличии на прямом выходе триггера 13 единичного сигнала. Установка тригг гера 13 в единичное состояние осуществляется по сигналу с .выхода gg (m-1)-го дешифратора 12, который выделяет из регистра 11 сдвига комбинацию, состоящую из одних нулей. Таким образом, на выходе анализатора 2 синфазности формируются три сигнасообщения,- В начальный момент функциони- I рования устройства или при потере синфазного приема (наличие во .всех разрядах второго регистра сдвига нулец) с помощью дешифратора 10 выделяющего это состояние, осуществляется запись во все разряды этого регистра единиц

(разрядность регистра совпадает с числом символов в сообщении), С помощью элемента И 8 происходит циклическая перезапись в этот регистр

некоторое время в регистре остается только одна единица, которая в моИ 8 соответствует приему бита проверки на четность. Вывод о наличии синфазности приема и выработки импульса цикловой синхронизации осуществляется с помощью анализатора 2 синфазности. Это происходит следующим образом. Все вьщеленнные на выходе элемента И 8 моменты четности записываются в регистр 11 сдвига, разрядность которого выбирается равной также десяти п-разрядных слов. Вывод о наличии синфазности приема делается в том случае, когда хоть- бы только в m-2-M дешифраторе . 12

вьщеляется комбинация 0,,,,1, а в этот момент времени на п-е входы. всех т-3 дешифраторов 12 поступают

единицы (разрядность этих дешифраторов совпадает с разрядностью сообще- ния), т,е делается вывод о том, что вьщелено местоположение бита проверки на четность. Выработка сигнала цикловой синхронизации осуществляется с помощью т-го дешифратора 12.

0

формируется на инверсном выходе триггера. 13, который устанавливается в нулевое состояние сигналами с выхода т-го дешифратора 12, Вывод об утере синфазного приема делается при наличии на прямом выходе триггера 13 единичного сигнала. Установка тригг гера 13 в единичное состояние осуществляется по сигналу с .выхода g (m-1)-го дешифратора 12, который выделяет из регистра 11 сдвига комбинацию, состоящую из одних нулей. Таким образом, на выходе анализатора 2 синфазности формируются три сигнала. На первом выходе формируется сигнал цикловой синхронизации, по которому происходит разделение принимае-мых символов на сообщения. Соответственно на втором и третьем выходах формируются сигнал синфазной и не- синфазной работы устройства. Если учитывать то, что разрядность перво- то регистра 6 сдвига выбрана равной десяти п-раэрядных слов, то значение m следует выбирать равным 12.

Возникновение ошибки в принимаемом еообщении может привести к невыделению бита проверки на четность, в результате чего во втором регистре 9 сдвига происходит стирание единичного символа, указывающего местоположение бита проверки на четность, В этом случае устройство переходит в режим поиска синфазного положения Во все разряды второго регистра 9 сдвига записываются единицы и осуществляется последовательное выделение сигнала цикловой синхронизации (как было указано ранее). Организация и проведение этого режи1-1а связаны с утерей ряда сообщений или организацией их переспроса,Все это

приводит к уменьшению пропускной способности устройства и увеличению

удельного времени нахождения его в режиме фазирования Для исключеьшя влияния ошибок на работу устройстпа введен блок 4 обнаружения ошибок. Для коррекции однократных ошибок введен блок 5 исправления ошибок. При обнаружении ошибки устройство функционирует следуюищм образом. По сигналу о наличии ошибки в принимаемом символе (третий выход декодера

3 биимпульсного сигнала ), поступающему на второй вход блока 5 исправления ошибок, и при синфазт-юй работе устройства (сигнал на втором выходе анализатора 2 синфазности) на выходе первого Элемента И 31 (в блоке 5 исправления ошибок ) формируется си1- нал наличия ошибки, который поступает на четвертый вход блока 4 обнаружения ошибок. По этому сигналу осуществляется установка триггера 25 в единичное состояние, по сигналу с прямого выхода которого разрешается прохо; одение с выхода второго регистра 9 сдвига единичного сигнала (момента четности } при нали- чии ошибки через элемент Н 26 на выход блока. В этом случае исключается

возможность стирания сигнала, указывающего местоположение бита лроверки на четностьр элементом Н 8 при нарушении условия четности в принимаемом

сообщении. Коррекция ошибки осуществляется следующим образом. По сигналу с выхода первого элемента И 31 происходит обнуление и запуск раты второго счетчика 29 импульсов (происходит определение номера искаженного символа в сообщении), сброс и запись единицы в первый счетЧик 28 импульсов. По. сигналу цикловой синхронизации (конец принимаемого сообщения

на . четвертый вход блока осуществляется останов работы счетчиков 28 и 29 импульсов. При обнаружении ошибки в декодере 3 биимпульсного сигнала

в искаженный бит записывается нулевой символ, однако в этом спучае может произойти исправление ошибки (т.е. значение символа записано верно ). Правильрюсть записи в этом случае контролируется с помощью декодера 7. Если на выходе элемента И 8 в этом случае появляется единичный сигнал, то считается, что значение символа вписано верно. В противном

случае на выходе второго элемента И 32 формируется управляющий сигналj по которому в соответствии с показа- . второго счетчика 29 импульсов на одном из выходов дешифратора 30

формируется единичный сигнал j кото - рый и записывается в соответствующий разряд первого регистра 6 сдвига (блок 1 проверки на четностьJ. Если в сообщении обнаружено две и более

ошибок (проверка на четность в этом случае не может быть использована для коррекции ошибок, подсчет числа ошибок происходит с помощью первого счетчика 28 импульсов у происходит

отказ о т коррекции ошибки, сброс

и останов работы второго счетчика 29 импульсов. Потребителю с третьего выхода блока 5 исправления ошибок поступает сигнал о наличии ошибки, которая не корректируется кодом.

Формула изобретения

1. Устройство для синхронизации gg биимпульсного сигнала, содержащее блок проверки на четность и-анализатор синфазности, отличающееся тем, что, с целью уменьшения времени фазирования при одновременном снижении вероятности ошибки, введены блок обнаружения ошибки, блок исправления ошибки и декодер биимпульсного сигнала,.вход которого является информационным входом устройства для синхрониз-ации биимпульсного сигнала, а первый, второй и третий выходы подключены соответственно к синхронизирующим входам ана- лизатора синфазности, блока проверки на четность и блока исправления ошибки, к информационному входу блока проверки на четность и информационному входу блока исправления ошибки, к управляемому входу которого подключен управляющий вход блока обнаружения ошибки и первьш выход блока проверки на четность, к управляющему входу которого подключен первый выход блока исправления ошибки, к входу сигнала цикловой синхронизации которого подключен вход сигнала цикловой синхронизации блока обнаружения о шябки и первый выход анализато- ра синфазности, второй выход которого соединен с вторым синхронизирующим входом блока исправления ошибки, второй выход которого соединен с пер

вым информационным входом блока обна-зо синфазности.

ружения ошибки, к второму информационному входу которого подключен второй выход блока проверки на четность-, к второму информационному входу которого подключен информационный вход анализатора синфазности и выход блока обнаружения ошибки,

2. Устройство по п,1, о т л и - чающееся тем, что блок проверки на четность содержит последовательно соединенные первый регистр сдвига, первые входы которого являются управляющим входом блока проверки на четность, второй вход - информационным входом блока проверки на четност,ь, декодер и элемент И, к второму входу которого подключен выход второго регистра сдвига и второй выход блока проверки на четность, а выход является первым выходом блока проверки на четность, а также последовательно соединенные второй регистр сдвига, синхронизирующий вход кото-: рого подключен к синхронизирую щему входу первого регистра сдвига и явля ется соответствующим входом блока проверки на четность, и дешифратор, выход которого соединен с управляющим входом второго регистра сдвига.

информационньш вход которого является информационным входом блока проверки на четность.

3, Устройство по п.2, отличающееся Тем, что анализатор синфазности содержит регистр сдвига, m дешифраторов (где m 1, 2, 3...) и триггер, входы которого соединены соответственно с выходом т- и (т-1)-го дешифраторов, а выход является вторым выходом-анализатора синфазности, причем регистр сдвига имеет (т-2) группы по п разрядов каждая,, выходы которых соединены с соответствующими входами (т-2)-х дешифраторов, выходы которых а также п-й выход каждой группы соединены с соответствующими входами т-го дешифратора, выход которого является первым выходом анализатора синфазности и подключен к первому входу триггера, к второму входу которого подключен выход l.m-1 )-го дешифратора, входы которого объединены с входами (т-2)-го дешифратора, а первый и второй входы регистра сдвига являются, синхронизирующими и информационным входами анализатора

5

0

5

0

5

4. Устройство по п.1, отличающееся тем, что декодер биимпульсного сигнала содержит дифференцирующий блок, вход которого является входом декодера биимпульсного сигнала, а первый и второй выходы соединены соответственно с первыми входами первого и второго элементов И, выходы которых соединены соответственно с первыми входами триггера и первого элемента ИЛИ, и первым входом третьего элемента ИЛИ и вторым входом- первого элемента ИЛИ, выход которого соединен с первыми - входами- элемента И-НЕ и второго элемента 1-1ЛИ и через линию задержки с вторыми входами элемента И-НЕ и второго элемента ИЛИ, выход которого является вторым выходом декодера биимпульсного сигнала и соединен с первым входом третьего элемента И и через ждушдй мультивибратор с вторыми входами первого- и второго элементов И, к второму входу третьего элемента И подключен выход элемента И- НЕ, а выход третьего элемента И является третьим выходом декодера биим- , пульсного сигнала и подключен к второму входу третьего элемента IfflH

выход которого соединен с вторым вхдом триггера, выход которого является первым выходом декодера биим- пульсного сигнала. .

3. Устройство по п.1, о т л и - чающееся тем, что блок обнружения ошибок содержит элемент И, первый вход которого является первы информационным входом блока обнару- жения ошибки, к второму входу подключен выход триггера, первый и второй входы которого являются соответственно вторым информационным и синхронизирующим входами блока обнаруж НИН.ошибок, а выход элемента И соединен с первым входом элемента 11ПИ, второй вход которого является управляющим входом блока обнаружения ошибок, а выход элемента ИЛИ является выходом блока обнаружения ошибки.

6, -Устройство по п.1, о т л и - чающе.е ся тем, что блок исправления ошибок содержит последова

ф

4/2. J

10

тельно соединенные второй счетчик и дешифратор, выходы которого .являются первым выходом блока обнаружения ошибок, а к управляющему входу через первый вход второго элемента И и инвертор подключен управляющий вход блока исправления ошибок, второй вход второго элемента И является входом цикловой синхронизации блока исправления ошибок и соединен с соответствующими входами первого и второго счетчиков импульсов, к входу сброса которого подключен выход первого счетчика импульсов, к входу синхронизации которого подключен соответствующий вход второго счетчика и является входом сигнала синхронизации блока исправления ошибок, а к объединенным информационным входам первого и второго счетчиков через первый и второй входы элемента И подключе ны соответствующие входы блока исправления ошибок.

ФизЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема биимпульсных сигналов | 1989 |

|

SU1596477A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1406809A2 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ С ЖЕСТКИМИ И МЯГКИМИ РЕШЕНИЯМИ ДЛЯ ДВУХСТУПЕНЧАТОГО КАСКАДНОГО КОДА И МОДУЛЯЦИИ ПО ТИПУ СТЫКА С1-ФЛ | 2024 |

|

RU2834891C1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| СПОСОБ ОЦЕНКИ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2085045C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С ИНТЕГРИРОВАННЫМИ МЯГКИМИ И ЖЕСТКИМИ РЕШЕНИЯМИ | 2011 |

|

RU2450464C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

Изобретение относится к технике связи. Цель изобретения - уменьшение времени фазирования при одновременном снижении вероятности ошибки. Устр-во содержит блок проверки 1 на четность, анализатор 2 синфазности, декодер 3 биимпульсного сигнала, блок 4 обнаружения ошибок и блок 5 исправления ошибок. Передаваемые данные в биимпульсном коде поступают на вход декодера 3, на выходах которого формируются следующие сигналы: двоичная информация, последовательность синхронизирующих импульсов и сигнал наличия ошибки в принимаемом символе. Эти сигналы, поступая на блок проверки 1, анализатор 2 и декодер 3, обеспечивают синхронность работы устр-ва. Для исключения влияния оши- бок на работу устр-ва введен блок обнаружения 4, а для коррекции однократных ошибок - блок исправления 5. Устр-во по пп. 2-6 ф-лы отличается выполнением блока проверки 1, анализатора 2, декодера 3, блока обнаруже- ния 4 и блока исправления 5, даны их ил. 5 з.п. ф-лы, 6 ил. 11 & (Л Од сл о 00 СлЭ

&ь/)(,од1

Фиг.5

Составнт.ель И.Грацианская Редактор Н.Лазаренко Техред М.Ходанич ..Корректор М.Шароши

Заказ 5299/57Тираж 636Подписное

ВНШШИ Государственного комйтет а СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 6

| Патент США № 4412329, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-11-07—Публикация

1985-10-02—Подача