СП СП

to

00

со ел

Изобретение относится к радиотехнике и может быть использовано в асинхронно-адресных системах связи.

Цель изобретения - увеличение аи- самбля формируемых дискретно-частотных сигналов.

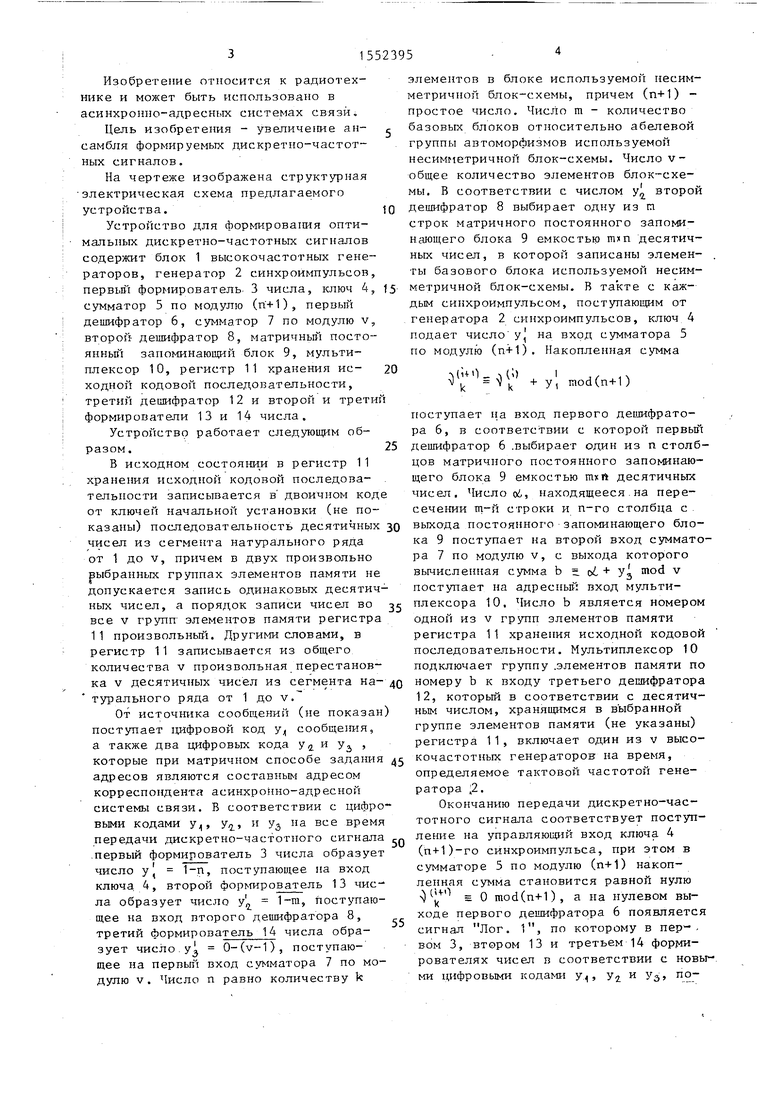

На чертеже изображена структурная электрическая схема предлагаемого устройства.

Устройство для формирования оптимальных дискретно-частотных сигналов содержит блок 1 высокочастотных генераторов, генератор 2 синхроимпульсов, первый формирователь 3 числа, ключ 4, сумматор 5 по модулю (n-t-1), первый дешифратор 6, сумматор 7 по модулю v, второй дешифратор 8, матричный постоянный запоминающий блок 9, мультиплексор 10, регистр 11 хранения ис- ходной кодовой последовательности, третий дешифратор 12 и второй и третий формирователи 13 и 14 числа.

Устройство работает следующим образом.

В исходном состоянии в регистр 1 1 хранения исходной кодовой последовательности записывается в двоичном коде от ключей начальной установки (не показаны) последовательность десятичных чисел из сегмента натурального ряда от 1 до v, причем в двух произвольно выбранных группах элементов памяти не допускается запись одинаковых десятичных чисел, а порядок записи чисел во все v групп элементов памяти регистра 11 произвольный. Другими словами, в регистр 11 записывается из общего количества v произвольная перестановка v десятичных чисел из сегмента на- турального ряда от 1 до v.

От источника сообщений (не показан поступает цифровой код уА сообщения, а также два цифровых кода у4 и уа , которые при матричном способе задания адресов являются составным адресом корреспондента асинхронно-адресной системы связи. В соответствии с цисЪро выми кодами у,, уг, и у на все время передачи дискретно-частотного сигнала первый формирователь 3 числа образует число у , поступающее на вход ключа 4, второй формирователь 13 числа образует число у г 1-ш, поступающее на вход второго дешифратора 8, третий формирователь 14 числа образует число у 0-(v-1), поступающее на первый вход сумматора 7 по модулю v. Число п равно количеству k

элементов в блоке используемо несимметричной блок-схемы, причем (п+1) - простое число. Число m - количество базовых блоков относительно абелевой группы автоморфизмов используемой несимметричной блок-схемы. Число v- общее количество элементов блок-схемы. В соответствии с числом у второй дешифратор 8 выбирает одну из гл строк матричного постоянного запоминающего блока 9 емкостью тип десятичных чисел, в которой записаны элементы базового блока используемой несимметричной блок-схемы. В такте с каждым синхроимпульсом, поступающим от генератора 2 мшхроимпулъсов, ключ 4 подает число yj на вход сумматора 5 по модулю (п+1). Накопленная сумма

ui+0 ч (ilI , , ..

v k N k + у, mod(n+1)

поступает на вход первого дешифратора 6, в соответствии с которой первый дешифратор 6 выбирает один из п столбцов матричного постоянного запоминающего блока 9 емкостью тхЛ десятичных чисел. Число oi, находящееся на пересечении m-ft строки и п-го столбца с выхода постоянного запоминающего блока 9 поступает на второй вход сумматора 7 по модулю v, с выхода которого вычисленная сумма b cxL + у mod v поступает на адресный вход мультиплексора 10, Число b является номером одной из v групп элементов памяти регистра 11 хранения исходной кодовой последовательности. Мультиплексор 10 подключает группу .элементов памяти по номеру b к входу третьего дешифратора 12, который в соответствии с десятичным числом, хранящимся в выбранной группе элементов памяти (не указаны) регистра 11, включает один из v высокочастотных генераторов на время, определяемое тактовой частотой генератора ,2.

Окончанию передачи дискретно-частотного сигнала соответствует поступление на управляющий вход ключа 4 (п+1)-го синхроимпульса, при этом в сумматоре 5 по модулю (п+1) накопленная сумма становится равной нулю

) 0 mod(n+1), а на нулевом выкходе первого дешифратора 6 появляется

сигнал Лог. 1, по которому в первом 3, втором 13 и третьем 14 формирователях чисел в соответствии с новыми цифровыми кодами у, уг и уй, поступающими от источника сообщений, обрадуются новые числа у| , у, у .

При отсутствии сообщений от источника сообщений десятичные числа у(, У 2 и у3 на пыходах формирователей 3, 14 и 13 чисел равны нулю, накоштеная сумма в сумматоре 5 по модулю (п+1), равна нулю, сигнал Лог. 1 присутст- вует на нулевом выходе первого дешифратора 6, на обоих входах сумматора 7 по модулю v присутствуют десттичные числа, равные нулю. Десятичное число нуль присутствует на входе третьего дешифратора 12, на нулевом входе которого (не показан) присутствует сигнал Лог. 1, поэтому все v высокочастотных генераторов блока 1 высокочастотных генераторов выключены. В этом случае можно осуществить смену используемой оптимальной системы дискретно-частотных сигналов путем .записи от ключей начальной установки (не показаны).

Формула изобретения

Устройство для формирования оптимальных дискретно-частотных сигналов, содержащее блок высокочастотных генераторов, первый формирователь числа, выход которого соединен с информационным входом ключа, выход которого подключен к входу сумматора по модулю (п+1), выход которого соединен с входом первого дешифратора, нулевой выход которого подключен к управляющему входу первого формирователя числа и к управляющему входу генератора синхроимпульсов, выход которого подключен к управляющему входу ключа, при

0 g 0 5

0

5

0

этом информационный вход первого формирователя числа является перпым информационным входом устройства, выходами которого являются выходы блока высокочастотных генераторов, отличающееся тем, что, с целью увеличения ансамбля формируемых дискретно-частотных сигналов, введены два дешифратора, два формирователя числа, сумматор по модулю v, матричный постоянный запоминающий блок, мультиплексор и регистр хранения исходной кодовой последоватепьности, выходы которого соединены с информационными входами мультиплексора, адресный вход которого подключен к выходу сумматора по модулю v, первый вход которого подключен к выходу матричного постоянного запоминающего блока, первый вход которого подключен к выходу первого дешифратора, нулевой выход которого соединен с управляющим входом второго формирователя числа и с управляющим входом третьего формирователя числа, выход которого соединен с вторым входом сумматора по модулю v, выход второго формирователя числа через второй дешифратор подключен к второму входу матричного постоянного запоминающего блока, выход мультиплексора соединен с входом третьего дешифратора, выходы которого подключены к входам блока высокочастотных генераторов, при этом информационные входы второго и третьего формирователей числа являются соответственно вторым и третьим информационными входами устройства, четвертыми информационными входами которого являются входы регистра хранения исходной кодовой последовательности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь квазиоптимальных дискретно-частотных сигналов | 1988 |

|

SU1578836A1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для управления автономным инвертором | 1990 |

|

SU1810973A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ СИСТЕМ ДВУКРАТНЫХ ПРОИЗВОДНЫХ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 2014 |

|

RU2553057C1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение ансамбля формируемых дискретно-частотных сигналов. Устройство для формирования оптимальных дискретно-частотных сигналов содержит блок 1 ВЧ-генераторов, генератор 2 синхроимпульсов, формирователь 3 числа, ключ 4, сумматор 5 по модулю (N + 1) и дешифратор 6. Цель достигается введением сумматора 7 по модулю V, дешифраторов 8 и 12, матричного постоянного запоминающего блока 9, мультиплексора 10, регистра 11 хранения исходной кодовой последовательности и формирователей 13 и 14 числа, с помощью которых включается один из V ВЧ-генераторов блока 1 на время, определяемое тактовой частотой генератора 2. 1 ил.

Авторы

Даты

1990-03-23—Публикация

1988-05-26—Подача