У1

Ч

эо эо до

&

3

Изобретение относится к электросвязи и может быть использовано в асинхронно-адресных системах связи.

Цель изобретения - увеличение числа формируемых сигналов.

На чертеже представлена структур ная электрическая схема формирователя квазиоптимальных дискретно- частотных сигналов.

Формирователь квазиоптимальных дискретно-частотных сигналов содержит блок 1 ключей, генератор 2 синхроимпульсов, первьй сумматор 3, первый дешифратор 4 и блок 5 высокочастотных генераторов, а также блок 6 буферных регистров, первый и второй постоянные запоминающие блоки 7 и 8, элемент И9, счетчик 10 с второго по пятый дешифраторы 11-1 второй сумматор 15, регистр 16 и мультиплексор 17.

Формирователь квазиоптимальных дискретно-частотных сигналов работает следующим образом

При включении источника питания (не показан) производится установка в нулевое состояние регистра 16 и счетчика 10 по модулю (k+1). При этом на первом выходе второго дешиф

ратора 11 имеется сигнал 1, от которого блок 1 ключей закрыт. На выходах первого дешифратора 4 имеется число, равное нулю, при котором на всех его выходах, кроме нулевого имеется сигнал О. При этом все U генераторов блока 5 высокочастотных генераторов выключены. Генератор 2 синхроимпульсов вырабатывает импульсы, поступающие на вход элемента И9 Так как на входах блока 6 буферных регистров десятичные числа равны нулю, то на пятом выходе блока 6 буфеных регистров присутствует сигнал О и на вход счетчика 10 импульсы от генератора 2 синхроимпульсов не поступают.

Затем в регистр 16 записывается в двоичном коде последовательность десятичных чисел из сегмента натурального ряда от 1 до U, причем в двух произвольно выбранных группах ячеек не допускается запись одинаковых чисел, порядок записи которых произволен, т, е. в регистр 16 записывается из общего количества U чисел произвольная выборка U десятичных чисел.

От источника сообщений поступа- ют два цифровых кода Y( 0 - (U-1)

и 1 - m, которые при матричном способе значения адресов являются составным адресом корреспондента.

а также два цифровых кода (k-1) и Уд 1 - (k-1), определяющие при табличном способе задания М-ичный символ информации, передаваемый корреспонденту асинхронно-адресной сис

темы связи, где m - число базовых блоков циклической схемы Штейнера S(4, k, U); M - объем алфавита, равный (k-1)xk0 При этом с пятого выхода блока 6 буферных регистров поступает сигнал 1 и импульсы с генератора 2 синхроимпульсов начинают поступать на вход счетчика 10. По первому импульсу счетчик 10 из нулевого состояния переходит в первое, и сигнал О с первого выхода второго дешифратора 11 открывает блок 1 ключей и переводит блок 6 буферных регистров из режима приема информации в режим хранения цифровых кодов Y( -Y на все время передачи дискретно-частотного сигнала. Цифровой код Y1 0 - (U-1) поступает на вторые входы второго сумматора 15 по модулю U. Цифровой код Y 1 - m поступает на вторые входы пятого дешифратора 14, который выбирает одну из m строк второго постоянного запоминающего блока 8 емкостью m x k деся- тичных чисел. Цифровой код (k-1 поступает на вторые входы первого сумматора 3 по модулю k. Цифровой код 1 - (k-1) поступает на входы третьего дешифратора 12, который выбирает одну из (k-1) строк первого постоянного запоминающего блока 7 емкостью (k-1) xk десятичных чисел.

Под действием каждого импульса счетчик 10 из состояния L переходит в состояние (L+1), после чего на (Ъ+1)-м выходе третьего дешифратора 11 появляется сигнал ,

Цифровой код h, находящийся в первом постоянном запоминающем блоке 7 на пересечении -и строки и (L+D-ro столбца, определяется по формуле

h 5 Y4 L mod k, (1)

где Y - I + (k - 1); L - 0 + (k - 1); k - простое число; г - наименьшее из чисел, взаимно простых с числом (k-1). С выходов первого постоянного за- -поминающего блока 7 цифровой код h

поступает на первые входы первого сумматора 3 ио модулю k, с выходов которого вычисленная сумма

nsh + Y, mod k (2)

поступает на входы четвертого дешифратора 13, которьй выбирает во втором постоянном запоминающем блоке 8 емкостью m x k десятичных чисел из k столбцов одно из чисел с порядковым номером По Число L, находящееся на пересечении m-й строки и n-го столбца, с выходов второго постоянного запоминающего блока 8 поступает на первые входы второго сумматора 15 по модулю U, с выходов которого вычисленная сумма

1- L + Y

mod U

поступает на управляющие входы мультиплексора 17, Число 1 является номером одной из U групп ячеек регистра 16, в которых хранятся исходные кодовые последовательности. В результате этого информация, хранящаяся в указанной группе ячеек регистра 16, через мультиплексор 17 и открытый блок 1 ключей воздействует на входы первого дешифратора 4, что вызывает включение соответствующего высокочастотного генератора, входящего в блок 5 высокочастотных генераторов, на время, определяемое тактовой частотой генератора 2 синхроимпульсов.

Окончанию передачи дискретно-частотного сигнала соответствует поступление на вход счетчика 10 (k+0-го синхроимпульса, по которому счетчик 10 по модулю (k-t-1) переходит в нулевое состояние о Сигнал 1 с первого выхода второго дешиЛратора 11 поступает на управляющий вход блока 6 буферных регистров управляющий вход блока 1 ключей, которьй запирается, вызывая прекращение работы блока 5 высокочастотных генераторов.

Блок 6 буферных регистров осуществляет прием новых цифровых кодов Y, - Y4, поступающих от источника сообщений. Под воздействием очередного синхроимпульса цикл работы формирователя по передаче дискретно- частотного сигнала повторяется.

При отсутствии сигнала от источника сообщений десятичные числа в двоичном коде Y, - Y4 на выходах блока 6 буферных регистров равны нулю, все U высокочастотные генераторы блока 5 выключены, В этом случае мож10

5788366

но осуществить смеку испольэуемой квазиоптимальной системы дискретно- частотнык сигналов путем записи (через управляющие входы) в регистр 16 5 новой кодовой последовательности чисел из сегмента натурального ряда от 1 до U, представляющей собой другую перестановку U чисел из U возможных перестановоко

Таким образом, в предлагаемом устройстве в качестве адреса корреспондента асинхронно-адресной системы связи используется набор k частот, номера которых взаимно однозначно соответствуют элементам одного блока циклической 4-схемы Штейнера, Элементы базовых блоков размещены во втором постоянном запоминающем блоке 8, а элементы производного блока вычисляются относительно выбранного базового блока.

j L,, L4,.. o,L| | (3)

при помощи второго сумматора 15 по модулю U по правилу

15

20

25

JL, +Y, ,LL+Y, , .. . ,L((+Y, mod U,

(4)

0

Каждый из М-ичных символов передаваемого корреспонденту сообщения

5

0

определяется порядком следования выбранных k частот (элементов ьрсиз- водного блока)0 Перестановка элементов производного блока 4-схемы Штей- нера осуществляется по известному алгоритму синтеза квазиоптимальной композиционной системы дискретно- частотных сигналов

n Уд./2 + Y3 mod k (5)

Арифметическая операция сложения по модулю k выпопняется в реальном масштабе времени при помощи сумматора 3 по модулю k, а результат операций умножения и возведения в степень по модулю числа k вычислен заблаговременно и записан в первый постоянный запоминающий олок 7.

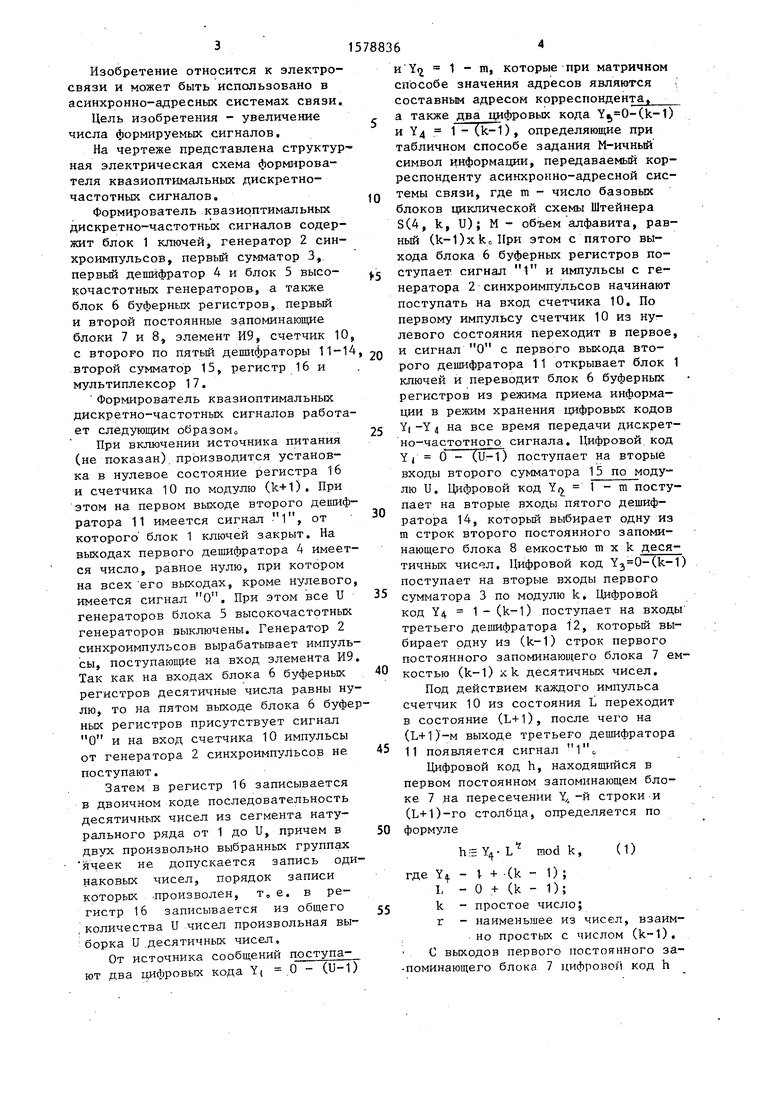

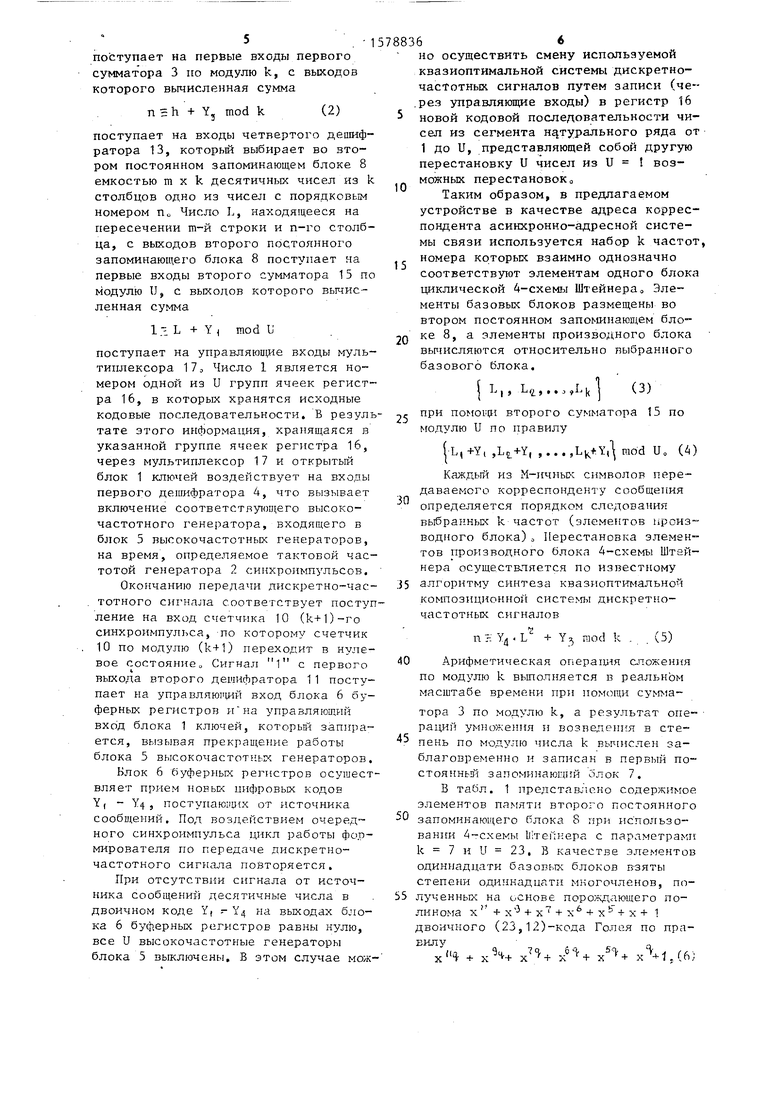

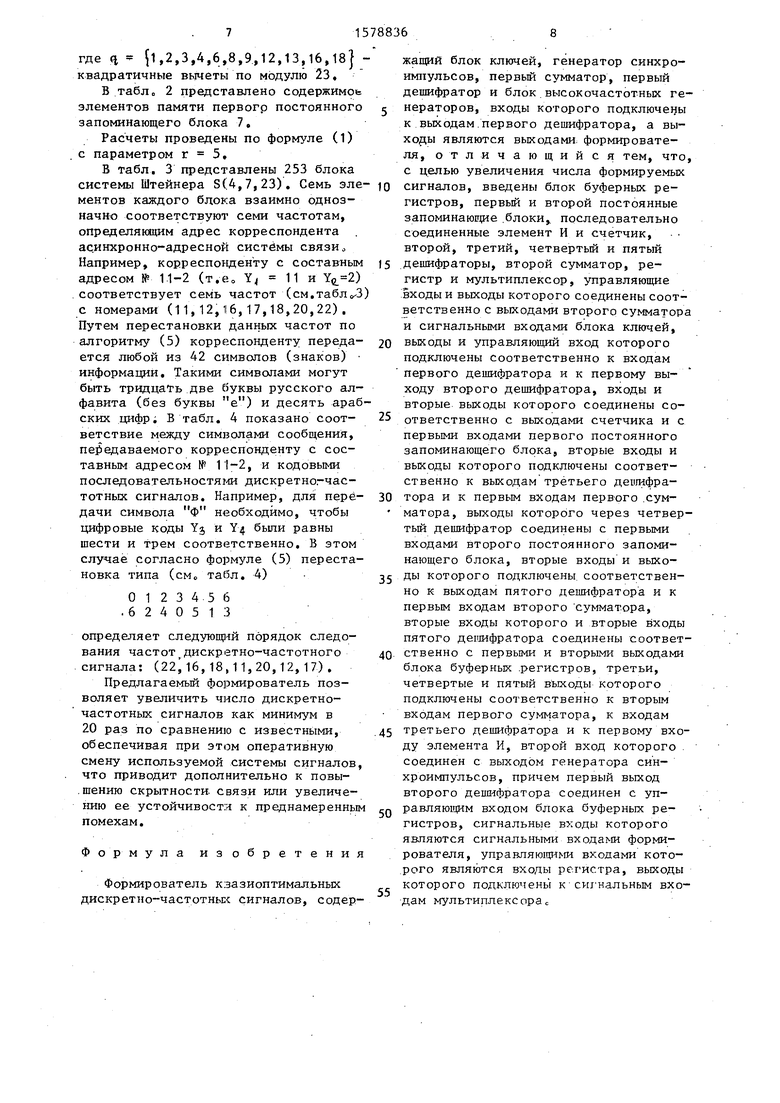

В табл. 1 представлено содержимое элементов памяти второго постоянного

О запоминающего блока 8 при использовании 4 схемы 11,тепнера с параметрами k 7 и U 23. В качестве элементов одиннадцати базовых блоков взяты степени одиннадцати многочленов, по5 лученных на основе порождающего полинома хг+х 3 + х7 + х6 + хь + х + 1 двоичного (23,12)-кода Голая по правилу

Х«Ч + XV Х7П ХИ + X5n .(fij

5

где (i - (1,2,3,4,6,8,9,12,13,16,18j - квадратичные вычеты по модулю 23,

В табло 2 представлено содержимоь элементов памяти первогр постоянного запоминающего блока 7.

Расчеты проведены по формуле (1) с параметром г 5.

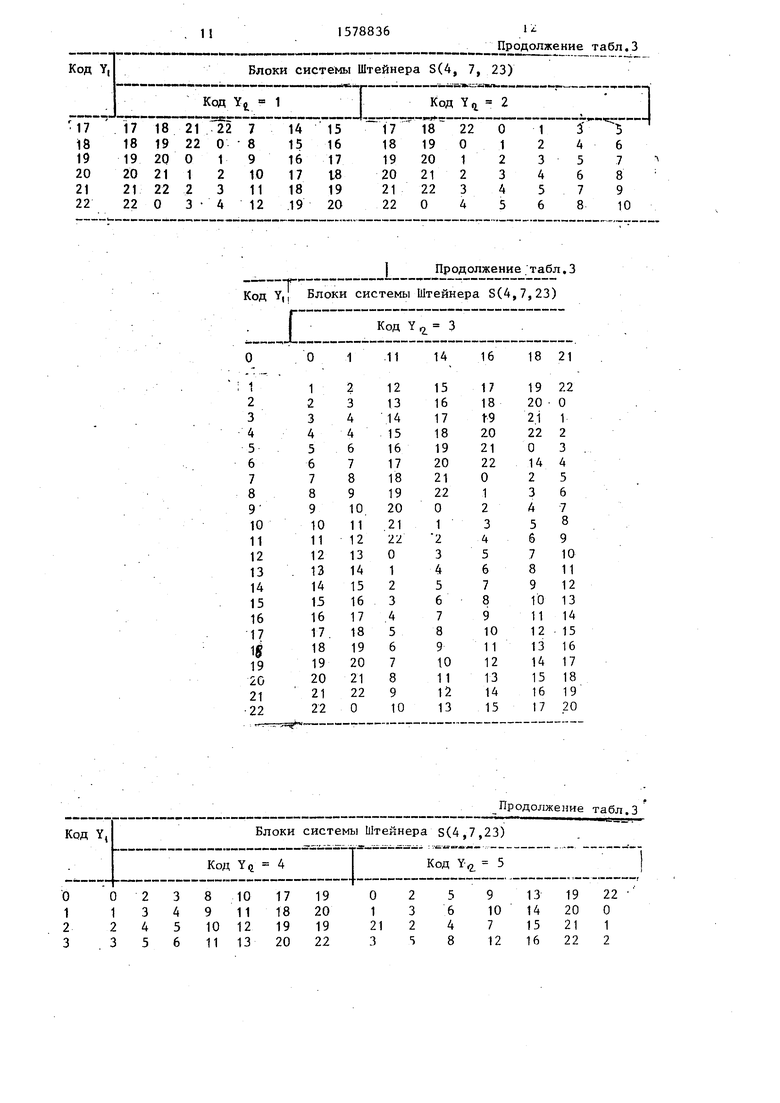

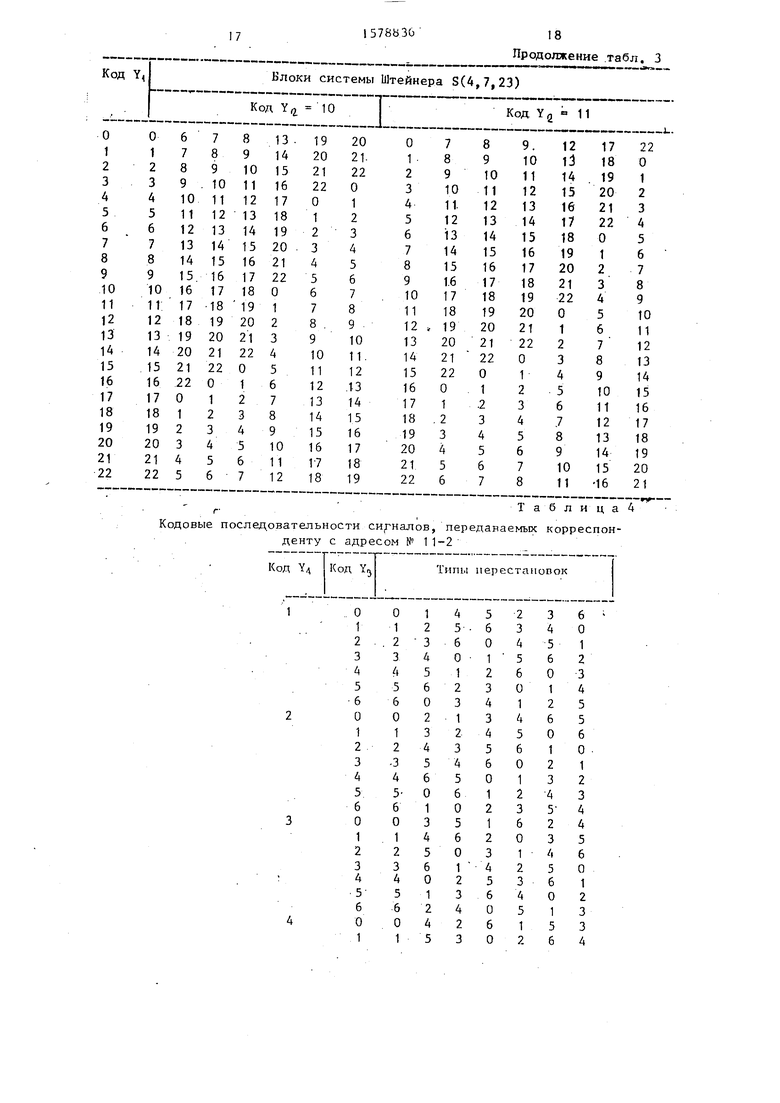

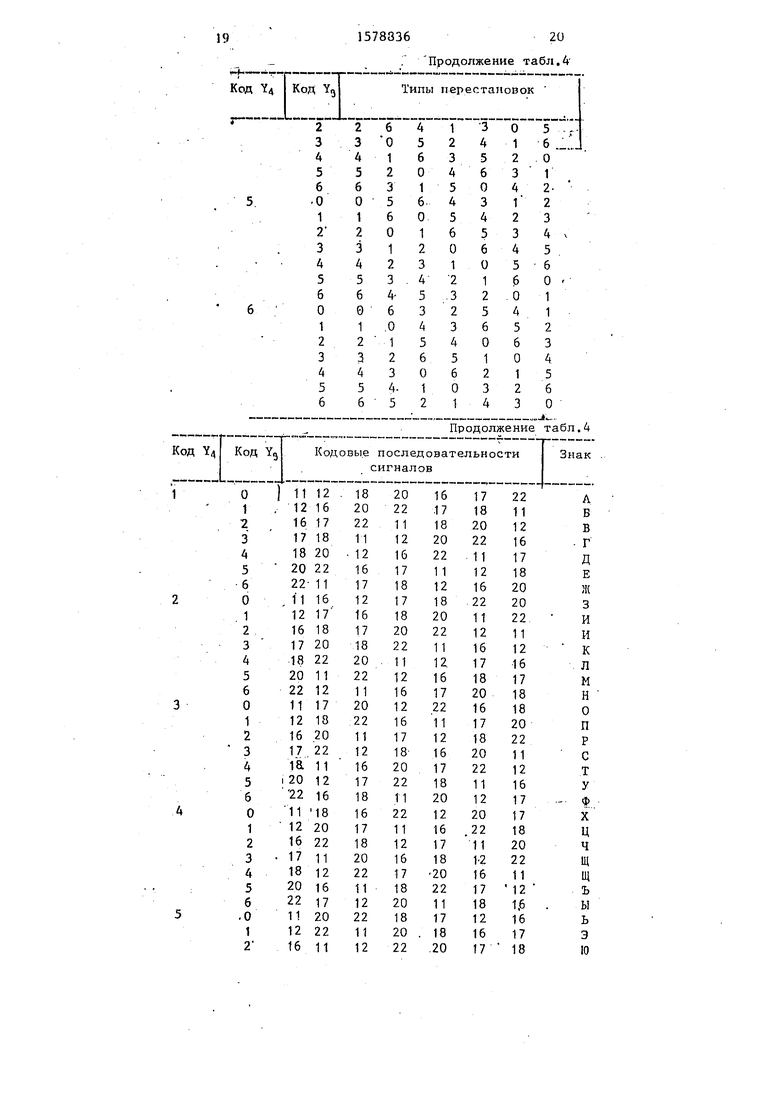

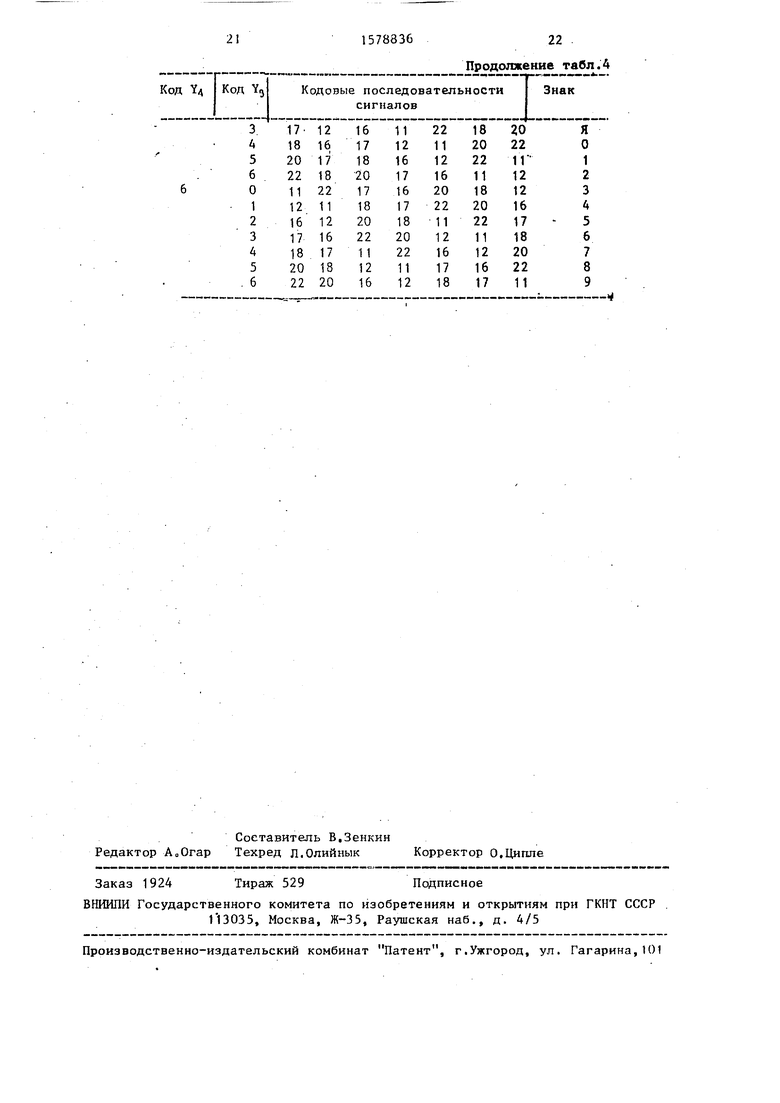

В табл. 3 представлены 253 блока системы Штейнера 8(4,7,23). Семь элементов каждого блока взаимно однозначно соответствуют семи частотам, определяющим адрес корреспондента асинхронно-адресной системы связи„ Например, корреспонденту с составным адресом № 11-2 (т.е„ Y, 11 и ) соответствует семь частот (см. с номерами (11,12,16,17,18,20,22). Путем перестановки данных частот по алгоритму (5) корреспонденту передается любой из 42 символов (знаков) информации. Такими символами могут быть тридцать две буквы русского алфавита (без буквы е) и десять арабских цифр; В табл. 4 показано соответствие между символами сообщения, передаваемого корреспонденту с составным адресом № 11-2, и кодовыми последовательностями дискретно.-час- тотных сигналов. Например, для передачи символа Ф необходимо, чтобы цифровые коды УЗ и Ґ4 были равны шести и трем соответственно, В этом случае согласно формуле (5) перестановка типа (см„ табл. 4)

О 1 2 3 4 5 б .6240513

определяет следующий порядок следования частот tдискретно-частотного сигнала: (22J16,18,11,20,12,17).

Предлагаемый формирователь позволяет увеличить число дискретно- частотных сигналов как минимум в 20 раз по сравнению с известными, обеспечивая при этом оперативную смену используемой системы сигналов, что приводит дополнительно к повышению скрытности связи или увеличению ее устойчивостл к преднамеренным помехам.

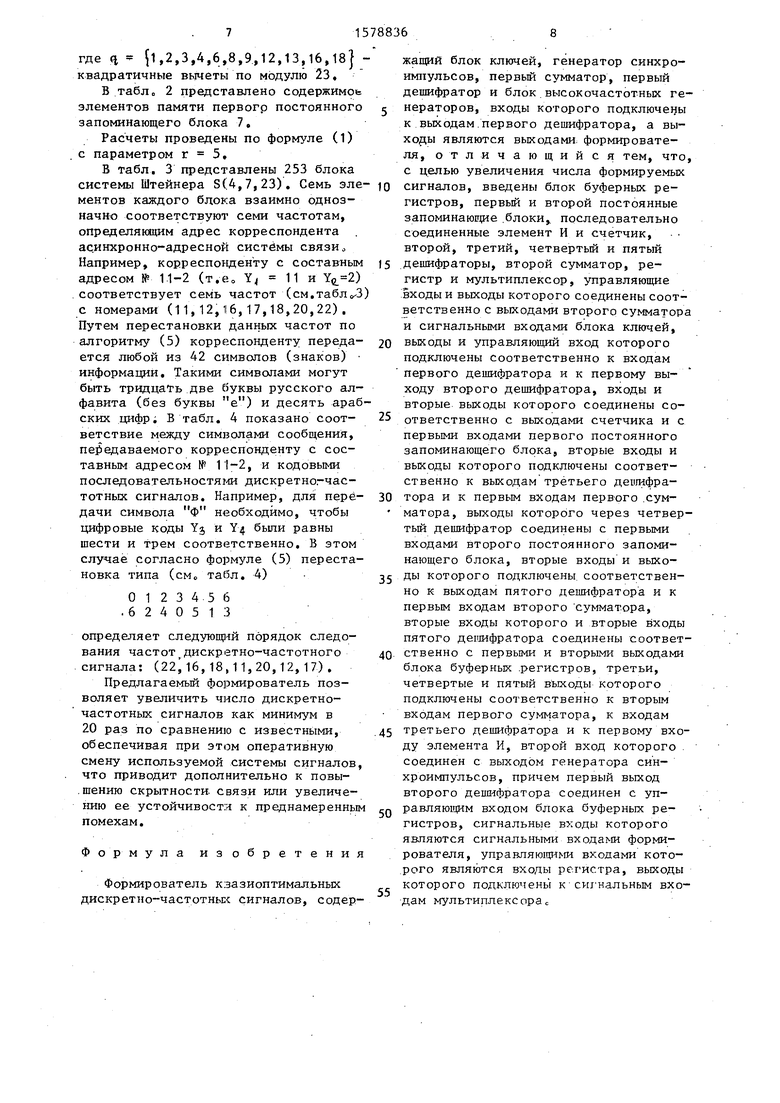

Формула изобретения

Формирователь к.зазиоптимальных дискретно-частотных сигналов, содержащий блок ключей, генератор синхроимпульсов, первый сумматор, первый дешифратор и блок высокочастотных генераторов, входы которого подключены к выходам первого дешифратора, а выходы являются выходами формирователя, отличающийся тем, что, с целью увеличения числа формируемых

сигналов, введены блок буферных регистров, первый и второй постоянные запоминающие блоки, последовательно соединенные элемент И и счетчик, второй, третий, четвертый и пятый

5 дешифраторы, второй сумматор, регистр и мультиплексор, управляющие Входы и выходы которого соединены соответственно с выходами второго сумматора и сигнальными входами блока ключей,

0 выходы и управляющий вход которого подключены соответственно к входам первого дешифратора и к первому выходу второго дешифратора, входы и вторые выходы которого соединены со5 ответственно с выходами счетчика и с первыми входами первого постоянного запоминающего блока, вторые входы и выходы которого подключены соответственно к выходам третьего дешифра0 тора и к первым входам первого сум- матора, выходы которого через четвертый дешифратор соединены с первыми входами второго постоянного запоминающего блока, вторые входы и выхо5 ды которого подключены соответственно к выходам пятого дешифратора и к первым входам второго сумматора, вторые входы которого и вторые входы пятого дешифратора соединены соответ0 ственно с первыми и вторыми выходами блока буферных регистров, третьи, четвертые и пятый выходы которого подключены соответственно к вторым входам первого сумматора, к входам

5 третьего дешифратора и к первому входу элемента И, второй вход которого соединен с выходом генератора синхроимпульсов, причем первый выход второго дешифратора соединен с упQ равляющим входом блока буферных регистров, сигнальные входы которого являются сигнальными входами формирователя, управляющими входами которого являются входы регистра, выходы которого подключены к сигнальным вхо5

дам мультиплексора.

19

157833620

Продолжение табл.4

21

1578836

22 Продолжение табл.А

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования оптимальных дискретно-частотных сигналов | 1988 |

|

SU1552395A1 |

| Цифровой обнаружитель-измеритель частоты | 1989 |

|

SU1797127A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Прибор для измерения частотных характеристик | 1986 |

|

SU1335935A1 |

| Устройство дуплексной передачи и приема сигналов | 1987 |

|

SU1515375A1 |

| НЕЙРОВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2553098C2 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| Устройство для предварительной фильтрации входных сигналов узкополосных цифровых фильтров | 1990 |

|

SU1739481A1 |

| СПОСОБ И УСТРОЙСТВО ОПРЕДЕЛЕНИЯ КООРДИНАТ ИСТОЧНИКА РАДИОИЗЛУЧЕНИЯ | 2005 |

|

RU2283505C1 |

Изобретение относится к электросвязи и может быть использовано в асинхронно-адресных системах связи. Цель изобретения - увеличение числа формируемых сигналов. Для достижения цели в формирователь введены блок 6 буферных регистров, первый и второй постоянные запоминающие блоки 7 и 8, элемент И 9, счетчик 10, второй-пятый дешифраторы 11 - 14, второй сумматор 15, регистр 16 и мультиплексор 17. Блок 6 буферных регистров осуществляет прием цифровых кодов от источника сообщения. В качестве адреса корреспондента используется набор частот, элементы базовых блоков размещены во втором постоянном запоминающим блоком 8, а элементы производного блока вычисляются во втором сумматоре 15. Арифметическая операция сложения по модулю K выполняется в реальном масштабе времени в первом сумматоре 3, а результат арифметических вычислений записи - в первом постоянном запоминающим блоке 7. Обеспечивается оперативная смена системы сигналов при значительном увеличении числа дискретно-частотных сигналов. 1 ил.,4 табл.

Составитель В.Зенкин Редактор А„0гар Техред л.Олийнык Корректор О.Цигше

Заказ 1924

Тираж 529

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г.Ужгород, ул. Гагарина,101

Подписное

| УСТРОЙСТВО ФОРМИРОВАНИЯ АНСАМБЛЯ ЧАСТОТНО- ВРЕМЕННЫХ СИГНАЛОВ | 0 |

|

SU362437A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-07-15—Публикация

1988-09-28—Подача