Данное изобретение относится к вычислительной технике.

Системы управления подвижными объектами как авиационной, так и ракетно-космической техники, а также мобильных робототехнических комплексов в качестве одного из основных звеньев включают подсистему инерциальной навигации, которая традиционно создавалась на основе гироскопической платформы. Однако ограниченный диапазон изменения угловых положений объекта практически исключает ее использование для высокоманевренных объектов. В связи с этим в последнее время все большее распространение получают бескарданные инерциальные системы (БИНС), в которых отсутствуют механические гироскопы, задающие базовую ориентацию инерциальной системы координат, и средства силовой стабилизации с многочисленными жгутами проводов, ограничивающими угловое перемещение жестко связанного с конструкцией объекта управления корпуса платформы.

В БИНС инерциальная система координат рассчитывается математически бортовыми вычислительными устройствами по информации, поступающей от акселерометров и датчиков угловых скоростей, в качестве которых используют кольцевые лазерные датчики - кольцевые лазерные гироскопы или волоконно-оптические гироскопы. Независимо от типа датчика требуется высокоскоростная обработка информации об угловых скоростях и ее пересчет в инерциальную систему координат. В основе этих преобразований лежат матричные вычисления, где в качестве элементов матриц используются тригонометрические функции типа sinx и cosx. Не смотря на существенный прогресс в области создания бортовых цифровых вычислительных машин (БЦВМ) их производительности оказывается недостаточно для решения задач БИНС, так как программное вычисление тригонометрической функции занимает существенное время (несколько миллисекунд), а требуется за 1 миллисекунду сформировать полную трехкоординатную инерциальную систему. В связи с этим возникает необходимость введения в состав БЦВМ или дополнительно к ней специализированных вычислительных устройств, ориентированных на решение в требуемое время задач БИНС, Эти устройства должны быть ориентированы в первую очередь на быстрое вычисление тригонометрических функций и матричные вычисления. Рядом специалистов в последнее время для вычисления функций одной или нескольких переменных предлагается использовать нейронные сети. Данное направление представляется достаточно перспективным для модернизации БЦВМ, с целью ускорения решения задач БИНС. Общеизвестно, что тригонометрические функции sinx и cosx могут быть представлены полиномом, представляющим сумму членов различных степеней переменной х с соответствующими коэффициентами. Для быстрой реализации вычислений в этом случае применимы нейронные сети, в которых необходимо реализовать быстрое суммирование и умножение, а «обучение» сети вести путем записи в память вычислителей соответствующих вычисляемой функции коэффициентов полинома. По нейронным вычислителям известны предложения (См. статью А.Н. Горбань «Обобщенная апроксимационная теорема и вычислительные возможности нейронных сетей» / Сибирский журнал вычислительной математики 1998, Т1 №1, стр.12-24), где на рисунках (рис.1 - рис.4) приведены примеры построения компонентов нейронных сетей на основе сумматоров с набором весовых коэффициентов на входе. Однако отсутствие в их составе аппаратурных умножителей и средств задания коэффициентов для «обучения» сети, что является обязательным при настройке вычисления конкретной функции, не позволяет использовать их для создания специализированных вычислителей БИНС. Некоторые решения по компонентам нейронных сетей приведены в другом источнике (См. Л.Н. Ясинецкий «Введение в искусственный интеллект» Учебн. пособие для ВУЗов, 2 издание. Изд. «Академия»), где на стр.29 приведено описание нейрона Мак-Каллона, Питтса на базе нескольких компонентов, содержащих сумматор произведений переменной и коэффициентов, и элементы И, ИЛИ, НЕ). Однако отсутствие умножителей и средств задания коэффициентов для «обучения» сети также не позволяет использовать эти решения для выполнения поставленной задачи: быстрого вычисления тригонометрических функций.

Наиболее полно задача создания вычислителей, на основе принципов нейросетей решена в изобретении «Нейропроцессор» (См. патент RU №2473126, от 20.01.2013), который можно принять за прототип. Известный нейропроцессор содержит блок связи (БС) с БЦВМ верхнего уровня системы автоматического управления, блок микропрограммного управления (БМУ) и набор умножителей с сумматором. Однако в данном изобретении полностью не решена задача быстрых матричных вычислений, являющихся основой алгоритмов БИНС, а также задача работы вычислителя в составе систем управления изделиями ракетно-космической техники (в частности космическими аппаратами и робототехническими комплексами, предназначенными для работы в экстремальных условиях(широкий диапазон изменения температуры окружающей среды от -60 до +125 градусов по Цельсию, механических воздействиях в виде ударов и широкополосной вибрации) и полях ионизирующего излучения, космического пространства, импульсных излучений при вспышках на Солнце, авариях ядерно-энергетических установок и направленном противодействии, вызывающих кратковременные сбои в работе аппаратуры и параметрические изменения электрофизических характеристик полупроводниковых структур, являющихся основой БИС, на которых реализуются компоненты процессора, и вызывающих изменение быстродействия БИС, что в итоге делает процессор неработоспособным и не позволяет использовать в полной мере возможности нейросетевых структур при решении задач БИНС в составе систем автоматического управления изделиями и объектами ракетно-космической техники и в частности космическими аппаратами, а также робототехническими комплексами, предназначенными для работы в экстремальных условиях и полях ионизирующего излучения.

Для систем управления космическими аппаратами с длительным временем работы существует также задача нейтрализации отказов, вызванных естественным старением аппаратуры и потоком тяжелых заряженных частиц.

В связи с этим при использовании цифровых вычислительных устройств в системах автоматического управления такими объектами и комплексами требуется нейтрализации отказов как катастрофических, вызванных естественным старением аппаратуры и потоком тяжелых заряженных частиц, так и параметрическими изменениями в материалах полупроводников из-за перепадов температуры и дозовых эффектов в интегральных микросхемах, на основе которых создаются современные бортовые вычислительные устройства. Все это требует применения новых решений в части построения бортовых вычислительных устройств, ориентированных на использование в системе управления с БИНС. Для решения поставленных задач предлагается использовать ориентированный на решение задач БИНС

НЕЙРОСЕТЕВОЙ ВЫЧИСЛИТЕЛЬ (далее по тексту Нейровычислитель или просто Вычислитель).

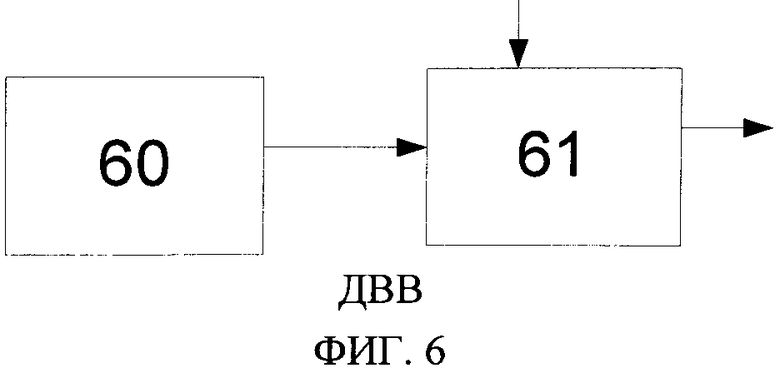

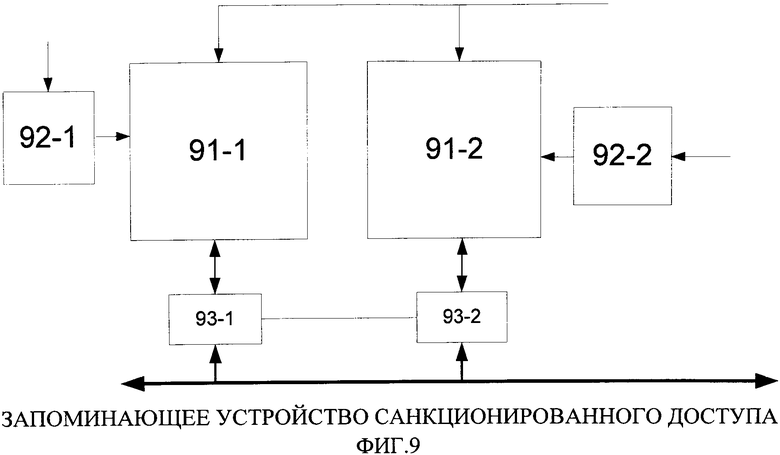

В состав вычислителя входят блок связи (БС), связанный магистральной линией с запоминающим устройством (ЗУ) и запоминающим устройством санкционированного доступа, блокирующий вход которого подключен к выходу датчика внешнего воздействия. Выходы БС подключены к блоку микропрограммного управления (БМУ) и установочному входу источника вторичного электропитания (ИВЭП). К магистральной линии подключены первый и второй блоки матричных нейропроцессоров (БНП), входы которых подключены к выходам БС, а их выходы подключены к операционному устройству (ОУ), содержащему последовательно включенные умножитель и сумматор. Выход ОУ подключен к ЗУ, хранящему результирующую матрицу вычислений, содержимое которой через БС может считываться БЦВМ, так как магистральный мультиплексный вход-выход БС является входом-выходом вычислителя, подключенным к БЦВМ. Выходы БМУ подключены к управляющим входам всех цифровых компонентов вычислителя.

Кроме того силовой вход ИВЭП является силовым входом вычислителя, а установочный вход ИВЭП подключен к установочному выходу БС.

ИВЭП содержит модуль постоянного питания (МПП) и модуль импульсного питания (МИП), силовой вход которых является силовым входом источника, установочный вход которого является одноименным входом МПП и формирователя синхроимпульсов (ФСИ), три управляющих выхода которого подключены к управляющим входам МИП, а выходы постоянного и импульсного питания модулей, и синхронизирующие выходы ФСИ являются выходами постоянного и импульсного питания и синхроимпульсов источника питания.

Каждый БНП содержит девять нейропроцессоров, образующих матрицу с размерностью 3×3. Вход каждого нейропроцессора подключен в выходу устройства связи с БЦВМ, а магистральными входами-выходами нейропроцессоры подключены к дублированной магистрали, являющейся внешней магистралью блока.

БМУ содержит базовый регистр кода операции, базовый регистр признаков, входы которого являются входами признаков блока, базовый счетчик адреса и базовый регистр смещения, установочные входы которых являются входом блока, подключенным к выходу БС, а их выходы образуют адресную шину, подключенную к входу базового микропрограммного запоминающего устройства (БМПЗУ), выходы которого являются выходами блока, а дополнительные выходы БМПЗУ подключены к входам базового регистра смещения.

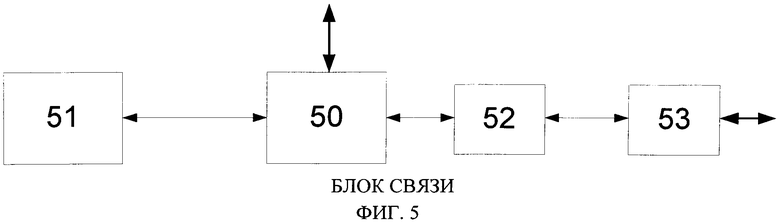

Блок связи содержит процессор, вход-выход которого является магистральным входом-выходом блока. Через первую двунаправленную связь к процессору подключено связное запоминающее устройство, а через вторую двунаправленную связь и через кодирующе-декодирующее устройство процессор подключен к приемно-передающему устройству магистральной мультиплексной лини связи, являющейся линией связи блока и нейровычислителя в целом с подсистемами верхнего уровня и БЦВМ в частности.

Каждый нейропроцессор, входящий в состав БМНП содержит микропроцессор, входы и вход-выход которого являются входами и входом-выходом нейропроцессора. Через двунаправленную шину к нему подключено процессорное ЗУ, а выход микропроцессора через буферный регистр подключен к установочному входу процессорного БМУ и к входам n умножителей, соединенных последовательно шинами переноса. Выходы умножителей подключены к входам сумматора, подключенного выходом к входу схемы связи, вход-выход которой объединенный с входом-выходом микропроцессора является входом-выходом нейропроцессора.

Процессорный БМУ содержит процессорный регистр кода, процессорный регистр признаков, входы которого являются входами признаков блока, процессорный счетчик адреса и процессорный регистр смещения, установочные входы этих регистров и счетчика являются установочным входом блока, а их выходы образуют адресную процессорную шину, подключенную к входу процессорного микропрограммного запоминающего устройства, выходы которого являются управляющими выходами блока, а дополнительные выходы этого запоминающего устройства подключены к входам процессорного регистра смешения.

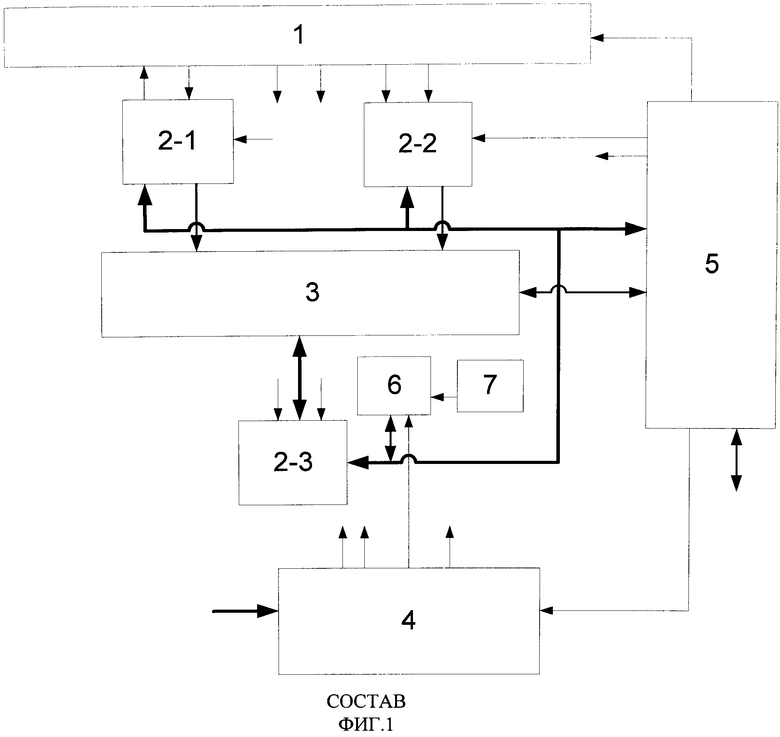

ЗУСД включает первый и второй накопители, блокирующие входы которых являются блокирующим входом ЗУСД. Кроме того к входу каждого накопителя - первого и второго подключен выход своего сумматора метки времени, соответственно первого и второго, вход каждого из которых является входом метки времени запоминающего устройства, а через первую двунаправленную связь к каждому накопителю - первому и второму подключен свой сумматор массивов, соответственно первый и второй, вход-выход каждого из которых совместно с входом-выходом каждого из накопителей подключен к магистральной шине запоминающего устройства, являющейся магистралью нейровычислителя.

ИВЭП включает с свой состав модуль постоянного питания (МПП) и модуль импульсного питания (МИП), силовые входы которых являются силовым входом источника, установочный вход которого является установочным входом МПП и формирователя синхроимпульсов (ФСИ), три управляющих выхода которого подключены к одноименным входам МИП, а выходы метки времени и синхроимпульсов ФСИ, постоянного питания МПП и импульсного МИП являются одноименными выходами ИВЭП.

МПП содержит три идентичных конвертора, установочные входы которых являются установочным входом источника. Частотные выходы конверторов подключены к частотным входам блока контроля и у правления (БКУ).

Выходы конверторов кроме того подключены к контрольным входам БКУ и через блок отключения (БО) подключены к входам блока выравнивания (БВ), выход которого является выходом модуля и ИВЭП и подключен к дополнительному контрольному входу БКУ, выходы которого подключены к управляющим входам БО.

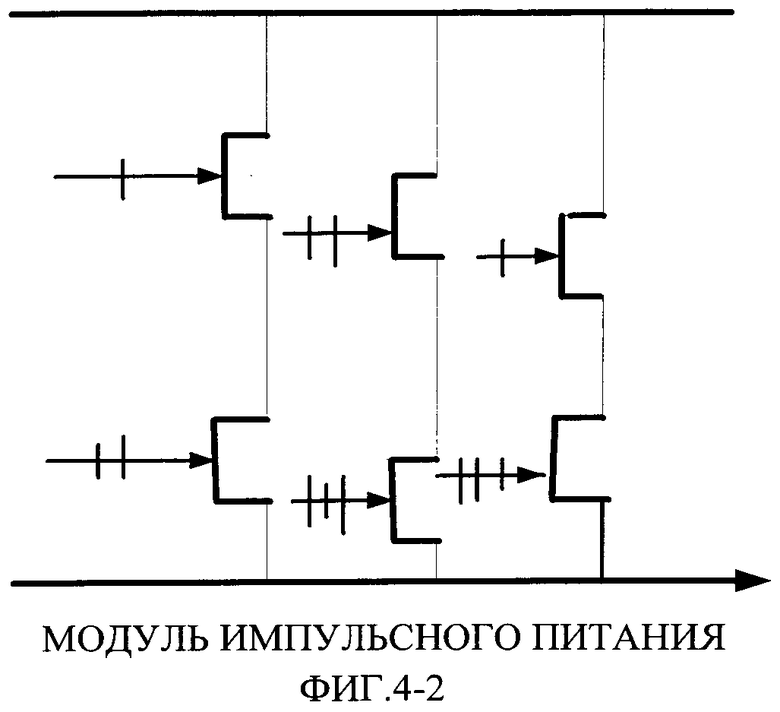

МИП содержит три идентичные ветви, объединенные с каждой из сторон, одна из которых является силовым входом, вторая выходом,. В каждой ветви последовательно включены два полевых транзистора, а три входных управляющих сигнала разведены так, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях. Такая разводка обеспечивает резервирование исполнения управляющих сигналов по принципу мажоритарной выборки «2 из 3».

Конвертор содержит фильтр, вход которого является силовым входом конвертора. За фильтром включен трансформатор, в разрыв первичной обмотке которого установлен транзистор - прерыватель. После вторичной обмотки установлен выпрямляющий диод (диодный мостик), за которым следует выходной фильтр нижних частот. Выход этого фильтра является выходом конвертора, который подключен к цепи обратной связи, начинающейся с преобразователя напряжения в частоту. Выход этого преобразователя подключен к входу элемента развязки (гальванической развязки), выход которого является частотным выходом конвертора и в свою очередь подключен к входу частотно-импульсного модулятора (ЧИМ), которым заканчивается обратная связь, так как его выход подключен к базе транзистора - прерывателя, частотой переключения которого можно изменять уровень выходного напряжения конвертора, а введение в ЧИМ установочного входа, являющегося установочным входом конвертора позволяет задавать номинал формируемой модулятором частоты прерываний транзистора и следовательно управлять выходным напряжением конвертора.

БО содержит три полевых транзистора, истоки которых являются входами, стоки - выходами, а управляющие входы соединены с затворами транзисторов.

БВ содержит три идентичные цепи. В каждой цепи последовательно включены резистор и диод. У резистора первый вывод является входом. Второй вывод резистора подключен к аноду диода этой цепи. Катоды всех трех диодов объединены и образуют выход блока.

БКУ содержит первый, второй, третий и четвертый частотные счетчики. Входы первых трех являются частотными входами блока, подключенными соответственно к частотным выходам первого, второго и третьего конверторов. Вход четвертого счетчика подключен к выходу контрольного преобразователя напряжения в частоту, входы которого являются контрольными и дополнительным контрольным входами блока, подключенными к выходам конверторов и блока выравнивания. Выход первого счетчика подключен к первым входам первого и второго сумматоров. Выход второго счетчика подключен ко второму входу второго сумматора и первому входу третьего сумматора, а выход третьего счетчика подключен ко вторым входам третьего и первого сумматоров. Выход четвертого счетчика подключен к первому входу четвертого сумматора, ко второму входу которого подключен выход регистра контрольного кода, выход которого подключен ко вторым входам всех контрольных схем сравнения. При этом, вход регистра контрольного кода объединен с входом регистра допуска, выходы которого подключены ко вторым входам первой, второй, третьей и четвертой контрольных схем сравнения. К выходам этих схем подключены входы соответствующих им первого, второго, третьего и четвертого триггеров ошибок, выходы которых подключены к управляющей группе логических элементов, выходы которой являются выходами блока, подключенными к управляющим входам блока отключения.

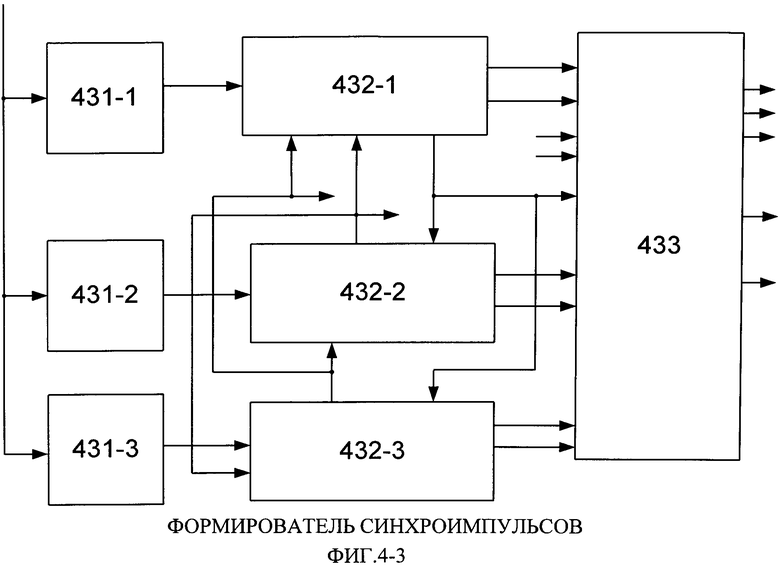

ФСИ содержит первый, второй и третий генераторы импульсов, установочный вход каждого из которых является установочным входом формирователя, а выход каждого из генераторов подключен к входу своего, соответственно, первого второго и третьего блока фазирования. Фазирующий выход каждого из этих блоков подключен к фазирующим входам двух других блоков и фазирующим входам блока мажоритации, к синхронизирующим входам которого подключены синхронизирующие выходы блоков фазирования, а выходы блока мажоритации являются выходом метки времени и синхроимпульсов формирователя.

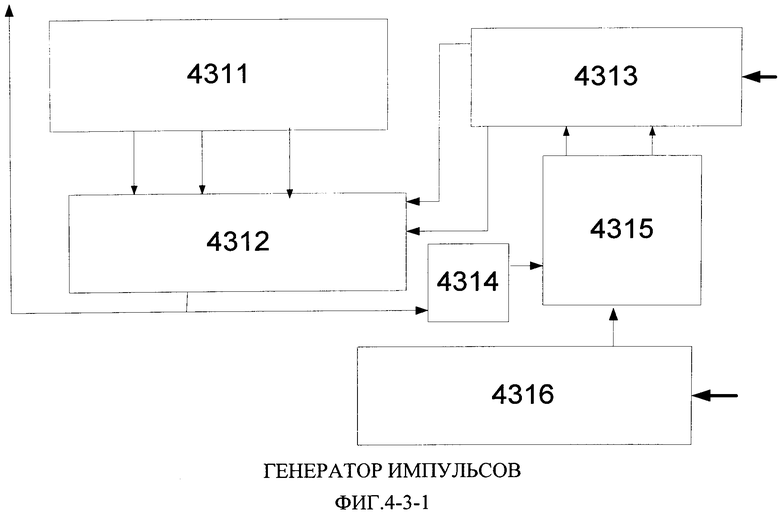

Генератор импульсов, входящий в ФСИ, содержит несколько (n) последовательно соединенных инверторов, подключенных выходами к входам первого мультиплексора. Выход этого мультиплексора является выходом генератора и подключен к входу первого инвертора и входу первого счетчика частоты. Выходы этого счетчика подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода. Инкрементный и декрементный выходы первой схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора. Кроме того установочный вход первого регистра кода и установочный вход первого счетчика кода являются установочным входом генератора.

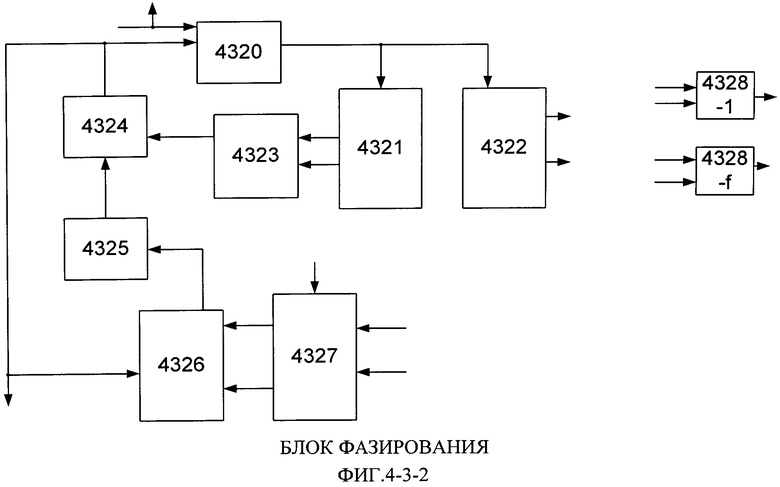

Блок фазирования содержит элемент И, первый вход которого является входом блока, а выход подключен к входу сдвигового регистра и реализованного на динамических триггерах счетчика, выход которого через дешифратор подключен к входу триггера останова, выход этого триггера является фазирующим выходом блока и подключен ко второму входу элемента И и первому входу мажоритарного элемента, выход которого подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера останова. Ко второму и третьему входу мажоритарного элемента подключены выходами триггеры привязки, входы которых являются фазирующими входами блока. При этом выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам f триггеров - формирователей, выходы которых являются синхронизирующими выходами блока.

ЧИМ содержит группу последовательно соединенных инверторов, подключенных выходами к входам второго мультиплексора. Выход этого мультиплексора подключен к входу первого инвертора группы и является выходом генератора, вход которого является входом второго счетчика частоты. Выходы второго счетчика частоты подключены к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода. Инкрементный и декрементный выходы второй схемы сравнения подключены к одноименным входам второго счетчика кода частоты, выходы которого подключены к управляющим входам второго мультиплексора. Кроме того установочный вход второго регистра кода и установочный вход второго счетчика кода являются установочным входом генератора.

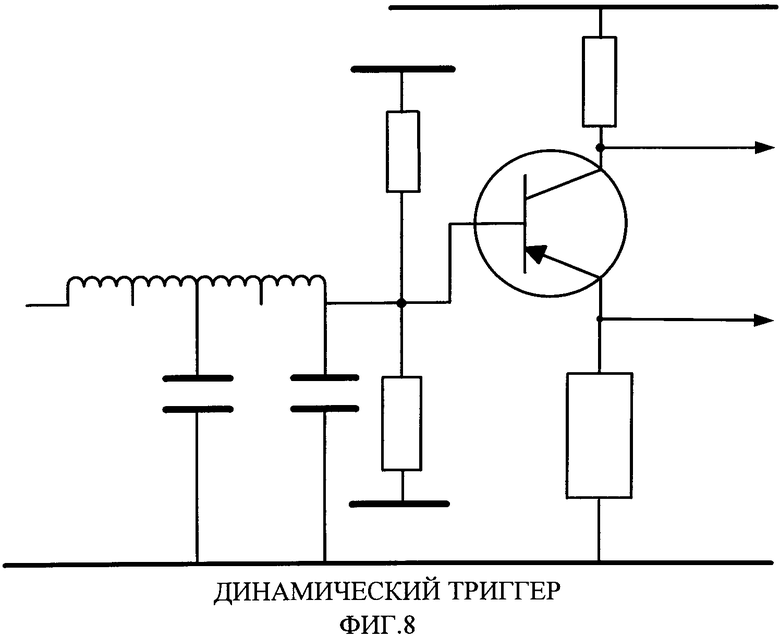

Динамический триггер выполнен как транзисторный усилитель с особенностью в том что к базе транзистора триггера кроме резисторного делителя, задающего рабочую точку транзистора подключена как элемент памяти цепь из индуктивности L и конденсатора С. Особенность является то, что для обеспечения защиты от внешних для триггера электромагнитных наводок индуктивность имеет две обмотки рабочую и компенсационную.

Компенсационная обмотка намотана поверх рабочей со встречным по отношению к намотке рабочей обмотки расположением витков.

Состав Нейровычислителя и составляющих компонентов приведен в виде структур и схем на фигурах с 1-й по 8-ю.

На фигуре 1 приведен состав Нейровычислителя, где цифрой 1 обозначен БМУ, цифрами 2-1 и 2-2 обозначены соответственно первый и второй блоки матричных вычислителей, цифрой 3 обозначено ОУ, цифрой 2-3 обозначено матричное запоминающее устройство, цифрой 4 - ИВЭП и цифрой 5 обозначен блок связи.

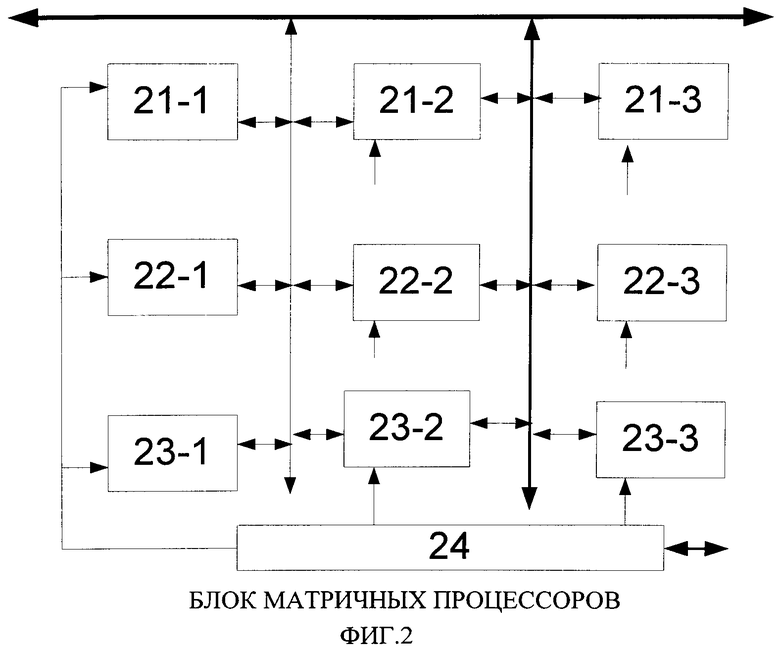

Блок матричных процессоров приведен на фигуре 2. Здесь цифрами от 21-1 до 23-3 обозначены нейропроцессоры и цифрой 24 - устройство связи.

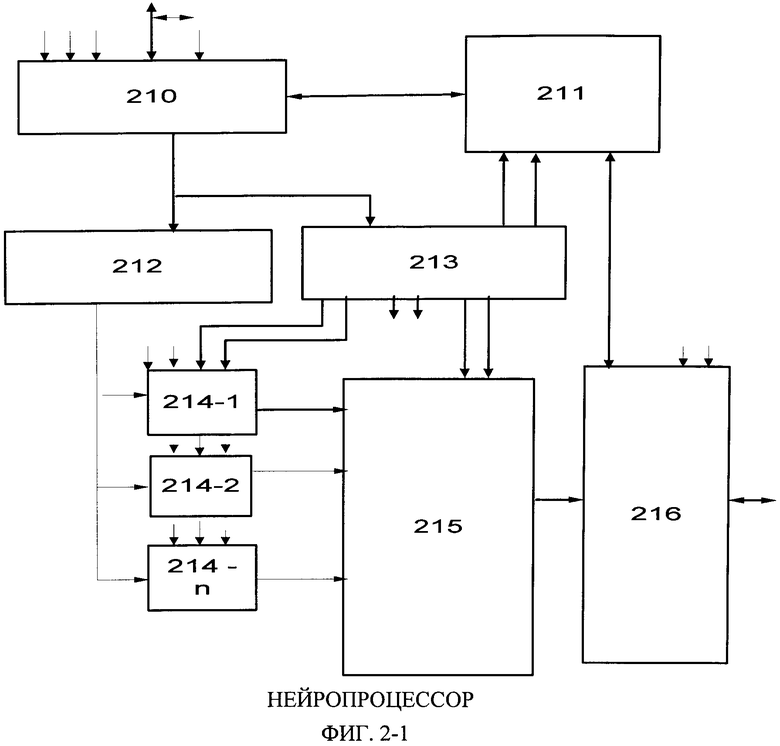

Нейропроцессор приведен на фигуре 2-1. Здесь цифрами 210 обозначен микропроцессор, цифрами 211 - процессорное ЗУ, 212 - буферный регистр, цифрами 213 обозначен процессорный БМУ, цифрами от 214-1 до 214-n обозначены умножители, цифрами 215 - сумматор и цифрами 216 обозначено устройство связи.

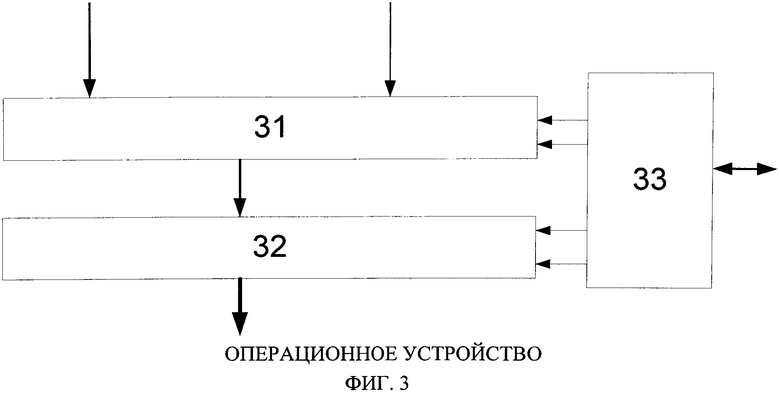

Операционное устройство приведено на фигуре 3, где цифрами 31 обозначен блок умножения, цифрами 32 - блок сумматоров и цифрами 33 обозначен блок связи с матричным ЗУ.

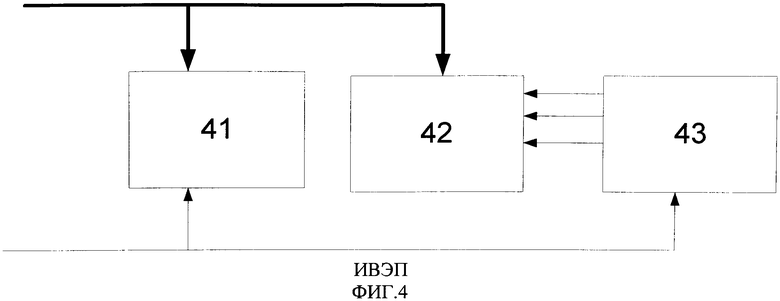

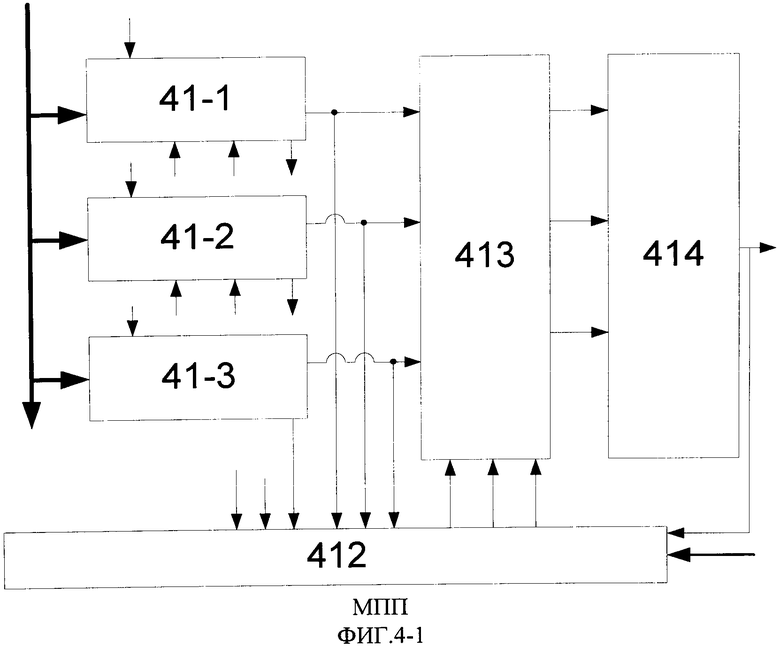

ИВЭП приведен на фигуре 4, где цифрами 41, 42 и 43 обозначены соответственно модуль постоянного питания, модуль импульсного питания и ФСИ.

МПП приведен на фигуре 4-1. На фигуре цифрами 41-1, 41-2 и 41-3 обозначены конверторы, цифрами 412 - БУК и цифрами 413 и 414 обозначены соответственно БО и БВ.

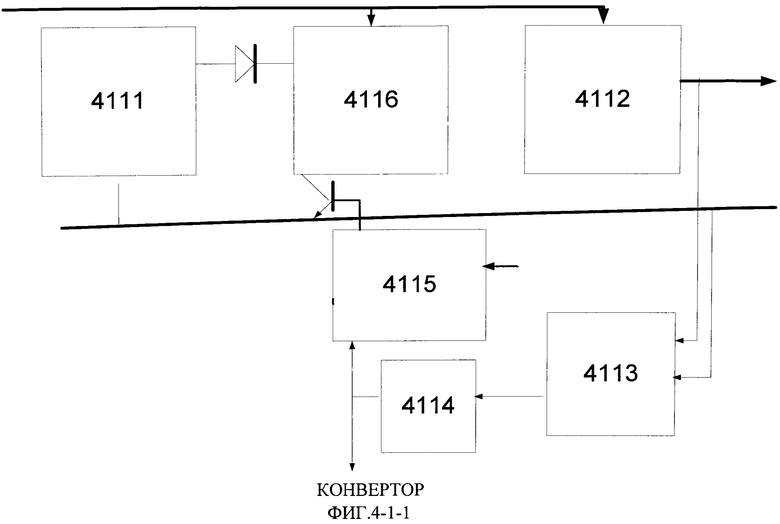

Конвертор приведен на фигуре 4-1-1. Здесь цифрами 4111 и 4112 обозначены соответственно фильтр и выходной фильтр. Цифрами 4116 обозначен трансформатор. Цифрами 4113 обозначен преобразователь напряжения в частоту, цифрами 4114 - элемент развязки и цифрами 4115 обозначен ЧИМ.

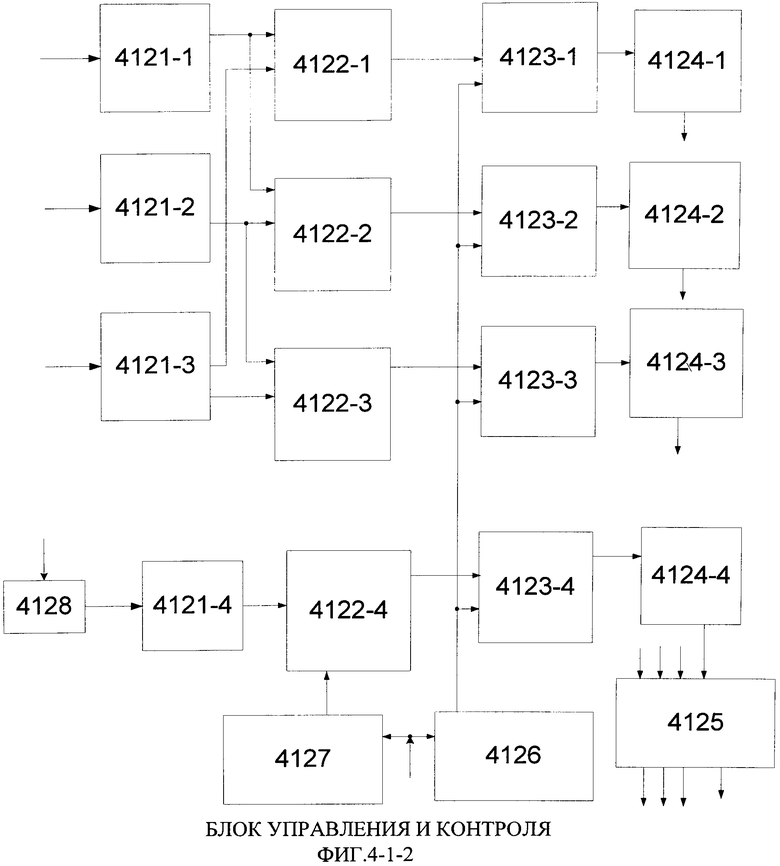

На фигуре 4-1-2 приведен БУК. На этой фигуре цифрами от 4121-1 до 4121-4 обозначены первый, второй, третий и четвертый частотные счетчики. Цифрами от 4122-1 до 4122-4 обозначены первый, второй, третий и четвертый сумматоры. Цифрами от 4123-1 до 4123-4 обозначены первая, вторая, третья и четвертая контрольные схемы совпадения. Цифрами от 4124-1 до 4124-4 обозначены первый, второй, третий и четвертый триггеры неисправности. Цифрами 4125 обозначена группа логических схем, цифрами 4126 и 4127 обозначены регистр кода и регистр допуска соответственно и цифрами 4128 обозначен контрольный преобразователь напряжения в частоту.

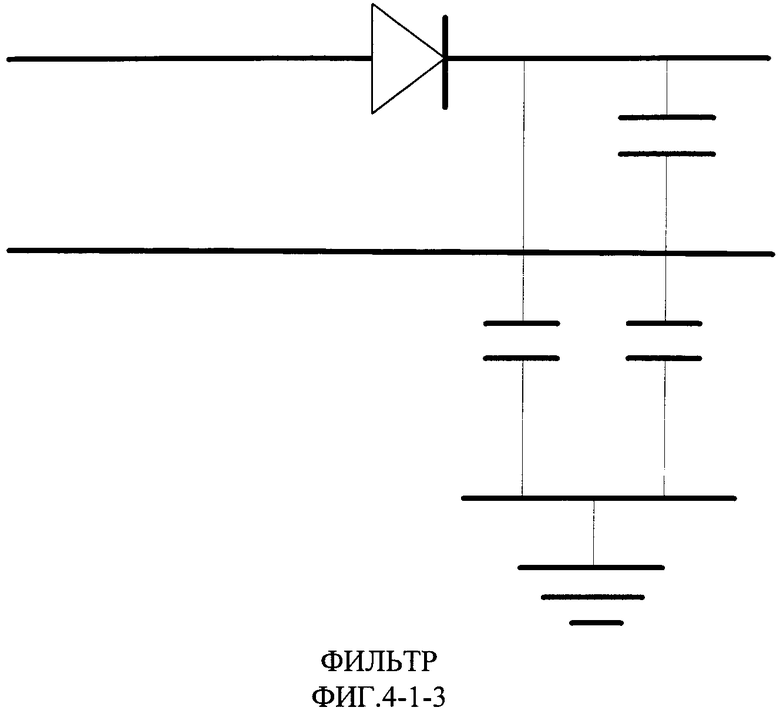

Фильтр приведен на фигуре 4-1-3.

ЧИМ приведен на фигуре 4-1-4, где цифрами 4141 обозначена группа инверторов, цифрами 4142 - второй мультиплексор, цифрами 4143 обозначен второй счетчик кода частоты, цифрами 4144 - второй счетчик частоты, цифрами 4145 обозначена вторя схема сравнения и цифрами 4146 обозначен второй регистр кода частоты.

МИП приведен на фигуре 4-2.

ФСИ приведен на фигуре 4-3. Здесь цифрами 431-1, 431-2 и 431-3 обозначены соответственно первый, второй и третий генераторы импульсов. Цифрами 432-1, 432-2 и 432-3 обозначены первый, второй и третий блоки фазирования и цифрами 433 обозначен блок мажоритации.

ГИ приведен на фигуре 4-3-1, где цифрами 4311 обозначены инверторы, цифрами 4312 - первый мультиплексор, цифрами 4313 обозначен первый счетчик кода частоты, цифрами 4314 обозначен первый счетчик частоты, цифрами 4315 - первая схема сравнения и цифрами 4316 обозначен первый регистр кода частоты.

Блок фазирования приведен на фигуре 4-3-2. Здесь цифрами 4320 обозначен элемент И, цифрами 4321 и 4322 обозначены соответственно счетчик на динамических триггерах и сдвиговый регистр. Цифрами 4323 обозначен дешифратор, цифрами 4324 и 4325 обозначены, соответственно, триггер останова и триггер пуска. Цифрами 4326 обозначен мажоритарный элемент, цифрами 4327 - триггеры привязки и цифрами от 4328-1 до 4328-f обозначены триггеры формирователи.

Блок связи приведен на фигуре 5, где цифрами 50 обозначен процессор, цифрами 51 - запоминающее устройство, цифрами 52 и 53 обозначены соответственно кодирующе-декодирующее устройство и приемно-передающее устройство.

ДВВ приведен на фигуре 6, где цифрами 60 и 61 обозначены, соответственно, чувствительный элемент датчика и формирователь сигнала.

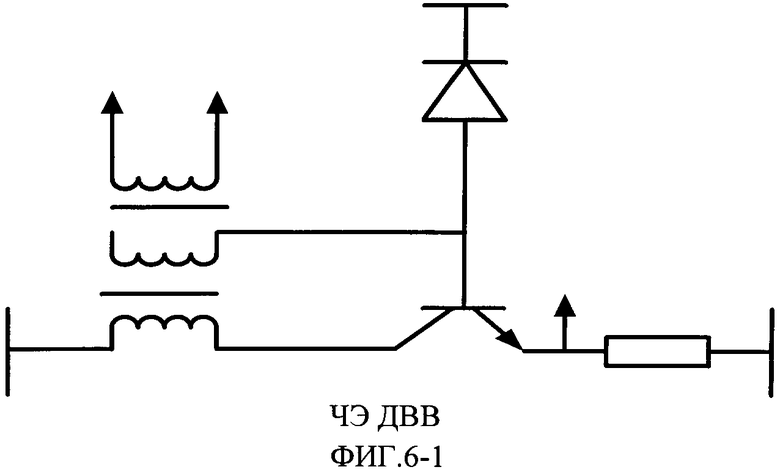

Чувствительный элемент ДВВ приведен на фигуре 6-1.

Формирователь сигнала приведен на фигуре 7, где цифрами 70 обозначен КЗГ, цифрами 71-таймерный счетчик, цифрами 72 обозначен таймерный дешифратор, цифрами 73 обозначен триггер блокировки, цифрами 74 и 75 обозначены, соответственно регистр кода и дешифратор кода и цифрами 76 обозначен логический элемент.

Динамический триггер приведен на фигуре 8.

ЗУСД приведен на фигуре 9, где цифрами 91-1 и 91-2 обозначены энергонезависимые накопители, цифрами 92-1 и 92-2 обозначены сумматоры метки времени и цифрами 93-1 и 93-2 обозначены сумматоры массивов.

Нейровычислитель может быть реализован следующим образом:

Все цифровые узлы реализуются на основе комплекта радиацонностойких БИС серии 1825 и запоминающих устройств на основе БИС серии 1620, изготавливаемых в производстве АО «Ангстрем», дополненных БИС на основе базовых матричных кристаллов серий 1555 и 1556, изготавливаемых там же. ЗУСД реализуется на основе многоотверстевых магнитных сердечников или цилиндрических тонких магнитных пленок, изготавливаемых в производстве ФГУП «НПОА», г. Екатеринбург, в производстве которого изготавливаются из дискретных элементов ИВЭП, ДВВ и динамический триггер.

Нейровычислитель работает следующим образом. Перед началом работы из БЦВМ верхнего уровня во все микропрограммные запоминающие устройства загружаются микропрограммы и «обучающие» коэффициенты, обеспечивающие вычисление требуемых функций и алгоритмов матричных преобразований. В МПП и ФСИ источника вторичного электропитания вводятся уставки, соответствующие номинальным значениям питания и частоты следования синхроимпульсов. По результатам периодически проводимых по командам БЦВМ тестовых проверок, для чего загружаются соответствующие микропрограммы, производится определение фактического быстродействия цифровых узлов и вводятся уставки в МПП и ФСИ, соответствующие максимально возможному быстродействию, которое может изменяться при изменении температуры окружающей среды и снижаться при наборе заметной дозы (не мене 100 Крад) или повышаться при начальном наборе дозы (до 10 Крад).

Все результаты вычислений один раз в цикле (примерно одиг раз в 1 мс) записываются в несколько идентичных по составу данных зон ЗУСД, накопители которых блокируются от несанкционированного обращения. Блокировка поддерживается сигналом ДВВ на время внешнего воздействия, После окончания воздействия формирователем сигнала ДВВ формирует сигнал обнуления/пуска по которому вычислитель переходит к выполнению микропрограмм рестарта, записанных в постоянной памяти всех его БМУ, используя сохранившийся в ЗУСД массив результатов последнего перед сбоем цикла вычислений. Достоверный массив из нескольких резервных выбирается путем проверки его содержимого по его контрольной сумме, формируемой для каждого массива перед началом записи в ЗУСД.

Таким образом, введение в состав вычислителя блока матричных нейпроцессоров, в которых каждый нейропроцессор, являясь элементом матрицы, обеспечивает быстрое вычисление тригонометрических функций, а каждый блок является, по сути, исходной матрицей в произведений двух матриц.

Введенное после этого блока операционное устройство обеспечивает высокою скорость при вычислении элементов результирующей матрицы, элементы которой являются компонентами пространственных векторов трех координатной инерциальной системы.

В результате чего достигается требуемое(не более 1 мс) для работы БИНС в составе САУ высокоманевренными объектами время формирования инерциальной системы координат.

Ведение резервирования на уровне отдельных узлов компонентов вычислителя и введение режимов перестройки номиналов питающих напряжений и частоты следования синхроимпульсов позволяет нейтрализовать как катастрофические отказы элементов вычислителя, вызванные естественным старением и(или) потоком тяжелых заряженных частиц космического пространства, так и обеспечить максимально возможное быстродействия вычислителя для каждого интервала работы, нейтрализуя или используя для повышения производительности изменение быстродействия полупроводниковых элементов, вызванное изменением температуры окружающей среды и(или) дозовыми эффектами в материалах полупроводниковых структур элементов из-за действия ионизирующего излучения космического пространства, ядерно-энергетических установок или загрязненной местности.

Кроме того введение режима рестарта вычислительного процесса с использованием сохраненных в ЗУСД рестартовых массивов в каждом цикле вычислений позволят нейтрализовать сбои в работе вычислителя, вызванные внешним ионизирующим импульсным излучением при вспышках на Солнце, авариях ядерно-энергетических установок и направленным противодействием.

Все эти свойства предложенного Нейровычислителя позволяют успешно использовать его в составе БИНС, устанавливаемых в системы управления высоко маневренными объектами ракетно-космической техники и в частности комическими аппаратами а также робототехническими комплексами, предназначенными для ликвидации аварий типа Чернобыльской или для работы в инженерных войсках.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2013 |

|

RU2563333C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2536434C2 |

| СБОЕУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2541839C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 2013 |

|

RU2534955C1 |

| СИСТЕМА УПРАВЛЕНИЯ КОСМИЧЕСКОГО АППАРАТА | 2013 |

|

RU2560204C2 |

| СИСТЕМА АСТРОНАВИГАЦИИ | 2013 |

|

RU2548927C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ | 2013 |

|

RU2514135C1 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| НЕЙРОПРОЦЕССОР | 2011 |

|

RU2473126C1 |

Изобретение относится к вычислительной технике и может быть использовано при создании бесплатформенных инерциальных систем, входящих с состав систем автоматического управления высокоманевренными судами, объектами авиационной техники, изделиями ракетно-космической техники и космическими аппаратами в частности, а также мобильными робототехническими комплексами, особенностью которых является обеспечение работоспособности в экстремальных условиях. Техническим результатом является повышение быстродействия матричных вычислений. Устройство содержит блок микропрограммного управления, два блока матричных нейропроцессоров, операционное устройство, матричное запоминающее устройство, источник вторичного электропитания, блок связи, запоминающее устройство санкционированного доступа, датчик внешнего воздействия. 22 з.п. ф-лы, 20 ил.

1. Нейровычислитель, содержащий блок связи, вход-выход которого является входом-выходом нейровычислителя, а выход подключен к установочному входу блока микропрограммного управления, выходы которого соединены с управляющими входами всех цифровых компонентов вычислителя, отличающийся тем, что в его состав введены первый и второй блоки матричных нейропроцессоров, которые через магистраль подключены к матричному запоминающему устройству и запоминающему устройству санкционированного доступа, блокирующий вход которого подключен к выходу датчика внешнего воздействия, причем выходы блока связи подключены к входам блоков матричных нейропроцессоров, выходы которых соединены с операционным устройством, выход которого подключен к запоминающему устройству, а установочный выход блока связи подключен к установочному входу источника вторичного электропитания, выход метки времени которого подключен к временному входу запоминающего устройства санкционированного доступа, а синхронизирующие выходы и выходы питания которого подключены к соответствующим входам остальных блоков нейровычислителя.

2. Нейровычислитель по п. 1, отличающийся тем, что блок микропрограммного управления содержит базовый регистр кода операции, базовый регистр признаков, входы которого являются входами блока, базовый счетчик адреса и базовый регистр смещения, установочный вход каждого из которых является установочным входом блока, а их выходы образуют адресную шину блока, подключенную к входу базового микропрограммного запоминающего устройства, выходы которого являются выходами блока, а дополнительный выход базового микропрограммного запоминающего устройства подключен к входу базового регистра смещения.

3. Нейровычислитель по п. 1, отличающийся тем, что блок матричных нейропроцессоров, содержит девять нейропроцессоров, образующих матрицу размерностью 3×3, причем входы нейропроцессоров являются выходами устройства связи, вход-выход которого является входом-выходом блока, а магистральный вход-выход каждого нейропроцессора подключен к магистральной шине, являющейся внешней магистралью блока.

4. Нейровычислитель по п. 1, отличающийся тем, что источник вторичного электропитания содержит модуль постоянного питания и модуль импульсного питания, силовой вход каждого из которых является силовым входом источника, установочный вход которого является установочным входом модуля постоянного питания и формирователя синхроимпульсов, три управляющих выхода которого подключены к одноименным входам модуля импульсного питания, выход которого, а также выходы модуля постоянного питания и формирователя синхроимпульсов являются выходами импульсного, постоянного питания, метки времени и синхронизирующими выходами источника.

5. Нейровычислитель по п. 1, отличающийся тем, что блок связи содержит процессор, к которому через процессорную магистраль подключено связное запоминающее устройство и устройство связи по магистрали, а вход-выход процессора через кодирующее-декодирующее устройство подключен к входу-выходу приемо-передающего устройства, магистральный мультиплексный вход-выход которого является одноименным входом-выходом блока.

6. Нейровычислитель по п. 1, отличающийся тем, что запоминающее устройство санкционированного доступа содержит первый и второй энергонезависимые накопители, блокирующий вход каждого из которых является одноименным входом устройства, а к входу каждого накопителя, первого и второго, подключены выходы соответствующих им первого и второго сумматоров метки времени, вход каждого из которых является входом метки времени устройства, при этом первый вход-выход каждого накопителя подключен к двунаправленной шине внешней связи запоминающего устройства, к которой подключены своим первым входом-выходом соответствующие накопителям первый и второй сумматоры массивов, каждый из которых, первый и второй, своим вторым входом-выходом подключен ко второму входу соответственно первого и второго накопителя.

7. Нейровычислитель по п. 1, отличающийся тем, что датчик внешнего воздействия содержит чувствительный элемент, подключенный выходом к входу формирователя сигнала, выход которого является выходом датчика.

8. Нейровычислитель по п. 3, отличающийся тем, что нейропроцессор содержит микропроцессор, входы и вход-выход которого являются входами и входом-выходом нейропроцессора, а выход микропроцессора через буферный регистр подключен к установочному входу процессорного блока микропрограммного управления, выходы которого подключены к управляющим входам остальных компонентов нейропроцессора и входам n соединенных последовательно шинами переноса умножителей, подключенных выходами к входам сумматора, выход которого является выходом нейропроцессора.

9. Нейровычислитель по п. 4, отличающийся тем, что модуль постоянного питания содержит три идентичных конвертора, установочные входы которых являются установочным входом модуля, а выходы подключены к контрольным входам блока контроля и управления и через блок отключения подключены к входам блока выравнивания, выход которого является выходом модуля, подключенным к дополнительному контрольному входу блока контроля и управления, управляющие выходы которого подключены к одноименным входам блока отключения.

10. Нейровычислитель по п. 4, отличающийся тем, что модуль импульсного питания содержит три идентичные ветви, объединенные с каждой из сторон, одна из которых является входом, вторая - выходом, причем в каждой ветви установлено два последовательно включенных полевых транзистора, а три входных управляющих сигнала разведены таким образом, что каждый из них подключен к затворам двух транзисторов, установленных в разных ветвях, образуя выборку «2 из 3».

11. Нейровычислитель по п. 4, отличающийся тем, что формирователь синхроимпульсов содержит первый, второй и третий генераторы импульсов, установочные входы которых являются установочным входом формирователя, а выход каждого генератора, первого, второго и третьего, подключен к входу своего блока фазирования, соответственно первого, второго и третьего, фазирующий выход каждого из которых подключен к фазирующим входам двух других блоков и фазирующим входам блока мажоритации, к синхронизирующим входам которого подключены синхронизирующие выходы блоков фазирования, а выходы блока мажоритации являются выходами метки времени и синхроимпульсов формирователя.

12. Нейровычислитель по п. 7, отличающийся тем, что чувствительный элемент датчика внешнего воздействия выполнен как блокинг генератор, к базе транзистора которого помимо резисторного делителя подключен обратносмещеный диод.

13. Нейровычислитель по п. 7, отличающийся тем, что формирователь сигнала содержит кварцевый задающий генератор, подключенный выходом к входу интервального счетчика, подключенного выходом через интервальный дешифратор к сбрасывающему входу триггера запрета, запускающий вход которого является входом формирователя и объединен с запускающим входом интервального счетчика и логического элемента, выход которого является выходом формирователя, а блокирующий вход этого элемента подключен к выходу блокирующего дешифратора, входы которого подключены к выходам регистра кода, вход которого является входом кода блокировки формирователя.

14. Нейровычислитель по п. 8, отличающийся тем, что процессорный блок микропрограммного управления содержит процессорный регистр кода операции, процессорный регистр признаков, входы которого являются входами блока, процессорный счетчик адреса и процессорный регистр смещения, установочный вход которых является установочным входом блока, а их выходы образуют адресную шину блока, подключенную к входу процессорного микропрограммного запоминающего устройства, выходы которого являются выходами блока, а дополнительный выход процессорного запоминающего устройства подключен к входу процессорного регистра смешения.

15. Нейровычислитель по п. 9, отличающийся тем, что блок выравнивания содержит три идентичные цепи, объединенные с каждой из сторон, одна из которых является входом, вторая - выходом, а в каждой цепи последовательно включены резистор и диод, причем первый вывод резистора является входом, второй подключен к аноду диода, а катоды диодов всех цепей объединены и являются выходом модуля.

16. Нейровычислитель по п. 9, отличающийся тем, что конвертор содержит последовательно включенный фильтр, вход которого является силовым входом конвертора, трансформатор с включенным в первичную обмотку транзистором прерывателем, выпрямляющий диод во вторичной обмотке и выходной фильтр, выход которого является выходом конвертора и подключен к входу преобразователя напряжения в частоту, подключенного выходом к элементу развязки, выход которого является частотным выходом конвертора и подключен к входу частотно-импульсного модулятора, установочный вход которого является установочным входом конвертора, а выход подключен к базе транзистора прерывателя.

17. Нейровычислитель по п. 9, отличающийся тем, что блок отключения содержит три полевых транзистора, исток каждого из которых является входом, сток - выходом, а каждый из трех входных управляющих сигналов подключен к затвору соответствующего транзистора.

18. Нейровычислитель по п. 9, отличающийся тем, что блок контроля и управления содержит четыре частотных счетчика, входы первого, второго и третьего из которых являются частотными входами блока, а вход четвертого подключен к выходу схемы преобразования напряжения в частоту, входы которой являются контрольными и дополнительным контрольным входом блока, причем выход первого счетчика подключен к первым входам первого и третьего сумматора, выход второго подключен ко второму входу первого сумматора и первому входу третьего сумматора, а выход третьего счетчика подключен ко вторым входам первого и третьего сумматора, при этом выход четвертого счетчика подключен к первому входу четвертого с устройства совпадения, ко второму входу которого подключен выход регистра кода, вход которого является установочным входом блока и объединен с входом регистра допуска, выход которого подключен к первым входам первого, второго и третьего устройств совпадения, ко вторым входам которых подключены выходы соответственно первого, второго и третьего сумматора, а выход каждого устройства совпадения, первого, второго, третьего и четвертого, через свой соответственно первый, второй, третий и четвертый триггеры ошибки подключен к входу логического устройства, выходы которого являются выходами блока.

19. Нейровычислитель по п. 11, отличающийся тем, что генератор импульсов содержит n последовательно соединенных инверторов, выходы которых подключены к входам первого мультиплексора, выход которого является выходом генератора и подключен к входу первого инвертора и входу первого счетчика частоты, выходы которого подключены к первым входам первой схемы сравнения, ко вторым входам которой подключены выходы первого регистра кода частоты, а инкрементный и декрементный выходы первой схемы сравнения подключены к одноименным входам первого счетчика кода частоты, выходы которого подключены к управляющим входам первого мультиплексора, причем установочный вход первого счетчика кода частоты и первого регистра кода частоты являются установочным входом генератора.

20. Нейровычислитель по п. 11, отличающийся тем, что блок фазирования содержит элемент «И», первый вход которого является входом блока, выход подключен к входу сдвигового регистра и входу реализованного на динамических триггерах счетчика, подключенного выходами через дешифратор к запускающему входу триггера останова, выход которого является фазирующим выходом блока и подключен к первому входу элемента «И» и к первому входу мажоритарного элемента, выход которого подключен к входу триггера пуска, подключенного выходом к сбрасывающему входу триггера останова, а ко второму и третьему входам мажоритарного элемента подключены выходы триггеров привязки, входы которых являются фазирующими входами блока, при этом выходы четных и нечетных разрядов сдвигового регистра подключены соответственно к запускающим и сбрасывающим входам f формирователей синхроимпульсов, выходы которых являются синхронизирующими выходами блока.

21. Нейровычислитель по п. 16, отличающийся тем, что частотно-импульсный модулятор содержит группу последовательно соединенных инверторов, выходы которых подключены к входам второго мультиплексора, выход которого подключен к входу первого инвертора и является выходом модулятора, вход которого является входом второго счетчика частоты, выходы которого подключены к первым входам второй схемы сравнения, ко вторым входам которой подключены выходы второго регистра кода частоты, а инкрементный и декрементный выходы схемы сравнения подключены к одноименным входам второго счетчика кода частоты, выходы которого подключены к управляющим второго мультиплексора, причем установочный вход второго счетчика кода частоты и второго регистра кода частоты является установочным входом модулятора.

22. Нейровычислитель по п. 16, отличающийся тем, что фильтр содержит в плюсовой цепи диод, анод которого является входом, катод - выходом, между которым и минусовой шиной установлен низкочастотный конденсатор, а катод диода и минусовая шина в свою очередь через свой высокочастотный конденсатор подключены к шине земли.

23. Нейровычислитель по п. 20, отличающийся тем, что динамический триггер выполнен как транзисторный усилитель, к базе транзистора которого кроме резисторного делителя подключена LC цепь, индуктивность которой имеет рабочую обмотку и намотанную поверх нее встречно-компенсационную, концы которой закорочены.

| НЕЙРОПРОЦЕССОР | 2011 |

|

RU2473126C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Матричное устройство для вычисления тригонометрических функций | 1984 |

|

SU1226448A1 |

| US 5278945 A, 11.01.1994 | |||

| Пильная рамка | 1974 |

|

SU525543A1 |

Авторы

Даты

2015-06-10—Публикация

2013-08-23—Подача