f

(21)4316422/24-24

(22)12.10.87

(46) 15.05.90. Бюл. Ь 18

(71)Казахский опытно-экспериментальный завод геофизических приборов Казгеофизприбор

(72)В.В.Вайсер, В.М.Зуев, В.А.Каши- цын, В.А.Красюков, В.Т.Курточкин

и Е.В.Тишина

.(53) 681.327.12(088.8)

(56)Заявка Великобритании № 2093299, кл. G 06 К 11/06, 1982.

Заявка Великобритании К- 2080539, кл. G 08 С 21/00, 1982.

(54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ

(57)Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода графической информации в ЭВМ. Целью изобретения является повышение помехоустойчивости устройства при возникновении одиночных импульсных помех. Устройство содержит планшет с ортогонально расположенными координатными шинами в виде одиночных проводников.

Излучаемый катушкой съемйика координат синусоидальный с игнал поочерзд- но принимается координатными шинами. Положение центра съемника координат определяется блоком определения координат путем сложения грубого и точного отсчетов по каждой координате. Грубый отсчет определяется сменой фазы сигнала, индуцированного в соседних координатных шинах. Смена фазы сигнала выявляется блоком сравнения. При пределении. точного отсчета устройство реализует уравнение линейной регрессии для.двух усредненных амплитуд. Блок определения координат содержит мультиплексор, оперативную память, умножитель, схему сравнения, делитель, формирователь дополнительного кода, коммутатор, реверсивный счетчик адреса шин, постоянную память, сумматор и распределитель. Устройство позволяет повысить помехоустойчивость за счет отбрасывания наибольшей и наименьшей амплитуд считанного сигнале с координатной шины и усреднения модулей амплитуд о 1 счетов, взятых с каждой координатнгл шины. 2 з.п. ф-лы, 6 ил.-

I

(Л

сг

СП

О Јь ф О5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания графической информации | 1987 |

|

SU1681316A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для считывания графической информации | 1982 |

|

SU1043692A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1451742A1 |

| Устройство для считывания графической информации | 1980 |

|

SU935987A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1425738A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1991 |

|

RU2029370C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И РЕГИСТРАЦИИ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ | 1994 |

|

RU2092901C1 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для ввода графической информации в ЭВМ. Целью изобретения является повышение помехоустойчивости устройства при возникновении одиночных импульсных помех. Устройство содержит планшет с ортогонально расположенными координатными шинами в виде одиночных проводников. Излучаемый катушкой съемника координат синусоидальный сигнал поочередно принимается координатными шинами. Положение центра съемника координат определяется блоком определения координат путем сложения грубого и точного отсчетов по каждой координате. Грубый отсчет определяется сменой фазы сигнала, индуцированного в соседних координатных шинах. Смена фазы сигнала выявляется блоком сравнения. При определении точности отсчета устройство реализует уравнение линейной регрессии для двух усредненных амплитуд. Блок определения координат содержит мультиплексор, оперативную память, умножитель, схему сравнения, делитель, формирователь дополнительного кода, коммутатор, реверсивный счетчик адреса шин, постоянную память, сумматор и распределитель. Устройство позволяет повысить помехоустойчивость за счет отбрасывания наибольшей и наименьшей амплитуд считанного сигнала с координатной шины и усреднения модулей амплитуд отсчетов, взятых с каждой координатной шины. 2 з.п.ф-лы, 6 ил.

Изобретение относится к области автоматики и вычислительной техники,- а именно к устройствам для считывания графической информации, и может быть исполь овано для ввода графической информации в ЭВМ.

Целью изобретения является повышение помехоустойчивости устройства.

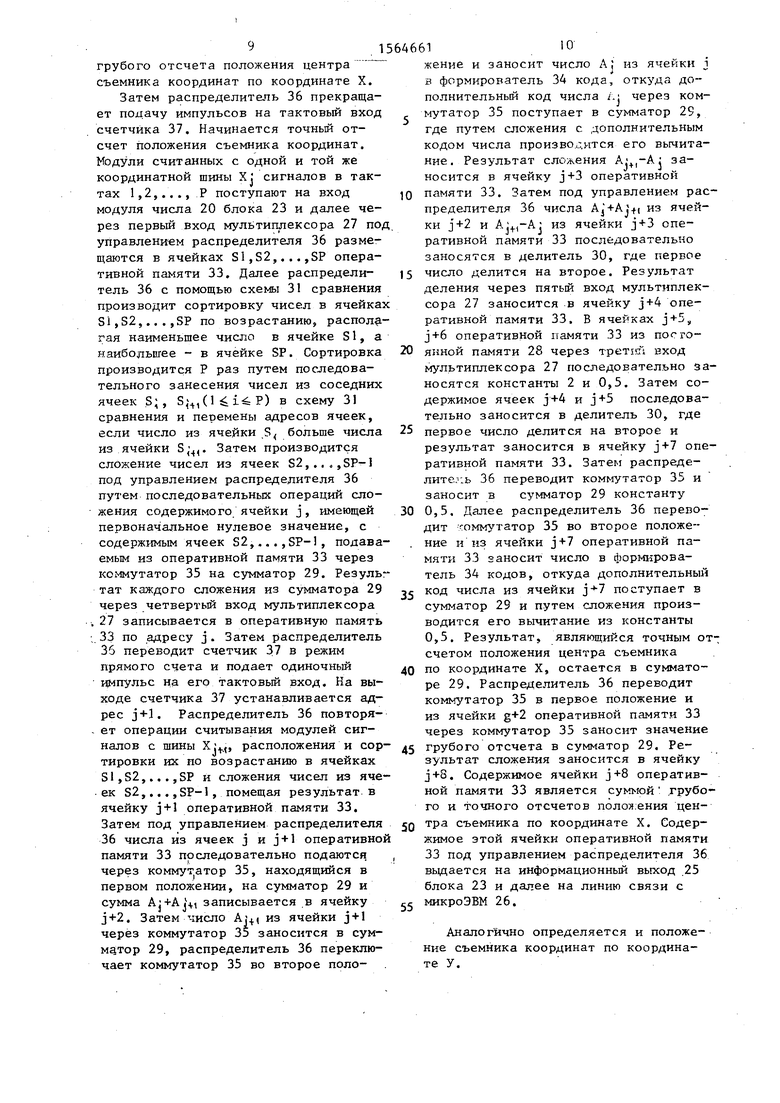

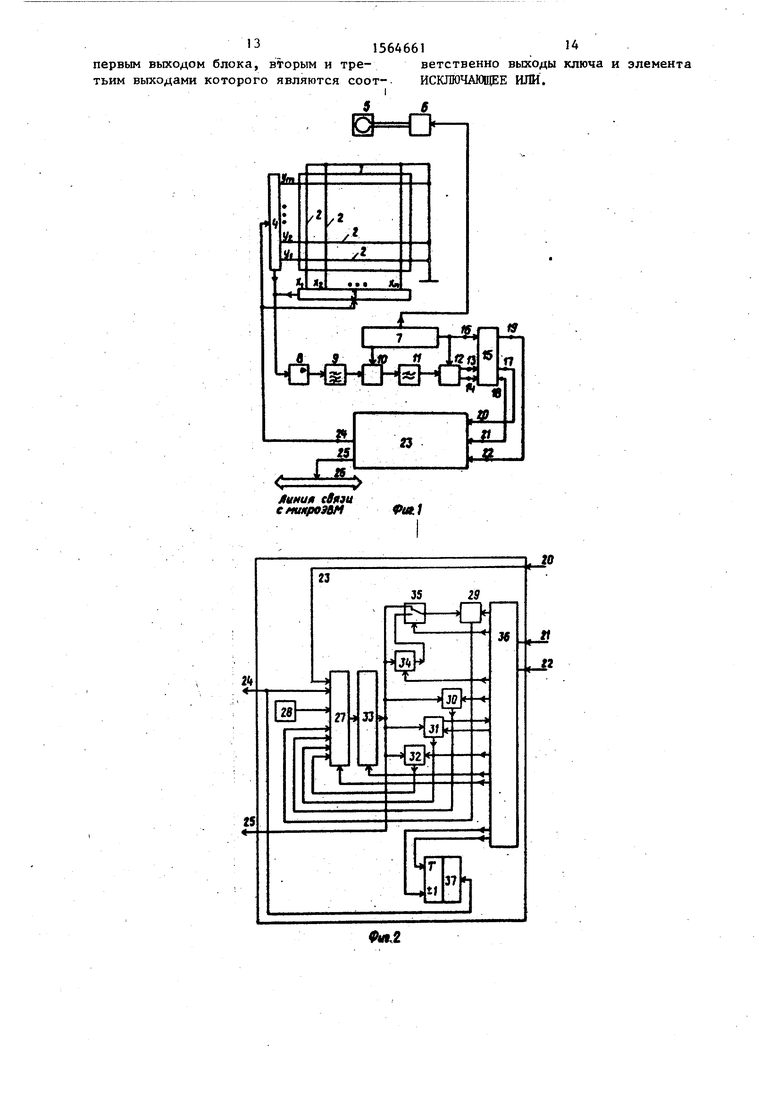

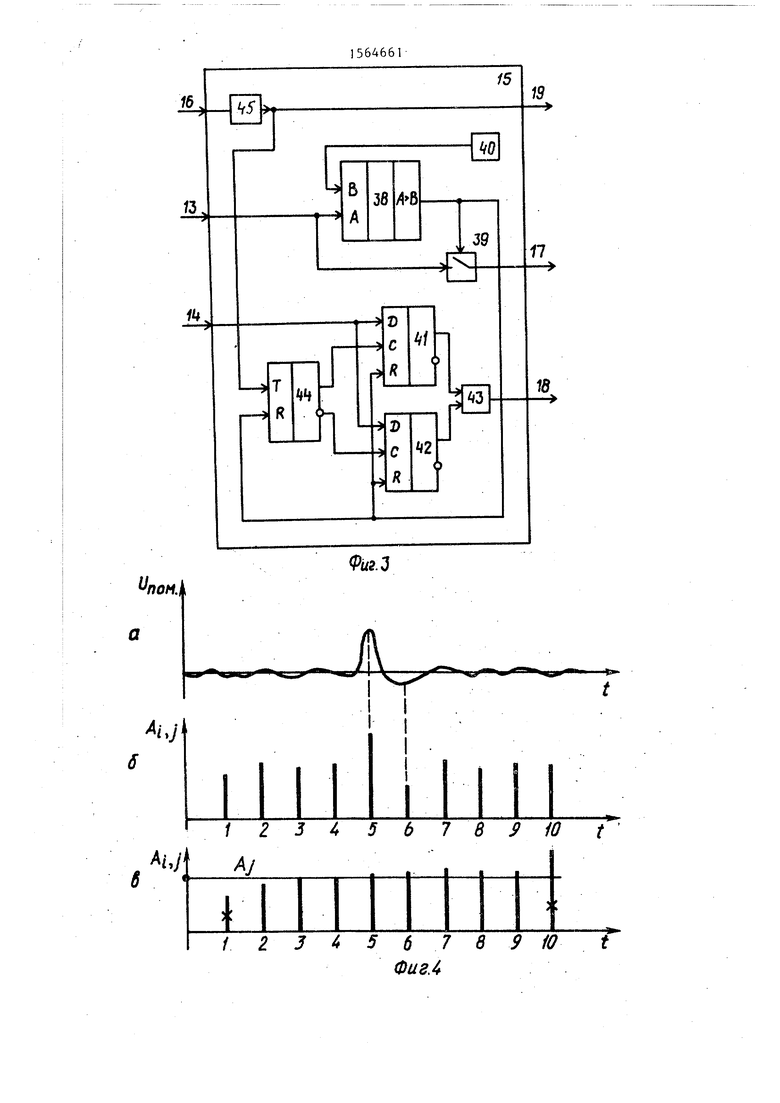

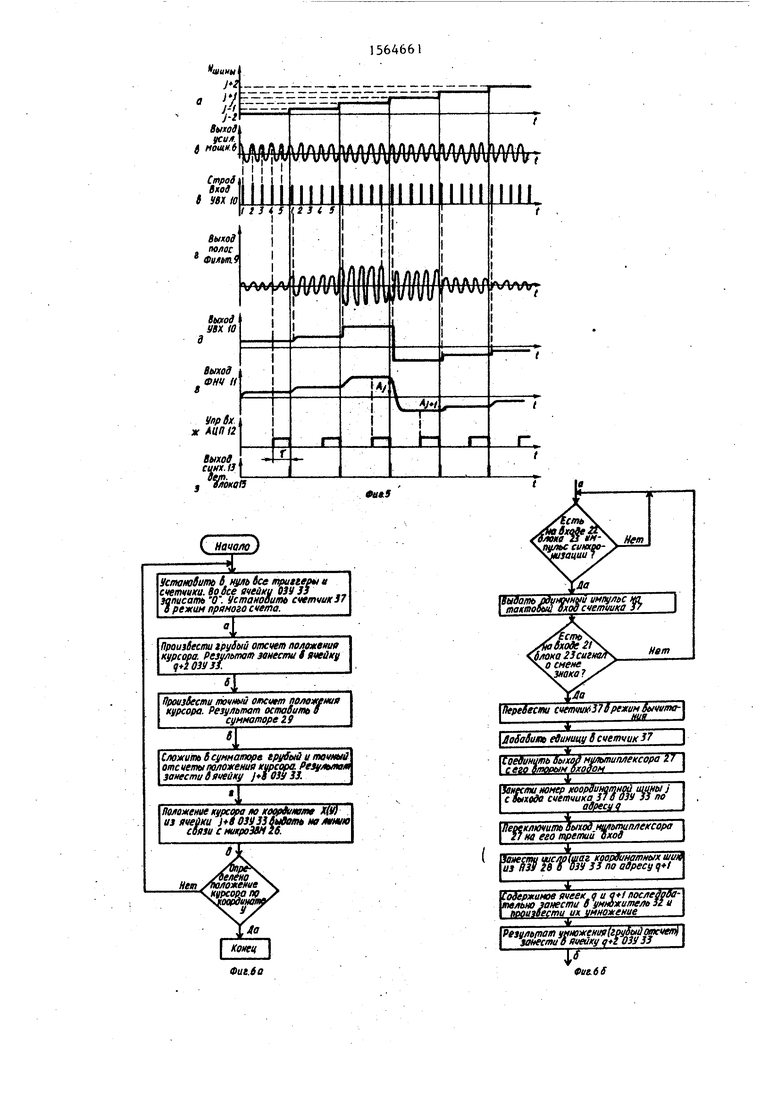

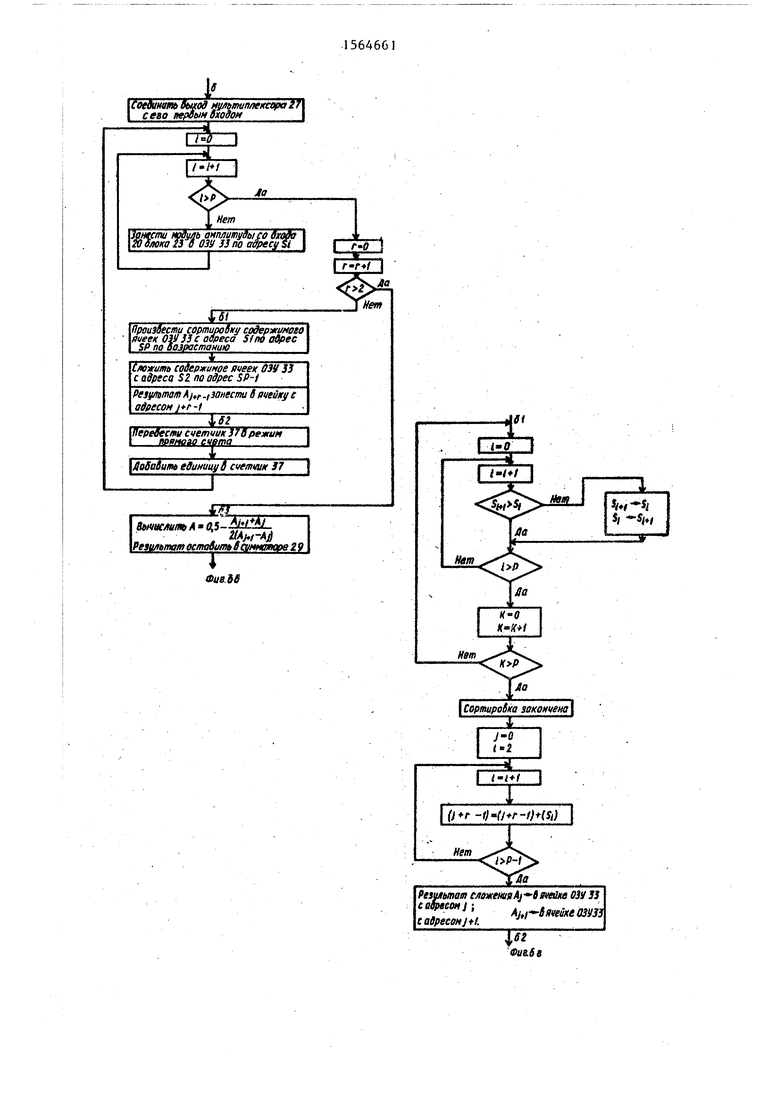

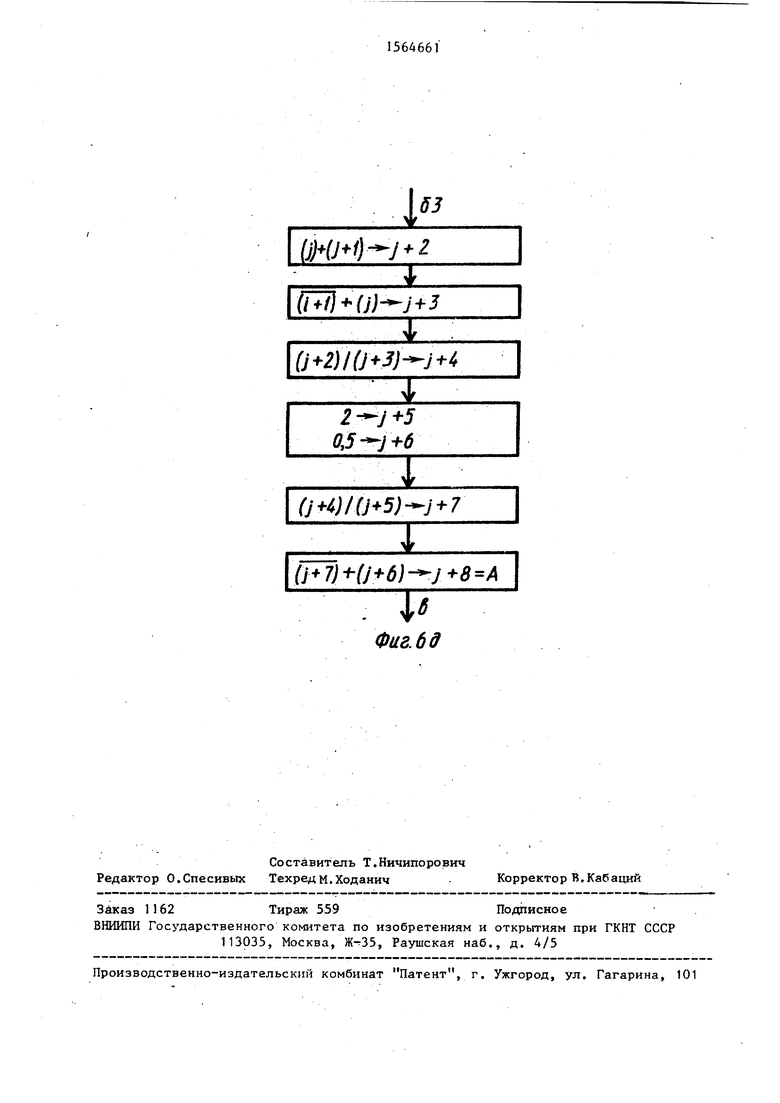

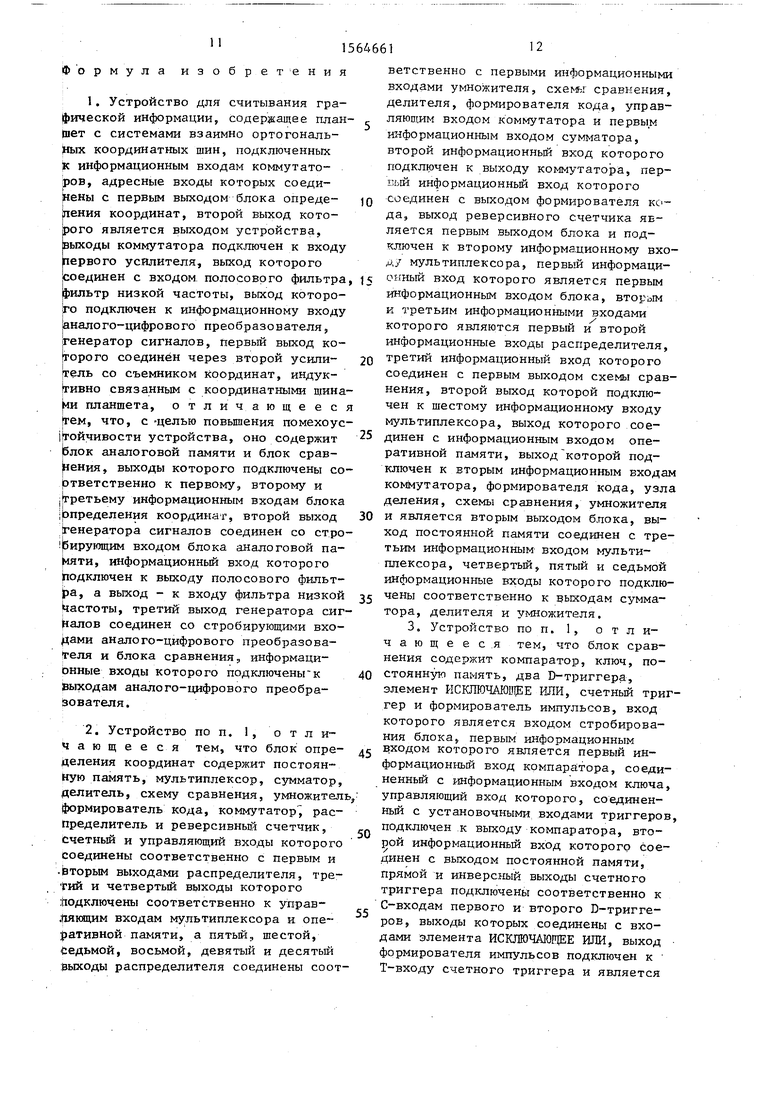

На фиг. 1 изображена блок-схема устройства; на фиг. 2 - структурная схема блока определения координат; на фиг. 3 - структурная схема блока сравнения; на фиг. 4 - диаграмма, поясняющая влияние одиночной импульсной помехи на амплитуду отсчета (модуль числа); на фиг. 5 - эпюры

напряжений в характерных точках схемы устройства; на фиг. 6 - алгоритм работы распределителя.

Устройство (фиг. 1) содержит план- шет 1 с системами взаимно ортогональных координатных шин 2, выполненных в виде одиночных проводников Х4,

ХйХ„ и У, ,У4,...,УП, уложенных

е постоянным шагом по осям X и У, Одни концы координатных шин подключены к общей шине устройства, а другие - к соответствующим информационным входам коммутатора 3 шин X и коммутатора 4 шин У. Катушка возбуждения съемника 5 координат подключена к выходу усилителя 6, вход которого соединен с выходом синусоидального сигнала генератора 7 сигналов. Информационные выходы коммутаторов 3 и 4 подключены ко входу последовательной цепочки, состоящей из усилителя 8, полосового фильтра 9, блока 10 аналоговой памяти, фильтра 11 нижних частот, АЦП 12, причем вход стробирования блока 10 и управляющий вход АЦП 12 соединены соответственно с выходом стробирования и управляющим входом генератора 7. Выходы модуля числа и знака числа АЦП 12 соединены соответственно с информционными входами (входами модуля числа и знака числа) 13 и 14 блока 15 сравнения, управляющий вход 16 которого соединен с управляющим выходом генератора 7. Выходы модуля числа 17, смены знака 18 и синхронизации 19 блока 15 сравнения соединены соответственно с входом 20 модуля числа, входом 21 смены знака и входом 22 синхронизации блока 23 определени координат. Выход 24 номера координатной шины блока 23 соединен с адресными входами коммутаторов 3 и 4. Информационный выход 25 блока 23 соединен с линией связи микроЭВМ 26, Вход 20 модуля числа и выход 24 номера координатной шины блока 23 соединены соответственно с первым и вторым информационными входами мультиплексора 27 (фиг. 2), к третьему информационному входу которого подключен выход постоянной памяти 28. Четвертый - седьмой информационные входы мультиплексора 27 соединены соответственно с выходом сумматора 29, делителя 30, информационным выходом схемы 31 сравнения и выходом умножи

5

0

5

0

5

0

5

0

5

теля 32. Выход мультиплексора 27 соединен с информационным входом оперативной памяти 33, выход которой соединен с информационными входами делителя 30, схемы 31 сравнения, умножителя 32 и формирователя 34 кодов, вход и выход которого соединены соответственно с первым и вторым информационными входами коммутатора 35, выход которого соединен с информационным входом сумматора 29. Управляющий выход схемы 31 сравнения соединен с п-ервым входом распределителя 36,второй вход которого, являющийся входом 21 смены знака блока 23 определения координат, соединен с выходом 18 смены знака блока 15 сравнения. Первый и второй выходы распределителя 36 соединены соответственно с тактовым входом и входом управления направлением счета счетчика 37 адреса шин, выход которого соединен с выходом номера координатной шины 24 блока 23, а с третьего по десятый выходы распределителя 36 соединены соответственно с управляющими входами сумматора 29, коммутатора 35, формирователя 34 (дополнительного) кода, делителя 30, схемы 31 сравнения, умножителя 32, оперативной памяти 33 и мультиплексора 27.

Блок 15 сравнения (фиг. 3) содержит компаратор 38, первый вход которого соединен с входом 13 модуля числа блока 15 и через ключ 39 соединен с выходом числа 17 блока 15 сравнения. Второй вход компаратора 38 соединен с выходом постоянной памяти 40. Вход 14 знака числа блока 15 соединен с D-входами первого 41 и второго 42 D- триггеров, прямые выходы которых через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 43 подключены к выходу 18 смены знака блока 15. Входы синхронизации первого 41 и второго 42 D-триггеров соединены соответственно с прямым и инверсным выходами счетного триггера 44, вход формирователя 45 подключен к управляющему входу 16 блока 15, входы устансгвки в ноль триггеров 41, 42 и 44 соединены с выходом компаратора 38 и с управляющим входом ключа 39, а выход формирователя 45 соединен с тактовым входом счетного триггера 44 и выходом 19 синхронизации блока 15.

Устройство для считывания графической информации работает следующим образом.

Излучаемый катушкой съемника 5 координат синусоидальный сигнал поочредно принимается координатными ткна ми XA,Xi}.. . ,ХП, У,УЈ,...,УП. Поло-

жение центра съемника координат определяется блоком 23 путем сложения грубого и точного отсчетов по каждой координате. Грубый отсчет определяется сменой фазы сигнала, индуцированного в соседних координатных шинах j и j + 1, и последующим умножением номера координатной шины j на расстояние между шинами. Смена фазы сигнала выявляется блоком 15 сравнения. При определении точного отсчета А устройство реализует уравнение линейной регрессии для двух усредненных амплитуд Aj и Ал,:

. n r Aj+i+Aj ,5- )

VAjt, Aj

Усредненные амплитуды Aj и Ajf1 определяются путем отбрасывания максимального и минимального модулей амплитуд и усреднения остальных модулей амплитуд в серии из Р отсчето взятых с одной и той же координатной шины j или j +1:

1 рм1 ри

А,- д.. д. 1- У А,, Г р-2 & V Р-2 Ј4A .J+r

Как видно из фиг. 4, в серии из 10 отсчетов (Р.Ю), взятых с j-й координатной шины, под влиянием одиночной импульсной помехи (фиг. 4а) искажены 5 (наибольший) и 6 (наименьший) модули амплитуд отсчетов А;; (фиг. 46), которые при сортировке по возрастанию перемещаются соответственно на 10 и 1 позиции (фиг. 4в) и затем отбрасываются при определении усредненного отсчета:

j 1 АГ 8 |гАЧГ

Число Р выбирают преимущественно в

пределах 5-20.

I

После установки съемника 5 в нужную точку планшета 1 (фиг. 1) оператор нажимает кнопку Пуск (не показана), в результате чего обнуляются все ячейки оперативной памяти 33 (фиг,. 2), реверсивный счетчик 37 адреса шин и сбрасываются в нуль тригеры 41, 42 и 44 (фиг. 3). На выходах блока 15 устанавливаются нулевые сигналы. С выхода счетчика 37 нуле,

6616

вой адрес поступает на второй вход мультиплексора 27 и через выход 24 номера координатной шины блока 23 - на адресные входы коммутаторов 3 и 4 шин X и У. Коммутатор 3 шин X подключает на вход усилителя 8 шину

X, (фиг. 5а). Поступающий с выхода

синусоидального сигнала генератора 7

синусоидальный сигнал с частотой преимущественно 200-400 кГц усиливается усилителем 6 (фиг. 56), который звпитывает катушку съемника 5. Величина наведенного в координатных шинах

X и У сигнала зависит от расстояния от них съемника 5. Усиленный усилителем 8 сигнал, наведенньй в координатной шине, пропускается через полосовой фильтр 9, центральная часто™

та полосы пропускания которого установлена равной частоте сигнала, излучаемого съемником 5. Отфильтрованный полосовым фильтром 9 сигнал (фиг.5г) поступает далее на информационный

вход блока 10 аналоговой памяти, на вход стробирования которого с выхода сигнала стробирования генератора 7 поступает серия из пяти строб-импульсов, синхронизированных во времени с вершиной положительной полуволны выходного напряжения усилителя 6 (, г. 5в) . Выходной сигнал блока 10 в виде полки постоянного напряжения (фиг. 5д) фильтруется от коммутационных выбросов и высокочастотных помех фильтром 11 нижних частот (фиг, 5е) и подается на информационный вход АЦП 12, на управляющий вход которого с управляющего выхода генератора 7 подается импульс длительностью около полутора периодов строб- импульсов, разрешающий оцифровывание сигналов (фиг. 5ж), причем передний фронт импульса Ј совпадает с

четвертым строб-импульсом серии. На выходе модуля числа АЦП 12 до окончания действия управляющего импульса устанавливается модуль числа, сог ответствующий амплитуде сигнала, наведенного в соответствующей координатной шине, а на выходе знака числа - знак числа, которые поступают на соответствующие входы 13 и 14 блока 15. Синхронизация работы блока 15

с процессом аналого-цифрового преоб- , разования осуществляется путем подачи на управляющий вход 16 блока 15 того же импульса с управляющего выхода генератора 7, что и на управляющий

вход АЦП 12 (фиг. 5ж)„ По заднему фронту этого импульса формирователем 45 (фиг. 3, фиг. 5з) генерируется импульс синхронизации, поступающий на тактовый вход счетного триггера 44 и на выход 19 синхронизации блока 15 В блоке 15 (фиг. 3) производится анализ оцифрованного сигнала по модулю и по знаку. Когда модуль числа, поступающий через вход 13 блока 15 на первый вход компаратора 38, меньше, чем заранее заданный порог шумов, поступающий в виде цифрового кода с выхода постоянной памяти 40 на второй вход компаоатора 38, триггеры 41, 42 и 44 удерживаются в нулевом состоянии 1, поступающей с выхода компаратора 38. Этим же сигналом с выхода компаратора 38 ключ 39 удержи зается в разомкнутом состоянии. На выходе модуля числа 17 блока 15 присутствует О. О с прямых выходов

D-триггеров 41 и 42 поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 43 и на его выходе, являющемся выходом J8 смены знака блока 15, присутствует Q. Нулевые значения с выходов 17 и 18 блока 15 поступают на входы 20 и 21 блока 23, который с приходом синхроимпульса с выхода 19 синхронизации блока 15 на вход 22 синхронизации блока 23 через выход 24 номера координатной шины разрешает опрос следующей координатной шины Х, путем добавления единицы в счетчик 37 (фиг. 5а).

Описанный процесс опроса координатных шин X продолжается до тех пор, пока модуль числа на первом вхо де комгГаратора 38 не превысит значения кода порога шумов на его второ входе, на его выходе появится О, разрешающий переключение всех триггеров блока 15, ключ 39 при этом замыкается и модуль числа проходит на выход модуля числа блока 15. На выходе 18 смены знака блока 15 будет удерживаться нулевой уровень. По мере приближения опрашиваемых, координатных шин к съемнику координат значение наведенного в них сигнала будет возрастать (фиг, 5г).

При каждом запуске процесса аналого-цифрового преобразования генератор 7 подает соответствующий импульс длительностью на управляющий вход АЦП 12 и управляющий вход 16 блока 15. В момент окончании этого

5

5

0

0

0

5

5

0

5

импульса формирователь 45 вырабатывает синхроимпульс, который поступает на тактовый вход счетного триггера 44 и на выход 19 синхронизации блока 15. Когда компаратор 38 разрешает работу триггеров, счетный триггер 44 год действием синхроимпульса с выхода формирователя 45 перебрасывается и по положительному фронту сигнала, поступающего с его прямого или инверсного выхода, записывает О или 1, поступающие с входа 14 знака числа 15 в соответствующий D-триггер. Пока знак числа не меняется, в обоих D-триггерах 41 и 42 записано одно и то же двоичное число - нуль или единица, и на выходе элемента 43 ИСКГОО- ЧАЮВ1ЕЕ ИЛИ присутствует О. Как только произойдет смена фазы считанного координатными шинами сигнала означающая, что на шине X: амплитуда сигнала имеет один знак, а на шине X , t - обратный знак, на входе 14 знака числа блока 15 логический сигнал изменится на противоположный, в одном из триггеров 41 или 42 состояние изменится на противоположное, на одном входе элемента 43 ИСКЛЮЧАЮЩЕЕ ИЛИ будет присутствовать О, на другом - 1 и на его выходе появится 1, которая поступит на выход 18 смены знака блока 15, С выхода 18 смены знака блока J5 1 поступает ма вход 21 смены знака блока 23 и далее на первый вход распределителя 36, Распределитель 36 -через первый управляющий выход подает на вход управления счета счетчика 37 сигнал на перевод его в режим вычитания, а через второй управляющий выход добавляет одиночньй импульс на тактовый вход счетчика 37 и на его выходе адрес меняется со значения j + 1 на j. Затем это-- число j через второй вход мультиплексора 27 распределитель 36 заносит в ячейку g оперативной памяти 33, а в ячейку g+1 заносит из постоянной памяти 28 число , соответствующее шагу координатной сбтки в миллиметрах. Значения из ячеек g, g+1 оперативной памяти 33 под управлением распределителя 36 последовательно заносятся в умножитель 32, а результат умножения, представляющий собой грубый отсчет положения съемника координат по координате X, заносится в ячейку g+2 оперативной памяти 33. Так заканчивается стадия

91

грубого отсчета положения центра съемника координат по координате X.

Затем распределитель 36 прекращает полачу импульсов на тактовый вход счетчика 37. Начинается точный отсчет положения съемника координат. Модули считанных с одной и той же координатной шины X; сигналов в тактах 1,2,..., Р поступают на вход модуля числа 20 блока 23 и далее через первый вход мультиплексора 27 по управлением распределителя 36 размещаются в ячейках Sl,S2,...,SP оперативной памяти 33. Далее распределитель 36 с помощью схемы 31 сравнения производит сортировку чисел в ячейка Sl,S2,...,SP по возрастанию, располагая наименьшее число в ячейке S1, а наибольшее - в ячейке SP. Сортировка производится Р раз путем последовательного занесения чисел из соседних ячеек S;, S,() в схему 31 сравнения и перемены адресов ячеек, если число из ячейки S больше числа

из ячейки S

ч Затем производится

сложение чисел из ячеек S2,,..,SP-1

под управлением распределителя 36 путем последовательных операций сложения содержимого ячейки j, имеющей первоначальное нулевое значение, с содержимым ячеек S2,...,SP-1, подаваемым из оперативной памяти 33 через коммутатор 35 на сумматор 29. Результат каждого сложения из сумматора 29 через четвертый вход мультиплексора

27 записывается в оперативную память 33 по адресу j. Затем распределитель 36 переводит счетчик 37 в режим прямого счета и подает одиночный импульс на его тактовый вход. На выходе счетчика 37 устанавливается адрес j+1. Распределитель 36 повторяет операции считывания модулей сигналов с шины X

JM

расположения и сортировки их по возрастанию в ячейках S1,S2,...,SP и сложения чисел из ячеек S2,...,SP-1, помещая результат в ячейку j+1 оперативной памяти 33. Затем под управлением распределителя 36 числа из ячеек j и j+1 оперативной памяти 33 последовательно подаются , через коммутатор 35, находящийся в первом положении, на сумматор 29 и сумма A:+AJ4i записывается в ячейку j+2. Затем число А:4, из ячейки j + 1 через коммутатор 35 заносится в сумматор 29, распределитель 36 переключает коммутатор 35 во второе поло10

Ч

в формирователь 34 кода, откуда дополнительный код числа л: через коммутатор 35 поступает в сумматор 29, где путем сложения с дополнительным кодом числа производится его вычитание. Результат сложения A -Ai заносится в ячейку j+З оперативной

памяти 33. Затем под управлением распределителя 36 числа Aj+Aj-H из ячейки j+2 и A:t(-A: из ячейки j+З оперативной памяти 33 последовательно заносятся в делитель 30, где первое

число делится на второе. Результат деления через пятый вход мультиплексора 27 заносится в ячейку j+4 оперативной памяти 33. В ячейках j+5, j+6 оперативной памяти 33 из постоянной памяти 28 через третий вход мультиплексора 27 последовательно заносятся константы 2 и 0,5. Затем содержимое ячеек j+4 и j+5 последовательно заносится в делитель 30, где первое число делится на второе и результат заносится в ячейку j+7 оперативной памяти 33. Затем распределите -:ь 36 переводит коммутатор 35 и заносит в сумматор 29 константу

0,5. Далее распределитель 36 переводит оммутатор 35 во второе положе- ние и из ячейки j+7 оперативной памяти 33 заносит число в формирователь 34 кодов, откуда дополнительный

код числа из ячейки j+7 поступает в сумматор 29 и путем сложения производится его вычитание из константы 0,5. Результат, являющийся точным отсчетом положения центра съемника

по координате X, остается в сумматоре 29. Распределитель 36 переводит коммутатор 35 в первое положение и из ячейки g+2 оперативной памяти 33 через коммутатор 35 заносит значение

грубого отсчета в сумматор 29. Результат сложения заносится в ячейку j+S. Содержимое ячейки j+8 оперативной памяти 33 является суммой грубого и точного отсчетов положения центра съемника по координате X. Содержимое этой ячейки оперативной памяти 33 под управлением распределителя 36 выдается на информационный выход 25 блока 23 и далее на линию связи с

микроЭВМ 26.

Аналогично определяется и положение съемника координат по координате У.

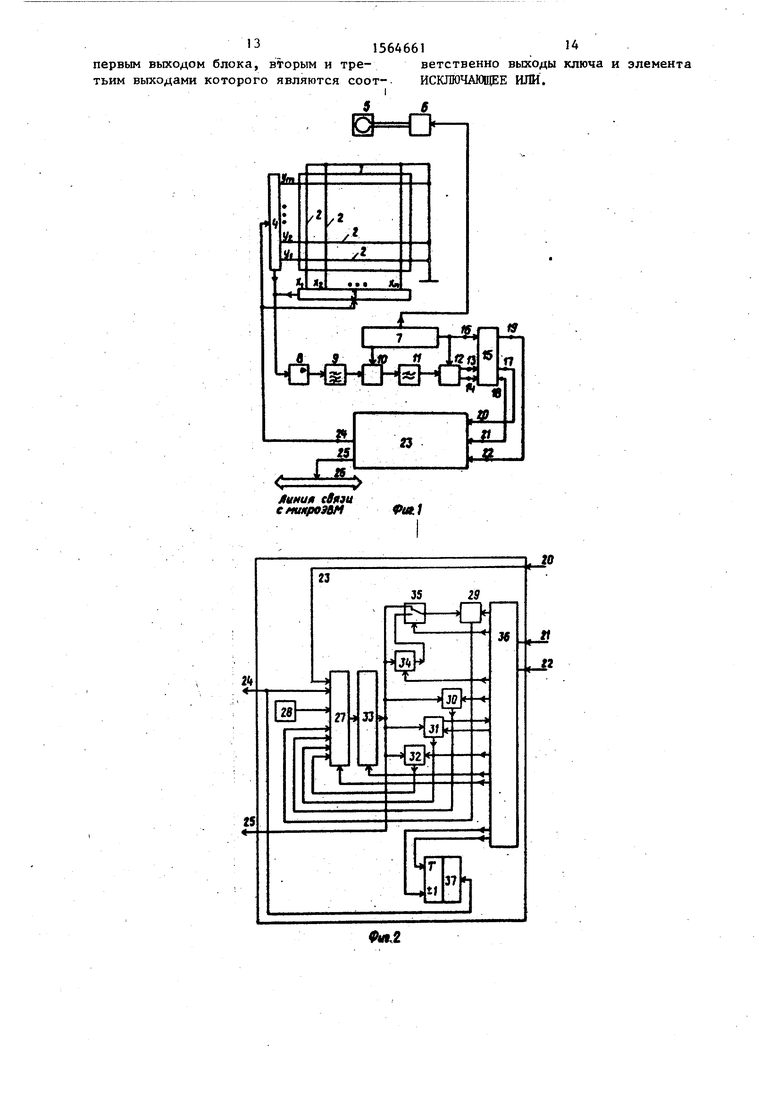

Формула изобретения

Q 5 0 0 5 0

45 „.

ветственно с первыми информационными входами умножителя, схемы сравнения, делителя, формирователя кода, управ- ляющим входом коммутатора и первым информационным входом сумматора, второй информационный вход которого подключен к выходу коммутатора, первый информационный вход которого соединен с выходом формирователя ки- да, выход реверсивного счетчика является первым выходом блока и подключен к второму информационному входу мультиплексора, первый информационный вход которого является первым информационным входом блока, вторым и третьим информационными входами которого являются первый и второй информационные входы распределителя, третий информационный вход которого соединен с первым выходом схемы сравнения, второй выход которой подключен к шестому информационному входу мультиплексора, выход которого соединен с информационным входом оперативной памяти, выход которой подключен к вторым информационным входам коммутатора, формирователя кода, узла деления, схемы сравнения, умножителя и является вторым выходом блока, выход постоянной памяти соединен с третьим информационным входом мультиплексора, четвертый, пятый и седьмой информационные входы которого подключены соответственно к выходам сумматора, делителя и умножителя.

ГЙ

Линия связи с микроЭЬМ

Ik

27

а

п

а

JL

Фае/

3529

Я

л LLi

Л

J k

-Q«

ut

пон.

Л ,;

12345678 9 10 t

6

4,7

Фаг. а

53

L

UHH-У+г

(Fti+U} i+3 I

(j+2)/(J+3)j+4

OJ)+6

I

(«)l(l+5) + 7 |

««мшшшнш вшшмш н ммммшкшнмняишД

V

(1+7)+и+6)

53

I

6

Фиг.6д

Авторы

Даты

1990-05-15—Публикация

1987-10-12—Подача