Изобретение относится к средствам обучения и пособиям для учебных целей и предназначено для отображения век- Торных диаграмм токов и напряжений. Цель изобретения - повышение быстродействия устройства.

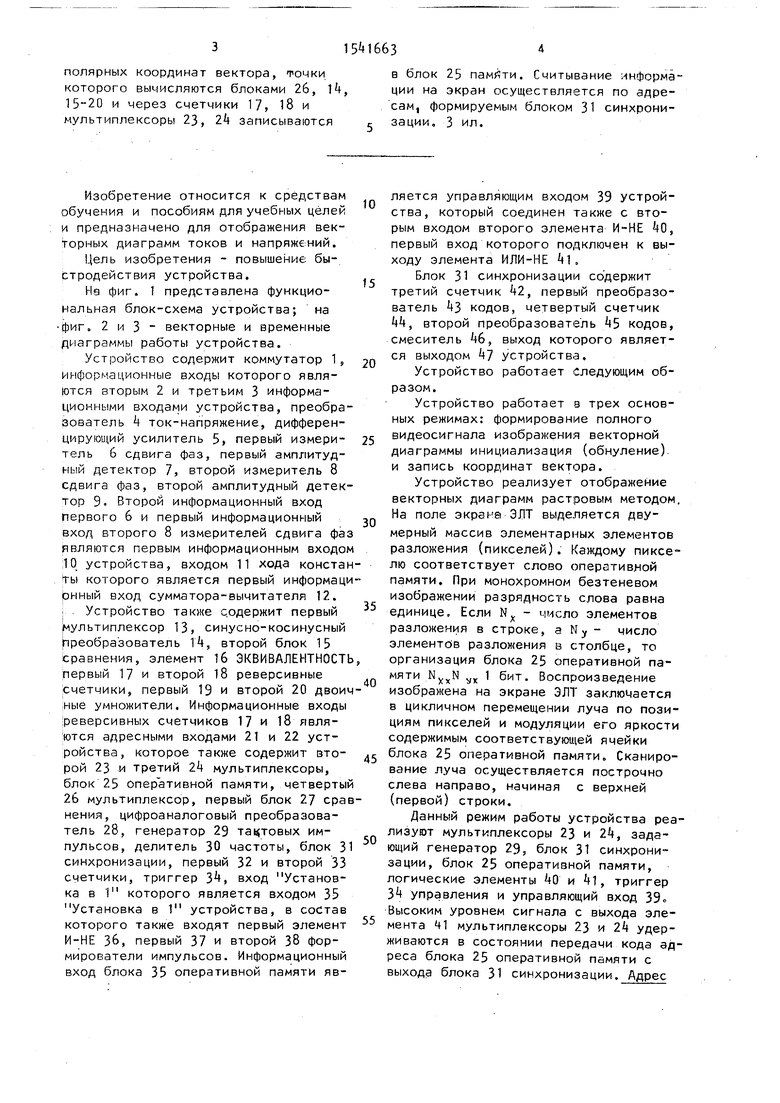

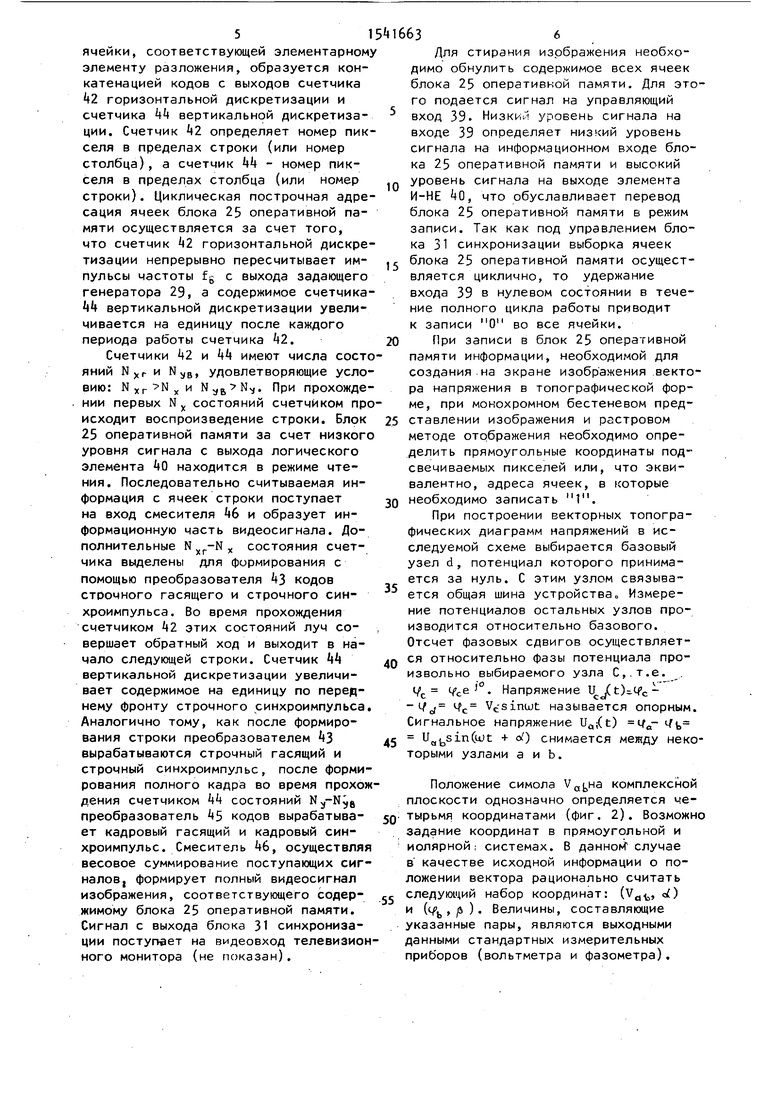

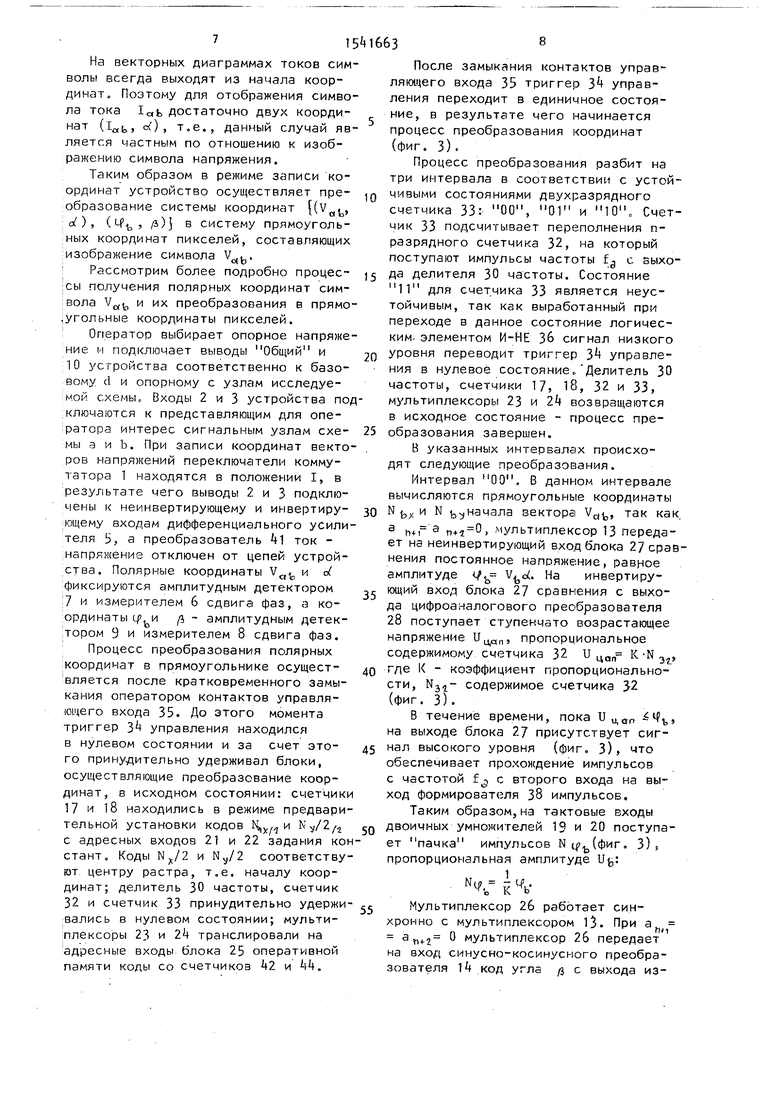

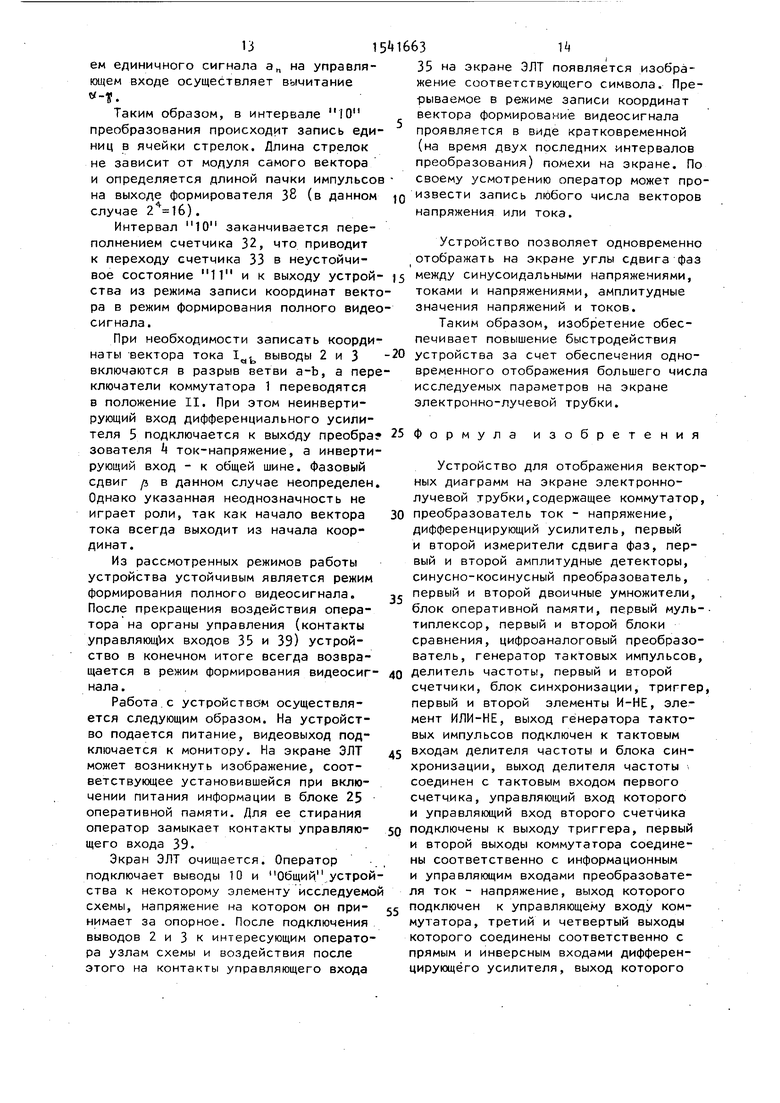

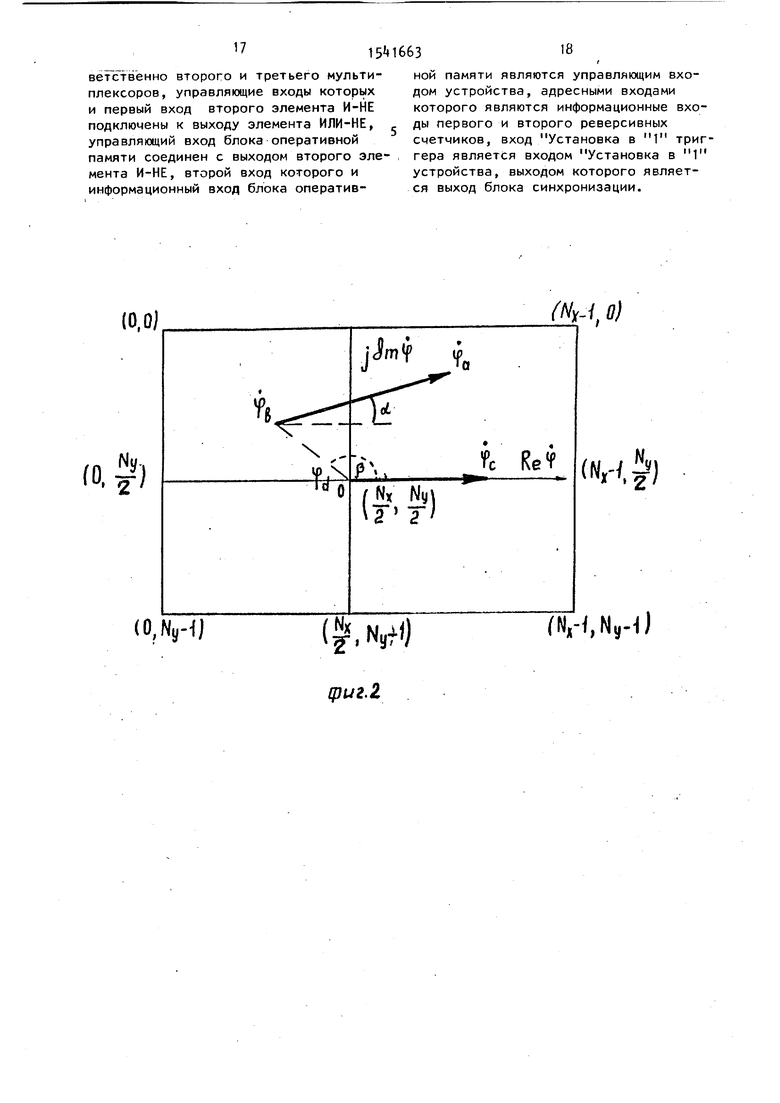

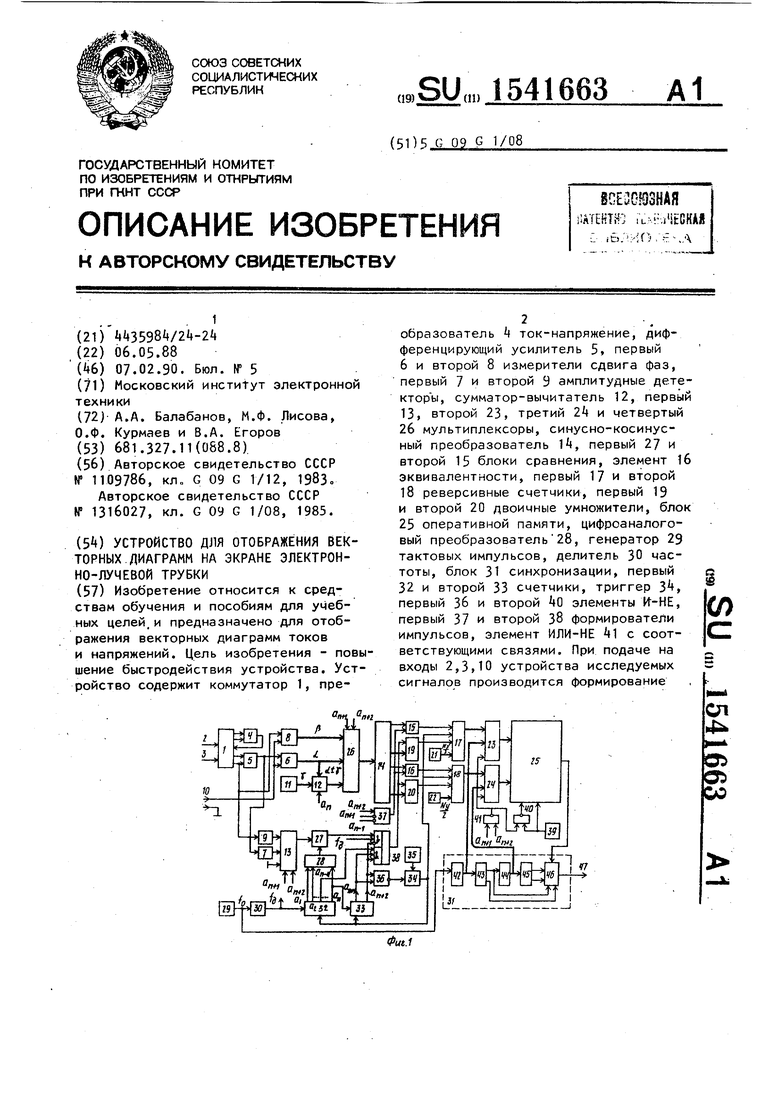

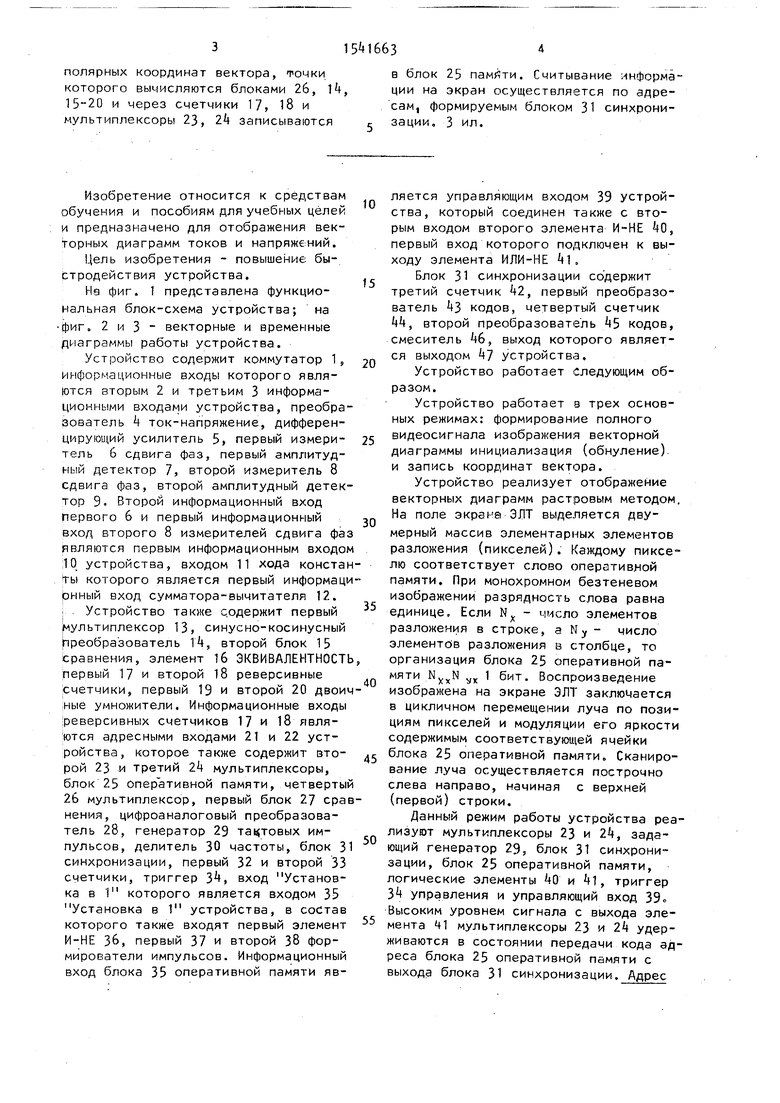

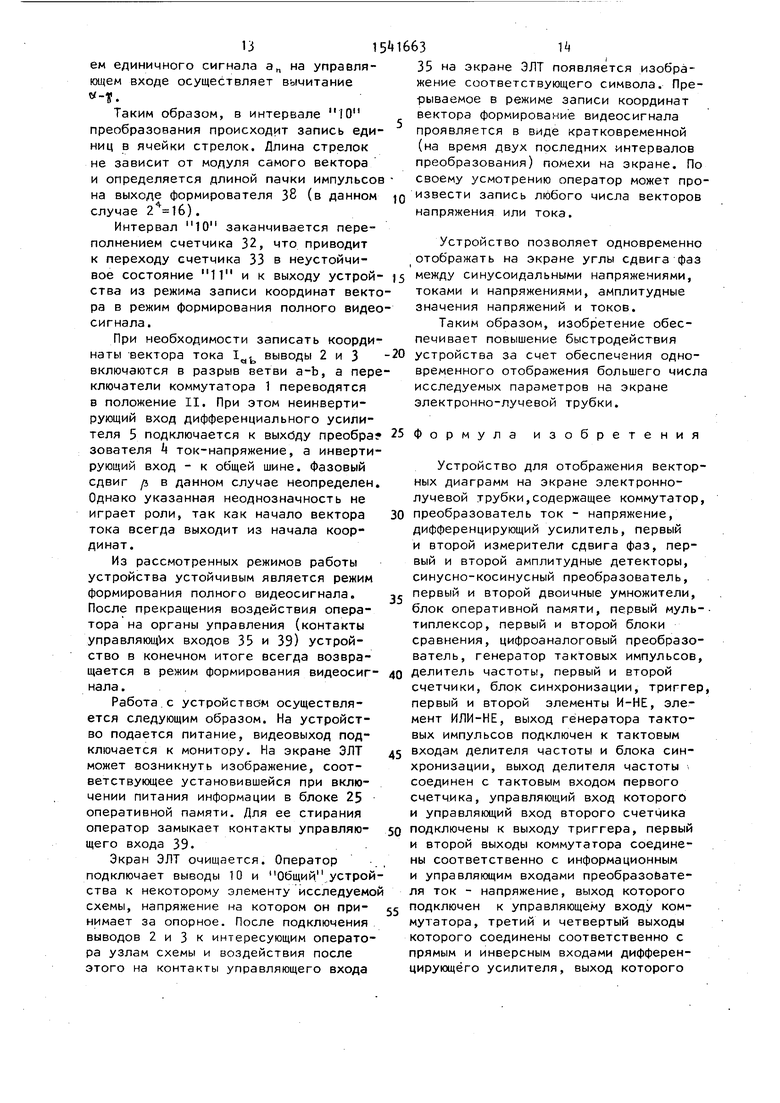

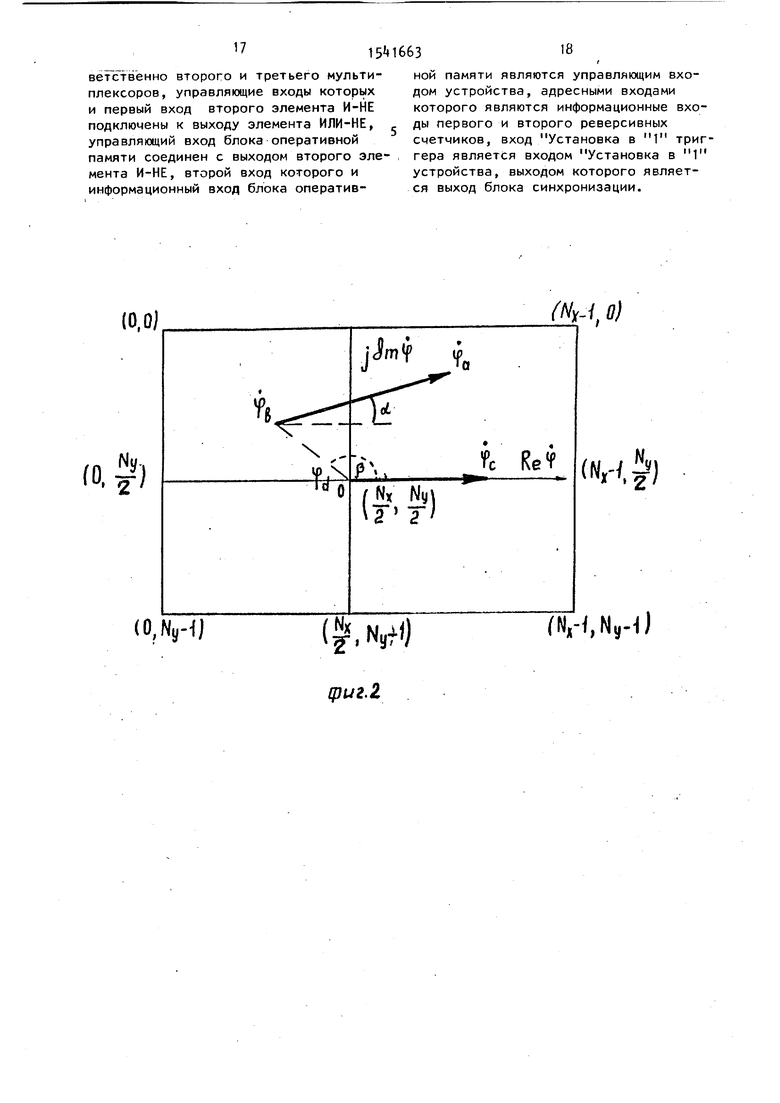

На фиг. 1 представлена функциональная блок-схема устройства; на фиг. 2 и 3 векторные и временные диаграммы работы устройства.

Устройство содержит коммутатор 1, Информационные входы которого являются вторым 2 и третьим 3 информационными входами устройства, преобразователь k ток-напряжение, дифференцирующий усилитель 5, первый измеритель б сдвига фаз, первый амплитудный детектор 7, второй измеритель 8 сдвига фаз, второй амплитудный детектор 9. Второй информационный вход Первого 6 и первый информационный вход второго 8 измерителей сдвига фаз рвляются первым информационным входом 10 устройства, входом 11 хода константы которого является первый информационный вход сумматора-вычитателя 12. Устройство также содержит первый мультиплексор 13, синусно-косинусный Преобразователь 14„ второй блок 15 сравнения, элемент 16 ЭКВИВАЛЕНТНОСТЬ, первый 17 и второй 18 реверсивные сметчики, первый 19 и второй 20 двоичные умножители. Информационные входы реверсивных счетчиков 17 и 18 являются адресными входами 21 и 22 устройства, которое также содержит второй 23 и третий 2k мультиплексоры, блок 25 оперативной памяти, четвертый 26 мультиплексор, первый блок 27 сравнения, цифроаналоговый преобразователь 28, генератор 29 тацтовых импульсов, делитель 30 частоты, блок 31 синхронизации, первый 32 и второй 33 счетчики, триггер 3, вход Установка в 1 которого является входом 35 Установка в 1 устройства, в состав которого также входят первый элемент И-НЕ 36, первый 37 и второй 38 формирователи импульсов. Информационный вход блока 35 оперативной памяти яв

5

0

5

0

5

0

5

0

5

ляется управляющим входом 39 устройства, который соединен также с вторым входом второго элемента И-НЕ 0, первый вход которого подключен к выходу элемента ИЛИ-НЕ Ц,

Блок 31 синхронизации содержит третий счетчик k2, первый преобразователь k3 кодов, четвертый счетчик kk, второй преобразователь kS кодов, смеситель k69 выход которого является выходом kj устройства.

Устройство работает следующим образом.

Устройство работает в трех основных режимах: формирование полного видеосигнала изображения векторной диаграммы инициализация (обнуление) и запись координат вектора.

Устройство реализует отображение векторных диаграмм растровым методом. На поле экрана ЭЛТ выдепяется двумерный массив элементарных элементов разложения (пикселей). Каждому пикселю соответствует слово оперативной памяти. При монохромном безтеневом изображении разрядность слова равна единице. Если NX - число элементов разложения в строке, a Ny - число элементов разложения в столбце, то организация блока 25 оперативной памяти NXxN VK 1 бит. Воспроизведение изображена на экране ЭЛТ заключается в цикличном перемещении луча по позициям пикселей и модуляции его яркости содержимым соответствующей ячейки блока 25 оперативной памяти. Сканирование луча осуществляется построчно слева направо, начиная с верхней (первой) строки.

Данный режим работы устройства реализуют мультиплексоры 23 и 2k, задающий генератор 29, блок 31 синхронизации, блок 25 оперативной памяти, логические элементы kQ и П , триггер 3k управления и управляющий вход 39 Высоким уровнем сигнала с выхода элемента 41 мультиплексоры 23 и 2k удерживаются в состоянии передачи кода адреса блока 25 оперативной памяти с выхода блока 31 синхронизации. Адрес

ячейки, соответствующей элементарному элементу разложения, образуется конкатенацией кодов с выходов счетчика 42 горизонтальной дискретизации и счетчика 44 вертикальной дискретиза- ции. Счетчик 42 определяет номер пикселя в пределах строки (или номер столбца), а счетчик 44 - номер пикселя в пределах столбца (или номер строки). Циклическая построчная адресация ячеек блока 25 оперативной памяти осуществляется за счет того, что счетчик 42 горизонтальной дискретизации непрерывно пересчитывает им- пульсы частоты f6 с выхода задающего генератора 29, а содержимое счетчика- № вертикальной дискретизации увеличивается на единицу после каждого периода работы счетчика 42.

Счетчики 42 и 44 имеют числа состояний Nxr и МуВ, удовлетворяющие условию: ,. При прохождении первых Nx состояний счетчиком происходит воспроизведение строки. Блок 25 оперативной памяти за счет низкого уровня сигнала с выхода логического элемента 40 находится в режиме чтения. Последовательно считываемая информация с ячеек строки поступает на вход смесителя 46 и образует информационную часть видеосигнала. Дополнительные NXf-Nx состояния счетчика выделены для формирования с помощью преобразователя 43 кодов строчного гасящего и строчного синхроимпульса. Во время прохождения счетчиком 42 этих состояний луч совершает обратный ход и выходит в начало следующей строки. Счетчик 44 вертикальной дискретизации увеличивает содержимое на единицу по переднему фронту строчного синхроимпульса. Аналогично тому, как после формирования строки преобразователем 43 вырабатываются строчный гасящий и строчный синхроимпульс, после формирования полного кадра во время прохождения счетчиком 44 состояний преобразователь 45 кодов вырабатыва- ет кадровый гасящий и кадровый синхроимпульс. Смеситель 46, осуществляя весовое суммирование поступающих сигналов, формирует полный видеосигнал изображения, соответствующего содер- жимому блока 25 оперативной памяти. Сигнал с выхода блока 31 синхронизации поступает на видеовход телевизионного монитора (не показан).

- 0 г 0

5 п Q 0

5

5

Для стирания изображения необходимо обнулить содержимое всех ячеек блока 25 оперативной памяти. Для этого подается сигнал на управляющий вход 39. Низкий уровень сигнала на входе 39 определяет низкий уровень сигнала на информационном входе блока 25 оперативной памяти и высокий уровень сигнала на выходе элемента И-НЕ 40, что обуславливает перевод блока 25 оперативной памяти в режим записи. Так как под управлением блока 31 синхронизации выборка ячеек блока 25 оперативной памяти осуществляется циклично, то удержание входа 39 в нулевом состоянии в течение полного цикла работы приводит к записи О во все ячейки.

При записи в блок 25 оперативной памяти информации, необходимой для создания на экране изображения вектора напряжения в топографической форме, при монохромном бестеневом представлении изображения и растровом методе отображения необходимо определить прямоугольные координаты подсвечиваемых пикселей или, что эквивалентно, адреса ячеек, в которые необходимо записать 1.

При построении векторных топографических диаграмм напряжений в исследуемой схеме выбирается базовый узел d, потенциал которого принимается за нуль. С этим узлом связывается общая шина устройства Измерение потенциалов остальных узлов производится относительно базового. Отсчет фазовых сдвигов осуществляется относительно фазы потенциала произвольно выбираемого узла С, т.е. Vc Напряжение 15 Jit)-ifс- - Чd Ус Vc-sinujt называется опорным. Сигнальное напряжение Uai(t) ife- Uabsin(ujt + л ) снимается между некоторыми узлами а и Ь.

Положение симола комплексной плоскости однозначно определяется четырьмя координатами (фиг. 2). Возможно задание координат в прямоугольной и полярной системах. В данном случае в качестве исходной информации о положении вектора рационально считать следующий набор координат: (Vat, «О и (vb , ja ). Величины, составляющие указанные пары, являются выходными данными стандартных измерительных приборов (вольтметра и фазометра).

71

На векторных диаграммах токов символы всегда выходят из начала координат. Поэтому для отображения символа тока 1аь достаточно двух координат (lab, °0 т.е., данный случай является частным по отношению к изображению символа напряжения.

Таким образом в режиме записи координат устройство осуществляет преобразование системы координат ((V, оО ( 5 А)} в систему прямоугольных координат пикселей, составляющих изображение символа V,

Рассмотрим более подробно процессы получения полярных координат символа УйЬ и их преобразования в прямо ,угольные координаты пикселей.

Оператор выбирает опорное напряже

ние и подключает выводы Общий и

10 устройства соответственно к базовому d и опорному с узлам исследуемой схемы. Входы 2 и 3 устройства поключаются к представляющим для оператора интерес сигнальным узлам схемы э и Ъ. При записи координат векторов напряжений переключатели коммутатора 1 находятся в положении I, в результате чего выводы 2 и 3 подключены к иеинвертирующему и инвертирующему входам дифференциального усилителя 5, а преобразователь 41 ток - напряжение отключен от цепей устройства. Полярные координаты VC(b и с( фиксируются амплитудным детектором 7 и измерителем 6 сдвига фаз, а координаты if .и ft амплитудным детектором 9 и измерителем 8 сдвига фаз. Процесс преобразования полярных координат в прямоугольнике осуществляется после кратковременного замыкания оператором контактов управляющего входа 35. До этого момента триггер 34 управления находился в нулевом состоянии и за счет этого принудительно удерживал блоки, осуществляющие преобразование координат, в исходном состоянии: счетчик 17 и 18 находились в режиме предварительной установки кодов Н,х и Ny/2/2 с адресных входов 21 и 22 задания костант. Коды и Ny/2 соответствуют центру растра, т.е. началу координат; делитель 30 частоты, счетчик 32 и счетчик 33 принудительно удержи вались в нулевом состоянии; мультиплексоры 23 и 2k транслировали на адресные входы блока 25 оперативной памяти коды со счетчиков 42 и 44.

8

0

5

0

5

После замыкания контактов управляющего входа 35 триггер 34 управления переходит в единичное состояние, в результате чего начинается процесс преобразования координат (фиг. 3).

Процесс преобразования разбит на три интервала в соответствии с устойчивыми состояниями двухразрядного счетчика 33: 00, 01 и 10,, Счетчик 33 подсчитывает переполнения п- разрядного счетчика 32, на который поступают импульсы частоты fa с выхода делителя 30 частоты. Состояние 11 для счетчика 33 является неустойчивым, так как выработанный при переходе в данное состояние логическим- элементом И-НЕ 36 сигнал низкого уровня переводит триггер 34 управления в нулевое состояние, Делитель 30 частоты, счетчики 17, 18, 32 и 33, мультиплексоры 23 и 24 возвращаются в исходное состояние - процесс пре- 5 образования завершен.

В указанных интервалах происходят следующие преобразования.

Интервал 00, В данном интервале вычисляются прямоугольные координаты 0 N ьр и N уначала вектора Vd, так как a h+ а , мультиплексор 13 передает на неинвертирующий вход блока 27 сравнения постоянное напряжение, равное амплитуде ъ . На инвертиру- 5 ющий вход блока 2 сравнения с выхода цифроаналогового преобразователя 28 поступает ступенчато возрастающее напряжение U,,, пропорциональное содержимому счетчика 32 U цап K-N3i, где К - коэффициент пропорциональности, N31- содержимое счетчика 2 (фиг. 3).

В течение времени, пока U , на выходе блока 27 присутствует сигнал высокого уровня (фиг. 3), что обеспечивает прохождение импульсов с частотой f с второго входа на выход формирователя 38 импульсов.

Таким образом,на тактовые входы 50 двоичных умножителей 19 и 20 поступает пачка импульсов N (фиг. 3) , пропорциональная амплитуде U,:

i ъ

Мультиплексор 26 работает синхронно с мультиплексором 13. При а

0

45

Кн

а

tn-2

0 мультиплексор 26 передает на вход синусно-косинусного преобразователя 14 код угла ft с выхода измерителя 8 фазового сдвига. На управляющие входы двоичных умножителей 19 и 20 поступают коды модулей функций косинуса и синуса Icos/jlM Isin/sf. Следовательно, на выходах умножителей 19 и 20 в течение данного интервала

формируются пачки, содержащие

NL/ Jcos/ Ј fjcosp/

NU |sinft| |sin|S bК ь

импульсов.

Данные величины являются модулями координат начала вектора относительно центра растра, имеющего координаты Nx/2 и Ny/2. Абсолютные координаты начала вектора, с учетом направления нумерации пикселей сверху вниз и слева направо, должны рассчитываться по формулам

NX 1

+ -i cos/з;. N 1

Nbx 2

(2)

N

Ъ/ Г

Таким образом, направление подсчета (в плюс или в минус) пачек импульсов NfgM N2fl счетчиками 17 и 18, в которых предварительно установлены коды

Nx/2

и

Nu/2, определяется как знаками

тригонометрических функций, так и координатой (X или Y). В устройстве принята следующая кодировка знаков тригонометрических функций и направления счета: + -0; счет на увеличение, --0; счет на вычитание 1. С учетом указанных кодировок сигналы направления счета D( и D{i счетчиков 17 и 18 задаются выражениями

D14 sign(sin/3)

где sign функция знака величины, х;

П х °; о

sign х ., п В анализируемом X У U

тервале преобразования низкий уровень сигнала а п+1 обуславливает низкий уровень сигнала на выходе формирователя 37. Следовательно, на выходе блока 15 сравнения реализующего логическую функцию НЕЭКВИВАЛЕНТНОСТЬ, сигнал соответствует функции знака sign(cos/j), а на выходе элемента 16, реализующего логическую функцию ЭКВИ ВАЛЕНТНОСТЬ, сигнал соответствует отрицанию функции знака sign(sinp). Таким образом устройство реализует вычисление абсолютных координат на

30

45

-55 чала-вектора иаЪ согласно выражениям (2).

В течение данного интервала устройство продолжает формирование видеосигнала, соответствующего прежнему содержимому оперативной памяти, так как а „,., а 0 и, следовательно, адресация оперативной памяти, нахо- JQ дящейся в режиме чтения, осуществляется блоком 31 синхронизации. Интервал завершается переполнением счетчика 32 и переходом счетчика 33 в состояние 01 (a h+ 0, а п+1 1). 15 Интервал 01. В данном интервале происходит запись единиц в те ячейки блока 25 оперативной памяти, которые соответствуют пикселям, расположенным на отрезке прямой между началом и кон- 20 цом вектора VaV

Единичное значение сигнала на выходе логического элемента ИЛИ-НЕ 41 опре- деляет нулевой сигнал на входе логического элемента И-НЕ 40, что обуславлива- 25 ет высокий уровень сигнала на управляющем входе блока 25 оперативной памяти и, следовательно, перевод его в режим записи. На информационный вход блока 25 оперативной памяти с управляющего . входа 39 поступает сигнал высокого уровня.

Адресация необходимых ячеек блока 25 памяти происходит следующим образом,, Синхронно работающие мультиплексоры 13 и 26 в анализируемом интервале преобразования транслируют на свои выходы сигналы с вторых входов. Следовательно, синусно-косинусный преобразователь 14 на своих выходах форми- 40 РУет коды знака функции косинуса sign(cosoO, модуля icosotf, знака функции синуса sign(sinoO и модуля | sino/l.

Так как счетчик 32 к началу данного интервала был обнулен (через переполнение) , то (по аналогии с работой блоков в интервале 00) на выходе формирователя 38 формируется пач35

5

ка импульсов Nx/afc пропорциональная 5о амплитуде аЬ (фиг. з)

N

vat I Vat

На выходах двоичных умножителей и 20 формируются пачки

1 Vqb.|coSoff;

N,3

Nvot/cosrf к

N4o Ny /siiW/ - Veb|sino(/

eW

К

Низкий уровень сигнала а„41обуславливает нулевой сигнал на выходе формирователя 37. Поэтому закон выработки сигналов направления счета идентичен закону в интервале 00, т.е, сигналы направления счета D17 и D 18 счетчиков 17 и 18 задаются выражениями

10

2 Lf SiSBlc°S Dfg sign(sinof)

В начале рассматриваемого интервала преобразования содержимые счетчике 17 и 18 определяются выражениями (2), т.е. соответствуют координатам точки М Лначальной точки вектора аъ) С учетом знаков тригонометрических функций и направления счета к моменту1 окончания выработки пачки импульсов N содержимые счетчиков 17 и 18 ся соотношениями

задают- 20

1UNfev+

Nc.y NbT

v coso(;

уаЪ

sine/.

(3)

Величины N и ординатам точки

U.

Vat,

N а;, соответствуют ко- Ч4 -конечной точки

СТ

вектора и,,, ° процессе счета содержимые счетчиков 17 и 18 проходят координаты всех пикселей, расположенных на прямой между начальной и конечной точками-вектора U ab. В ячейки блока 25 оперативной памяти, соответстЕэую- щие данным пикселям, записываются единицы, так как блок 25 оперативной памяти находится в режиме записи, а на его информационном входе 39 присутствует единичный сигнал. Интервал Ыак и предыдущий) завершается переполнением счетчика 32 и переходом счетчика 33 в состояние 10.

Интервал 10 В этом интервале происходит запись единиц в ячейки блока 2 оперативной памяти, которые соответствуют пикселям, изображающим стрелки на конце вектора.

За счет единичного значения второго разряда a h+1 счетчика 33 адресные входы блока 25 оперативной памяти остаются подключенными к счетчикам 17 и 18, оперативная память на информационном входе которой поддерживается высокий уровень сигнала, продолжает удерживаться в режиме записи. Входы мультиплексоров 26 и 13 подключены соответственно к выходу суммато- ра-вычитателя 12 и общей шине устройства, Так как в анализируемом интер-

вале ап+г 1, a a n+f 0, прохождение импульсов f , через формирователь 38

заблокировано. Сигнал на выходе формирователя 38 соответствует разряду a „4-1 счетчика 32.

Таким образом, за весь интервал на тактовые входы двоичных умножителей 19 и 20 поступает пачка, содержащая 2 -16 импульсов (фиг. 3). Адресация лучей стрелок вектора осуществляется за четыре подинтервала (в соответствии с изменениями разряда a h счетчика 32). В первом под- интервале происходит запись единицы в ячейки правой, если смотреть по направлению вектора, стрелки. Сумматор- вычитатель 12 низким значением сигнала а„ переводится в режим суммирования. На его выходе формируется код t + -y, где

If-- угол ориентации стрелки относительно направления вектора. Код угла

7 поступает с выхода блока 11 задания константы. На выходе формирователя 37 за счет низкого значения сигнала а „, в данном подинтервале сигнал равен 1. Поэтому сигналы направления счета счетчиков 17 и 18 инвертируются

D17 (o( + y) ; D 1g (o(+ -p

Содержимые счетчиков 17 и 18 изменяются, образуя координаты пикселей правой стрелки в направлении от кон- ца вектора к концу стрелки (фиг. 3) Во втором подинтервале по отношению к первому изменяется только значение сигнала а

П-1

Сигналы направления счета восстанавливаются.

Di7 I Јig2ЈЈ2S i3l2J D,j sign sinW+ $

В результате координаты адресуемых пикселей изменяются в обратном направлении: от конца стрелки к концу вектора (фиг. 3). Второй подинтервал, таким образом, дублирует уже осуществленную в первом подинтервале запись единиц в ячейки правой стрелки, но необходим для восстановления в счетчиках 17 и 18 координат конца вектора.

В третьем и четвертом подинтерва- лах п#- аналогии с первым и вторым происходит запись единиц в ячейки левой стрелки (фиг. 3). Процессы, протекающие в данных подинтервалах, идентичны, за исключением того, что сумматор-вычитатель 12 под действии

ем единичного сигнала ап на управляющем входе осуществляет вычитание «-Я.

Таким образом, в интервале 10 преобразования происходит запись единиц в ячейки стрелок. Длина стрелок не зависит от модуля самого вектора и определяется длиной пачки импульсов на выходе формирователя 38 (в данном случае 2 16).

Интервал 10 заканчивается переполнением счетчика 32, что приводит к переходу счетчика 33 в неустойчивое состояние 11 и к выходу устройства из режима записи координат вектора в режим формирования полного видеосигнала.

При необходимости записать коордиТаким образом, изобретение обеспечивает повышение быстродействия 20 устройства за счет обеспечения одновременного отображения большего числа исследуемых параметров на экране электронно-лучевой трубки.

30

35

наты вектора тока I4t выводы 2 и 3 включаются в разрыв ветви а-Ъ, а переключатели коммутатора 1 переводятся в положение II. При этом неинвертирующий вход дифференциального усилителя 5 подключается к выхбду преобра 25 формула изобретения зователя k ток-напряжение, а инвертирующий вход - к общей шине. Фазовый сдвиг р в данном случае неопределен. Однако указанная неоднозначность не играет роли, так как начало вектора тока всегда выходит из начала координат.

Из рассмотренных режимов работы устройства устойчивым является режим формирования полного видеосигнала. После прекращения воздействия оператора на органы управления (контакты управляющих входов 35 и 39) устройство в конечном итоге всегда возвращается в режим формирования видеоси - нала.

Работа с устройством осуществляется следующим образом. На устройство подается питание, видеовыход подключается к монитору. На экране ЭЛТ может возникнуть изображение, соответствующее установившейся при включении питания информации в блоке 25 оперативной памяти. Для ее стирания оператор замыкает контакты управляющего входа 39.

Экран ЭЛТ очищается. Оператор

40

Устройство для отображения векторных диаграмм на экране электроннолучевой трубки,содержащее коммутатор, преобразователь ток - напряжение, дифференцирующий усилитель, первый и второй измерители сдвига фаз, первый и второй амплитудные детекторы, синусно-косинусный преобразователь, первый и второй двоичные умножители, блок оперативной памяти, первый мультиплексор, первый и второй блоки сравнения, цифроаналоговый преобразователь, генератор тактовых импульсов, делитель частоты, первый и второй счетчики, блок синхронизации, триггер первый и второй элементы И-НЕ, элемент ИЛИ-НЕ, выход генератора тактовых импульсов подключен к тактовым

д5 входам делителя частоты и блока синхронизации, выход делителя частоты соединен с тактовым входом первого счетчика, управляющий вход которого и управляющий вход второго счетчика

50 подключены к выходу триггера, первый и второй выходы коммутатора соединены соответственно с информационным и управляющим входами преобразователя ток - напряжение, выход которого подключен к управляющему входу коммутатора, третий и четвертый выходы которого соединены соответственно с прямым и инверсным входами дифференцирующего усилителя, выход которого

подключает выводы 10 и Общий устройства к некоторому элементу исследуемой схемы, напряжение на котором он принимает за опорное. После подключения выводов 2 и 3 к интересующим оператора узлам схемы и воздействия после этого на контакты управляющего входа

1663Т

35 на экране ЭЛТ появляется изображение соответствующего символа. Прерываемое в режиме записи координат вектора формирование видеосигнала проявляется в виде кратковременной (на время двух последних интервалов преобразования) помехи на экране. По своему усмотрению оператор может произвести запись любого числа векторов напряжения или тока.

10

Устройство позволяет одновременно отображать на экране углы сдвига фаз между синусоидальными напряжениями, токами и напряжениями, амплитудные значения напряжений и токов.

Таким образом, изобретение обеспечивает повышение быстродействия устройства за счет обеспечения одновременного отображения большего числа исследуемых параметров на экране электронно-лучевой трубки.

формула изобретения

формула изобретения

Устройство для отображения векторных диаграмм на экране электроннолучевой трубки,содержащее коммутатор, преобразователь ток - напряжение, дифференцирующий усилитель, первый и второй измерители сдвига фаз, первый и второй амплитудные детекторы, синусно-косинусный преобразователь, первый и второй двоичные умножители, блок оперативной памяти, первый муль типлексор, первый и второй блоки сравнения, цифроаналоговый преобразователь, генератор тактовых импульсов, делитель частоты, первый и второй счетчики, блок синхронизации, триггер, первый и второй элементы И-НЕ, элемент ИЛИ-НЕ, выход генератора тактовых импульсов подключен к тактовым

входам делителя частоты и блока синхронизации, выход делителя частоты соединен с тактовым входом первого счетчика, управляющий вход которого и управляющий вход второго счетчика

подключены к выходу триггера, первый и второй выходы коммутатора соединены соответственно с информационным и управляющим входами преобразователя ток - напряжение, выход которого подключен к управляющему входу коммутатора, третий и четвертый выходы которого соединены соответственно с прямым и инверсным входами дифференцирующего усилителя, выход которого

10

15

20

25

подключен к входу первого амплитудного детектора и к первому информационному входу первого измерителя сдвига фаз, второй информационный вход которого и первый информационный вход второго измерителя сдвига фаз являются первым информационным входом устройства, вторым и третьим информационными входами которого являются первый и второй информационные входы коммутатора, четвертый выход которого соединен с вторым информационным входом измерителя сдвига фаз и с входом второго амплитудного детектора, выходы первого счетчика подключены к входам цифроаналогового преоб- разователя, выход которого соединен с Первым информационным входом первого блока сравнения, выход старшего разряда первого счетчика подключен к тактовому входу второго счетчика, Первый и второй выходы синусно-коси- Нусного преобразователя соединены с информационными входами соответственно первого и второго двоичных умножителей, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит сумматор- эычитатель, второй, третий и четвертый мультиплексоры, элемент ЭКВИВАЛЕНТНОСТЬ, первый и второй реверсивные счетчики, первый и второй формирователи импульсов, выходы первого И второго измерителей сдвига фаз под- 35 ключены соответственно к первому и йторому информационным входам четвер- foro мультиплексора, третий информационный вход которого соединен с выходом сумматора-вычитателя,, первый ин- 40 формационный вход которого подключен к выходу первого измерителя сдвига фаз, а второй информационный вход является входом кода константы суммирования устройства, выход четвертого мультиплексора соединен с входом си- нусно-косинусного преобразователя, третий выход которого подключен к первому входу второго блока сравнения, выход которого соединен с входом Установка в 0 первого реверсивного счетчика, тактовый вход которого подключен к выходу первого двоичного умножителя, тактовый вход которого и тактовый Вход второго двоичного умиожите- Ля соединены с выходом второго формирователя импульсов, первый вход которого подключен к выходу первого

15 416631б

блока сравнения, второй информационный вход которого соединен с выходом первого мультиплексора, первый и второй информационные входы которого подключены соответственно к выходам первого и второго амплитудных детек-N торов, третий информационный вход первого мультиплексора соединен с входом нулевого потенциала устройства, первый и второй управляющие входы первого и четвертого мультиплексоров, первый и второй информационные входы первого формирователя импульсов, второй, третий и четвертый информационные входы второго формирователя импульсов, первый и второй входы первого элемента И-НЕ, первый и второй входы элемента ИЛИ-НЕ подключены соответственно к первому и второму выходам второго счетчика, четвертый выход синусно-косинусного преобразователя соединен с первым входом элемента ЭКВИВАЛЕНТНОСТЬ, второй вход которого и второй информационный вход второго блока сравнения подключены к выходу первого формирователя импульсов, третий вход которого соединен с соответствующим выходом первого счетчика, выход старшего разряда которого подключен к управляющему входу сумматора-вычитателя, второй информационный вход которогр соединен с выходом первого измерителя сдвига фаз, выход делителя частоты подключен к пятому информационному ., входу второго формирователя импульсов, шестой информационный вход которого соединен с соответствующим выходом первого счетчика выход второго Двоичного умножителя подключен к тактовому входу второго реверсивного счетчика, вход Установка в О которого соединен с выходом элемента ЭКВИВАЛЕНТНОСТЬ выхоч первого элемента И-НЕ подключен к входу Установка в О триггера, выход которого соединен с входами управления записью первого и второго реверсивных счетчиков, выходы которых подключены к первым информационным входам соответственно второго; и третьего мультиплексоров, вторые информационные входы которых соединены соответственно с первым и вторым выходами блока синхронизации, информационный вход которого подключен к выходу блока оперативной памяти, первый и второй адресные входы которого соединены с выходами соот30

45

50

55

ветственно второго и третьего мультиплексоров, управляющие входы которых и первый вход второго элемента И-НЕ подключены к выходу элемента ИЛИ-НЕ, , управляющий вход блока оперативной памяти соединен с выходом второго элемента И-НЕ, второй вход которого и информационный вход блока оперативной памяти являются управляющим входом устройства, адресными входами которого являются информационные входы первого и второго реверсивных счетчиков, вход Установка в 1 триггера является входом Установка в 1 устройства, выходом которого является выход блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1985 |

|

SU1316027A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| ДИСПЛЕЙ | 1990 |

|

RU2015536C1 |

| Анализатор кодовых последовательностей импульсов (его варианты) | 1984 |

|

SU1238243A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для отображения графической информации на экране цветного телевизионного индикатора | 1990 |

|

SU1836719A3 |

| Устройство для определения амплитуды узкополосного случайного сигнала | 1983 |

|

SU1124328A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

| Устройство для отображения векторов на экране электронно-лучевой трубки | 1988 |

|

SU1635171A1 |

Изобретение относится к средствам обучения и пособиям для учебных целей и предназначено для отображения векторных диаграмм токов и напряжений. Цель изобретения - повышение быстродействия устройства. Устройство содержит коммутатор 1, преобразователь 4 ток-напряжение, дифференцирующий усилитель 5, первый 6 и второй 8 измерители сдвига фаз, первый 7 и второй 9 амплитудные детекторы, сумматор-вычитатель 12, первый 13, второй 23, третий 24 и четвертый 26 мультиплексоры, синусно-косинусный преобразователь 14, первый 27 и второй 15 блоки сравнения, элемент 16 эквивалентности, первый 17 и второй 18 реверсивные счетчики, первый 19 и второй 20 двоичные умножители, блок 25 оперативной памяти, цифро-аналоговый преобразователь 28, генератор 29 тактовых импульсов, делитель 30 частоты, блок 31 синхронизации, первый 32 и второй 33 счетчики, триггер 34, первый 36 и второй 40 элементы И-НЕ, первый 37 и второй 38 формирователи импульсов, элемент ИЛИ-НЕ 41 с соответствующими связями. При подаче на входы 2,3,10 устройства исследуемых сигналов производится формирование полярных координат вектора, точки которого вычисляются блоками 26,14,15-20 и через счетчики 17,18 и мультиплексоры 23,24 записываются в блок 25 памяти. Считывание информации на экран осуществляется по адресам, формируемым блоком 31 синхронизации. 3 ил.

(0.0

(%-/, в)

Тг.Упр.(6ыход блока 34}

Ы

щ

Вход

16

Фиг.З

| Устройство для отображения векторных диаграмм на экране ЭЛТ | 1983 |

|

SU1109786A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-06—Подача