На фиг. 1 представлена структурная JQ матора 9 через элементы И группы 6

подается код с выхода 4.1 старших р рядов регистра 4 сдвига, т.е. содер жимое регистра 4, деленное на 2. Сл довательно, на информационный вход накапливающего сумматора 9 поступае код

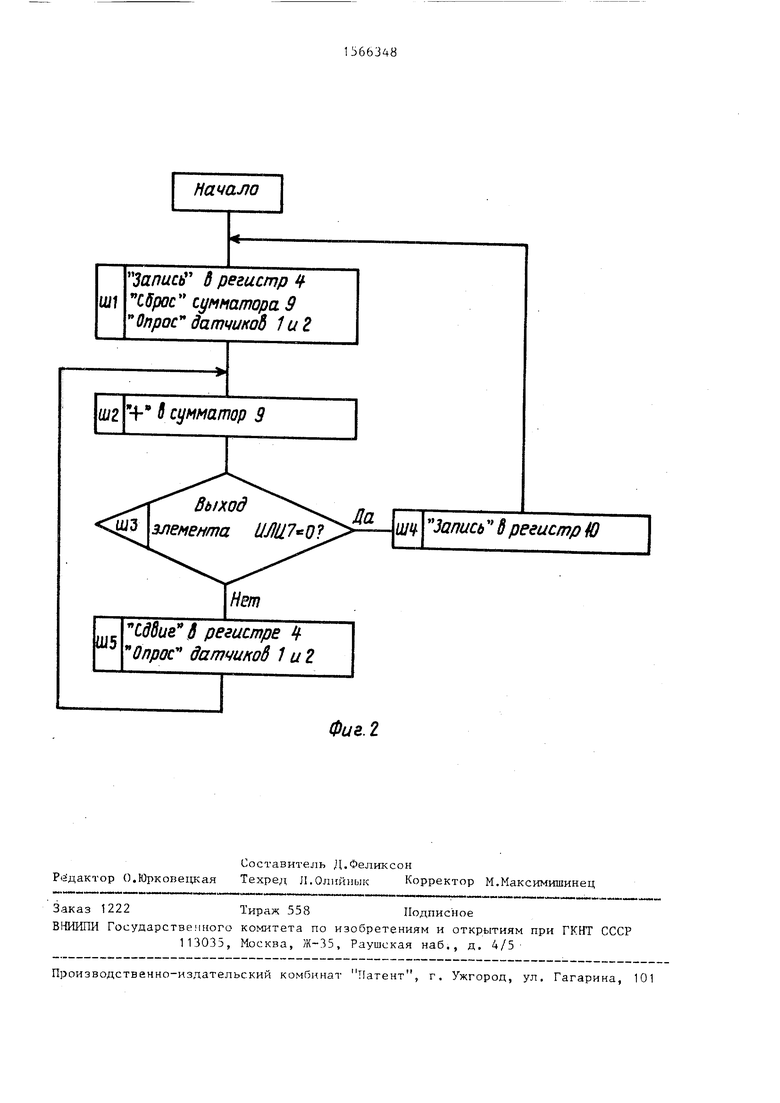

схема предлагаемого генератора; на фиг. 2 - блок-схема алгоритма работы блока синхронизации.

Генератор равномерно распределенных случайных чисел с:. чержит первый и второй датчики 1 и .. равновероятной двоичной цифры, генератор 3 тактовых импульсов, регистр 4 сдвига, выход 4.1 старших разрядов (разряды 1,2,.. п-1) регистр сдвига, выход 4.2 млад- шего разряда (разряд 0) регистра сдвига, блок 5 си-хронизации, группу 6 элементов И, э. емент ИЛИ 7, элемент И 8, накапливающий сумматор 9, регистр 10 памяти и информационный выход 11.

Регистр 4 сдвига предназначен для хранения максимального значения диапазона генерируемых случайных чисел и его последовательного деления на 2 Блок 5 синхронизации предназначен дл реализации алгоритма работы генератора (фиг. 2).

Генератор работает следующим образом.

В исходном состоянии сигналы на выходах блока 5 синхронизации отсутствуют, генератор 3 тактовых импульсов выключен.

Но сигналу Пуск начинает работать генератор 3 тактовых импульсов. С приходом первого тактового импульса начинает работать блок 5 син- .хронизации.

На шаге Ш1 блок 5 синхронизации выдает сигналы: Запись в регистр 4, Сброс сумматора 9, Опрос датчиков 1 и 2. По сигналу Запись в регистр 4 сдвига с входа задания начальных условий записывается максимальное значение диапазона генерируемых случайных чисел. Но сигналу Сброс в накапливающий сумматор 9 записывается значение . Но сигналу Опрос датчики 1 и 2 независимо друг от друга вырабатывают на сво- , их выходах равновероятные двоичные цифры РО и РО соответственно.

матора 9 через элементы И группы 6

Q 5

0

5

0

5

0

подается код с выхода 4.1 старших разрядов регистра 4 сдвига, т.е. содержимое регистра 4, деленное на 2. Следовательно, на информационный вход накапливающего сумматора 9 поступает код

Р;,(), где - знак операции целочисленного

деления.

Одновременно на вход переноса накапливающего сумматора 9 поступает значение с выхода элемента И 8. Если , на вход переноса, очевидно, поступает значение 0.. Если , на. вход переноса черет элемент И 3 с выхода 4.2 подается младший разряд ре- .гистра 4 сдвига, т.е. остаток от деления содержимого регистра 4 на 2. Другими словами, на вход переноса накапливаемого сумматора 9 поступает код

pЈ(y,mod2),

где mod - знак операции вычисления остатка от целочисленного деления.

Таким образом, при выполнении шага Ш2 в накапливающем сумматоре 9 записывается число

s« SO+PO 2)+Ро (), где SB - предыдущее содержимое накапливающего сумматора 9; двоичная цифра на выходе первого датчика 1; код, поступающий с выхода 4.1 старших разрядов регистра 4;

двоичная цифра на выходе второго датчика 2; (yftmod2)- значение младшего разряда

с выхода 4.2 младшего разряда регистра 4.

На шаге ШЗ анализируется значение выхода элемента ИЛИ 7. Если все старшие разряды регистра 4 равны 0, следующим выполняется шаг Ш4. В противном случае следующим выполняется шаг Ш5.

При выполнении шага Ш5 блок 5 синхронизации выдает сигналы Сдвиг

Р.

(У.2)

л«

515

в регистре А и Опрос датчиков 1 и 2. При -этом в регистре А сдвига выполняется сдвиг, и содержимое регистра А становится равным у„ (у.2). На выходах датчиков 1 и 2 появляются случайные двоичные цифры р| и pj соответственно. После шага Ш5 блок 5 синхронизации вновь выполняет гааг 1Л2.

После гчага Ш2 вновь выполняется шаг ШЗ, на котором анализируется выход элемента ИЛИ 7. Если выход элемента HJB1 7 отличен от нуля, т.е. хотя бы один из разрядов выхода А.1 ре

гистра А отличен от нуля,, вновь выполняется шаг Ш5, Ш2 и т.д.

При выполнении шага ША блок 5 синхронизации выдает управляющий сигнал Запись в регистр 10 памяти. При этом в регистре фиксируется случайное число z, которое появляется и на выходе 11 генератора.

К моменту выполнения шага ША в накапливающем сумматоре 9 зафиксировано

случайное число z,, где k - номер 25 датчика равновероятной двоичной циф- первого значащего разряда числа А. Из способа получения числа (деление А пополам, повторное деление полученного числа пополам и т.д., суммированиг

ры, выход младшего разряда регистра сдвига соединен с вторым входом элемента И, группа выходов старших разрядов регистра сдвига соединена с

0

5

генератор тактовых импульсов, группу элементов И, элемент ИЛИ, элемент И, отличающийся тем, что, с целью увеличения быстродействия, в него введены второй датчик равновероятной двоичной цифры, регистр сдвига, накапливающий сумматор, блок синхронизации и регистр, причем вход запуска генератора является входом запуска генератора тактовых импульсов, выход которого соединен с тактовым входом блока синхронизации, первый выход которого соединен с входами опроса первого и второго датчиков равновероятной двоичной цифры, выход первого датчика равновероятной двоичной цифры соединен с первыми входами элементов И группы, выходы которых соединены с группой информационных входов накапливающего сумматора, информационный вход которого соединен с выходом элемента И, первый вход которого соединен с выходом второго

датчика равновероятной двоичной циф-

ры, выход младшего разряда регистра сдвига соединен с вторым входом элемента И, группа выходов старших разрядов регистра сдвига соединена с

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного процесса | 1986 |

|

SU1388858A1 |

| Генератор псевдослучайных чисел | 1977 |

|

SU708381A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1001097A1 |

| Генератор нормально распределенных случайных чисел | 1984 |

|

SU1226450A1 |

| Генератор случайного марковского процесса | 1989 |

|

SU1619262A1 |

| Генератор псевдослучайных чисел | 1980 |

|

SU907548A1 |

| Генератор псевдослучайных чисел | 1979 |

|

SU868734A1 |

| Датчик случайных чисел | 1980 |

|

SU888115A1 |

| Генератор случайных чисел | 1987 |

|

SU1524048A1 |

| Генератор случайного марковского процесса | 1989 |

|

SU1624446A1 |

Изобретение относится к вычислительной технике и может быть использовано для моделирования равномерно распределенных случайных чисел с переменным диапазоном. Целью изобретения является повышение быстродействия генератора равномерно распределенных случайных чисел. Это достигается введением в генератор второго датчика 2 равновероятной двоичной цифры, регистра 4 сдвига, блока 5 синхронизации, накапливающего сумматора 9, регистра 10 памяти. Очередное случайное число получается путем последовательного сдвига верхней границы диапазона и сложения получаемых чисел в зависимости от выходов датчиков равновероятной двоичной цифры. Время выработки очередного случайного числа определяется числом сдвигов в регистре 4 сдвига. Увеличение быстродействия генератора позволяет проводить испытания микропроцессоров на их рабочих частотах. 2 ил.

соответствующих чисел и остатков деле-30 вторыми входами элементов И группы

ния в зависимости от значения случайных двоичных цифр на выходах датчиков 1 и 2) следует, что (Н zЈ А, причем закон распределения случайных чисел z является равномерным.

С выполнением шага ША цикл выработки очередного случайного числа z завершен. После выполнения шага ША начинается новый цикл: вновь выполняется шаг UI1 ,Ш2 и т.д.

Формула изобретения Генератор равномерно распределен-

35

40

и с группой входов элемента ИЛИ, выход которого соединен с входом оста нова блока синхронизации, второй и третий выходы которого соединены с входами записи и сдвига регистра сдвига соответственно, четвертый и пятый выходы блока синхронизации со динены с входами обнуления и разрешения суммирования накапливающего сумматора соответственно, выход накапливающего сумматора соединен с и формационным входом регистра, вход записи которого соединен с шестым выходом блока синхронизации, выход

ных случайных чисел, содержащий дат- ., регистра является информационным вычик равновероятной двоичной цифры,

ходом генератора.

5

0

и с группой входов элемента ИЛИ, выход которого соединен с входом останова блока синхронизации, второй и третий выходы которого соединены с входами записи и сдвига регистра сдвига соответственно, четвертый и пятый выходы блока синхронизации соединены с входами обнуления и разрешения суммирования накапливающего сумматора соответственно, выход накапливающего сумматора соединен с информационным входом регистра, вход записи которого соединен с шестым выходом блока синхронизации, выход

ходом генератора.

Начало

Ш1

ЗаписГ д регистр V Сброс сумма/пора 9 Опрос датчиков 1и2

Ш2

Ч- 6 сумматор 9

Ш5

Сдвиг 6 регистре 4 Опрос датчиков 1 и 2

Фиг. 2

Запись д регистр Ю

| Генератор равномерно распределенных случайных чисел | 1985 |

|

SU1256023A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Генератор случайных чисел | 1981 |

|

SU991422A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-28—Подача