Изобретение относится к аналого- м вычислительной технике и может гь использовано при моделировании , 1сктротехничегких устройств, содержащих тиристоры.

Цель изобретения - расширение функциональных возможностей устройства та счет моделирования режима работы тиристора при критической скорости нарастания напряжения du/dt.

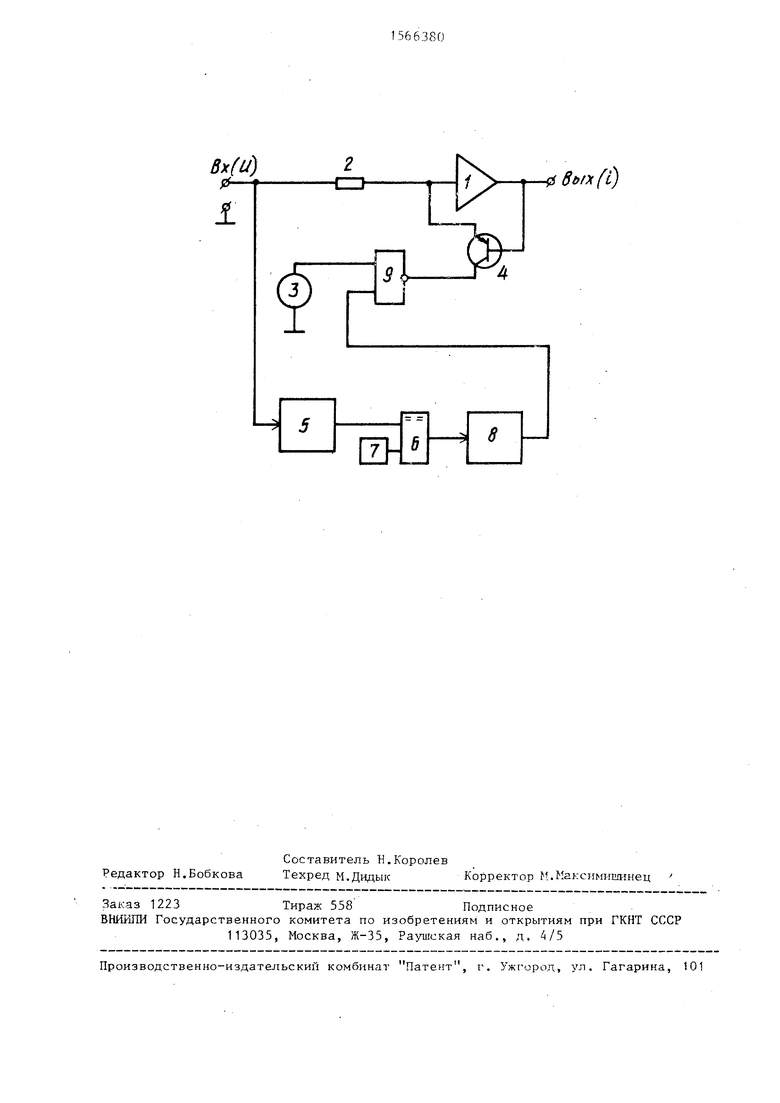

На чертеже изображена функциональная схема устройства для моделирования тиристора.

Устройство содержит операционный усилитель 1, масштабный резистор 2, источник 3 управляющего напряжения, транзистор 4, дифференциальный блок 5, компаратор 6, источник 7 опорного напряжения, формирователь 8 импульсов, элемент ИЛИ 9.

Устройство для моделирования тиристора работает следующим образом.

Входной сигнал, соответствующий моделируемому напряжению анод-катод моделируемого тиристора, поступает через резистор 2 на вход операционного усилителя 1 и вход дифференцирующего блока 5.

Наличие положительного сигнала напряжения на коллекторе транзистора 4 соответствует отсутствию сигнала управления для устройства, а нулевой сигнал на коллекторе транзистора 4 означает подачу сигнала управления на него.

СП

о

ОЭ

оо

00

При подаче на коллектор положительного напряжения транзистор 4 находится в открытом состоянии независимо от полярности входного сигнала и шунтирует операционный усилитель 1. Этим моделируется непроводящее состояние модели тиристора.

При снятии положительного напряжения с коллектора и отрицательном вход ном напряжении транзистор 4 закрывается, на выходе операционного усилителя 1 появляется положительное напряжение, пропорциональное моделируемому току тиристора, которое удерживает транзистор 4 в закрытом состоянии независимо от напряжения на коллекторе. На эмиттере транзистора 4 всегда нулевое напряжение, так как он подсоединен к суммирующей точке операционного усилителя 1. Транзистор 4 откроется только при нулевом напряжении на выходе операционного усилителя 1 и положительном напряжении на его коллекторе. Этим моделируется закрытое состояние модели транзистора. Причем характер напряжения и тока модели тиристора зависит от модели исследуемого устройства.

Дифференцированный входной сигнал с дифференцирующего блока 5 поступает на первый вход компаратора 6, где сравнивается с сигналом источника 7 опорного напряжения, поступающим на второй вход компаратора. Причем опорное напряжение выставляется равным критическому значению du/dt для исследуемого типа тиристора. При равенства этих напряжений компаратор 6 выдает сигнал на формирователь 8 импульсов, который формирует амплитуду и длитель ность импульса, подаваемого на элемен ИЛИ 9. Причем длительность импульсов, Нормируемых блоком 8,не зависит от величины скорости нарастания du/dt входного напряжения и соответствует длительности управляющих импульсов источника 3 управляющего напряжения.

С инвертирующего выхода элемента ИЛИ 9 этот сигнал проходит на коллектор транзистора 4 и выключает его, моделируя процесс включения Тиристора при достижении критической скорости нарастания du/dt. Применение элемента ИЛИ 9 с инверсным выходом позволяет использовать источник управляющего напряжения с нулевым выходным напряжением (неинверсным), где низкий потенциап соответствует отсутствию управляющего сигнала, а высокий - подаче управляющего импульса.

Формула изобретения

Устройство для моделирования тиристора, содержащее источник управляющего напряжения, масштабный резистор, транзистор и операционный усилитель, вход которого соединен с эмиттером транзистора и через масштабный резистор - с катодным выводом устройства, база транзистора подключена к выходу операционного усилителя и к анодному выводу устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет моделирования режима работы тиристора при критической скорости нарастания напряжения, оно содержит компаратор, источник опорного напряжения, формирователь импульсов, элемент ИЛИ и дифференци- 5 рующий блок, вход которого подключен к катодному выводу устройства, а выход - к первому входу компаратора, второй вход которого соединен -с выходом источника опорного напряжения, выход компаратора соединен с входом формирователя импульсов, выход кото- ого соединен t первым входом элемен- :а ИЛИ, второй вход которого соединен с источником управляющего напряжения, инверсный выход элемента ИЛИ соединен с коллектором транзистора.

0

5

)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования @ -фазного вентильного электродвигателя | 1990 |

|

SU1797133A1 |

| Устройство для моделирования симмистора | 1981 |

|

SU963006A1 |

| Устройство для моделирования тиристора | 1976 |

|

SU739563A1 |

| Устройство для моделирования тиристора | 1983 |

|

SU1091190A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛ ВРЕМЕНИ | 1991 |

|

RU2032269C1 |

| ЭЛЕКТРИЧЕСКАЯ ТЯГОВАЯ СИСТЕМА ТРАНСПОРТНОГО СРЕДСТВА С ДВИГАТЕЛЕМ ПОСТОЯННОГО ТОКА | 2008 |

|

RU2351484C1 |

| Источник питания электрофильтра | 1983 |

|

SU1201807A1 |

| Устройство для моделирования электромагнитных процессов в асинхронных машинах | 1989 |

|

SU1681315A1 |

| Устройство для моделирования тиристора | 1983 |

|

SU1161966A1 |

| Устройство для моделирования @ -фазного управляемого выпрямителя | 1980 |

|

SU959105A1 |

Изобретение относится к вычислительной технике и может быть использовано при исследовании вентильных систем, а также схем, содержащих тиристоры. Целью изобретения является расширение функциональных возможностей за счет моделирования режима работы тиристора при критической скорости нарастания напряжения. Устройство содержит источник управляющего напряжения, операционный усилитель, масштабный резистор, транзистор, работающий в инверсном режиме, дифференцирующий блок, компаратор и источник опорного напряжения. На источнике опорного напряжения заранее выставляется пороговое значение, равное критическому уровню скорости нарастания напряжения на тиристоре. 1 ил.

| Стульников В.П., Колче-в К.В | |||

| и др | |||

| Моделирование мостовых вентильных схем, - Известия вузов СССР | |||

| Энергетика, 1974, N 8 | |||

| Устройство для моделирования тиристора | 1976 |

|

SU570072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-03-30—Подача