(54) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ т-ФАЗНОГО УПРАВЛЯЕМОГО ВЫПРЯМИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ТЕПЛОВОЙ ЗАЩИТЫ ЭЛЕКТРОДВИГАТЕЛЯ | 2012 |

|

RU2498472C1 |

| Устройство для моделирования @ -фазного вентильного электродвигателя | 1990 |

|

SU1797133A1 |

| Устройство для управления грузоподъемным электромагнитом | 1990 |

|

SU1817144A1 |

| СТЕНД ДЛЯ ИСПЫТАНИЙ ТОПЛИВНО-РЕГУЛИРУЮЩЕЙ АППАРАТУРЫ ГАЗОТУРБИННЫХ ДВИГАТЕЛЕЙ | 1991 |

|

RU2008642C1 |

| Тиристорный стабилизатор переменного напряжения для активно-индуктивной нагрузки | 1987 |

|

SU1597867A1 |

| Вентильный электропривод | 1990 |

|

SU1697251A1 |

| Устройство для компенсации реактивной мощности нагрузки и симметрирования трехфазной сети | 1985 |

|

SU1261044A1 |

| Статический возбудитель электрических машин | 1991 |

|

SU1786618A1 |

| Устройство для моделирования электрических машин | 1988 |

|

SU1597886A1 |

| УСТРОЙСТВО ДЛЯ ВКЛЮЧЕНИЯ АВИАГОРИЗОНТА В ПИЛОТАЖНЫЙ КОМПЛЕКС | 2002 |

|

RU2213938C1 |

1

Изобретение относится к вычислительной и преобразовательной технике и может быть использовано в аналоговых моделирующих комплексах для исследования электромагнитных процессов в тиристорных выпрямителях, а также при разработке и отладке систем управления выпрямителями.

Известно устройство для моделирования ш-фазного вентильного преобразователя, включающее интегратор, функциональный преобразователь, нелинейный блок и цепь, имитирующую нагрузку. Это устройство не позволяет моделировать процессы коммутации, моделировать выпрямители с замкнутой системой управления, учитывать свойства первичного источника питания 1.

Наиболее близким по техническим характеристикам к предлагаемому является устройство для моделирования управляемого выпрямителя , содержащее управляемый генератор, соединенный через функциональный преобразователь с электронной схемой, моделирующей тиристор, к выходу которой подключен блок вычисления тока нагрузки. Изменением управляющего напряжения регулирует фазу управляющих импульсов. На выходе функционального преобразователя формируется напряжение, имеющее форму выходного напряжения т-фазного выпрямителя, причем начальная фаза соответствующих отрезков .синусоид определяется управляющим сигналом. Указанное устройство отличается простотой и сострит в основном из стандартных аналоговых вычислительных блоков 2.

Недостатками этого устройства являются невозможность моделирования процессов д коммутации несимметричных режимов работы выпрямителя, а также невозможность учета свойств первичного источника питания выпрямителя.

Цель изобретения - расщирёние функциональных возможностей за счет моделирования несимметричных режимов работы и учета свойств первичного источника питания.

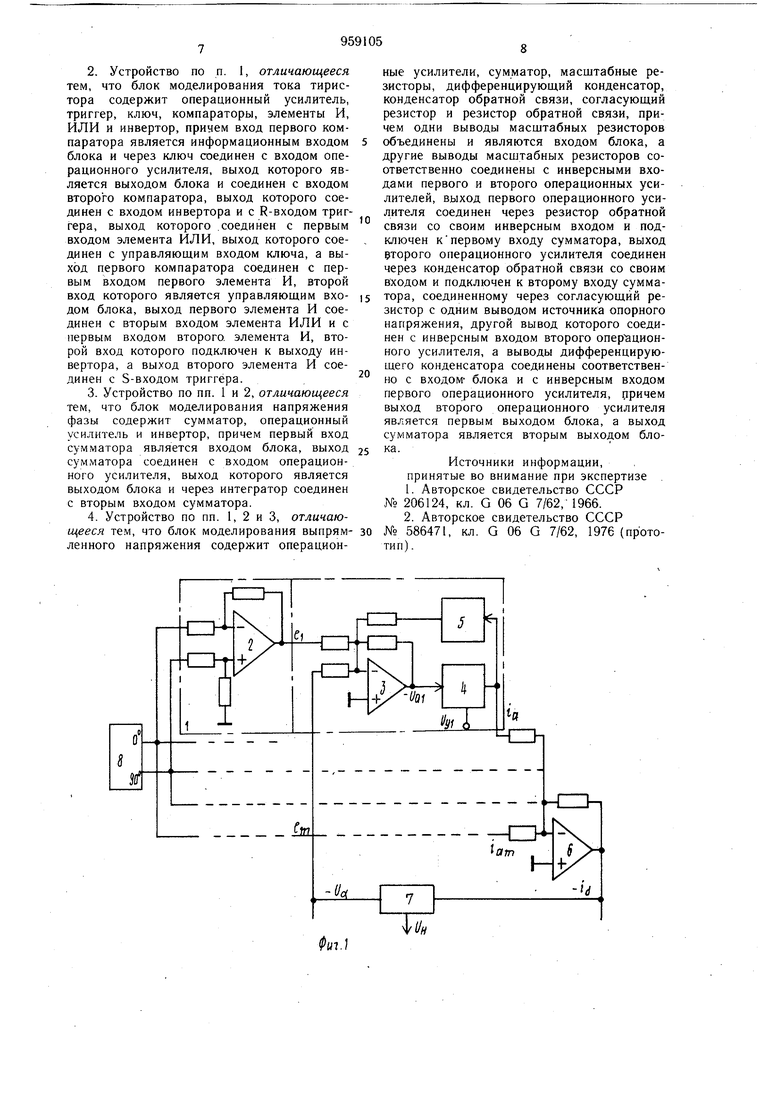

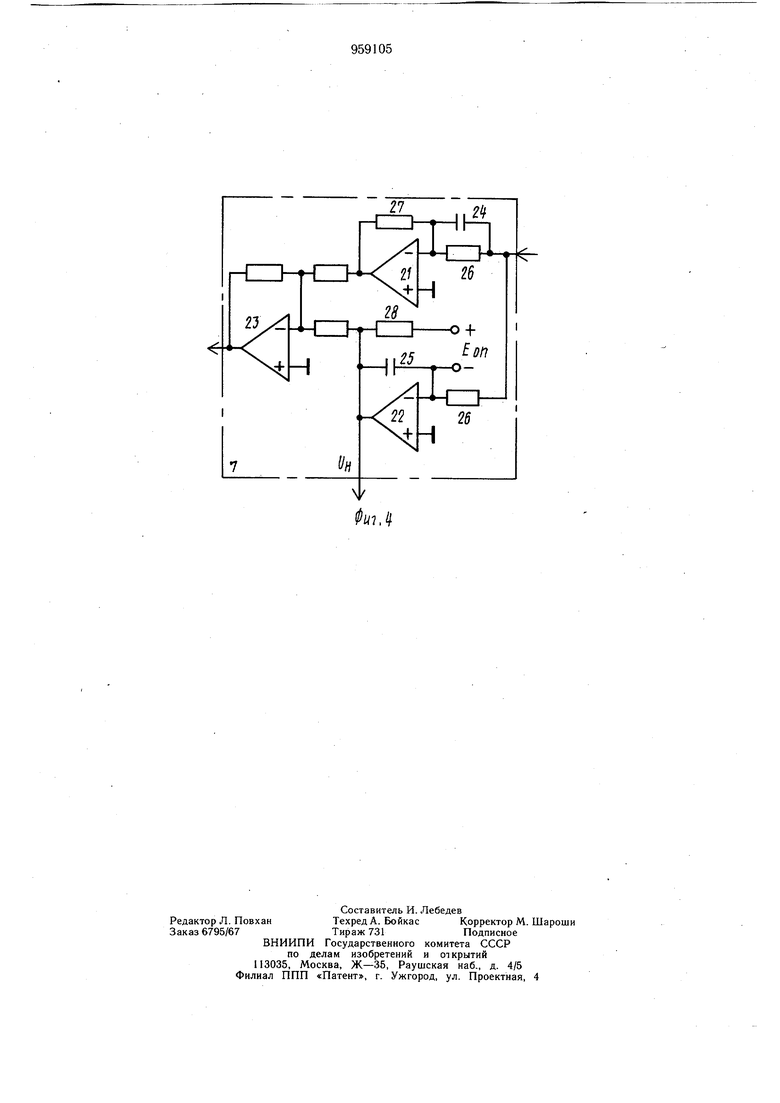

Для достижения цели в устройство для моделирования т-фазного управляемого выпрямителя, содержащее узел моделирования одной фазы управляемого выпрямителя, состоящий из сумматора и блока моделирования тока тиристора, дополнительно введены генератор двухфазного синусоидального напряжения, :умматор токов тиристоров, блок моделирования выпрямленного напряжение и т-1 узлов моделирования одной фазы управляемого выпрямителя, а каждый узел дополнительно содержит операционный усилитель и блок моделирования напряжения фазы, причем выход oneрационного усилителя каждого узла моделирования одной фазы управляемого выпрямителя соединен с первым входом сумматора своего узла, выход которого соединен с информационным входом блока моделирования тока тиристора этого узла, выход которого через блок моделирования напряжения фазы соединен со вторым входом сумматора своего узла, а выходы блоков моделирования тока тиристора всех узлов соединены соответственно со входами сумматора токов тиристоров, выход которого соединен со входом блока моделирования выпрямленного напряжения, первый выход которого является выходом устройства, а второй выход соединен с третьими входами сумматоров всех узлов, причем первый и второй выходы генератора двухфазного синусоидального напряжения соединены соответственно с прямыми и инверсными входами операционных усилителей всех узлов, а управляющие входы блоков моделировакия тока тиристора являются входами устройства, блок моделирования тока тиристора изделий, операционный усилитель, триггер, ключ, компараторы, элементы И, ИЛИ и инвертор, причем вход первого компаратора является информационым входом блока и через ключ соединен с входом операционного усилителя, выход которого является выходом блока и соединен со входом второго компаратора, выход которого соединен со входами инвертора, связанным с R-входом триггера, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с управляющим входом ключа, а выход первого компаратора соединен с первым входом первого элемента И, второй вход которого является управляющим входом блока, выход первого элемента И соединен со вторым входом элемента ИЛИ, связанным с первым входом второго элемента И, второй вход которого подключен к выходу инвертора, а выход второго элемента И соединен с S-входом триггера, блок моделирования напряжения фазы содержит сумматор, операционный усилитель и интегратор, причем первый вход сумматора является входом блока, а выход сумматора соединен со входом операционного усилителя, выход которого является выходом блока и через интегратор соединен со вторым входом сумматора, блок моделирования выпрямленного напряжения содержит операционные усилители, сумматор, масщтабные резисторы, дифференцирующий конденсатор, конденсатор обратной связи, согласующий резистор и резистор обратной связи, причем одни выводы масщтабных резисторов объединяются и являются входом блока, а другие выводы масщтабных резисторов, соответственно соединены с инверсными входами первого и второго операционных усилителей, выход первого операционного усилителя соединен через резистор обратной связи со своим инверсным входом и подключен к первому входу сумматора, выход второго операционного усилителя соединен через конденсатор обратной связи со своим входом и подключен ко второму входу сумматора, соединенному через согласующий резистор с одним выводом источника опорного напряжения, другой вывод которого соединен с инверсным входом второго операционного усилителя, а выводы дифференцирующего конденсатора соединены соответственно со входом блока и с инверсным входом первого отрицательного усилителя, причем выход второго операционного усилителя является первым выходом, блока, а выход сумматора является Езторым выходом блока. На фиг. 1 представлена блок-схема устройства; на фиг. 2 - схема блока моделирования тока тиристора; на фиг. 3 - схема блока моделирования напряжения фазы; на фиг. 4 - схема блока моделирования выпрямленного напряжения. Устройство содержит -узел моделирования одной фазы управляемого выпрямителя 1, содержащий операционный усилитель 2, сумматор 3, блок 4 моделирования тока тиристора и блок 5 моделирования напряжения фазы. Кроме того, устройство содержит сумматор 6 токов тиристоров, блок 7 моделирования выпрямленного напряжения и генератор 8 двухфазного синусоидального напряжения Блок моделирования тока тиристора содержит операционный усилитель 9, ключ 10, первый компаратор 11, элементы И 12 и 13, элемент ИЛИ 14, инвертор 15, второй компаратор 16 и триггер 17. Блок моделирования напряжения фазы содержит сумматор 18, операционный усилитель 19 и интегратор 20. Блок моделирования выпрямленного напряжения содержит операционные усилители 21, 22, сумматор 23, конденсаторы- дифференцирующий 24 и обратной связи 25, масщтабирующие резисторы 26, резистор, обратной связи 27 и согласующий резистор 28. Устройство работает следующим образом. Двухфазное напряжение, поступающее с генератора синоусидальных колебаний 1, с помощью операционных усилителей 2 преобразуется в ряд аналогов фазных ЭДС выпрямителя вида е Em sin (a)t ((ot ); еп, En,sin(u)t + m), где ЕТП- амплитуда; ш- круговая частота ЭДС. Изображение по Лапласу напряжения на к-ом тиристоре Ua(S) равно UaK(S) EJS)-Ud(S)-Zik(S(WS), (2) где E,(S), Ud(S) 1ак(5) - изображение по Лапласу, соответственно фазной ЭДС, выпрямленного напряжения и тока тиристора; Zik(S) - операторное сопротивление фазы первичного источника питания. В соответствии с уравнением (2) на входы сумматора 3 каждой фазы подаются аналоги фазной ЭДС с операционных усилителей 2, падения напряжения на внутреннем сопротивлении первичного источника питания с выхода блока моде; ирования напряжения фазы 5 и выпрямленного напряжения с блока моделирования выпрямленного напряжения 7. Тогда сигнал на выходе сумматора 3 является аналогом падения напряжения на вентиле Uax. Блок 4 вычисляет ток тиристора в соответствии с зависимостью f(U где oC - фаза управляющего импульса. . Величина аналога определяется, в частности, параметрами блока вычисления выпрямленного напряжени 7 и блока вычисления напряжения фазы. Если в реальном выпрямителе существует индуктивность в цепи первичного источника, то процесс перехода тока с предыдущего тиристора на очередной затягивается. В устройстве существуют аналоги токов на выходах нескольких фаз. Параметры индук-, тивности моделируются параметрами параллельной цепи в обратной связи операционного усилителя блока моделирования тока нагрузки. Выпрямительный ток в процессе коммутации складывается из токов отдельных фаз на блоке суммирования токов тиристоров 6. На внекоммутационных интервалах он равен току работающей фазы. По величине его аналога в блоке моделирования выпрямленного напряжения вычисляется аналог мгновенного значения напряжения на выходе схемы выпрямления. Схема блока 7, показанная на чертеже, моделирует Г-образный ЬС-фильтр, к выходу которого подключена активная нагрузка с противо-ЭДС отображаемой ЭДС «. Устройство представляет собой систему с обратной связью по выпрямленному напряжению. Это позволяет обойтись одним комплектом моделей тиристоров и построить устройство для моделирования выпрямителя полностью на стандартных аналоговых вычислительных элементах. Таким образом, выполнение устройства в соответствии с изобретением позволяет испытать системы импульсно-фазового управления, в том числе, подобрать коррекцию системы с целью обеспечения устойчивости и требуемых динамических свойств управляемого выпрямителя,. подобрать оптимальную ширину узких управляющих импульсов, с целью обеспечения устойчивого включения тиристоров в режиме прерывистых токов; исследовать электромагнитные процессы в выпрямителе с заданными параметрами силовой части, в том числе процессы коммутации с использованием конкретной системы управления. При этом довольно просто могут быть учтены такие факторы, как динамические свойства первичного источника питания соизмеримой мощности, несимметрия питающего напряжения, уход частоты питающей сети. Все это позволяет существенно сократить время и затраты на проектирование управляемых выпрямителей, повысить достоверность получаемых результатов. Формула изобретения I. Устройство для моделирования т-фазного управляемого выпрямителя, содержащее узел моделирования одной фазы управляемого выпрямителя, состоящий из сумматора и блока моделирования тока тиристора, отличающееся тем, что, с целью расщирения функциональных возможностей за счет обеспечения возможностей воспроизведения несимметричных режимов работы выпрямителя и учета свойств первичного источника питания, в него дополнительно введены генератор двухфазного синусоидального напряжения и m-1 узлов моделирования одной фазы управляемого выпрямителя, а каждый узел дополнительно содержит операционный усилитель и блок моделирования напряжения фазы, причем выход операционного усилителя каждого узла моделирования одной фазы управляемого выпрямителя соединен с первым входом сумматора своего узла, выход которого соединен с информационным входом блока моделирования тока тиристора этого узла, выход которого через блок моделирования напряжения фазы соединен с вторым входом сумматора своего узла, выходы блоков моделирования тока тиристора всех узлов соединены соответственно с входами сумматора токов тиристоров, выход которого соединен с входом блока моделирования выпрямленного напряжения, первый выход которого является выходом устройства, а второй выход соединен с третьими входами сумматоров всех узлов, причем первый и второй выхо-ды генератора двухфазного синусоидального напряжения соединены соответственно с прямыми и инверснымя входами операционных усилителей всех узлов, а управляющие входы блоков моделирования тока тиристора являются входами устройства. 2.Устройство по п. 1, отличающееся тем, что блок моделирования тока тиристора содержит операциониый усилитель, триггер, ключ, компараторы, элементы И, ИЛИ и инвертор, причем вход первого компаратора является информационным входом блока и через ключ соединен с входом операционного усилителя, выход которого является выходом блока и соединен с входом второго компаратора, выход которого соединен с входом инвертора и с R-входом триггера, выход которого .соединен с первым входом элемента ИЛИ, выход которого соединен с управляющим входом ключа, а выход первого компаратора соединен с первым входом первого элемента И, второй вход которого является управляющим входом блока, выход первого элемента И соединен с вторым входом элемента ИЛИ и с первым входом второго, элемента И, второй вход которого подключен к выходу инвертора, а выход второго элемента И соединен с S-входом триггера. 3.Устройство по пп. 1 и 2, отличающееся тем, что блок моделирования напряжения фазы содержит сумматор, операционный усилитель и инвертор, причем первый вход сумматора является входом блока, выход сумматора соединен с входом операционного усилителя, выход которого является выходом блока и через интегратор соединен с вторым входом сумматора. 4.Устройство по пп. 1, 2 и 3, отличающееся тем, что блок моделирования выпрямленного напряжения содержит операционные усилители, сумматор, масштабные резисторы, дифференцирующий конденсатор, конденсатор обратной связи, согласующий резистор и резистор обратной связи, причем одни выводы масштабных резисторов объединены и являются входом блока, а другие выводы масштабных резисторов соответственно соединены с инверсными входами первого и второго операционных усилителей, выход первого операционного усилителя соединен через резистор обратной связи со своим инверсным входом и подключен кпервому входу сумматора, выход второго операционного усилителя соединен через конденсатор обратной связи со своим входом и подключен к второму входу сумматора, соединенному через согласующий резистор с одним выводом источника опорного напряжения, другой вывод которого соединен с инверсным входом второго операционного усилителя, а выводы дифференцирующего конденсатора соединены соответственно с входом- блока и с инверсным входом первого операционного усилителя, причем выход второго операционного усилителя является первым выходом блока, а выход сумматора является вторым выходом блока. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 206124, кл. G 06 G 7/62, 1966. 2.Авторское свидетельство СССР № 58647, кл. G 06 G 7/62, 1976 (прототип) .

Авторы

Даты

1982-09-15—Публикация

1980-07-07—Подача