Ч

12

ел

а :о

sj

;о i

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронные часы, корректируемые радиосигналами точного времени | 1975 |

|

SU558258A1 |

| РАДИОСТАНЦИЯ | 1995 |

|

RU2141723C1 |

| Оптоэлектронные часы | 1985 |

|

SU1525675A1 |

| Автоматическое пороговое устройство | 1981 |

|

SU1012429A1 |

| ТЕЛЕФОННАЯ РАДИОСТАНЦИЯ С ВОЗМОЖНОСТЬЮ ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2510914C1 |

| СИСТЕМА СИНХРОНИЗАЦИИ ЧАСОВ ПО РАДИОКАНАЛУ | 1985 |

|

SU1840365A1 |

| РАДИОСТАНЦИЯ | 2000 |

|

RU2225673C2 |

| РАДИОСТАНЦИЯ | 2000 |

|

RU2225674C2 |

| РАДИОСТАНЦИЯ ДЛЯ НЕЗАВИСИМОЙ РАБОТЫ 10 ТЕЛЕФОННЫМИ И 10 ТЕЛЕГРАФНЫМИ КАНАЛАМИ | 2013 |

|

RU2523120C1 |

| Оптоэлектронные часы | 1989 |

|

SU1688228A1 |

Изобретение относится к области приборостроения и может использоваться в устройствах времени для автоматической коррекции шкалы времени до значения часа включительно с помощью сигналов проверки времени повышенной информативности и является усовершенствованием устройства, описанного в авт.св. N 700854. Цель - автоматизация сеанса коррекции шкалы времени по сигналам точного времени, которые передаются по сети звукового вещания. На вход схемы И 16 поступает импульс коррекции, равный по длительности шестому сигналу проверки времени повышенной информативности (ПВПИ), на другой вход которой поступают импульсы от генератора 13. На третий вход схемы И 16 подается импульс, разрешающий прохождение на вход формирователя 17 импульсов от генератора 13 с выхода триггера 12, если длительность шестого сигнала ПВПИ больше 100 мс. На вход схемы памяти 18 поступают импульсы с периодом следования 20 мс, число которых соответствует значению передаваемого в данный момент часа. 3 ил.

выходы значении часа б Шична-десятичном коде (8-4-2-1)t t

ю

Фиг.2

Изобретение относится.к приборостроению, может использоваться в устройствах времени для автоматической коррекции шкалы времени до значения часа включительно с помощью сигналов проверки времени повышенной информативности и является усовершенствованием устройства по авт.св. №700854.

Целью изобретения является автоматизация сеанса коррекции шкалы времени по сигналам точного времени, которые передаются по сети звукового вещания.

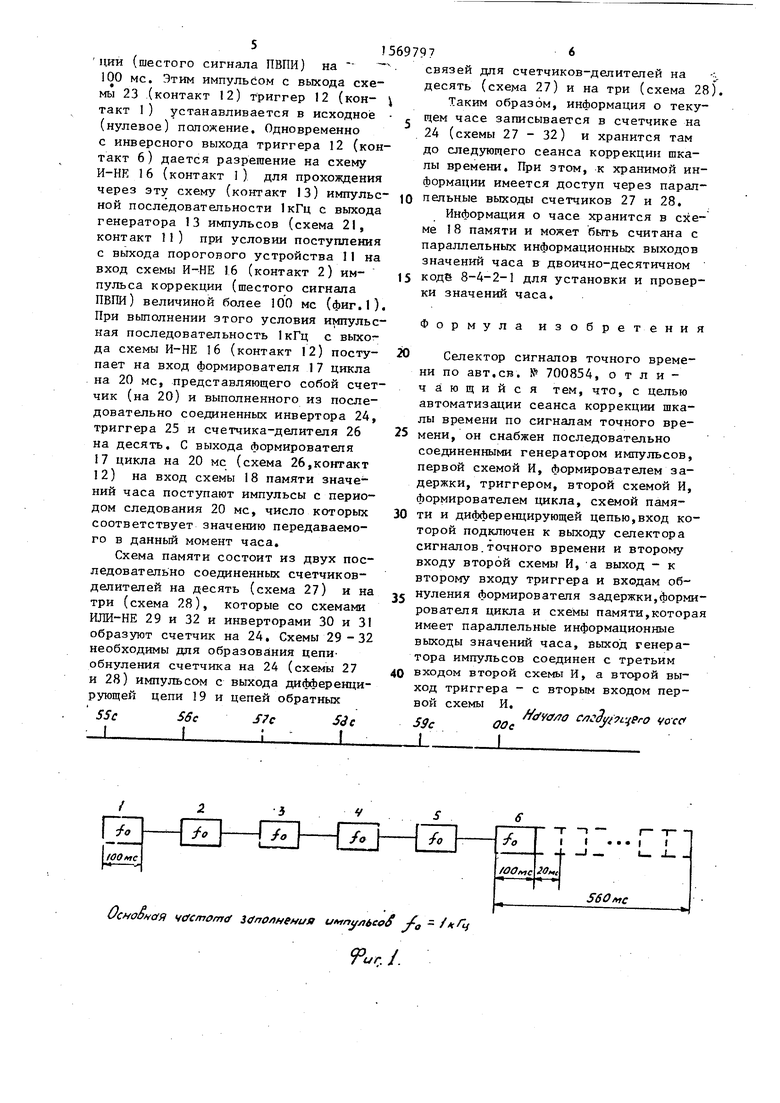

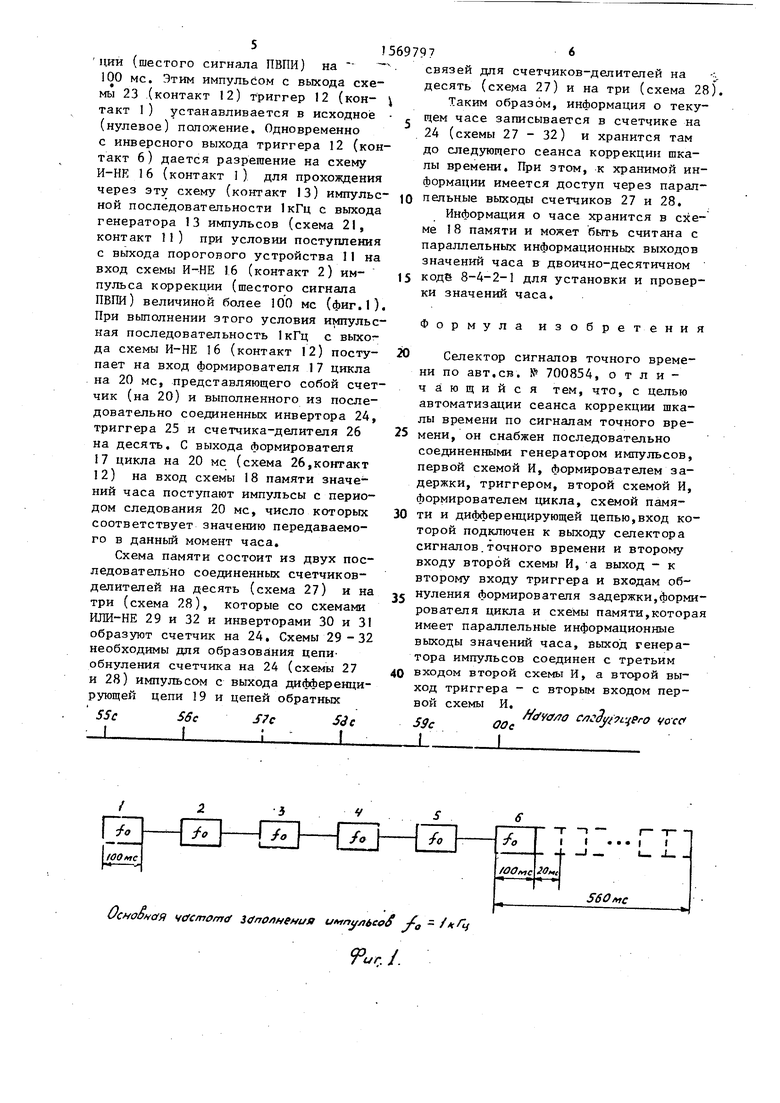

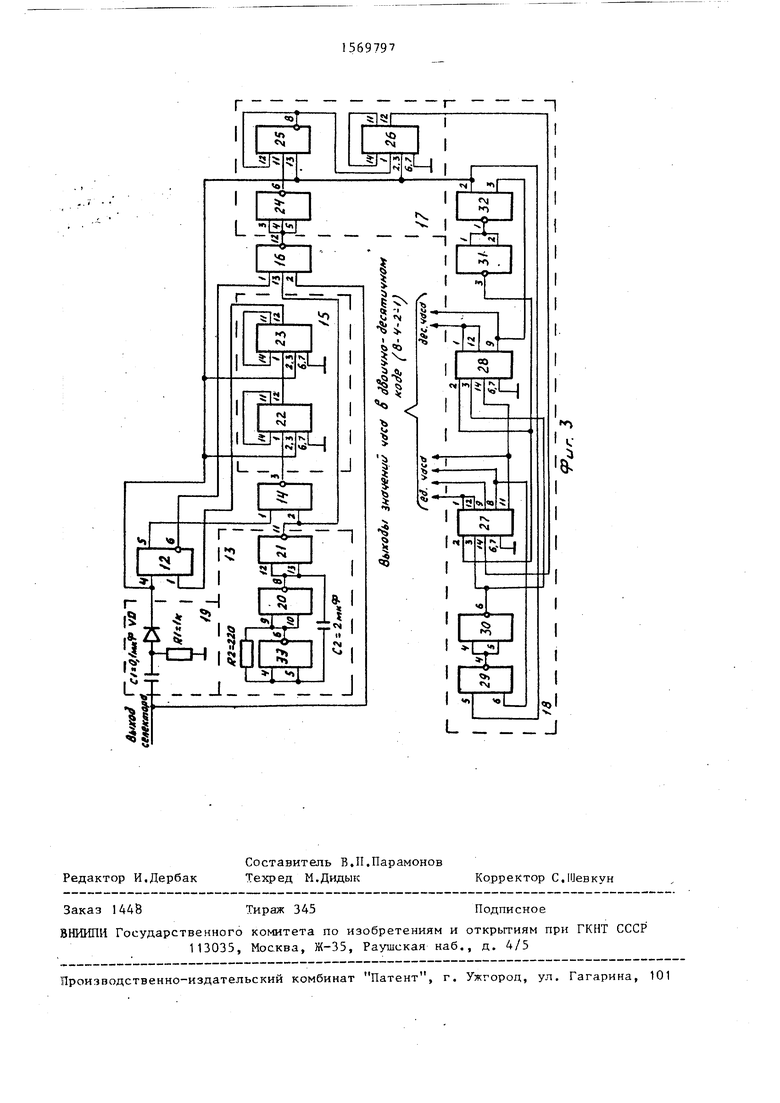

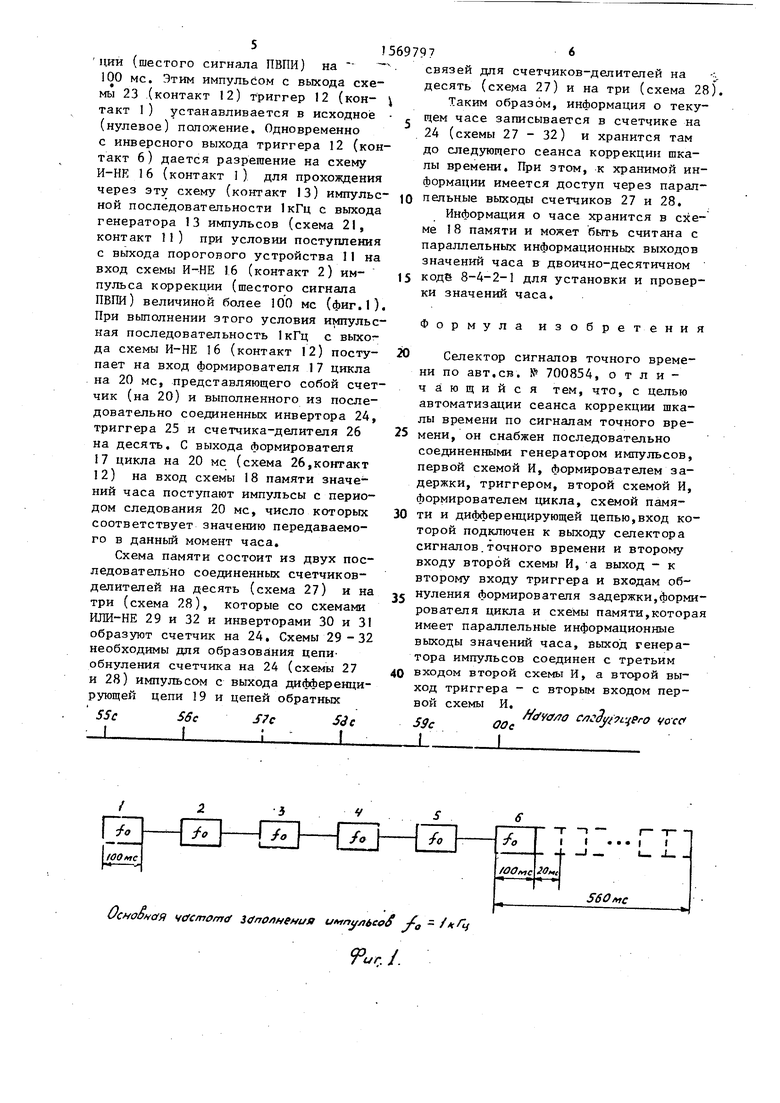

На фиг.1 представлена структура сигналов новой формы; на фиг.2 структурная схема селектора; на фиг. 3 - принципиальная схема блоков введенных дополнительно в селектор сигналов точного времени.

Селектор состоит из усилителя- ограничителя 1, формирователя 2 импульсов, триггера 3 со счетным входом, дифференцирующей цепи 4, тригге ра 5 с раздельными входами, схемы 6 задержки сумматора 7 по модулю два, интегратора 8, дифференцирующей цепи 9, накопителя 10, порогового устройства 11 и дополнительно введенных в схему триггера 12 с раздельными входами, генератора 13 импульсов, двухвходовой схемы И 14, формирователя 15 задержки, трехвходовой схемы И 16, формирователя 17 цикла, блока 18 памяти и дифференцирующей цепи 19

Последовательно соединены усилитель-ограничитель 1, формирователь 2 импульсов, триггер 3, дифференцирующая цепь 4, триггер 5, схема 6 задержки, выход которой соединен с вторым входом триггера 5, первый выход которого соединен с вторым входо сумм атора 7, первый вход которого соединен с выходом триггера 3, а выход - с вторым входом интегратора 8, первый вход которого соединен с выходом формирователя 2.импульсов, а выход соединен с входом дифференцирующей цепи 9, выход которой соединен с входом накопителя 10, выход которого соединен с входом порогового устройства 1 1 .

Выход генератора 13 соединен с входами схем И 14 и 16. Второй вход схемы И 14 соединен с выходом триггера 12. К выходу схемы И 14 подключен формирователь 15 задержки, а к выходу формирователя 15 одним из дву

0

5

0

5

0

5

0

5

входов подключен триггер 12. К выходу селектора сигналов точного времени (порогового устройства 11) подключена схема 16 и дифференцирующая цепь 19, выход которой подключен к второму входу триггера 12, к формирователям 15 задержки и цикла 17,а также к схеме 18 памяти значений часа. Второй выход триггера 12 подключен к третьему входу схемы И 16. Выход схемы И 16 соединен с формирователем 17 цикла, выход которого подключен к схеме,18 памяти значений часа, имеющей параллельные информационные выходы значений часа.

Блоки 12 - 19 работают следующим образом.

Импульс коррекции, равный по длительности шестому сигналу проверки времени повышенной информативности (ПВПИ) (фиг.I), поступает на один из трех входов схемы И-НЕ 16, тем самым подготавливается прохождение через эту схему импульсной последовательности 1кГц. Одновременно по переднему фронту импульса коррекции дифференцирующей цепью 19, состоящей из конденсатора С1, регистра RI и диода VD, выделяется импульс, который поступает на один из установочных входов (контакт 4) триггера 12 и записывает в триггер логическую 1, а также устанавливает в исходное (нулевое) положение формирователи 15 и 17 и схему 18 памяти. С прямого выхода триггера 12 (контакт 5) дается разрешение на прохождение через схему И-НЕ 14 импульсов с частотою следования 1кГц, формируемых генератором 13 импульсов. Одновременно с инверсного выхода триггера 12 (контакт 6) дается запрет на прохождение импульсной последовательности 1кГц через схему И-НЕ 16 (контакт 1), Генератор 13 собран по схеме из трех последовательно соединенных схем И-НЕ 33, 20 и 21, а также резистора R2 и конденсатора С2. Импульсная последовательность 1кГц с выхода схемы 21 поступает через схему И-НЕ 14 на вход формирователя 15 задержки на 100 мс5 выполненного из двух последовательно соединенных счетчиков-делителей 22 и 23 на десять.

Таким образом, на выходе формирователя 15 (схема 23, контакт 12) образуется импульс, начало которого отстоит от начала импульса коррекции (шестого сигнала ПВПИ) на 4 100 мс. Этим импульсом с выхода схемы 23 (контакт 12) триггер 12 (кон- такт I) устанавливается в исходное (нулевое) положение. Одновременно с инверсного выхода триггера 12 (контакт 6) дается разрешение на схему И-НЕ 16 (контакт I) для прохождения через эту схему (контакт 13) импульсной последовательности 1кГц с выхода генератора 13 импульсов (схема 21, контакт 11 ) при условии поступления с выхода порогового устройства 11 на вход схемы И-НЕ 16 (контакт 2) импульса коррекции (шестого сигнала ПВПИ) величиной более 100 мс (фиг.1). При выполнении этого условия импульсная последовательность 1кГц с выхода схемы И-НЕ 16 (контакт 12) поступает на вход формирователя 17 цикла на 20 мс, представляющего собой счетчик (на 20) и выполненного из последовательно соединенных инвертора 24, триггера 25 и счетчик а-делит ел я 26 на десять. С выхода формирователя 17 цикла на 20 мс (схема 26,контакт 12) на вход схемы 18 памяти значений часа поступают импульсы с периодом следования 20 мс, число которых соответствует значению передаваемого в данный момент часа.

Схема памяти состоит из двух последовательно соединенных счетчиков- делителей на десять (схема 27) и на три (схема 28), которые со схемами ИЛИ-НЕ 29 и 32 и инверторами 30 и 31 образуют счетчик на 24, Схемы 29-32 необходимы для образования цепи- обнуления счетчика на 24 (схемы 27 и 28) импульсом с выхода дифференцирующей цепи 19 и цепей обратных

SScSScS7c53 е

I I;I

ч

Осноонс/Я 4CfCm0m J Заполнения импу/гьсоЈ fa -

Я/л /

связей для счетчиков-делителей на ;.

десять (схема 27) и на три (схема 28) Таким образом, информация о текущем часе записывается в счетчике на 24 (схемы 27-32) и хранится там до следующего сеанса коррекции шкалы времени. При этом, к хранимой информации имеется доступ через парал- JO пельные выходы счетчиков 27 и 28.

Информация о часе хранится в схеме 18 памяти и может быть считана с параллельных информационных выходов значений часа в двоично-десятичном 15 коде 8-4-2-1 для установки и проверки значений часа.

ормула изобретения

Селектор сигналов точного времени по авт.св. № 700854, отличающийся тем, что, с целью автоматизации сеанса коррекции шкалы времени по сигналам точного времени, он снабжен последовательно соединенными генератором импульсов, первой схемой И, формирователем задержки, триггером, второй схемой И, формирователем цикла, схемой памя- ти и дифференцирующей цепью,вход которой подключен к выходу селектора сигналов.точного времени и второму входу второй схемы И, а выход - к второму входу триггера и входам обнуления формирователя задержки,формирователя цикла и схемы памяти,которая имеет параллельные информационные выходы значений часа, выход генератора импульсов соединен с третьим входом второй схемы И, а второй выход триггера - с вторым входом первой схемы И,

fiafYff/to слмумщего vo ccf 59сООсJ

II

II -35

S

I

| Селектор сигналов точного времени | 1976 |

|

SU700854A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-07—Публикация

1988-08-23—Подача