(54) СЕЛЕКТОР СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Селектор сигналов точного времени | 1988 |

|

SU1569797A2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ | 1990 |

|

RU2006946C1 |

| Приемник цифрового линейного сигнала | 1986 |

|

SU1462509A1 |

| Система для передачи цифровой информации по проводным каналам связи | 1985 |

|

SU1256233A1 |

| Адаптивное устройство для обработки избыточной информации | 1982 |

|

SU1062752A1 |

| Устройство синхронизации приемника многочастотных сигналов | 1984 |

|

SU1185627A1 |

| ИЗМЕРИТЕЛЬ ФАЗ ОСЦИЛЛОГРАФИЧЕСКИЙ | 2005 |

|

RU2314543C2 |

| Устройство для передачи и приема цифровых сигналов | 1986 |

|

SU1415452A1 |

| СТАНЦИЯ ПОМЕХ | 2010 |

|

RU2434241C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

1

Изобретение относится к приборостроению и может использоватвся в устройствах для коррекции часов и контроля прохождения радиосигнала тошого времени.

Известны селекторы сигналов точного време1ш, содержащие камертонный фильтр, детектор, интегрирующую цепочку, усилитель-формирователь, емкостный накопитель и пороговый элемент, причем параллельно камертонному фильтру включен усилитель-детектор с интегрирующей цепочкой на выходе, служащий компенсационным каналом 1 .

Эти устройства не обладают необходимой надежностью, так как не имеют достаточной защиты от ложных срабатываний, а дальнейщее сужение полосы пропускания фильтра не позволяет увеличить отношение сигнал/помеха.

Наиболее близким к предлагаемому является селектор сигналов точного времени, содержащий узкополосный пропускающий фильтр и детектор 2.

Критишость параметров селектора к изменению амплитуды входного сигнала приводит к большой вероятности непрохождения полезноГО сигнала в одном случае, прохождения ложного сигнала коррекции в другом случае и, таким образом, снижает надежность работы селектора.

Цель изобретения - повышение надежности приема сигналов точного времени.

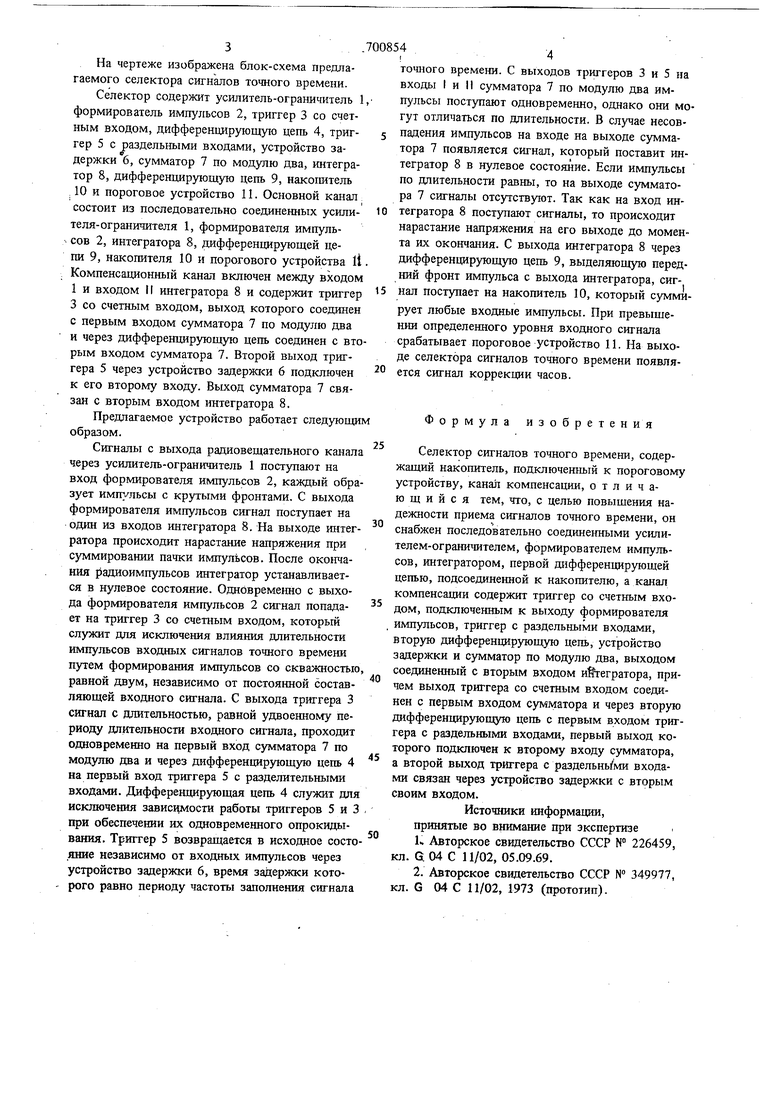

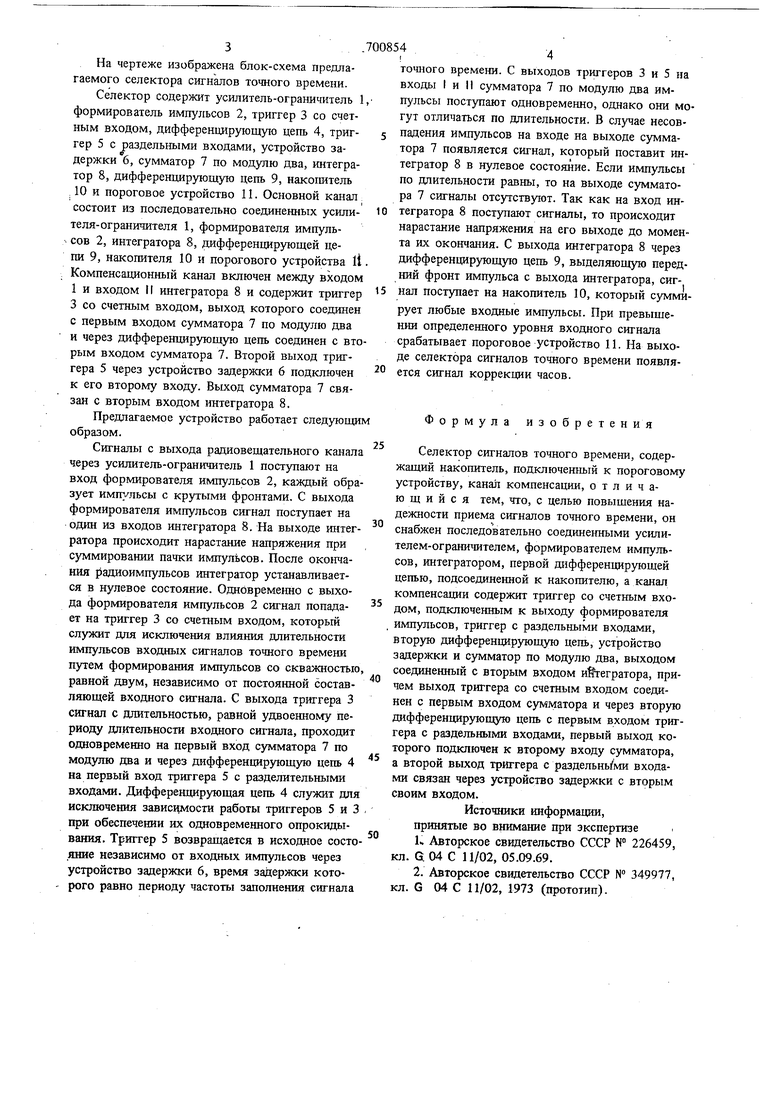

Это достигается тем, что предлагаемый селектор снабжен последовательно соедине1шыми усилителем-ограничителем, формирователем импульсов, интегратором, первой дифференцирующей цепью, подсоединенной к накопителю, а канал компенсации содержит триггер со счетным входом, подключенным к выходу фор шрователя импульсов, триггер с раздельными входами, вторую дифференцирующую цепь, устройство задержки и сумматор по модулю два, выходом соединенный с вторым входом интегратора, причем выход триггера со счетным входом соединен с первым входом сумматора и через вторую дифференцирующ)то цепь с первым входом триггера с раздельными входами, первый выход которого подключен к второму входу сумматора, а второй выход триггера с раздельными входами связан через устройство задержки с вторым своим входом. 3.7 На чертеже изображена блок-схема предлагаемого селектора сигналов точного времени. Селектор содержит усилитель-огра1шчитель формирователь импульсов 2, триггер 3 со счетным входом, дифференцирующую цепь 4, триггер 5 с раздельными входами, устройство задержки 6, сумматор 7 по модулю два, интегратор 8, дифференцирующую цепь 9, накопитель .10 и пороговое устройство 11. Основной канал состоит из последовательно соединенных усилителя-ограничителя 1, формирователя импульсов 2, интегратора 8, дифференцирующей цепи 9, накопителя 10 и порогового устройства it Компенсационный канал включен между входом 1 и входом II интегратора 8 и содержит триггер 3 со счетным входом, выход которого соединен с первым входом сумматора 7 по модулю два и через дифференцирзтощую цепь соединен с вто рым входом сумматора 7. Второй выход триггера 5 через устройство задерЖ1си 6 подключен к его второму входу. Выход сумматора 7 связан с вторым входом интегратора 8. Предлагаемое устройство работает следующи образом. Сигналы с выхода радиовещательного канала через усилитель-ограничитель 1 поступают на вход формирователя импульсов 2, каждый обра зует импульсы с крутыми фронтами. С выхода формирователя импульсов сигнал поступает на один из входов интегратора 8. На выходе интегратора происходит нарастание напряжения при с ммировании пачки импульсов. После окончания радиоимпульсов интегратор устанавливается в нулевое состояние. Одновременно с выхода формирователя импульсов 2 сигнал попадает на триггер 3 со счетным входом, который служит для исключения влияния длительности импульсов входных сигналов точного времени путем формирования импульсов со скважностью равной двум, независимо от постоянной составляющей входного сигнала. С выхода триггера 3 сигнал с длительностью, равной удвоенному периоду длительности входного сигнала, проходит одновременно на первый вход сумматора 7 по модзшю два и через дифференцирующую цепь 4 на первый вход триггера 5 с разделительными входами. Дифференцирующая цепь 4 служит для исключения зависн мости работы триггеров 5 и 3 при обеспечении их одновременного опрокидывания. Триггер 5 возвращается в исходное состо яние независимо от входных импульсов через устройство задержки 6, время задержки кото- рого равно периоду частоты заполнения сигнала 4 ТОЧНОГО времени. С выходов триггеров 3 и 5 на входы I и II сумматора 7 по модулю два импульсы поступают одновременно, однако они могут отличаться по длительности. В случае несовпадения импульсов на входе на выходе сумматора 7 появляется сигнал, который поставит интегратор 8 в нулевое состояние. Если импульсы по длительности равны, то на выходе сумматора 7 сигналы отсутствуют. Так как на вход интегратора 8 поступают сигналы, то происходит нарастание напряжения на его выходе до момента их окончания. С выхода интегратора 8 через дифференцирующую цепь 9, выделяющую передний фронт импульса с выхода интегратора, сигнал поступает на накопитель 10, который суммирует любые входные импульсы. При превышении определенного уровня входного сигнала срабатывает пороговое устройство 11. На выходе селектора сигналов точного времени появляется сигнал коррекции часов. Формула изобретения Селектор сигналов точного времени, содержащий накопитель, подключешштй к пороговому устройству, канал компенсации, отличающийся тем, что, с целью повышения надежности приема сигналов точного времени, он снабжен последовательно соединеьшыми усилителем-ограничителем, формирователем импульсов, интегратором, первой дифференцирующей цепью, подсоединенной к накопителю, а канал компенсации содержит триггер со счетным входом, подключенным к выходу формирователя импульсов, триггер с раздельными входами, вторую дифференцирующую цепь, устройство задержки и сумматор по модулю два, выходом соединенный с вторым входом и -егратора, причем выход триггера со счетным входом соединен с первым входом сумматора и через вторую дифференцирующую цепь с первым входом триггера с раздельными входами, первый выход которого подключен к второму входу сумматора, а второй выход триггера с раздельнь/ми входами связан через устройство задержки с вторым своим входом. Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР № 226459, кл. G04 С 11/02,05.09.69. 2. Авторское свидетельство СССР № 349977, кл. G 04 С 11/02, 1973 (прототип).

Авторы

Даты

1979-11-30—Публикация

1976-06-07—Подача