Изобретение относит-ся к вычислительной технике и может быть использовано при создании вычислительных систем для подключения внешних устройств к ЭВМ.

Цель изобретения - повышение быстродействия.

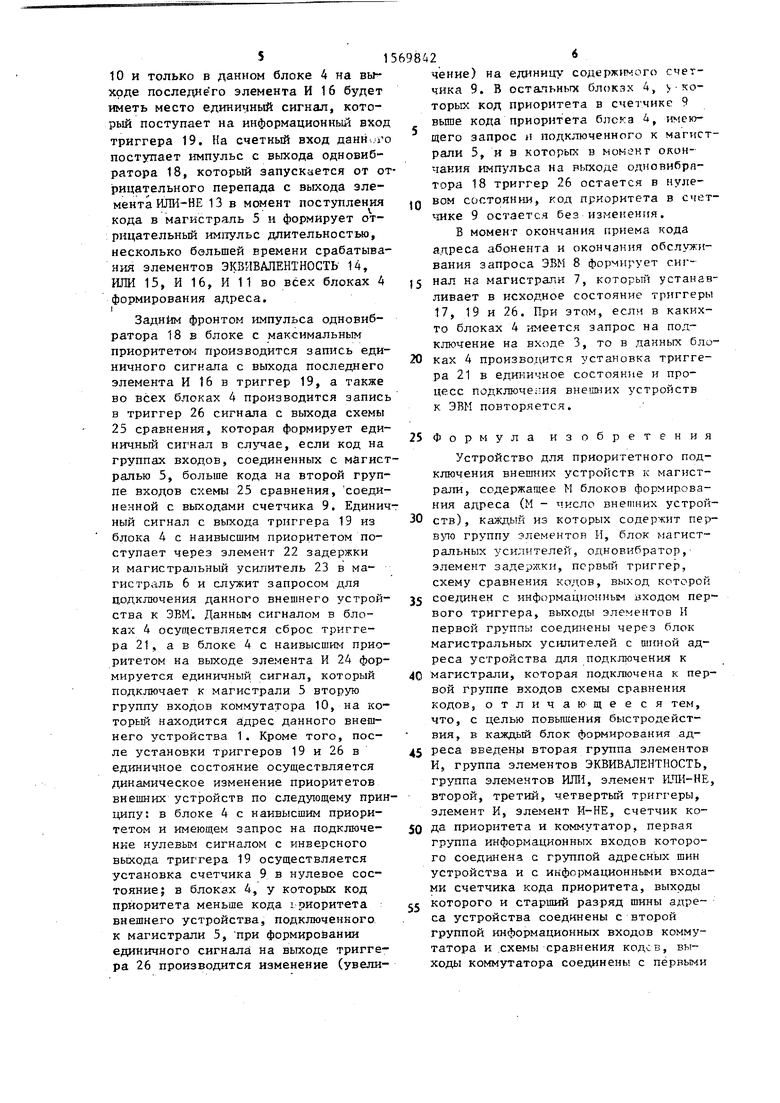

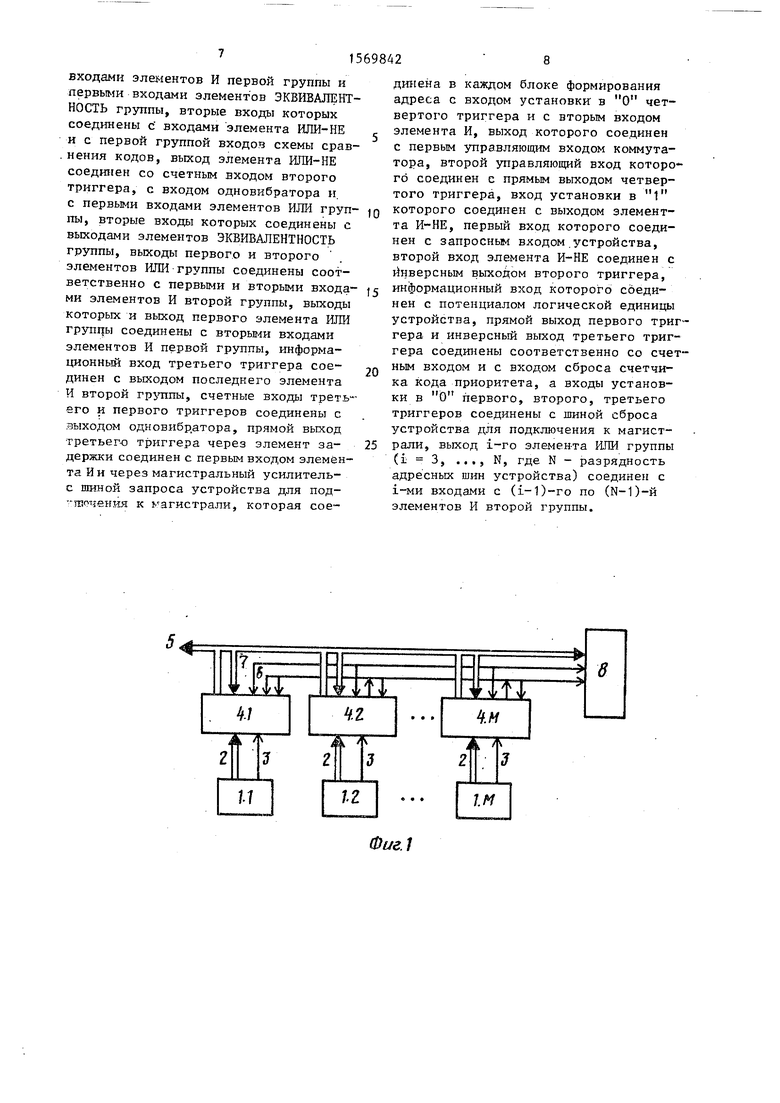

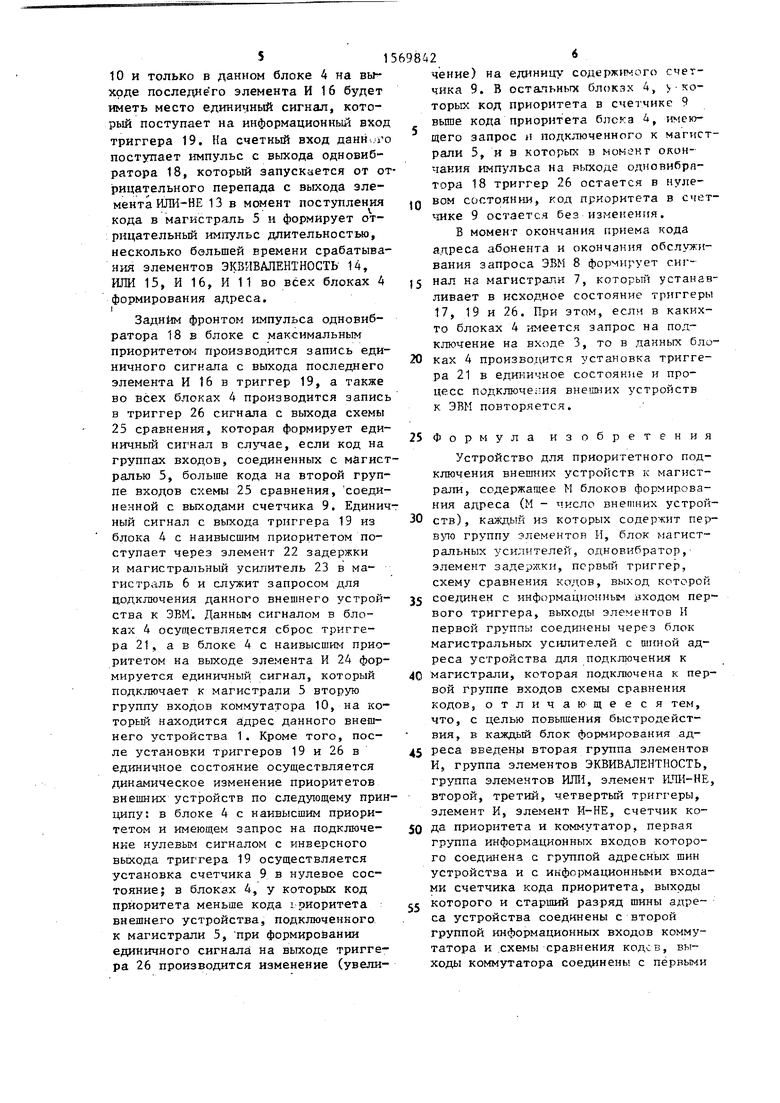

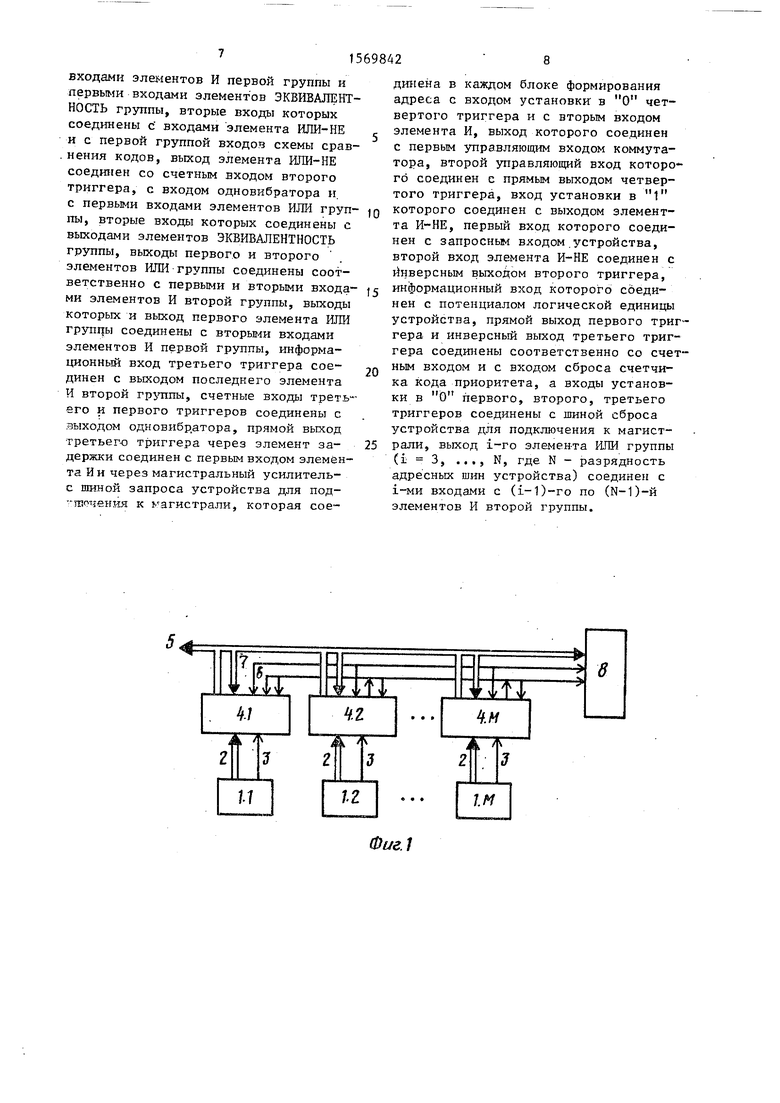

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока формирования адреса.

Устройство содержит 11 внешних устт ройств 1, адресный выход 2 внешнего устройства, запросный выход 3 внешнего устройства, М блоков 4 формирования адреса, магистраль 5 адреса,

магистраль 6 запроса, магистраль 7 сброса, ЭВМ 8.

Каждый блок 4 формирования адреса содержит счетчик 9 приоритета, коммутатор 10, выполненный в виде мно- говходового элемента И-1ШИ, груш;у элементов И 11, блок 12 магнстралъ- пых усилителей, элемент ИЛИ-НЕ 13, группу элементов ЭКВИВАЛЕНТНОСТЬ К, группу элементов ИЛИ 15, группу ментов И 16, триггер 17, однивибра- тор 18, триггер 19, элемент И-НЕ Г.О, триггер 21, элемент 22 задержки, магистральный усилитель 23, элемент И 24, схему 25 сравнения кодоп, -nun гер 26.

СП

Си

со

00 Ј

ю

v

В начальный момент производится установка в исходное нулевое состояние триггеров 17, 19, 21 и 26, в счет Чнк 9i (i - 1 - М) блока 4 записыва - ется код адреса i внешнего устройства 1, при этом в каждом блоке 4 на выходе коммутатора 10, выхода элементов И 11 ив магистрали 5 формируется нулевой код, а на выходе эле- мента ИЛИ-НЕ 13, выходах элементов ИЛИ 15, И 16 - единичный потенциал (цепи начальной установки не показаны). В момент поступления запроса на подключение к ЭВМ по пходу 3 при ус- ловин свободной магистрали 5 или.6 (триггер 17 находится в нулевом состоянии) единичный сигнал поступает на вход установки в 1 триггера 21 и устанавливает данный триггер в едн- ничное состояние.

Предположим, что запросы поступают по входам 3 одновременно сразу от пескольких внешних устройств, при сразу в нескольких блоках 4 осу- щесчвллется установка в единичное стояние триггера 21. Единичный сигнал с выхода триггера 21 поступает т червый управляющий вход коммута- ,. ,л 10 и подключает к выходам коммутатора выходы счетчики 9 приоритета. Коп приоритета блока 4, имеющего запрос на подключение через группу элементов И 11, магистральные усилители 12, поступает в магистраль 5, где устанавливается результирующий потенциал монтажного ИЛИ. В старом разряде кода всегда в магистраль 5 поступает единичный сигнал, поэтому независимо от кода приоритета в момент поступления кода в магистраль 5 хотя бы от одного внешнего устройства на выходе элемента 1ШИ-НЕ 13 формируется нулевой сигнал, который поступает на входы элементов ИЛИ 15, на счетный вход триггера 17 и устанавливает данный триггер в единичное состояние, поэтому если в каком-то блоке 4 сформируется новый запрос на входе 3, то триггер 21 в единичное состояние не установится до окончани обработки предыдущего запроса (сброса триггера 17).

В каждом блока 4 осуществляется поразрядное сравнение кода в магистрали 5 и выходного кода коммутатора 10.

Если блок 4 не имеет запроса на входе З, то на выходе коммутатора 10

Q

5

0

5

0

5

0

во всех разрядах будет иметь место нулевой код, поэтому на выходе элемента ЭКВИВАЛЕНТНОСТЬ 14, сравнивающего старшие разряды кодов, сформируется нулевой потенциал, который поступает через элемент ИЛИ 15 на входы всех элементов И 16 и приводит к формированию нулевого сигнала на выходах всех элементов И 16.

В тех блоках 4, в которых триггеры 21 устанавливаются в единичное состояние в старших разрядах кодов осуществляется совпадение единичных сигналов, поэтому в данных блоках 4 элементами ЭКВИВАЛЕНТНОСТЬ 14 производится поразрядное сравнение кодов приоритета, начинал со старших разрядов. Если потенциалы кодов в старшем разряде в магистрали 5 и на выходе коммутатора 10 совпадают, то на выходе элементов ЭКВИВАЛЕНТНОСТЬ 14, ИЛИ 15 в данном разряде формируется единичный сигнал, который поступает на вход элемента И 11 в данном разряде, разрешает дальнейшую выдачу кода в магистраль 5 через элемент И 11 в данном разряде. Кроме того, с выхода элемента ИЛИ 15 данного разряда единичный сигнал поступает на входы всех элементов И 16 и разрешает выдачу в магистраль 5 кодов приоритета в младших разрядах.

Таким образом, осуществляется поразрядное последовательное сравнение потенциалов кода в магистрали 5 и кода на выходе коммутатора 10.

Если в каком-то разряде происходит несовпадение потенциалов, то это означает, что в магистраль 5 в данном разряде имеет место более высокий код.

В этом случае на выходе элементов ЭКВИВАЛЕНТНОСТЬ 14, ИЛИ 15 в данном разряде сформируется нулевой потенциал, который поступает на входы элементов И 16 в данном разряде и в остальных младших разрядах, поэтому на вторые входы элементов И 11 в данном и остальных младших разрядах поступают нулевые сигналы и блокируют прохождение кода с выхода коммутатора 10 в данном и остальных младших разрядах.

Так как коды приоритета всех блоков 4 разные, то при поступлении запроса только в одном блоке 4 произойдет совпадение кода в магистрали 5 и коде приоритета с выхода коммутатора

51

10 и только в данном блоке 4 на выходе последнего элемента И 16 будет иметь место единичный сигнал, который поступает на информационный вход триггера 19. На счетный вход данн го поступает импульс с выхода одновиб- ратора 18, который запускается от отрицательного перепада с выхода элемента ИЛИ-НЕ 13 в момент поступления кода в магистраль 5 н формирует отрицательный импульс длительностью, несколько большей времени срабатывания элементов ЭКВИВАЛЕНТНОСТЬ 14, ИЛИ 15, И 16, И 11 во всех блоках 4

формирования адреса.

i

Задним фронтом импульса одновиб- ратора 18 в блоке с максимальным приоритетом производится запись единичного сигнала с выхода последнего элемента И 16 в триггер 19, а также во всех блоках 4 производится запись в триггер 26 сигнала с выхода схемы 25 сравнения, которая формирует единичный сигнал в случае, если код на группах входов, соединенных с магистралью 5, больше кода на второй группе входов схемы 25 сравнения, соединенной с выходами счетчика 9. Единичный сигнал с выхода триггера 19 из блока 4 с наивысшим приоритетом поступает через элемент 22 задержки и магистральный усилитель 23 в магистр, 1ль 6 и служит запросом для подключения данного внешнего устрой- ства к ЭВМ. Данным сигналом в блоках 4 осуществляется сброс триггера 21, а в блоке 4 с наивысшим приоритетом на выходе элемента И 24 формируется единичный сигнал, который подключает к магистрали 5 вторую группу входов коммутатора 10, на который находится адрес данного внешнего устройства 1. Кроме того, после установки триггеров 19 и 26 в единичное состояние осуществляется динамическое изменение приоритетов внешних устройств по следующему принципу: в блоке 4 с наивысшим приоритетом и имеющем запрос на подключе- нке нулевым сигналом с инверсного выхода триггера 19 осуществляется установка счетчика 9 в нулевое состояние; в блоках 4, у которых код приоритета меньше кода ; риоритета внешнего устройства, подключенного к магистрали 5, при формировании единичного сигнала на выходе триггера 26 производится изменение (увели0

5

8

g

0

42

чение) на единицу содерж ого счетчика 9. В остальньгх блок.чх 4, ч которых код приоритета в счетчике 9 выше кода приоритета блока 4, имеющего запрос н подключенного к магистрали 5, и в которых и момент окончания импульса на выходе одновибрл- тора 18 триггер 26 остается в нулевом состоянии, код приоритета в счгт- чике 9 остается без изменения.

В момент окончания приема кода адреса абонента и окончания обслуживания запроса ЭВМ 8 формирует сигнал на магистрали 7, который устанавливает в исходное состояние триггеры 17, 19 и 26. При этом, если в каких- то блоках 4 имеется запрос на подключение на входе 3, то в данных блоках 4 производится установка триггера 21 в единичное состояние н процесс подключения внешних устройств к ЭВМ повторяется.

Формула изобретения

Устройство для приоритетного подключения внешних устройств к магистрали, содержащее М блоков формирования адреса (М - исло внешних устройств), каждый из которых содержит первую группу - лементоп И, блок магистральных усилителей, одновибратор, элемент задержки, первый триггер, схему сравнения кодов, выход которой соединен с информационным входом первого триггера, выходы элементов И первой группы соединены через блок- магистральных усилителей с шиной адреса устройства для подключения к магистрали, которая подключена к первой группе входов схемы сравнения кодов, отличающее ся тем, что, с целью повышения быстродействия, в каждый блок формирования адреса введены вторая группа элементов И, группа элементов ЭКВИВАЛЕНТНОСТЬ, группа элементов ИЛИ, элемент ИЛИ-НЕ, второй, третий, четвертый триггеры, элемент И, элемент И-НЕ, счетчик кода приоритета и коммутатор, первая группа информационных входов которого соединена с группой адресных шин устройства и с информационными входами счетчика кода приоритета, выходы которого и старший разряд шины адреса устройства соединены с второй группой информационных входов коммутатора и схемы сравнения код., т;, выходы коммутатора соединены с первыми

входами элементов И первой группы и первыми входами элементов ЭКВИВАЛЕНТНОСТЬ группы, вторые входы которых соединены с входами элемента ИЛИ-НЕ и с первой группой входов схемы сравнения кодов, выход элемента ИЛИ-НЕ соединен со счетным входом второго триггера, с входом одновибратора и с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами элементов ЭКВИВАЛЕНТНОСТЬ группы, выходы первого и второго элементов ИЛИ группы соединены соответственно с первыми и вторыми входами элементов И второй группы, выходы которых и выход первого элемента ИЛИ группы соединены с вторыми входами элементов И первой группы, информационный вход третьего триггера соединен с выходом последнего элемента И второй группы, счетные входы третьего и первого триггеров соединены с пыходом одновибратора, прямой выход третьего триггера через элемент задержки соединен с первым входом элемента И и через магистральный усилитель- с шиной запроса устройства для под- ггх чения к магистрали, которая сое

5

0

5

динена в каждом блоке формирования адреса с входом установки в О четвертого триггера и с вторым входом элемента И, выход которого соединен с первым управляющим входом коммутатора, второй управляющий вход которого соединен с прямым выходом четвертого триггера, вход установки в 1 которого соединен с выходом элемент- та И-НЕ, первый вход которого соединен с запросным входом устройства, второй вход элемента И-НЕ соединен с инверсным выходом второго триггера, информационный вход которого соединен с потенциалом логической единицы устройства, прямой выход первого триггера и инверсный выход третьего триггера соединены соответственно со счетным входом и с входом сброса счетчика кода приоритета, а входы установки в О первого, второго, третьего триггеров соединены с шиной сброса устройства для подключения к магистрали, выход 1-го элемента ИЛИ группы

(1 3N, где N - разрядность

адресных шин устройства) соединен с i-ми входами с (i-l)-ro по (М-1)-й элементов И второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1434448A1 |

| Устройство для сопряжения вычислительной машины с магистралью обмена | 1986 |

|

SU1381519A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072046A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1983 |

|

SU1109754A1 |

| Устройство для сопряжения к абонентов с М вычислительными машинами | 1987 |

|

SU1411758A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Устройство для передачи и приема цифровой информации | 1984 |

|

SU1285614A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1985 |

|

SU1345193A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании вычислительных систем для подключения внешних устройств к ЭВМ. Цель изобретения - повышение быстродействия. Устройство содержит M блоков формирования адреса, соединенных с магистралями адреса, запроса и сброса. Каждый блок формирования адреса содержит счетчик, коммутатор, группу элементов И, группу магистральных усилителей, элемент ИЛИ-НЕ, группу элементов ЭКВИВАЛЕНТНОСТЬ, группу элементов ИЛИ, группу элементов И, четыре триггера, одновибратор, элемент И-НЕ, элемент задержки, магистральный усилитель, элемент И, схему сравнения кодов. В устройстве за счет динамического изменения приоритетов осуществляется упорядочение подключения абонентов, т. е. независимо от величины кода приоритета гарантируется подключение абонентов с любым приоритетом в течение определенного, заранее известного интервала времени. 2 ил.

Фиг.

Фиг. 2

| Устройство для сопряжения процессора с @ абонентами | 1985 |

|

SU1257652A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения внешних устройств с ЦВМ | 1986 |

|

SU1322321A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-18—Подача