00 СХ)

ел

со

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных системах с магистральной структурой обмена информацией.

Целью изобретения является повышение достоверности передаваемых данных и рас- пжрение класса решаемых задач за счет организации индивидуального и группового режимов обмена.

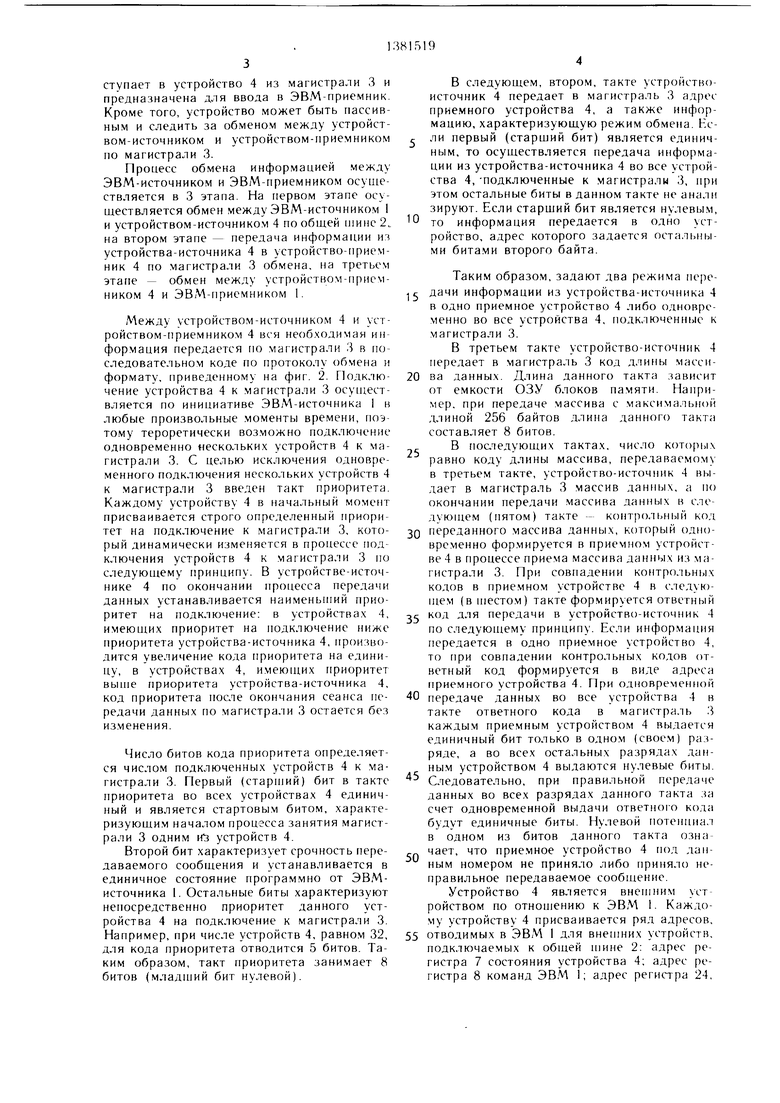

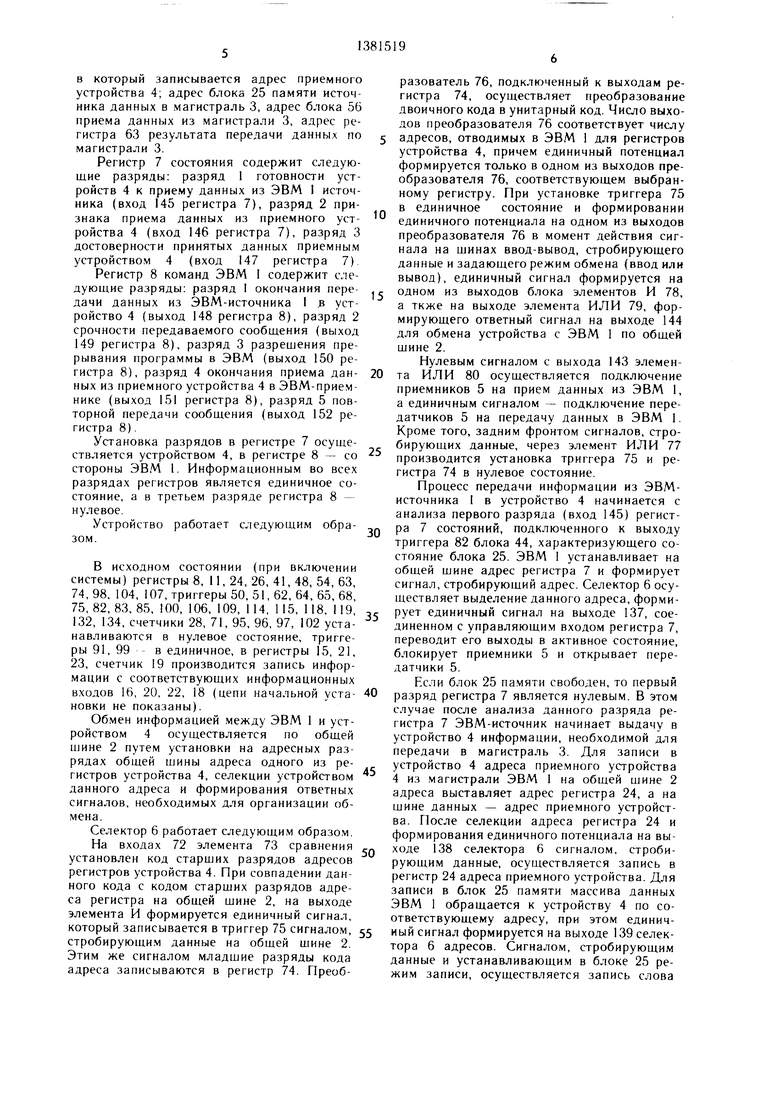

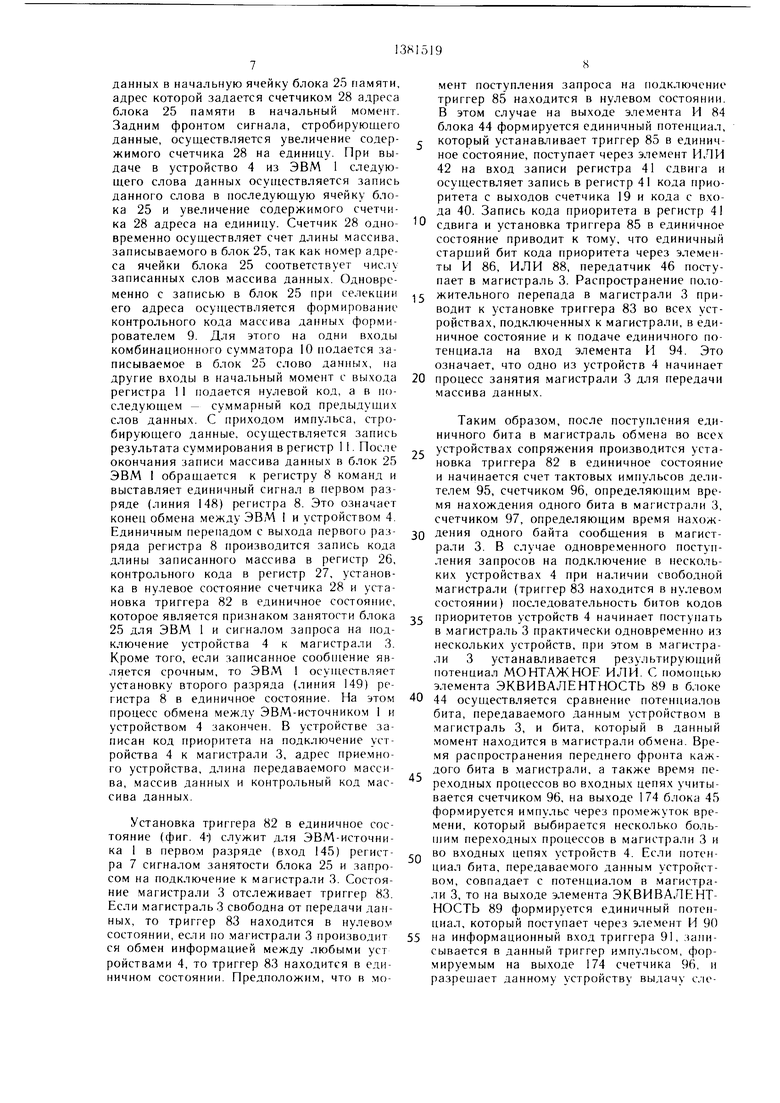

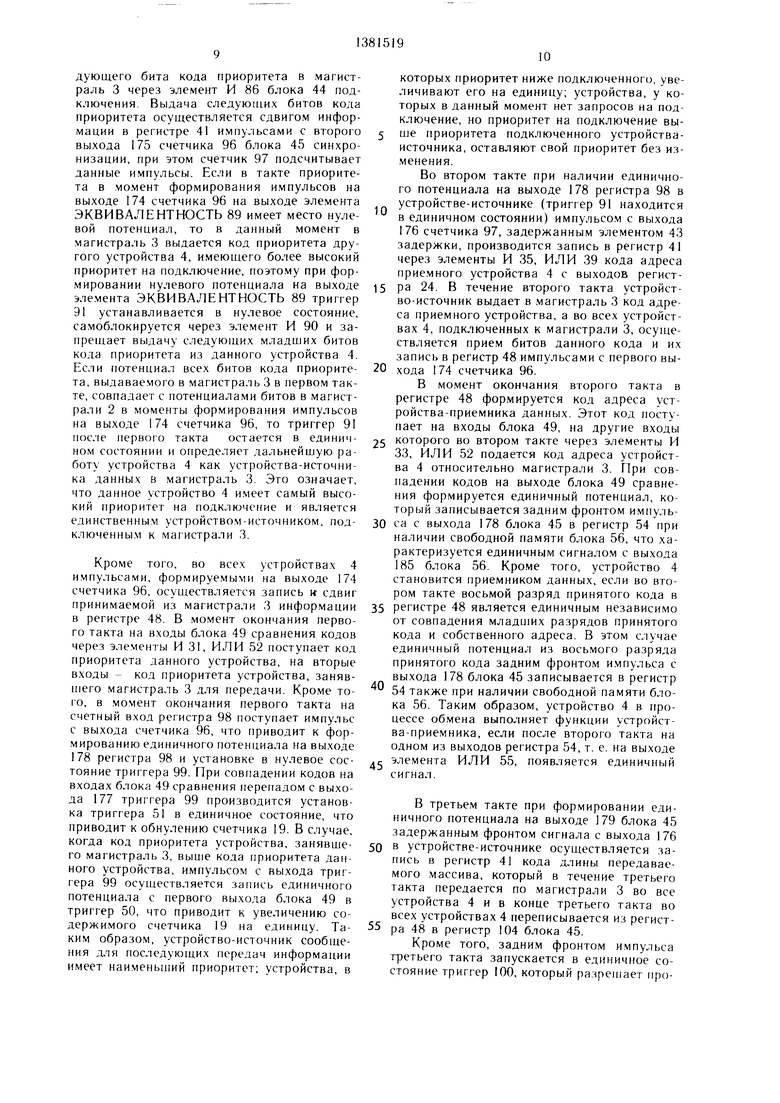

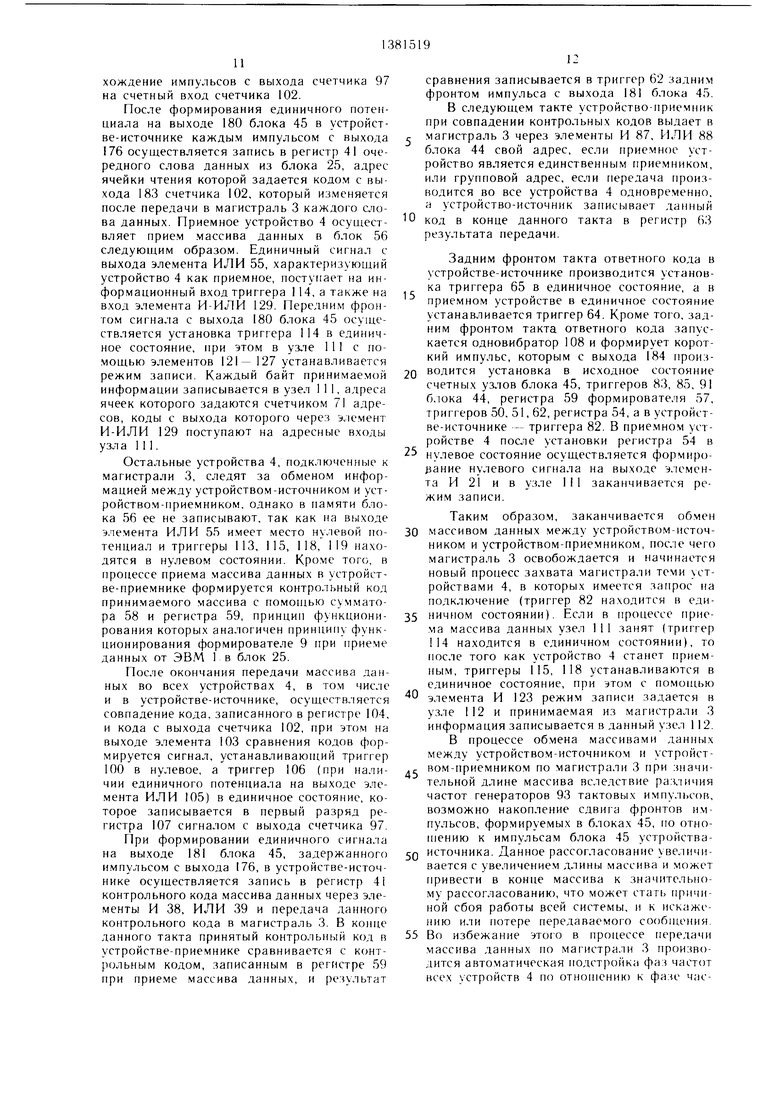

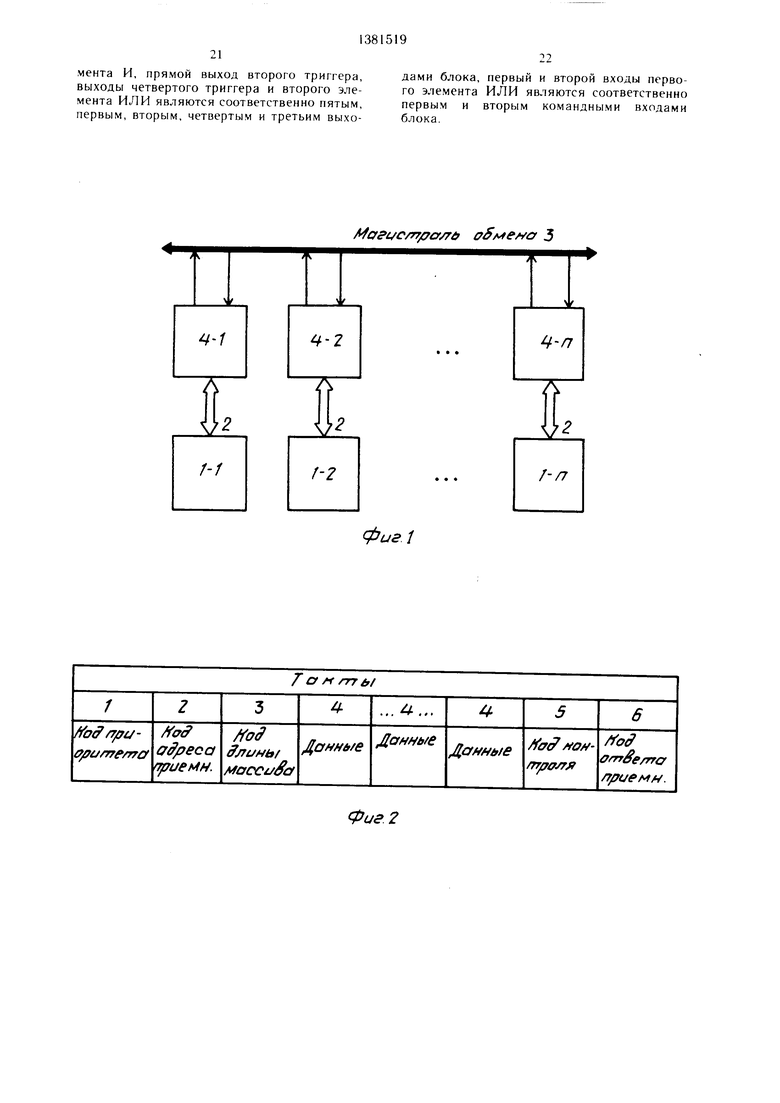

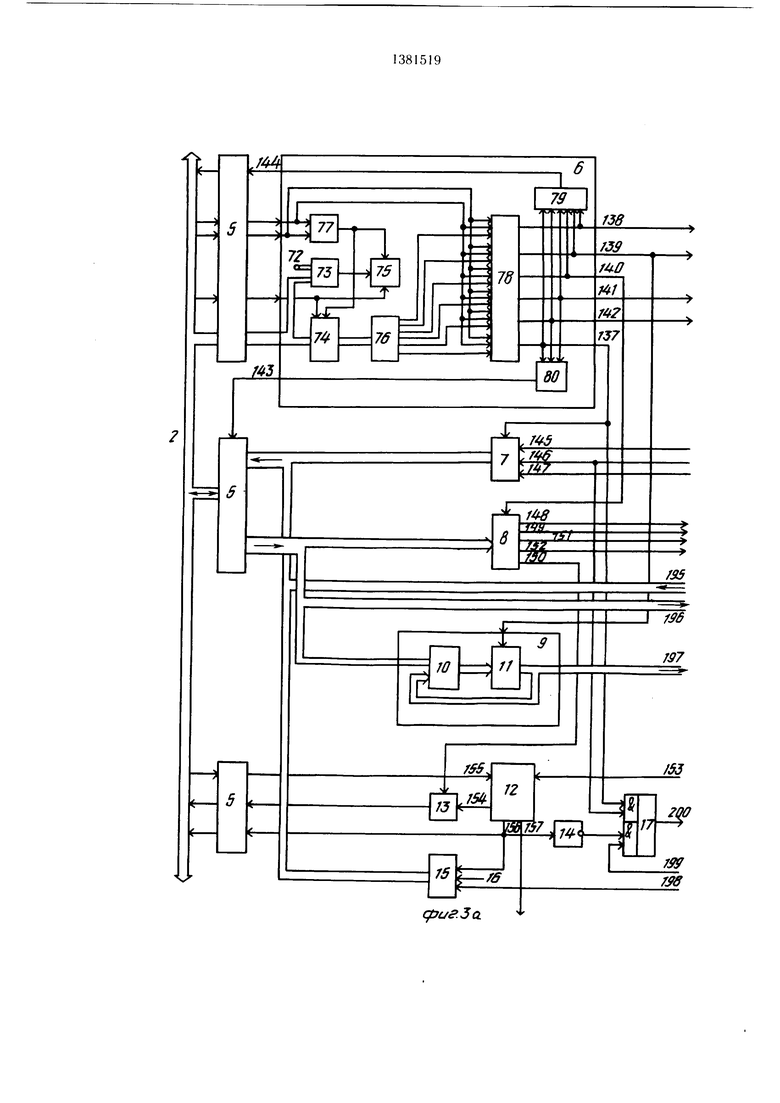

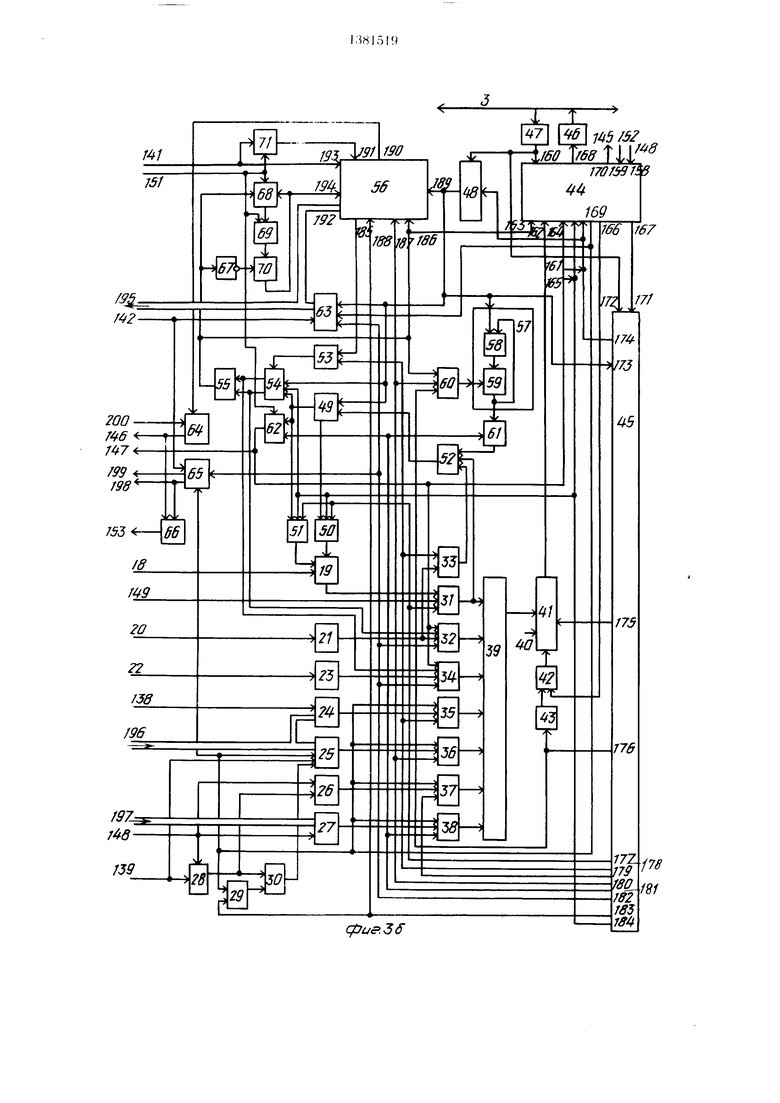

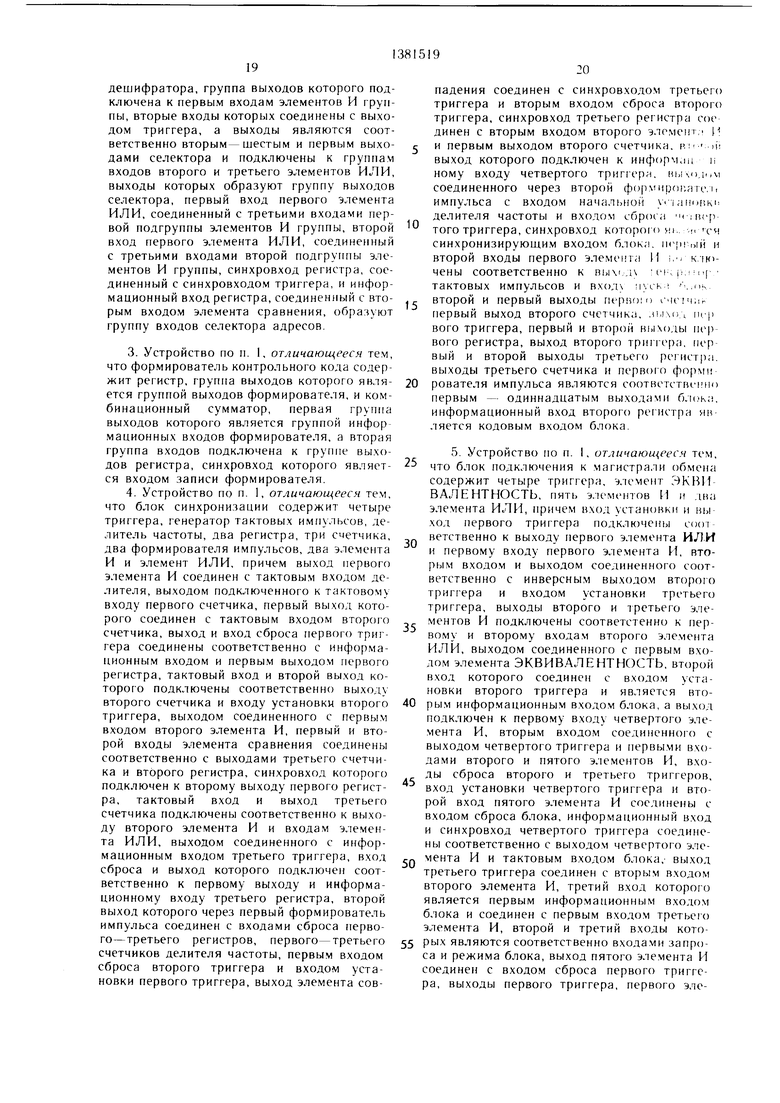

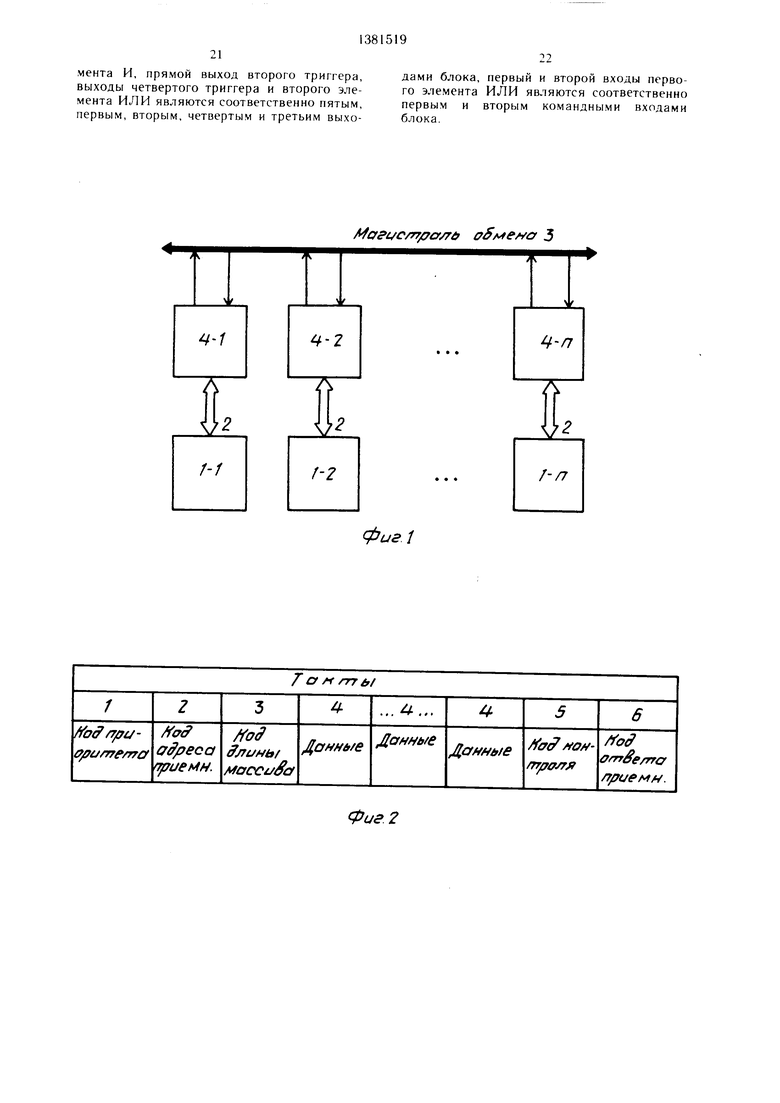

На фиг. 1 приведена структура одного из вариантов многомашинного вычислительного комплекса, в составе которого может использоваться устройство; на фиг. 2 - формат сообшения, который имеет место в магистрали обмена в процессе передачи информации .между устройствами; на фиг. 3 - структурная схема устройства; на фиг. 4 - функциональная схема блока подключения к магистрали обмена; на фиг. 5 - схема блока синхронизации; на фиг. 6 - схема блока приема данных; на фиг. 7 - схема блока прерывания.

На фиг. 1 обозначены ЭВМ 1, интерфейсы 2 (обшая шина) ЭВМ, магистраль 3 обмена, устройства 4 для сопряжения ЭВМ с магистралью обмена.

На фиг. 2 приведены номера тактов передаваемого сообшения и их содержание.

Устройство (фиг. 3) содержит блок 5 приемопередатчиков, селектор 6 адресов, регистр 7 состояния, регистр 8 команд ЭВМ, первый формирователь 9 контрольного кода, содержащий комбинационный сумматор 10 и регистр 11, блок 12 прерывания, второй элемент ИЛИ 13, второй элемент НЕ 14, регистр 15 адреса вектора прерывания, информационный вход 16 установки адреса вектора прерывания, элемент И-ИЛИ 17, вход 18 начальной установки кода приоритета, счетчик 19 кода приоритета, вход 20 установки индивидуального адреса устройства в магистрали обмена, регистр 21 индивидуального адреса, вход 22 установки группового адреса устройства в магистрали обмена, регистр 23 группового адреса, регистр 24 адреса приемника данных, блок 25 памяти передаваемых данных, регистр 26 кода длины массива, регистр 27 контрольного кода, счетчик 28 адреса, тринадцатый элемент И 29, первый элемент ИЛИ 30, второй 31, четвертый 32, третий 33, пятый 34, шестой 35, седьмой 36, восьмой 37 и девятый 38 элементы И, четвертый элемент ИЛИ 39, вход 40 синхрокода первого регистра 41 сдвига, пятый элемент ИЛИ 42, элемент 43 задержки, блок 44 подключения к магистрали обмена, блок 45 синхронизации, передатчик 46, приемник 47, второй регистр 48 сдвига, блок 49 сравнения кодов, четвертый 50 и пятый 51 триггеры, восьмой элемент ИЛИ 52, одиннадцатый элемент И 53, регистр 54 признака приема, шестой элемент ИЛИ 55, блок 56 приема данных, второй формирователь 57

контрольного кода, содержащий комбинационный сумматор 58 и регистр 59, десятый 60 и двенадцатый 61 элементы И, второй триггер 62, регистр 63 результата пере- 5 дачи, шестой 64 и первый 65 триггеры, седьмой элемент ИЛИ 66, первый элемент НЕ 67, третий триггер 68, третий элемент ИЛИ 69, первый элемент И 70, счетчик 71 адресов приема данных.

Селектор 6 содержит вход 72 задания

адреса устройства на обшей шине, элемент И 73 сравнения, регистр 74, триггер 75, преобразователь 76 кода, первый элемент ИЛИ 77, группу элементов И 78, второй элемент ИЛИ 79, третий элемент ИЛИ 80.

5Блок 44 подключения к магистрали обмена (фиг. 4) содержит первый элемент ИЛИ 81, первый 82 и второй 83 триггеры, первый элемент И 84, третий триггер 85, второй 86 и третий 87 элементы И, второй элемент ИЛИ 88, элемент ЭКВИВАЛЕНТ0 НОСТЬ 89, четвертый элемент И 90, четвертый триггер 91, пятый элемент И 92. 45 синхронизации (фиг. 5) содержит генераторы 93 тактовых импульсов, первый элемент И 94, делитель 95, первый 96

и второй 97 счетчики, первый регистр 98, пер- вый 99 и второй 100 триггеры, второй элемент И 101, третий счетчик 102, элемент 103 сравнения, второй регистр 104 (длины массива), элемент ИЛИ 105, третий триггер 106, третий регистр 107, второй

0 формирователь импульса (одновибратор) 108, четвертый триггер 109, первый формирователь (одновибоатор) 110.

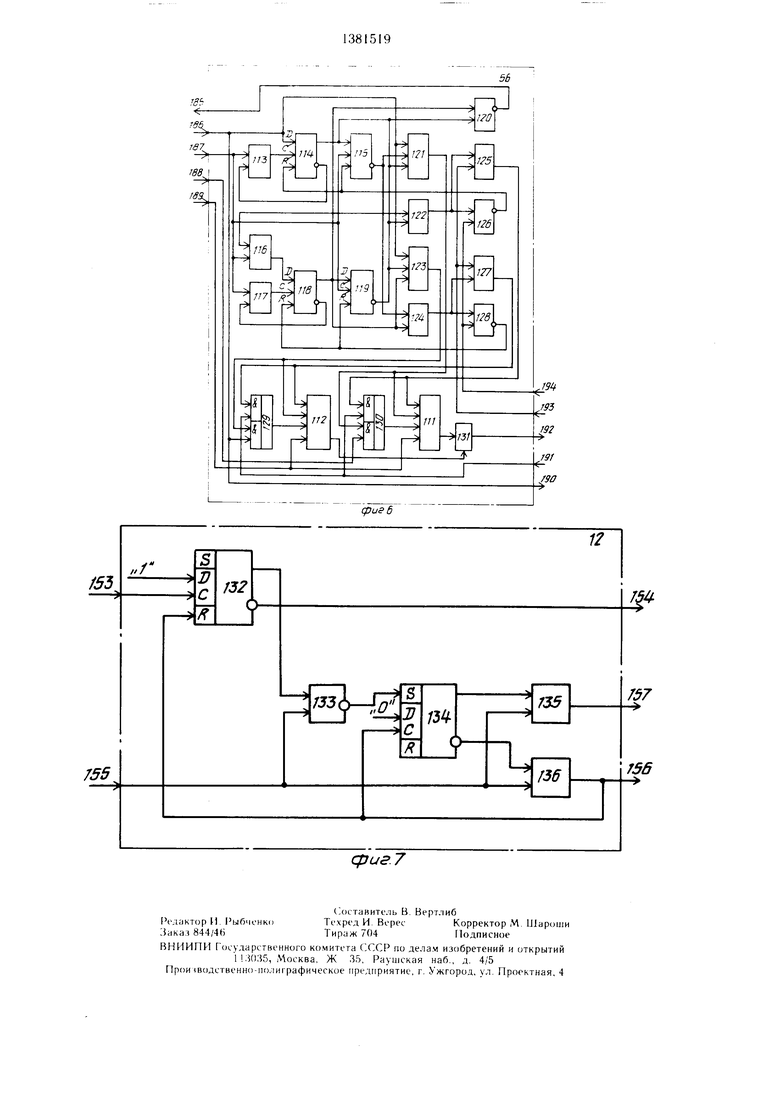

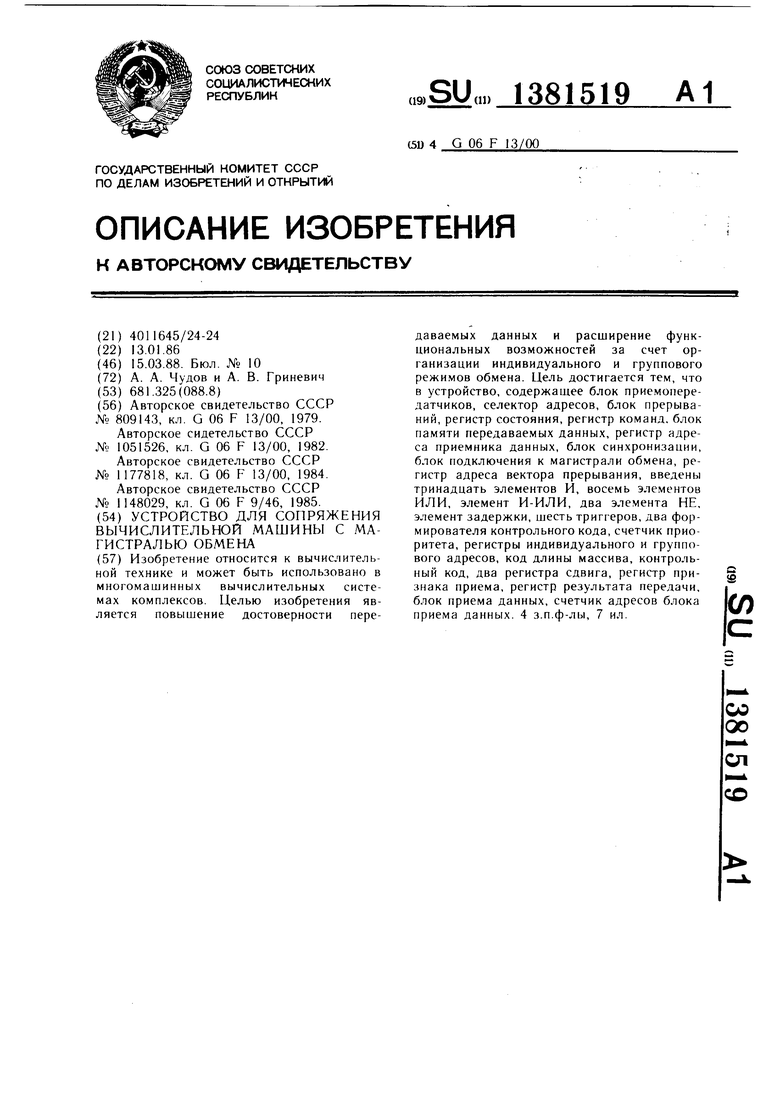

Блок 56 приема данных (фиг. 6) содержит первый 111и второй 112 узлы памяти, четвертый элемент И 113, первый 114 и второй 115 триггеры, третий 116 и пятый 117 элементы И, четвертый 118 и третий 119 триггеры, первый элемент И-НЕ 120, первый 121, шестой 122, второй 123, девятый 124 и седьмой 125 элементы И, второй элемент 0 И-НЕ 126, восьмой элемент И 127, третий элемент И-НЕ 128, первый 129 и второй 130 элементы И-ИЛИ, узел 131 элементов ИЛИ. Блок 12 прерывания (фиг. 7) содержит первый триггер 132, элемент И-НЕ 133, второй триггер 134, первый 135 и второй 136 элементы ИЛИ.

Кроме того, на фиг. 3-7 обозначены входы и выходы 137-200 блоков и функциональных элементов устройства.

Обмен информацией между ЭВМ-источ- ,, НИКОМ и ЭВМ-приемником осуществляется по магистрали 3 с помошью устройств 4, подключаемых к ЭВМ по интерфейсу 2. Каждое устройство 4 может выполнять функции источника информации. В этом случае информация поступает в устройство- 5 источник из ЭВМ-источника и предназначена для передачи в магистраль 3. Устройст во 4 может выполнять функции приемника информации. В этом случае информация поступает в устройство 4 из магистрали 3 и предназначена для ввода в ЭВМ-приемник. Кроме того, устройство может быть пассивным и следить за обменом между устройством-источником и устройством-приемником по магистрали 3.

Процесс обмена информацией между ЭВМ-источником и ЭВМ-приемником осуществляется в 3 этапа. На первом этапе осуществляется обмен между ЭВМ-источником 1 и устройством-источником 4 по общей тине 2,. на втором этапе - передача информации из устройства-источника 4 в устройство-приемник 4 по магистрали 3 обмена, на третьем этапе - обмен между устройстЕЮМ-прием- ником 4 и ЭВМ-приемником 1.

ДАежду устройством-источником 4 и устройством-приемником 4 вся необходимая информация передается по магистрали 3 в последовательном коде по протоколу обмена и формату, приведенному на фиг. 2. Подключение устройства 4 к магистрали 3 осуществляется по инициативе ЭВМ-источника 1 в любые произвольные моменты времени, поэтому тероретически воз.можно подключение одновременно нескольких устройств 4 к магистрали 3. С целью исключения одновременного подключения нескольких устройств 4 к магистрали 3 введен такт приоритета. Каждому устройству 4 в начальный момент присваивается строго определенный приоритет на подключение к магистрали 3. который динамически изменяется в процессе подключения устройств 4 к магистрали 3 по следующему принципу. В устройстве-источнике 4 по окончании процесса передачи данных устанавливается наименьший приоритет на подключение: в устройствах 4, имеющих приоритет на подключение ниже приоритета устройства-источника 4, производится увеличение кода приоритета на единицу, в устройствах 4, имеющих приоритет выше приоритета устройства-источника 4, код приоритета после окончания сеанса передачи данных по магистрали 3 остается без из.менения.

Число битов кода приоритета определяется числом подключенных устройств 4 к магистрали 3. Первый (старп1ий) бит в такте приоритета во всех устройствах 4 единичный и является стартовым битом, характеризующим началом процесса занятия магистрали 3 одним и устройств 4.

Второй бит характеризует срочность передаваемого сообщения и устанавливается в единичное состояние программно от ЭВМ- источника I. Остальные биты характеризуют непосредственно приоритет данного устройства 4 на подключение к магистрали 3. Например, при числе устройств 4. равном 32, для кода приоритета отводится 5 битов. Таким образом, такт приоритета занимает 8 битов (младший бит нулевой).

5

В следующем, втором, такте устройство- источник 4 передает в магистраль 3 адрес приемного устройства 4, а также информацию, характеризующую режим обмена. Кс ли первый (старший бит) является единичным, то осуществляется передача информации из устройства-источника 4 во все устройства 4, -подключенные к магистрали 3, при этом остальные биты в данном такте не аналн зируют. Если старший бит является нулевым,

- то информация передается в одно устройство, адрес которого задается остальными битами второго байта.

Таким образом, задают два режима пере5 дачи информации из устройства-источника 4 в одно приемное устройство 4 либо одновременно во все устройства 4, подключенные к магистрали 3.

В третьем такте устройство-источник 4 передает в магистраль 3 код длины масси0 ва данных. Длина данного такта зависит от емкости ОЗУ блоков памяти. Например, при передаче массива с максимальной длиной 256 байтов длина данного такта составляет 8 битов.

В последующих тактах, число которых равно коду длины массива, передаваемому в третьем такте, устройство-источник 4 выдает в магистраль 3 массив данных, а по окончании передачи массива данных в следующем (пятом) такте - контрольный код

0 переданного массива данных, который одновременно фор.мируется в приемном устройстве 4 в процессе приема массива данных из магистрали 3. При совпадении контрольных кодов в приемном устройстве 4 в следующем (в шестом) такте формируется ответный

5 код для передачи в устройство-источник 4 по следуюп1ему принципу. Если информация передается в одно приемное устройство 4, то при совпадении контрольных кодов ответный код формируется в виде адреса приемного устройства 4. При одновременной

0 передаче данных во все устройства 4 в такте ответного кода в магистраль 3 каждым прие.мным устройством 4 выдается единичный бит только в одно.м (своем) разряде, а во всех остальных разрядах данным устройством 4 выдаются нулевые биты. Следовательно, при правильной передаче данных во всех разрядах данного такта за счет одновременной выдачи ответного кода будут единичные биты. Нулевой потенциа. в одном из битов данного такта означает, что приемное устройство 4 под дап- ным номером не приняло либо приняло неправильное передаваемое сообщение.

Устройство 4 является внепшим уст ройством по отношению к ЭВМ 1. Каждому устройству 4 присваивается ряд адресов.

5 отводимых в ЭВМ 1 для внешних устройств, подключаемых к обшей шине 2: адрес регистра 7 состояния устройства 4; адрес регистра 8 команд ЭВМ 1; адрес регистра 24,

в который записывается адрес приемного устройства 4; адрес блока 25 памяти источника данных в магистраль 3, адрес блока 56 приема данных из магистрали 3, адрес регистра 63 результата передачи данных по магистрали 3.

Регистр 7 состояния содержит следующие разряды: разряд 1 готовности устройств 4 к приему данных из ЭВМ 1 источника (вход 145 регистра 7), разряд 2 признака приема данных из приемного уст- ройства 4 (вход 146 регистра 7), разряд 3 достоверности принятых данных приемным устройством 4 (вход 147 регистра 7)

Регистр 8 команд ЭВМ I содержит следующие разряды: разряд I окончания пере- дачи данных из ЭВМ-источника 1 .в устройство 4 (выход 148 регистра 8), разряд 2 срочности передаваемого сообщения (выход 149 регистра 8), разряд 3 разрешения прерывания программы в ЭВМ (выход 150 регистра 8), разряд 4 окончания приема дан- ных из приемного устройства 4 в ЭВМ-приемнике (выход 151 регистра 8), разряд 5 повторной передачи сообщения (выход 152 регистра 8).

Установка разрядов в регистре 7 осуществляется устройством 4, в регистре 8 - со стороны ЭВМ 1. Информационным во всех разрядах регистров является единичное состояние, а в третьем разряде регистра 8 - нулевое.

Устройство работает следующим обра зом.

В исходном состоянии (при включении системы) регистры 8, 11, 24, 26, 41, 48, 54, 63, 74,98, 104, 107, триггеры 50, 51, 62, 64, 65,68, 75, 82, 83, 85, 100, 106, 109, 114, 115, 118, 119, 132, 134, счетчики 28, 71, 95, 96, 97, 102 устанавливаются в нулевое состояние, триггеры 91, 99 - в единичное, в регистры 15, 21, 23, счетчик 19 производится запись информации с соответствующих информационных входов 16, 20, 22, 18 (цепи начальной уста- новки не показаны).

Обмен информацией между ЭВМ 1 и устройством 4 осуществляется по общей шине 2 путем установки на адресных разрядах общей щины адреса одного из регистров устройства 4, селекции устройством данного адреса и формирования ответных сигналов, необходимых для организации обмена.

Селектор 6 работает следующим образом.

На входах 72 элемента 73 сравнения установлен код старших разрядов адресов регистров устройства 4. При совпадении данного кода с кодом старших разрядов адреса регистра на общей шине 2, на выходе элемента И формируется единичный сигнал, который записывается в триггер 75 сигналом, стробирующим данные на общей шине 2. Этим же сигналом младшие разряды кода адреса записываются в регистр 74. Преоб

. 0

0

5

0

разователь 76, подключенный к выходам регистра 74, осуществляет преобразование двоичного кода в унитарный код. Число выходов преобразователя 76 соответствует чис/ту адресов, отводимых в ЭВМ 1 для регистров устройства 4, причем единичный потенциал формируется только в одном из выходов преобразователя 76, соответствующем выбранному регистру. При установке триггера 75 в единичное состояние и формировании единичного потенциала на одном из выходов преобразователя 76 в момент действия сигнала на шинах ввод-вывод, стробирующего данные и задающего режим обмена (ввод или вывод), единичный сигнал формируется на одном из выходов блока элементов И 78, а ткже на выходе элемента ИЛИ 79, формирующего ответный сигнал на выходе 144 для обмена устройства с ЭВМ 1 по общей щине 2.

Нулевым сигналом с выхода 143 элемента ИЛИ 80 осуществляется подключение приемников 5 на прием данных из ЭВМ 1, а единичным сигналом - подключение передатчиков 5 на передачу данных в ЭВМ 1. Кроме того, задним фронтом сигналов, стро- бирующих данные, через элемент ИЛИ 77 производится установка триггера 75 и регистра 74 в нулевое состояние.

Процесс передачи информации из ЭВМ- источника 1 в устройство 4 начинается с анализа первого разряда (вход 145) регистра 7 состояний, подключенного к выходу триггера 82 блока 44, характеризующего состояние блока 25. ЭВМ 1 устанавливает на общей щине адрес регистра 7 и формирует сигнал, стробирующий адрес. Селектор 6 осуществляет выделение данного адреса, формирует единичный сигнал на выходе 137, соединенном с управляющим входом регистра 7, переводит его выходы в активное состояние, блокирует приемники 5 и открывает передатчики 5.

Если блок 25 памяти свободен, то первый разряд регистра 7 является нулевым. В этом случае после анализа данного разряда регистра 7 ЭВМ-источник начинает выдачу в устройство 4 информации, необходимой для передачи в магистраль 3. Для записи в устройство 4 адреса приемного устройства 4 из магистрали ЭВМ 1 на общей щине 2 адреса выставляет адрес регистра 24, а на щине данных - адрес приемного устройства. После селекции адреса регистра 24 и формирования единичного потенциала на выходе 138 селектора 6 сигналом, стробирующим данные, осуществляется запись в регистр 24 адреса приемного устройства. Для записи в блок 25 памяти массива данных ЭВМ 1 обращается к устройству 4 по соответствующему адресу, при этом единичный сигнал формируется на выходе 139 селектора 6 адресов. Сигналом, стробирующим данные и устанавливающим в блоке 25 режим записи, осуществляется запись слова

данных в начальную ячейку блока 25 памятн, адрес которой задается счетчиком 28 адреса блока 25 намяти в начальный момент. Задним фронтом сигнала, стробируюшего данные, осуществляется увеличение содержимого счетчика 28 на единицу. При выдаче в устройство 4 из ЭВМ 1 следующего слова данных осуществляется запись данного слова в последующую ячейку блока 25 и увеличение содержимого счетчика 28 адреса на единицу. Счетчик 28 одновременно осуществляет счет длины массива, записываемого в блок 25, так как но.мер адреса ячейки блока 25 соответствует числу записанных слов массива данных. Одновременно с записью в блок 25 при селекции его адреса осуществляется формирование контрольного кода массива данных формирователем 9. Для этого на одни входы комбинационного сумматора 10 подается записываемое в блок 25 слово данных, па другие входы в начальный момент с выхода регистра 11 подается нулевой код, а в последующем - суммарный код предыдущих слов данных. С приходом импульса, стро- бирующего данные, осуществляется запись результата суммирования в регистр 11. После окончания записи массива данных в блок 25 ЭВМ I обращается к регистру 8 команд и выставляет единичный сигнал в первом разряде (линия 148) регистра 8. Это означает конец обмена между ЭВМ I и устройством 4. Единичным перепадом с выхода первого разряда регистра 8 производится запись кода длины записанного массива в регистр 26, контрольного кода в регистр 27, установка в нулевое состояние счетчика 28 и установка триггера 82 в единичное состояние, которое является признаком занятости блока 25 для ЭВМ 1 и сигналом запроса на подключение устройства 4 к магистрали 3. Кроме того, если записанное сообщение является срочным, то ЭВМ I осуществляет установку второго разряда (линия 149) регистра 8 в единичное состояние. На этом процесс обмена между ЭВМ-источником 1 и устройством 4 закончен. В устройстве записан код приоритета на подключение устройства 4 к магистрали 3, адрес прие.мно- го устройства, длина передаваемого массива, массив данных и контрольный код массива данных.

Установка триггера 82 в единичное состояние (фиг. 4j служит для ЭВМ-источника 1 в первом разряде (вход 145) регистра 7 сигналом занятости блока 25 и запросом на подключение к магистрали 3. Состояние магистрали 3 отслеживает триггер 83. Если магистраль 3 свободна от передачи данных, то триггер 83 находится в нулевом состоянии, еоти по магистрали 3 производит ся обмен информацией между любыми уст ройствами 4, то триггер 83 находится в единичном состоянии. Предположим, что в .момент поступления запроса на подключение триггер 85 находится в нулевом состоянии. В этом случае на выходе элемента И 84 блока 44 формируется единичный потенциал,

который устанавливает триггер 85 в единичное состояние, поступает через элемент ИЛИ 42 на вход записи регистра 41 сдвига и осуществляет запись в регистр 41 кода приоритета с выходов счетчика 19 и кода с входа 40. Запись кода приоритета в регистр 41

сдвига и установка триггера 85 в единичное состояние приводит к тому, что единичный старший бит кода приоритета через элементы И 86, ИЛИ 88, передатчик 46 поступает в магистраль 3. Распространение поло5 жительного перепада в магистрали 3 приводит к установке триггера 83 во всех устройствах, подключенных к магистрали, в единичное состояние и к подаче единичного потенциала на вход элемента И 94. Это означает, что одно из устройств 4 начинает

0 процесс занятия магистрали 3 для передачи массива данных.

Таким образом, после поступления единичного бита в магистраль обмена во всех

5 устройствах сопряжения производится установка триггера 82 в единичное состояние и начинается счет тактовых импульсов делителем 95, счетчиком 96, определяющим время нахождения одного бита в магистрали 3, счетчиком 97, определяющим время нахож0 дения одного байта сообщения в магистрали 3. В случае одновременного поступления запросов на подключение в нескольких устройствах 4 при наличии свободной магистрали (триггер 83 находится в нулевом состоянии) последовательность битов кодов

5 приоритетов устройств 4 начинает поступать в магистраль 3 практически одновременно из нескольких устройств, при этом в магистрали 3 устанавливается результирующий потенциал МОНТАЖНОЕ ИЛИ. С помоп1ьк элемента ЭКВИВАЛЕНТНОСТЬ 89 в блоке

0 44 осуществляется сравнение потенциалов бита, передаваемого данны.м устройство.м в магистраль 3, и бита, который в данный момент находится в магистрали обмена. Время распространения переднего фронта каждого бита в магистрали, а также время переходных процессов во входных цепях учитывается счетчиком 96, на выходе 174 блока 45 формируется импульс через промежуток времени, который выбирается несколько большим переходных процессов в магистрали 3 и д во входных цепях устройств 4. Если потенциал бита, передаваемого данным устройством, совпадает с потенциалом в магистрали 3, то на выходе элемента ЭКВИВАЛЕНТНОСТЬ 89 формируется единичный потенциал, который поступает через элемент И 90 5 на информационный вход триггера 91, записывается в данный триггер и.мпульсом, формируемым на выходе 174 счетчика 96, и разрешает данно.му устройству выдачу еледующего бита кода приоритета в магистраль 3 через элемент И 86 блока 44 подключения. Выдача следующих битов кода приоритета осуществляется сдвигом информации в регистре 41 импульсами с второго выхода 175 счетчика 96 блока 45 синхронизации, при этом счетчик 97 подсчитывает данные импульсы. Если в такте приоритета в момент формирования импульсов на выходе 174 счетчика 96 на выходе элемента ЭКВИВАЛЕНТНОСТЬ 89 имеет место нулевой потенциал, то в данный момент в магистраль 3 выдается код приоритета другого устройства 4, имеющего более высокий приоритет на подключение, поэтому при формировании нулевого потенциала на выходе элемента ЭКВИВАЛЕНТНОСТЬ 89 триггер Э1 устанавливается в нулевое состояние, самоблокируется через элемент И 90 и запрещает выдачу следующих младщих битов кода приоритета из данного устройства 4. Р1сли потенциал всех битов кода приоритета, выдаваемого в магистраль 3 в первом такте, совпадает с потенциалами битов в магистрали 2 в моменты формирования импульсов на выходе 174 счетчика 96, то триггер 91 после первого такта остается в единичном состоянии и определяет дальнейщую работу устройства 4 как устройства-источника данных в магистраль 3. Это означает, что данное устройство 4 имеет самый высокий приоритет на подключение и является единственным устройством-источником, подключенным к магистрали 3.

Кроме того, во всех устройствах 4 импульсами, формируемыми на выходе 174 счетчика 96, осуществляется запись ч сдвиг принимаемой из магистрали 3 информации в регистре 48. В момент окончания первого такта на входы блока 49 сравнения кодов через элементы И 31, ИЛИ 52 поступает код приоритета данного устройства, на вторые входы - код приоритета устройства, занявшего магистраль 3 для передачи. Кроме того, в момент окончания первого такта на счетный вход регистра 98 поступает импульс с выхода счетчика 96, что приводит к формированию единичного потенциала на выходе 178 регистра 98 и установке в нулевое состояние триггера 99. При совпадении кодов на входах блока 49 сравнения перепадом с выхода 177 триггера 99 производится установка триггера 51 в единичное состояние, что приводит к обнулению счетчика 19. В случае, когда код приоритета устройства, занявще- го магистраль 3, выше кода приоритета данного устройства, импульсом с выхода триггера 99 осуществляется запись единичного потенциала с первого выхода блока 49 в триггер 50, что приводит к увеличению содержимого счетчика 19 на единицу. Таким образом, устройство-источник сообщения для последующих передач информации имеет наименьший приоритет; устройства, в

которых приоритет ниже подключенного, увеличивают его на единицу; устройства, у которых в данный момент нет запросов на подключение, но приоритет на подключение выще приоритета подключенного устройства- источника, оставляют свой приоритет без изменения.

Во втором такте при наличии единичного потенциала на выходе 178 регистра 98 в устройстве-источнике (триггер 91 находится в единичном состоянии) импульсом с выхода 176 счетчика 97, задержанным элементом 43 задержки, производится запись в регистр 41 через элементы И 35, ИЛИ 39 кода адреса приемного устройства 4 с выходов регист5 ра 24. В течение второго такта устройство-источник выдает в .магистраль 3 код адреса приемного устройства, а во всех устройствах 4, подключенных к магистрали 3, осуществляется прием битов данного кода и их запись в регистр 48 импульсами с первого вы0 хода 174 счетчика 96.

В момент окончания второго такта в регистре 48 формируется код адреса устройства-приемника данных. Этот код поступает на входы блока 49, на другие входы

5 которого во втором такте через элементы И 33, ИЛИ 52 подается код адреса устройства 4 относительно магистрали 3. При совпадении кодов на выходе блока 49 сравнения формируется единичный потенциал, который записывается задним фронтом импуль0 са с выхода 178 блока 45 в регистр 54 при наличии свободной памяти блока 56, что характеризуется единичным сигналом с выхода 185 блока 56. Кроме того, устройство 4 становится приемником данных, если во втором такте восьмой разряд принятого кода в

5 регистре 48 является единичным независимо от совпадения младших разрядов принятого кода и собственного адреса. В этом случае единичный потенциал из восьмого разряда принятого кода задним фронтом и.мпульса с

выхода 178 блока 45 записывается в регистр П г ,-

54 также при наличии свободной памяти блока 56. Таким образом, устройство 4 в процессе обмена выполняет функции устройства-приемника, если после второго такта на одном из выходов регистра 54, т. е. на выходе г элемента ИЛИ 55, появляется единичный сигнал.

В третьем такте при формировании единичного потенциала на выходе 179 блока 45 задержанным фронтом сигнала с выхода 176

0 в устройстве-источнике осуществляется запись в регистр 41 кода длины передаваемого массива, который в течение третьего такта передается по магистрали 3 во все устройства 4 и в конце третьего такта во всех устройствах 4 переписывается из регист5 ра 48 в регистр 104 блока 45.

Кроме того, задним фронтом импульса третьего такта запускается в единичное состояние триггер 100, который разрешает про11

12

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема цифровой информации | 1984 |

|

SU1285614A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1434448A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1990 |

|

SU1728867A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1983 |

|

SU1109754A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072046A1 |

| Устройство для сопряжения двух ЭВМ | 1987 |

|

SU1499360A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1989 |

|

SU1683022A1 |

Изобретение отиосится к вычислительной технике и может быть использовано в многомашинных вычислительных системах комплексов. Целью изобретения является повышение достоверности передаваемых данных и расширение функциональных возможностей за счет организации индивидуального и группового режимов обмена. Цель достигается тем, что в устройство, содержашее блок приемопередатчиков, селектор адресов, блок прерываний, регистр состояния, регистр команд, блок памяти передаваемых данных, регистр адреса приемника данных, блок синхронизации, блок подключения к магистрали обмена, регистр адреса вектора прерывания, введены тринадцать элементов И, восемь элементов ИЛИ, элемент И-ИЛИ, два элемента НЕ, элемент задержки, шесть триггеров, два формирователя контрольного кода, счетчик приоритета, регистры индивидуального и группового адресов, код длины массива, контрольный код, два регистра сдвига, регистр признака приема, регистр результата передачи, блок приема данных, счетчик адресов блока приема данных. 4 з.п.ф-лы, 7 ил.

хождение импульсов с выхода счетчика 97 на счетный вход счетчика 102.

После формирования единичного потенциала на выходе 180 блока 45 в устройстве-источнике каждым импульсом с выхода 176 осуществляется запись в регистр 41 очередного слова данных из блока 25, адрес ячейки чтения которой задается кодом с выхода 183 счетчика 102, который изменяется после передачи в магистраль 3 каждого слова данных. Приемное устройство 4 осуществляет прием массива данных в блок 56 следующим образом. Единичный сигнал с выхода элемента ИЛИ 55, характеризующий устройство 4 как приемное, поступает на информационный вход триггера 114, а также на вход элемента И-ИЛИ 129. Передним фронтом сигнала с выхода 180 блока 45 осуществляется установка триггера 114 в единичное состояние, при этом в узле 111 с помощью элементов 121- 127 устанавливается режим записи. Каждый байт принимаемой информации записывается в узел 111, адреса ячеек которого задаются счетчиком 71 адресов, коды с выхода которого через эле.мент И-ИЛИ 129 поступают на адресные входы узл а 1 11.

Остальные устройства 4, подключенные к магистрали 3, следят за обменом информацией между устройством-источником и устройством-приемником, однако в памяти блока 56 ее не записывают, так как на выходе эле.мента ИЛИ 55 и.меет место нулевой потенциал и триггеры 113, 115, 118, 119 находятся в нулевом состоянии. Кроме того, в процессе приема массива данных в устройстве-приемнике формируется контрольный код принимаемого .массива с помощью сумматора 58 и регистра 59, принцип функционирования которых аналогичен принципу функционирования формирователе 9 при приеме данных от ЭВМ 1 в блок 25.

После окончания передачи массива данных во всех устройствах 4, в том числе и в устройстве-источнике, осуществляется совпадение кода, записанного в регистре 104, и кода с выхода счетчика 102, при этом на выходе элемента 103 сравнения кодов формируется сигнал, устанавливающий триггер 100 в нулевое, а триггер 106 (при наличии единичного потенциала на выходе элемента ИЛИ 105) в единичное состояние, которое записывается в первый разряд регистра 107 сигналом с выхода счетчика 97.

При формировании единичного сигнала на выходе 181 блока 45, задержанного импу.льсом с выхода 176, в устройстве-источнике осуществляется запись в регистр 41 контрольного кода массива данных через элементы И 38, ИЛИ 39 и передача данного контрольного кода в магистраль 3. В конце данного такта принятый контрольный код в устройстве-приемнике сравнивается с контрольным кодом, записанным в регистре 59 при приеме массива данных, и результат

сравнения записывается в триггер 62 задним

фронтом импульса с выхода 181 блока 45.

В следующем такте устройство-приемник

при совпадении контрольных кодов выдает в

магистраль 3 через элементы И 87, ИЛИ 88 блока 44 свой адрес, если приемное устройство является единственным приемником, или групповой адрес, если передача производится во все устройства 4 одновременно, а устройство-источник записывает данный

0 код в конце данного такта в регистр 63 результата передачи.

Задним фронтом такта ответного кода в устройстве-источнике производится установка триггера 65 в единичное состояние, а в приемном устройстве в единичное состояние устанавливается триггер 64. Кроме того, задним фронтом такта ответного кода запускается одновибратор 108 и формирует короткий импульс, которым с выхода 184 произ0 водится установка в исходное состояние счетных узлов блока 45, триггеров 83, 85, 91 блока 44, регистра 59 формирователя 57, триггеров 50, 51, 62, регистра 54, а в устройстве-источнике - триггера 82. В прие.мном устройстве 4 после установки регистра 54 в

5 нулевое состояние осуществляется формиро- нулевого сигнала на выходе элемента И 21 и в узле 111 заканчивается режим записи.

Таким образом, заканчивается обмен

0 массивом данных между устройством-источником и устройством-приемником, после чего магистраль 3 освобождается и начинается новый процесс захвата магистрали теми устройствами 4, в которых имеется запрос на подключение (триггер 82 находится в еди5 ничном состоянии). Если в процессе приема массива данных узел 111 занят (триггер 114 находится в единичном состоянии), то после того как устройство 4 станет приемным, триггеры 115, 118 устанавливаются в единичное состояние, при этом с помощью

0 элемента И 123 режим записи задается в

узле 112 и принимаемая из магистрали 3

информация записывается в данный узел 112.

В процессе обмена массивами данных

между устройством-источником и устройстг вом-приемником по магистрали 3 при значительной длине массива вследствие различия частот генераторов 93 тактовых импульсов, возможно накопление сдвига фронтов и.м- пульсов, формируемых в блоках 45, по отношению к импульсам блока 45 устройстваQ источника. Данное рассогласование увеличивается с увеличением длины массива и может привести в конце массива к значительному рассогласованию, что может стать причиной сбоя работы всей системы, и к искажению или ютере передаваемого сообщения.

5 Во избежание этого в процессе передачи массива данных по магистрали 3 производится авто.матическая подстройка фаз частот всех устройств 4 по отношению к фазе часJ3

тоты устройства-источника следующим образом. В процессе записи информации в регистр 41 в устройстве-источнике одновременно осуществляется запись в регистр 41 с входов 40 синхрокода, который является двух- битным и представляет собой «О в первом бите и «1 во втором бите. Данный код поступает в магистраль 3 в конце каждого такта, а также между каждым байтом данных, считываемых из блока 25. Кроме того, в каждом устройстве 4 формируется единичный потенциал на выходе счетчика 97 на время нахождения в магистрали 3 битов синхрокода, который поступает на информационный вход триггера 109 блока 45. Во время прохождения по магистрали 3 положительного перепада синхрокода данным перепадом осуществляется установка триггера 109 в единичное состояние, а на выходе одновибратора 110 формируется короткий импульс, который устанавливает делитель 95 и триггер 109 в нулевое состояние и исключает накопление рассогласования фаз частот импульсов на выходе делителя 95, т. е. исключает рассогласование фронтов импульсов, формируемых во всех устройствах 4 на выходах 174- 184 блока 45 в процессе передачи данных по магистрали 3.

Установка триггера 82 в устройстве-источнике в нулевое состояние, а триггера 64 в устройстве-приемнике в единичное состояние но окончании обмена данными приводит к формированию нулевого сигнала в разряде I (вход 145) регистра 7 состояния и к формированию в устройстве-приемника единичного сигнала в разряде 2 (вход 146) регистра 7, а также к установке триггера 132 в блоке 12 прерывания. В случае работы по прерываниям ЭВМ устанавливает единичный сигнал в разряде 3 (выход 150) регистра 8 и разрешает устройству выдачу сигнала требования прерывания через элемент ИЛИ 13 в ЭВМ 1, которая формирует ответный сигнал, устанавливающий триггеры 132 в нулевое состояние с помощью элементов 133- 136 блока 12. Устройство 4 выставляет на общую 2 вектор прерывания программы ЭВМ путем перевода выходов регистра 15 в активное состояние сигналом с выхода блока 12. ЭВМ-источник после принятия вектора прерывания от устройства-источника осуществляет обращение к регистру 63 результата передачи, выставляя на общей щине 2 его адрес. После селекции данного адреса и формирования единичного сигнала на выходе 142 селектора 6 осуществляется чтение содержимого регистра 63 и установка триггера 65 в нулевое состояние.

ЭВМ-приемник сообщения после чтения адреса вектора прерывания с нулевым младшим разрядом вектора прерывания, задаваемым триггером 65, переходит на подпрограмму чтения данных из блока 56 приема данных, адрес которого селектируется селек1381519

14

тором 6. Режим чтения задается на входе блока 56 во время действия единичного сигнала на выходе 141 селектора 6 адреса. С помощью элементов И 121, 125, 127 блока 56 осуществляется выбор узла 111 или 112, из которого осуществляется чтение принятого массива. Изменение адресов блока 56 осуществляется задним фронтом сигнала с выхода 141 селектора 6. После окончания

,. чтения принятого массива ЭВМ-приемник дважды обращается к регистру 8 и устанавливает сначала «I, а затем «О в четвертом разряде данного регистра. Если устройство 4 не участвует в данный момент в приеме следующего массива данных из

5 магистрали 3 (на выходе элемента ИЛИ 55 имеет место нулевой потенциал), то данный импульс с выхода 151 регистра 8 устанавливает в «О счетчик 71 и через элементы ИЛИ 69, И 70 поступает на вход блока 56 и устанавливает в «6 через элемент И-НЕ

0 126 или 128 триггеры 114, 115 или 118, 119 в зависимости от потенциалов на выходах элементов И 121-124. Если устройство 4 в .момент окончания чтения данных в ЭВМ 1 принимает очередной массив данных из ма5 гистрали 3, то на выходе элемента ИЛИ 55 имеет место единичный потенциал, который, поступает на информационный вход триггера 68, поэтому в момент прихода импульса с выхода 151 регистра 8 данный импульс не поступает на вход блока 56, а производит0 ся установка триггера 68 в «1, которая поступает на вход сброса триггера 68 и на вход блока 56 только после прием а очередного массива данных из магистрали 3 в узел 112 памяти блока 56, когда на выходе эле- MeHta ИЛИ 55 сформируется нулевой по5 тенциал.

Если ЭВМ 1 работает в программном режиме и запрещает прерывание программы, то после анализа разряда 3 (вход 147) регистра 7 и формирования единичного нала в данном разряде ЭВМ-источник ocyuie- ствляет чтение содержимого регистра 63, а ЭВМ-приемник при наличии единичного сигнала в разряде 2 (вход 146) регистра 7 осуществляет чтение принятого массива из

с блока 56, так же, как и при работе в режиме прерывания.

Формула изобретения

15

прерывания, информационный вход которого является входом установки адреса вектора прерывания устройства, селектор адресов, группа входов которого соединена с первой группой выходов блока приемопередатчиков, а первый, второй, третий и четвертый выходы и группа выходов - соответственно с синхровходами записи регистра состояния, регистра адреса приемника данных, блока памяти передаваемых данных н регистра команд и первой группой входов блока приемопередатчиков, вторая группя выходов которого соединена с информационными входами регистра команд, регист ра адреса приемника данных и блока памяти передаваемых данных, выходы регистра состояния и регистра адреса вектора гфе)ы- вания соединены с второй группой входов блока приемопередатчиков, первый и второй разрядные выходы регистра команд подключены соответственно к первому и второму командным входам блока подключения к магистрали обмена, отличающееся тем, что, с целью повышения достоверности передаваемых данных и расширения класса решаемых задач устройства, в него введены шесть триггеров, восемь элементов ИЛИ, тринадцать элементов И, элемент И-ИЛИ, два элемента НЕ, элемент задержки, два формирователя контрольного кода, регистр индивидуального адреса устройства, регистр группового адреса устройства, регистр кода длины массива, регистр контрольного кода, счетчик адресов передаваемых данных, два регистра сдвига, блок сравнения кодов, регистр признака приема, блок приема данных, регистр результата передачи, счетчик адресов приема данных, причем информационные входы счетчика кода приоритета, регистра индивидуального адреса устройства и регистра группового адреса устройства являются соответственно входами начальной установки кода приоритета, индивидуального и группового адреса устройства, счетный вход сметчика адресов передаваемых данных соединен с третьим выходом селектора адресов, выход счетчика адресов приема данных подключен к первому адресному входу блока приема данных, а счетный вход - к пятому выходу селектора адресов и входу признака вывода блока приема данных, П1естой выход селектора адресов соединен с входом чтения регистра результата передачи и с входом сброса первого триггера, первый разрядный выход регистра команд соединен с входами записи регистра кода длины массива и регистра контрольного кода, с входом сброса счетчика адресов передаваемых данных, выход которого соединен с первым входом первого элемента ИЛИ и информационным входом регистра длины массива, третий разрядный выход регистра команд соединен с первым входом первого элемента И, второй вход которого соединен с выходом счетчика кода приоритета, четвертый

1Ь

0

5

0

5

0

5

0

5

разрядный выход регистра команд соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом требования прерывания блока прерываний, пятый разрядный выход регистра команд соединен с входами сброса счетчика адресов приема данных и второго триггера, со счетным входом третьего триггера и с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом третьего триггера, вход установки «О которого соединен с выходом второго элемента И и с входом признака конца вывода блока приема данных, третий выход селектора адреса соединен с входом записи первого формирователя контрольного кода, группа информационных входов которого соединена с второй группой выходов блока приемопередатчиков, выход первого формирователя контрольного кода соединен с информационным входом регистра контрольного кода, выход регистра индивидуального адреса соединен с первыми входами третьего и четвертого элементов И, выходы регистра группового адреса, регистра адреса приемника данных, блока памяти передаваемых данных, регистров длины массива и контрольного кода соединены соответственно с первыми входами пятого девятого элементов И, выходы второго, четвертого- девятого элементов И соединены с группой входов четвертого элемента ИЛИ, выход которого соединен с первым информационным входом первого регистра сдвига, второй информационный вход которого является входом синхровхода устройства, первый выход блока синхронизации соединен с тактовым входом блока подключения к магистрали обмена и со счетным входом второго регистра сдвига, второй выход блока синхронизации подключен к счетному входу первого регистра сдвига, вход записи которого соединен с выходом пятого элемента ИЛИ, третий выход блока синхронизации соединен с первым входом десятого элемента И и через элемент задержки - с первым входом пятого элемента ИЛИ, второй вход которого соединен с первым выходом блока подключения к магистрали обмена, четвертый выход блока синхронизации соединен с третьим входом второго элемента И и с синхровходами четвертого и пятого триггеров, выходы которых подключены соответственно к счетному входу и входу сброса счетчика кода приоритета, пятый выход блока синхронизации соединен с вторыми входами шестого и пятого элементов И и с первым входом одиннадцатого элемента И, второй вход которого соединен с первым выходом блока приема данных, шестой выход блока синхронизации соединен с вторым входом восьмого элемента И, седьмой выход блока синхронизации соединен с вторыми входами седьмого и десятого элементов И и с входом признака ввода информации блока приема данных, второй выход которого соединен с

Г/

входом установки в «1 шестого триггера, восьмой выход блока синхронизации соединен с вторым входом девятого элемента И и .iM входом двенадцатого элементов И и синхровходом второго триггера, девятый выход б, 1ока синхронизации соединен с вторыми входами четвертого и IIHTOI O элементов И, с синхровходами первого триггера и регистра результата передачи, группа выходов которого и г-руппа выходо блока приема данных соединены с второй группой входов блока приемопередатчиков, десятый выход блоча синхр(;ни;)ации соединен с вторым ад- peeiii,iM входом блока приема данных и с периым входом тринадпатого элемента И, ) которого соеди 1ен с вторым входом первого элемента ИЛИ, выход которого сое- дин( н с адресным входом блока памяти нередаваемьгх данных, одиннадцатый выход блока синхронизации соединен с входами сброса четве|)того и питого триггеров, регистра признака приема и блока подключения к магис1 1али обм( на, перв1)1Й информацион- iihiii вход KOTopoio соединен с выходом первого регистра, вход запроса блока подключения к магистрали обмена соединен с выходом HiecToro э.пемента ИЛИ, с входом за- про -а на ввод информации блока приема даи.|ьг, с третьим входом десятого элемента ИЛИ, с информационным входом третьего 1риг|-ера и через первый элемент ИК с iiejiiibiM iiepBoi o э.лемента И, второй вход когорого соединен с выходом третьего э,1емента И, 1И, вход режима блока нодклю- чепия к машстра.ли обмена соединен с выходом второк) триг1 е|)а, с гретьими входами четвертого и пятою э.к ментов И, второй выход блока подключ1 ния к магистрали обмена соединен с входом пуска блока синхронизации, третий выход блока подключения к магистрали обмена соединен через передатчик с входом приемника, вход приемника и выход передатчика образуют вход-выход устройства Д.1Я подключения к магистра.чи обмена, выход приемника иодключен к второму информационному входу блока под- к.1ючения, к магистрали обмена, к синхро- входу б,чока синхронизации и к информационному входу второго )егистра сдвига, четвертый выход блока нодключения к магистрали обмена соединен с третьими входами HiecToro девятого элементов И, с ин- ()ормапион 1ым входом первого триггера, с входом режима чтения блока памяти передаваемых да1П1ых и е унрав,:1яю1пим вхо.шм |iei истра резу.пьтата передачи, г|ять|й б,1ока подключения к магистра;1и обмена соединен с первым информационным вхг)л)1 регисгра счктояния, второй информациоь ный вход которого соединен с выходом mecroio триггера, с первым входом седьмог О элемен та ИЛИ и с первым входом элемента И-И, 1И, второй вход которого соединен с первым выходом селектора ад)еса, выход второго регистра сдвига соединен с информа111(И18

0

ным входом блока приема данных, с первым информационным входом блока сравнения кодов, с информационным входом регистра результата передачи, с первым ин2 формационным входом регистра признака приема, с кодовым входом блока синхронизации и с информационным входом второго формирователя контрольного кода, вход записи которого соединен с выходом десятого элемента И, выход второго формирователя контрольного кода соединен с вторым входом двенадцатого элемента И, выход которого соединен с первым входом восьмого элемента ИЛИ, второй и третий входы которого соединены соответственно с вьгхо5 дами второго и третьего элементов И, выход восьмого элемента ИЛИ соединен с вторым информационным входом блока сравнения кодов, первый выход которого соединен с информационным входом четвертого триггера, второй выход блока сравнения ко0 дов соединен с информационными входами второго и пятого триггеров и с вторым информационным входом регистра признака приема, вход записи которого соединен с выходом одиннадцатого элемента И, первый

с и второй выходы регистра признака приема соединены с четвертыми входами соответственно питого и четвертого элементов И и с первым и вторым входами шестого элемента ИЛИ, прямой выход первого триггера соединен с вторым входом седьмого элемен0 та ИЛИ, с информационным входом регистра адреса вектора прерываний, инверсный выход первого триггера соединен с третьим входом элемента И-ИЛР 1, выход которого соединен с входом сброса шестого триггера, выход седьмого элемента ИЛИ соединен с

5 входом запроса канала блока прерываний, первый выход которого соединен с первым входом блока приемопередатчиков, управ- ЛИЮП1ИМ входом регистра адреса вектора прерывания и через второй элемент НН с четвертым входом элемента И-ИЛИ, второй

0 вход и выход блока приемопередатчиков соединены соответственно с выходом второго э.чемента ИЛИ и входом предоставлении прерываний блока прерывания, второй выход которого является выходом индикации сигна- ла предоставления нрерывании устройства, третий выход блока ирерывания соединен с вторым входом второго элемента ИЛИ, третий вход регистра состоянии соединен с выходом второго триггера.

19

дешифратора, группа выходов которого подключена к первым входам элементов И группы, вторые входы которых соединены с выходом триггера, а выходы являются соответственно вторым-шестым и первым выходами селектора и подключены к группам входов второго и третьего элементов ИЛИ, выходы которых образуют группу выходов селектора, первый вход первого элемента ИЛИ, соединенный с третьими входами первой подгруппы элементов И группы, второй вход первого элемента ИЛИ, соединенный с третьими входами второй подгруппы элементов И группы, синхровход регистра, соединенный с синхровходом триггера, и информационный вход регистра, соединенный с вторым входом элемента сравнения, образуют группу входов селектора адресов.

0

5

0

5

0

5

0

5

0

5

падения соединен с синхровходом третьего триггера и вторым входом сброса второго триггера, синхровход третьего регистра сое динен с вторым входом второго элемент. И и первым выходом второго счетчика, F , i lii

выход которого подключен к ИНфорМсШ li

ному входу четвертого триггера, ,i,,vi соединенного через второй фор.мпрог.гтм, импульса с входом начальной y. iaiioriKi делителя частоты и входо.м сброса м ;п, того триггера, синхровход которого щ. .., сч синхронизирующи.м входом блокл, nr|ii-,,iii и второй входы первого элемеиг; И .- K/IKI- чены соответственно к ,,i ; (мч г.М|. тактовых импульсов и вхол i ..MS, второй и первый выходы nepnoiD Г нччпг первый выход второго счетчика, .(мхо.ч iii-|i вого триггера, первый и второй В1,1ходы первого регистра, выход второго , пер вый и второй выходы третьего регистр;1. выходы третьего счетчика и первого рователя импульса являются COOTBCTCTBI IIIIO первым - одиннадцатым выходами блок;). информационный вход второго регистра ян- ляется кодовым входом блока.

мента И, прямой выход второго триггера, выходы четвертого триггера и второго элемента ИЛИ являются соответственно пятым, первым, вторым, четвертым и третьим выхо1-1

22

дами блока, первый и второй входы первого элемента ИЛИ являются соответственно первым и вторым командными входами блока.

affi/c/77/7Cf/rtf 3

фиг 1

Фиг 2

фиг. 5

| Устройство для сопряжения с общей маги-СТРАлью ВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU809143A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1982 |

|

SU1051526A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1177818, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1148029, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-01-13—Подача