Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения специализированных вычислительных устройств, предназначенных для автоматизированного решения задач конструирования радиоэлектронной и вычислительной аппаратуры.

Цель изобретения - упрощение устройства.

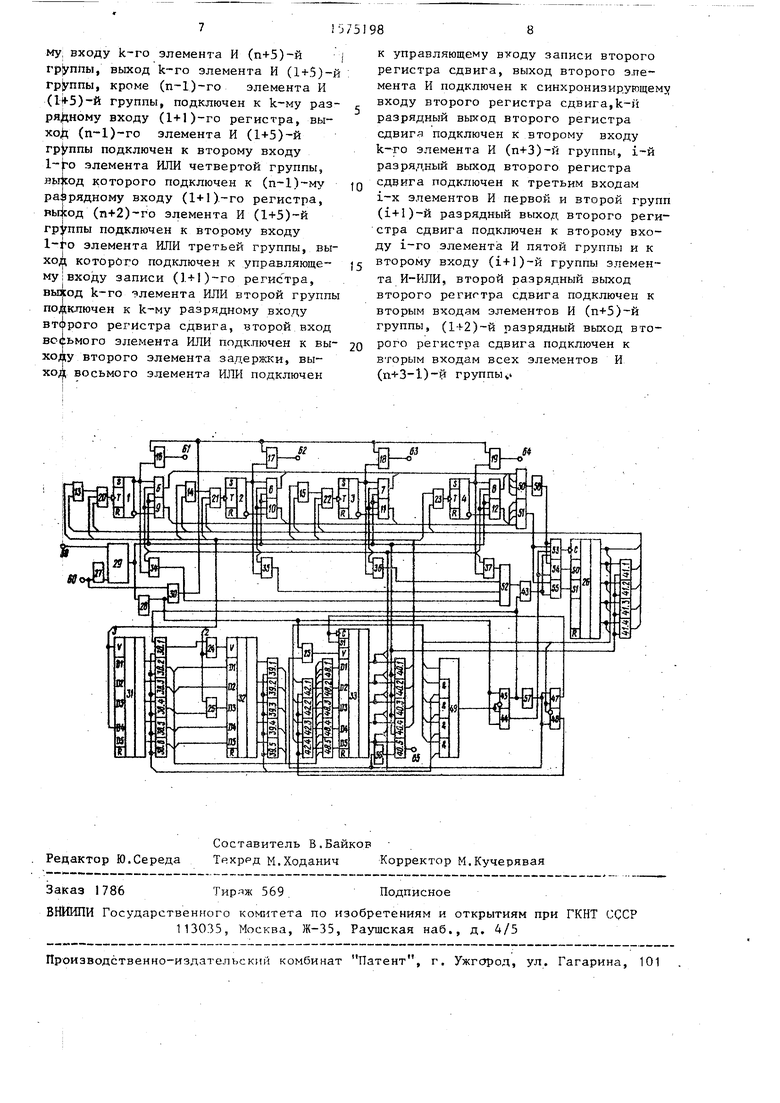

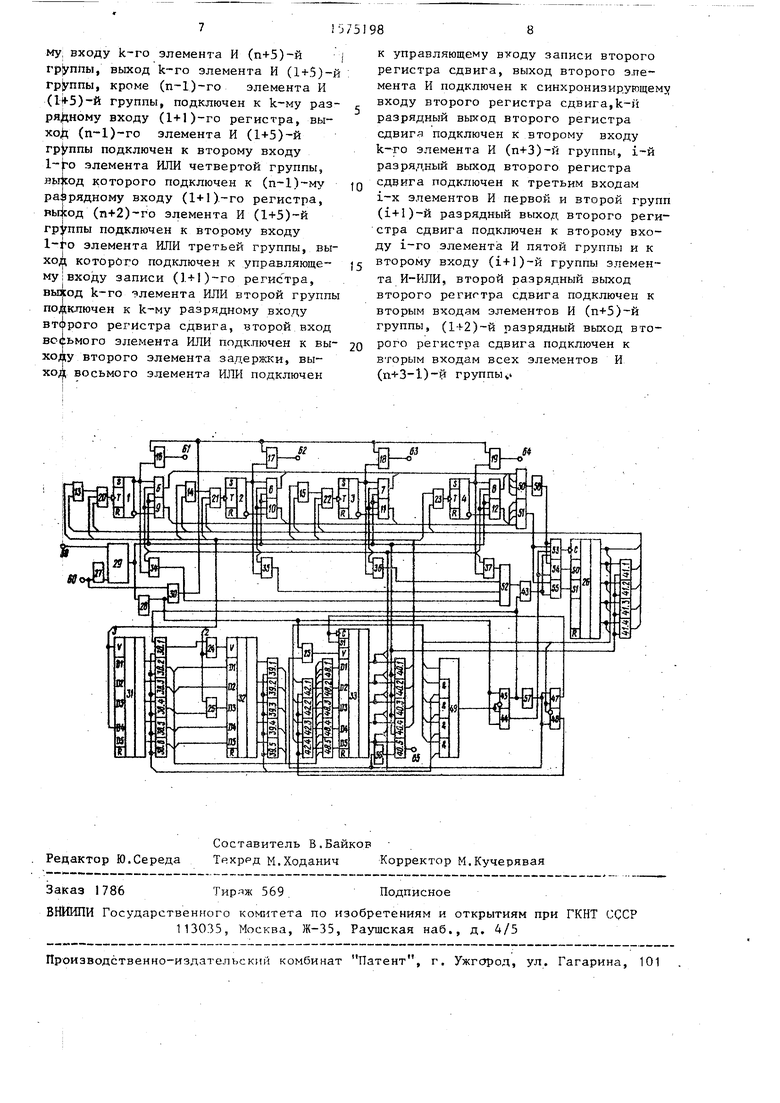

На чертеже представлена функциональная схема устройства на четыре разряда ().

Устройство содержит триггеры 1-4, элементы И 5-19, ИЛИ 20-25, регистр 26 сдвига, элементы 27 и 28 задержки, ключ 29, элемент ИЛИ 30, регистры 31 и 32, регистр 33 сдвига, элементы И 34-37, 38.1-38.6, 39.1-39.5, 40.1-40.5, 41.1-41.4, 42.1-42.4, 43-47, элементы ИЛИ 48.1-48.5, элемент И-ИЛИ 49, элементы ИЛИ 50-55, элементы 56-58 задержки, тактовый вход 59 кода, вход 60 запуска, информационные выходы 61-64, выход 65 окончания перебора.

В работе устройства используется алгоритм:

if gЈ - 1 then.

if t Ј О then gt«-gt

else g&M-SgM

t s t + 1

- 1

- 1

else{if then

se gv.-g,.,

СД

en

CO

00

8«,

if t

,

8Ј,

(

1 or t 0

8„

then t-t +

l se

t -t - g

/VЛ.

, t-t

if t 0

t.-i

then Ј 1 else Ј 1

л . .

и - 1

t + 1

€1

A

С/Л C. + 1

Перед началом работы триггеры -А регистры 26,31-33 устанавливаются в нулевое положение. Затем в тригге- рь: 1 и 2 (для случая , ) запи- сьвают единицы к регистр 26 записывается в унитарном коде значение , а в регистры 31-33 - в уни- коде значение С; k+1,, /, 1+1, где (). Пусковой им пу|льс с входа 60 поступает через эле ИЛИ 30 на входы элементов И 16- и открывая их, обеспечивает поступление очередного сочетания 1100 нф выходы устройства. Сигнал, пройдя эАемент 27 задержки, открывает ключ 29 для прохождения тактового им пульса с входа 59 на входы элементов И 5-12. Тактовый импульс, проходит через открытый элемент И 11 и далее через элементы ИЛИ 51,53 и 55, на в&оды С и S 1 регистра 26, осуществляя уменьшение значения на 1 (). Так как элемент И 40.3 открыт единичным потенциалом с третьего разрядного выхода регистра 33 а элемент И 41.1 - с второго разрядного выхода регистра 26, то импульс поступает через элементы И 41,1 и ИЛИ 20 на вход триггера 1, осуществляя его переход в нулевое состояние (,)« Через элементы И 40.3 и ИЛИ 22 импульс поступает на вход триггера 3, осуществляя его переброс в нулевое состояние (,) и через Элемент И 40,3 поступает на входы V и D 4 регистра 31, осуществляя запись в него значения Јэ 4 (ЈЈ,«-Ј,HС выхода элемента 28 задержки импульс поступает через элемент ИЛИ 30 на входы элементов И 16-19 и, открывая их, обеспечивает поступление очередного сочетания 0110 на выход устройства. Одновременно с этим импульс .с выхода элемента 28 задержки поступает через элемент ИЛИ 25 на вход V регистра 33, так как элемен гы И 38.1-38.6 открыты единичным потенциалом с третьего разрядного выхода регистра 33, то информация регистра перепишется в регистр 33 СЦ -Ј| )

0

0

0

5

5

0

45

0

5

Элемент И 5 открыт нулевым потенциалом с выхода элемента И-ИЛИ 49. Элемент И 35 открыт единичными потенциалами с единичного выхода триггера 2 и третьего разрядного выхода регистра 33, поэтому элемент И 43 также открыт. Импульс с выхода элемента И 45 проходит через элемент, И 43, ИЛИ 53 и 55 на входы С и S 1 регистра 26, уменьшая значение на ( t gЈ,.), а такжр на входы элементов И 38.1 и т.д. (при только один элемент И 38.1) и, так как элемент И 38.1 открыт единичным потенциалом с третьего разрядного выхода регистра 33, то импульс проходит через элемент ИЛИ 24 на вход V, разрешая перезапись информации из регистра 3 в регистр 32 (ЈЈ,,-ЈЈ,). С выхода элемента И импульс проходит через элемент 57 задержки и элемент И 47 на входы С и S 1 регистра 33, сдвигая информацию в нем на один разряд в сторону младшего разряда (j /o ). После формирования последнего сочетания 1001 в регист- рах будут содержаться слова: 00001, 00100, 00010. Элемент И 40.5 будет открыт единичным потенциалом с выхода последнего разряда регистра 33, следовательно импульс с выхода элемента 57 задержки, пройдя через элемент 56 задержки и элемент И 40.5, поступит на выход 65 окончания перебора.

Формула изобретения

Устройство дл я перебора сочетаний, содержащее п триггеров (п - число перебираемых элементов), ключ, первый регистр сдвига, п-2 регистров, четыре группы элементов ИЛИ, п+6 групп элементов И, элементы И-ИЛИ, восемь элементов ИЛИ, пять элементов И, пять элементов задержки, причем вход первого элемента задержки является пусковым входом устройства и соединен с первым входом первого элемента ИЛИ, выход первого элемента задержки подключен к управляющему входу ключа, информационный вход ключа является тактовым входом устройства, выход ключа подключен к входу второго элемента задержки, счетный вход 1-го триггера (,п) подключен к выходу 1-го элемента ИЛИ первой группы, прямой и инверсный выходы 1-го триггера подключены к первым входам 1-х элементов И и первой и второй групп соответственно, выходы элементов И первой группы подключены к входам второго элемента ИПИ, выходы элементов И второй группы подключены к входам третьего элемента ИЛИ, йыход второго элемента ИЛИ через третий элемент задержки подключен к первым входам четвертого и пятого элементов ИЛИ, выход третьего элемента ИЛИ подключен к второму входу четвертого элемента ИЛИ и к первому входу шестого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к синхронизирующему входу первого регистра сдвига, выходы пятого и шестого элементов ИЛИ подключены к управляющим вх,одам направления сдвига первого регистра сдвига, (i+1)-н разрядный выход первого регистра сдвига подключен к первому входу 1-го элемента И третьей группы, выход которого подключен к первому входу 1-го элемента ИЛИ первой группы, второй вход j-го (,) элемента ИЛИ первой группы соединен с выходом-j-го элемента И четвертой группы, первые входы всех элементов И четвертой группы подключены к первому разрядному выходу первого регистра сдвига, прямой выход 1-го триггера подключен к первому входу 1-го элемента И пятой группы, выходы элементов И пятой группы подключены к входам седьмого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, выход первого элемента И подключен к третьему входу четвертог элемента ИЛИ и к второму входу шестого элемента ИЛИ, выход второго элемента задержки подключен к второму входу первого элемента ИЛИ, к прямому входу второго элемента И и к первому входу третьего элемента И, выход второго элемента И подключен к второму входу первого элемента И, к входу четвертого элемента задержки и к первым входам (п+2)-х элементов И с шестой по (п+2)-ю групп, выход третьего элемента И подключен к четвертому входу четвертого элемента ИЛИ и к второму входу пятого элемента ИЛИ, выход четвертого элемета задержки подключен к первому входу четвертого элемента И к прямому входу пятого элемента И, к первому входу восьмого элемента ИЛИ и через пятый элемент задержки к первому

575198

- он10

15

20

25

входу (п-И)-го элемента И (п+3)й группы, выход пятого элемента И подключен к первым входам всех элементов И (п+4)й группы, первый разрядный выход первого регистра сдвига подключен к второму входу четвертого элемента И и к инверсному входу пятого элемента И, (1+1)-й разрядный выход первого регистра сдвига подключен к второму входу 1-го элемен- та И (п+4)-й группы, k-й (,n+l) разрядный выход первого регистра сдвига подключен к первому входу k-й группы элементов И-ИЛИ, выход элемента И-ИЛИ подключен к инверсному входу второго элемента И и к второму входу третьего элемента И, вы- хол i-ro элемента И (п+4)-й группы подключен к соответствующему входу (i+l-)-ro элемента ИЛИ второй группы, выходы k-x элементов И с шестой по (п+2)-к групп., а также (п+5)-й группы подключены к соответствующим входам k-го элемента И-ИЛИ второй группы, первый вход 1-го элемента И (п+6)-й группы подключен к прямому выходу i-ro триггера, вторые входы элементов И (п+6)-й группы являются выходами устройства, выход (п+1)-го элемента И (п+3)-й группы является выходом окончания перебора устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит второй регистр сдвига, причем выход ключа подключен к вторым вхо- лам элементов И первой и второй - групп, к вторым входам элементов И третьей группы, к первым входам с первого по n-й элемент И (п+3)-й группы, выход 1-го элемента И (.п+3)-й группы подключен к третьему входу j-ro элемента ИЛИ первой группы, выход n-го элемента И (г+3)-й группы подключен к второму входу

45 n-го элемента ИЛИ первой группы,выход (j+l)-ro элемента И (п+3)-й группы подключен к второму входу j-ro элемента И четвертой группы, выход (1+1)-го (, п-3) элемента И

50 (п+3)и группы подключен к первым входам 1-х элементов ИЛИ третьей и четвертой групп, выход (n-l)-ro элемента И (гН-З)-й групп подключен к n-му разрядному входу и управляющему

cj входу записи первого регистра, k-й разрядный выход 1-го регистра подключен к первому входу k-ro элемента И (1+5)-и группы, k-й разрядный выход (п-2)го регистра подключен к перво30

35

40

му входу k-го элемента И (п+5)-й группы, выход k-ro элемента И (1+5)-й группы, кроме (n-l)-ro элемента И ()-и группы, подключен к k-му раз- рядному входу (1+1)-го регистра, выход (n-l)-ro элемента И (1+5)-й группы подключен к второму входу 1-го элемента ИЛИ четвертой группы, вьфод которого подключен к (п-1)му разрядному входу (1+1)-го регистра, РЫХОД (п+2)го элемента И (1+5)-й группы подключен к второму входу 1-го элемента ИЛИ третьей группы, вы- хо которого подключен к управляюще- му входу записи (1-Й)-го регистра, выход k-ro -элемента ИЛИ второй группы подключен к k-му разрядному входу второго регистра сдвига, второй вход восьмого элемента ИЛИ подключен к вы- второго элемента задержки, вы- хо$ восьмого элемента ИЛИ подключен

к управляющему входу записи второго регистра сдвига, выход второго эпе- мента И подключен к синхронизирующем входу второго регистра сдвига,k-й разрядный выход второго регистра сдвигя подключен к второму входу k-ro элемента И (п+3)-н группы, 1-й разрядный выход второго регистра сдвига подключен к третьим входам 1-х элементов И первой и второй груп (1+1)-й разрядный выход второго регистра сдвига подключен к второму входу 1-го элемента И пятой группы и к второму входу (1+1)-й группы элемента И-ИЛИ, второй разрядный выход второго регистра сдвига подключен к вторым входам элементов И (п+5)-й группы, ()-й разрядный выход второго регистра сдвига подключен к вторым входам всех элементов И (п+3-1)-й группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для перебора сочетаний | 1987 |

|

SU1427382A1 |

| Устройство для исследования графов | 1985 |

|

SU1252791A1 |

| Устройство для упорядочивания чисел | 1984 |

|

SU1241228A1 |

| Устройство для перебора сочетаний | 1986 |

|

SU1370655A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Функциональный генератор перестановок | 1987 |

|

SU1513467A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| Устройство для определения вероятностного состояния дискретной системы | 1983 |

|

SU1164729A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1532943A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения специализированных вычислительных устройств, предназначенных, например, для автоматизированного конструирования радиоэлектронной и вычислительной аппаратуры. Целью изобретения является упрощение устройства. Устройство содержит триггеры, регистры, регистры сдвига, элементы И, ИЛИ, И-ИЛИ, элементы задержки. По сравнению с прототипом исключены два регистра, четыре группы элементов И, две группы элементов задержки, элемент И, элемент ИЛИ, три элемента задержки. 1 ил.

й-Ј

| Устройство для перебора сочетаний | 1985 |

|

SU1262520A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для перебора сочетаний | 1987 |

|

SU1427382A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-30—Публикация

1988-04-27—Подача